Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации c цифровым вычислительным устройствам.

Известен способ преобразования угла поворота вала в код, основанный на преобразовании угла в фазный гармонический сигнал, сдвинутый относительно опорного по фазе пропорционально углу поворота вала, интегрировании фазного гармонического сигнала дважды за период опорного сигнала в течение равных временных интервалов, сдвинутых по фазе относительно друг друга на π/2 , сравнении между собой результатов интегрирования в первом и втором временных интервалах, определении отношения меньшего по модулю из сравниваемых значений к большему, арктангенсном преобразовании значений отношения в код угла [1] . Недостатком известного способа является низкое быстродействие и малая точность, вызванная инструментальными погрешностями формирования фазного гармонического сигнала относительно опорного при реализации способа.

Наиболее близким техническим решением к данному изобретению является способ преобразования угла поворота вала в код, основанный на преобразовании угла в два фазных гармонических сигнала, первый из которых сдвинут относительно опорного по фазе пропорционально углу поворота вала, сравнении в дискретные моменты времени текущих значений амплитуды фазного сигнала с ортогональными им значениями, определении отношения меньшего по модулю из сравниваемых значений к большему, арктангенсном преобразовании отношения с учетом знаков сравниваемых значений и разности их модулей в текущее значение угла первого фазного сигнала, формировании мгновенных значений выходного кода угла поворота вала, при этом формируют второй фазный гармонический сигнал сдвинутым по фазе на π/2 относительно первого фазного сигнала, ортогональными значениями при сравнении являются текущие значения амплитуды второго фазного гармонического сигнала, а мгновенные значения выходного кода угла поворота вала формируют а виде разности текущих значений угла первого фазного сигнала и пилообразно изменяющегося опорного кода [2]. Недостатками известного способа являются наличие погрешности смещения фазных гармонических сигналов относительно опорного при изменении внешних условий, наличие случайных погрешностей, вызванных воздействием наводок, необходимость многофазного фазовращателя для преобразования угла поворота в два фазных гармонических сигнала, смещенных относительно друг друга на π/2 , а также аналогового селектора, что затрудняет реализацию способа.

Целью изобретения является повышение точности и упрощение аппаратурной реализации способа.

Поставленная цель достигается тем, что в способе преобразования угла поворота вала в код, основанном на преобразовании угла в два фазных гармонических сигнала, первый из которых сдвинут относительно опорного по фазе пропорционально углу поворота вала, сравнении в дискретные моменты времени текущих значений амплитуды первого фазного сигнала с ортогональными им значениями, определении отношения меньшего по модулю из сравниваемых значений к большему, арктангенсном преобразовании отношения с учетом знаков сравниваемых значений и разности их модулей в текущее значение угла первого фазного сигнала, формировании мгновенных значений кода угла поворота вала, формируют второй фазный гармонический сигнал сдвинутым относительно опорного по фазе на угол, пропорциональный дополнению угла до 2π , формируют ортогональные значения задержкой на π/2 текущих значений амплитуды первого фазного сигнала, сравнивают в те же дискретные моменты времени текущие значения амплитуды этого же сигнала π/2 и определяют отношение меньшего по модулю сравниваемого значения к большему для второго фазного сигнала, осуществляют арктангенсное преобразование отношения с учетом знаков сравниваемых значений и разности их модулей в текущее значение угла второго фазного сигнала, формируют мгновенные значения кода угла поворота вала в виде разности текущих значений угла первого и второго фазных сигналов, осуществляют скользящее усреднение мгновенных значений угла поворота вала.

Совокупность вновь введенных операций не обнаружена ни в одном из известных источников информации. Следовательно, по мнению авторов, предложенное техническое решение соответствует критерию изобретения "существенные отличия" и обеспечивает достижение поставленной цели - повышение точности и упрощение аппаратурной реализации способа.

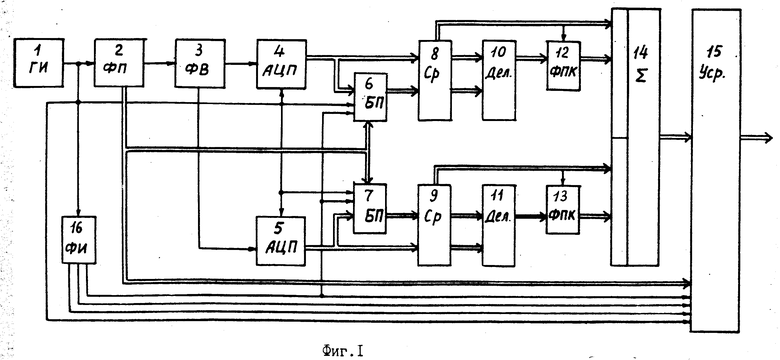

На фиг. 1 изображена структурная схема преобразователя угла поворота вала в код для осуществления предлагаемого способа; на фиг. 2 - структурная схема блока скользящего усреднения; на фиг. 3 - структурная схема формирования импульсов; на фиг. 4 - циклограмма работы преобразователя.

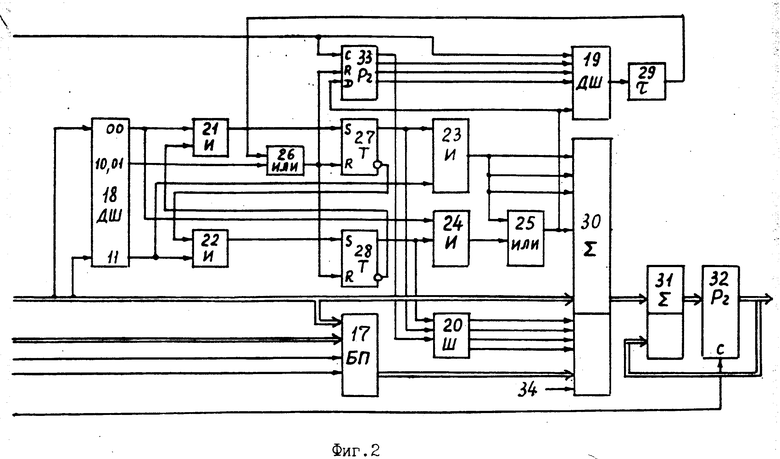

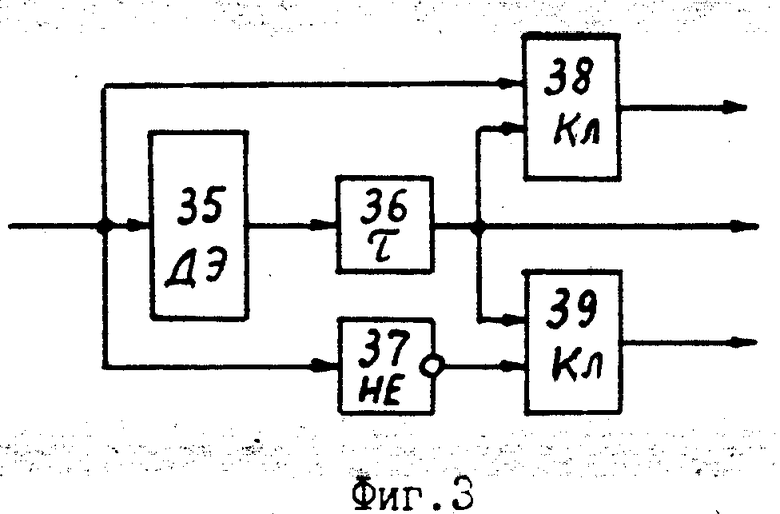

Преобразователь (фиг.1) содержит генератор 1 импульсов, формирователь 2 питания, фазовращатель 3, аналого-цифровые преобразователи (АЦП) 4 и 5, блоки 6 и 7 памяти, блоки 8 и 9 сравнения, блоки 10 и 11 деления, блоки 12 и 13 функционального преобразования кодов, цифровой сумматор 14, блок 15 скользящего усреднения, формирователь 16 импульсов. Блок 15 скользящего усреднения (фиг. 2) содержит блок 17 памяти, дешифраторы 18 и 19, шифратор 20, элементы 21 - 24 И, элементы 25, 26 ИЛИ, триггеры 27, 28, элемент 29 задержки, сумматоры 30 и 31, регистры 32 и 33, кодовую шину 34, формирователь 16 импульсов (фиг. 3) содержит дифференцирующий элемент 35, элемент 36 задержки, инвертор 37, ключи 38, 39.

Выход генератора 1 подключен к входу формирователь 2 питания, входу формирователя 16 импульсов, управляющим входам блоков 6 и 7 памяти, первому входу блока 15 и входам синхронизации АЦП 4 и 5. Формирователь 2 питания может быть выполнен в виде последовательно соединенных делителя частоты и фильтра, настроенного на частоту первой гармоники. Аналоговый выход формирователя 2 (выход фильтра) подключен к воду фазовращателя 3, который может быть выполнен в виде синусно-косинусного датчика угла с двумя фазосдвигающими RC-цепочками. Первый и второй выходы фазовращателя 3 подключены к информационным входам АЦП 4 и 5 соответственно. Выход АЦП 4 подключены к первой группе входов блока 8 сравнения и к информационным входам блока 6 памяти, выходы которого подключены к второй группе входов блока 8. Первая группа выходов блока 8 подключена к старшим разрядам первой группы входов сумматора 14, вторая и третья группы выходов блока 8 подключены соответственно к первой и второй группам входом блока 10 деления, выходы которого через блок 12 функционального преобразования кодов (ФПК) подключены к младшим разрядам первой группы входов сумматора 14. Один вход блока 12 соединен с выходом младшего разряда первой группы выходов блока 3. Выходы АЦП 5 подключены к первой группе входов блока 9 сравнения и к информационным входам блока 7 памяти, выходы которого подключены к второй группе входов блока 9.

Первая группа выходов блока 9 подключена к старшим разрядам второй группы входов сумматора 14, вторая и третья группы выходов блока 9 подключены соответственно к первой и второй группам входов блока 11 деления, выходы которого через блок 13 ФПК подключены к младшим разрядам второй группы входов сумматора 14. Один вход блока 13 соединен с выходом младшего разряда первой группы выходов блока 9. Выходы сумматора 14 подключены к информационным входам блока 15 скользящего усреднения, Цифровые выходы формирователя 2 (выходы разрядов делителя частоты) подключены к адресным входам блоков 6, 7 и 15. Выходы формирователя 16 импульсов подключены к соответствующим входам блока 15, а первый выход формирователя 16 подключен к входам разрешения блоков 6 и 7.

Информационные входы блока 17 памяти являются информационными входами блока 15 и подключены к младшим разрядам первой группы входов сумматора 30. Входы двух старших разрядов блока 17 подключены к входам дешифратора 13, первый выход которого подключен к первым входам элементом И 21, И 24, второй выход - к первым входам элементов И 22, И 23, выходы элементов И 21, И 22 подключены к одним входам триггеров 17 и 28, прямые выходы которых подключены соответственно к вторым входам элементов И 23, И 24, а инверсные выходы - к вторым входам элементов И 22, И 21. Выходы элементов И 23, И 24 через элемент ИЛИ 25 подключены к информационному входу регистра 15 и к входу младшего из старших разрядов первой группы входов сумматора первой группы входов сумматора 30, выход элемента И 23 подключен к входам остальных старших разрядов первой группы входов сумматора 30, выходы которого подключены к первой группе входов сумматора 31, выходы сумматора 31 подключены к информационным входам регистра 32, выходы которого являются выходами блока 15 и подключены к второй группе входом сумматора 31. Адресные входы блока 17 памяти являются адресными входами блока 15, а выходы блока 17 подключены к младшим разрядам второй группы входом сумматора 30, вход переноса сумматора соединен с шиной 34. Выход старшего разряда регистра 33, прямые выходы триггеров 27 и 28 подключены к входам шифратора 20, выходы которого подключены к старшим разрядам второй группы входов сумматора 30. Управляющий вход блока 17, вход разрешения блока 17, тактовый вход регистра 32 и тактовый вход регистра 33 являются входами с первого по четвертый соответственно блока 15. Выход элемента ИЛИ 25, тактовый вход регистра 33 и выходы младших разрядов регистра 33 подключены к входам дешифратора 19, выход которого через элемент 29 задержки подключен к одному входу элемента 26 ИЛИ, другой вход которого соединен с третьим выходом дешифратора 18, а выход подключен к входу сброса регистра 33 и к другим входам триггеров 27 и 28.

Вход дифференцирующего элемента 35 (фиг.3) является входом формирователя 16 и соединен с первым входом ключа 38, и через инвертор 37 - с первым входом ключа 39, выход дифференцирующего элемента 35 через элемент 36 задержки соединен с вторыми входами ключей 38. 39. Выходы элементов 36, 38 и 39 являются соответственно первым, вторым и третьим выходами формирователя 16.

Преобразователь работает следующим образом.1

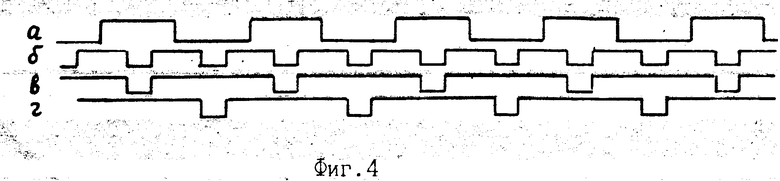

Генератор 1 формирует высокочастотные импульсы (фиг.4a) частотой fги. На выходах делителя частоты, входящего в состав формирователя 2, формируется пилообразно изменяющийся в функции времени код с частотой fо = fги/2k с дискретностью изменения, равной периоду генератора 1. Из выходных сигналов делителя частоты фильтр, входящий в состав формирователя 2, вырабатывает гармонический сигнал частотой fо питания фазовращателя 3, который работает в режиме пульсирующего поля с двойным фазосдвигающим элементом и вырабатывает два фазных гармонических сигнала, первый из которых сдвинут относительно опорного (сигнала питания) по фазе на угол +pα (где P - коэффициент электрической редукции фазовращателя 3, α - угол поворота вала фазовращателя 3), а второй сдвинут относительно опорного по фазе на угол -pα . В АЦП 4 и 5 определяются текущие значения N1 амплитуд первого и второго фазных гармонических сигналов с выходов фазовращателя 3 в каждом из периодов генератора 1. Измерение входных напряжений в АЦП 4 и 5 начинается по фронту выходного импульса генератора 1. В первом полупериоде выходного сигнала генератора 1 по импульсу разрешения с выхода элемента 36 (фиг. 4,б) из блоков 6 и 7 воспроизводится информация по адресу, соответствующем выходному коду делителя частоты формирователя 2. По концу импульса разрешения эта информации записывается в регистрах, входящих в состав соответствующих блоков памяти. Во втором полупериоде выходного сигнала генератора 1 по импульсу разрешения с выхода элемента 36 в блоки 6 и 7 памяти записывается текущая информация N1 с выходов соответствующих АЦП 4 и 5 по тому же адресу. В следующем периоде выходного сигнала генератора 1 адреса блоков 6 и 7 увеличивается на единицу. Число адресных разрядов блоков 6 и 7 выбирается равным K-2. В результате значения амплитуды первого и второго фазовых сигналов задерживаются в блоках 6 и 7 на π/2 и представляют собой ортогональные значения N2 по отношению к текущим значениям N1 амплитуд, сформированным в АЦП 4 и 5.

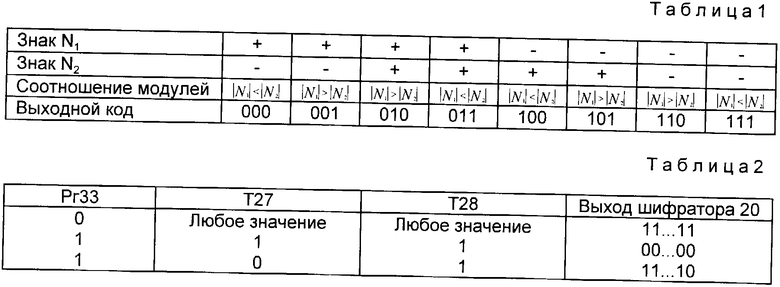

В блоках 8 и 9 анализируют знаки входных цифровых сигналов и их модули. В соответствии с табл. 1 на первой группе выходов блоков 8 и 9 формируют три старших разряда текущих значений угла первого и второго фазных сигналов.

Кроме того, в блоках 8 и 9 осуществляют подключение меньшего модуля  или

или  к входам делителя соответствующего блока 10 и 11, а большего модуля - к входам делителя того же блока 10 и 11. То есть блоки 8 и 9 по своему функциональному назначению эквивалентны селекторам октантов при работе с аналоговыми синусно-косинусными сигналами и могут быть выполнены в виде цифрового компаратора модулей

к входам делителя соответствующего блока 10 и 11, а большего модуля - к входам делителя того же блока 10 и 11. То есть блоки 8 и 9 по своему функциональному назначению эквивалентны селекторам октантов при работе с аналоговыми синусно-косинусными сигналами и могут быть выполнены в виде цифрового компаратора модулей  и

и  , дешифратора (для преобразования однопеременного кода знаков N1, N2 и цифрового компаратора модулей в арифметический код) и мультиплексора (для переключения модулей

, дешифратора (для преобразования однопеременного кода знаков N1, N2 и цифрового компаратора модулей в арифметический код) и мультиплексора (для переключения модулей  и

и  на две группы выходов в зависимости от выходного сигнала цифрового компаратора модулей).

на две группы выходов в зависимости от выходного сигнала цифрового компаратора модулей).

В блоках 10 и 11 определяют отношение меньшего по модулю значения  или

или  к большему значению, то есть формируют текущие значения тангенса (котангенса) в диапазоне π/4 для первого и второго фазных сигналов. В блоках 12 и 13 осуществляют функциональное преобразование кода тангенса в код угла. При этом в четных октантах (при единичном значении младшего разряда первой группы выходов блоков 8, 9 в соответствии с табл.1) в блоках 12 и 13 формируют дополнительный код. В результате на выходах блоков 12 и 13 формируют младшие разряды текущих значений угла первого и второго фазных сигналов.

к большему значению, то есть формируют текущие значения тангенса (котангенса) в диапазоне π/4 для первого и второго фазных сигналов. В блоках 12 и 13 осуществляют функциональное преобразование кода тангенса в код угла. При этом в четных октантах (при единичном значении младшего разряда первой группы выходов блоков 8, 9 в соответствии с табл.1) в блоках 12 и 13 формируют дополнительный код. В результате на выходах блоков 12 и 13 формируют младшие разряды текущих значений угла первого и второго фазных сигналов.

В сумматоре 14 формируют мгновенные значения кодов угла поворота вала в виде разности текущих значений угла первого и второго фазных сигналов в каждом периоде сигнала генератора 1. В блоке 15 осуществляют скользящее усреднение мгновенных значений угла поворота вала.

В первом полупериоде выходного сигнала генератора 1 по импульсу разрешения с выхода элемента 36 (фиг.4,б) из блока 17 воспроизводится информация по адресу, соответствующему выходному коду делителя частоты формирователя 2. Информация с инверсных выходов блока 17 поступает на младшие разряды второй группы входов сумматора 30, старшие разряды которой соединены с выходами шифратора 20, а вход переноса соединен с шиной 34 единичного потенциала. В сумматоре 30 происходит вычитание выходного кода блока 17 из текущего выходного кода сумматора 14. При этом вычитание заменено суммированием в дополнительном коде. Сформированная в сумматоре 30 разность кодов суммируется в сумматоре 31 с выходным кодом преобразователя с выхода регистра 32 и по фронту импульса с ключа 38 (фиг.4,в) записывается в регистр 32. Во втором полупериоде выходного сигнала генератора 1 по импульсу разрешения с выхода элемента 36 в блоке 17 памяти записывается текущая информация с выходов сумматора 14 по тому же адресу. По фронту импульса с ключа 39 (фиг.4,г) информация в регистре 33 сдвигается на один разряд. В следующем периоде выходного сигнала генератора 1 код адреса делителя частоты формирователя 2 увеличивается на единицу.

В дешифраторе 13 анализируется состояние двух старших разрядов каждого значения выходного кода сумматора 14. При нулевом состоянии этих разрядов выходной сигнал дешифратора 18 проходит через открытый элемент И 21 и устанавливает в 1 триггер 27. Элемент И 22 закрывается, а элемент И 23 открывается. В этом состоянии дешифратора 18, а также при увеличении кода сумматора 14 (состояние его старших разрядов равно 01, триггеры 27 и 28 сброшены с 0 и элементы 23, 24 закрыты) нулевые сигналы с выходов элементов 23 и 25 поступают на входы старших разрядов первой группы входов сумматора 30 и на один информационный вход последовательного регистра 33.

Если выходной код сумматора 14 уменьшается и переходит через границу полюсного деления (код старших разрядов изменяется из состояния 00 в состояние 11), то при каждом значении кода сумматора 14 со старшими разрядами 11 сигнал со второго выхода дешифратора 13 проходят через элементы 23 и 25 и в виде единичного сигнала поступает на входы старших разрядов первой группы входов сумматора 30. Единичный признак перехода через границу полюсного деления, сформированный элементом 25, запоминается в регистре 33. Текущее значение кода сумматора 14 запоминается в блоке 17 памяти. Шифратор 20 формирует значения старших разрядов второй группы входов сумматора 30 в зависимости от состояния старшего разряда регистра 33 и состояния триггеров 27, 18 в соответствии с табл.2.

Наличие единичных признаков на выходах всех младших разрядов регистра 33 и на выходе элемента 25 свидетельствует о завершении перехода через границу полюсного деления, когда все слагаемые суммы, хранящейся в регистре 32, соответствуют максимальным (старшие разряды кода блока 17 равны 11) или минимальным (старшие разряды кода блока 17 равны 00) значениям. При этом по отрицательному импульсу с выхода ключа 39 срабатывает дешифратора 19, и его выходной сигнал через элемент 29 задержки сбрасывает в 0 регистр 33 и триггеры 27, 28. Число слагаемых в каждом значении суммарного кода регистра 32 равно числу 2m ячеек памяти блока 17, при этом регистр 33 должен иметь 2m разрядов. Коррекция выходного кода регистра 32 после заверения перехода через границу полюсного деления не требуется. После окончания импульса сброса с выхода элемента 29 триггер 23 устанавливается в 1 сигналом с второго выхода дешифратора 18. При дальнейшем уменьшении выходного кода сумматора 14 состояние его старших разрядов становится равным 10. Сигналом с третьего выхода дешифратора 18 сбрасываются в 0 триггеры 28, 27 и регистр 22.

При переходе через границу полюсного деления в сторону увеличения кодов значение старших разрядов сумматора 14 изменяется из состояния 11 в состояние 00. Сначала сигналом с второго выхода дешифратора 18 триггер 28 устанавливается в 1. Затем при каждом значении коды сумматора 14 со старшими разрядами 00 сигнал с первого выхода дешифратора 18 проходит через элементы 24 и 25 и поступает на вход младшего из старших разрядов первой группы входов сумматора 30, на информационный вход регистра 33 и на одни из входов дешифратора 19. В регистре 33 последовательно записываются признаки, соответствующие кодам со старшими разрядами 00. Для каждого значения выходного кода блока 17 в шифраторе 20 формируется код старших разрядов в соответствии с табл.2. В каждом периоде генератора 1 происходит формирование разности между текущим кодом сумматора 14 со старшими разрядами с выходом элементов 23, 25 и кодом, задержанным на 2m тактов в блоке 17, со старшими разрядами этого кода с выходов шифратора 20. Полученная разность суммируется с выходным кодом регистра 32, соответствующим сумме 2m предыдущих значений кодов, и запоминается в регистре 32. В результате в каждом периоде генератора 1 производится обновление информации в регистре 32 путем замены значения, отстоящего от текущего на 2m тактов, на текущее значение. Число слагаемых в сумме мгновенных значений угла, хранящейся в регистре 32, всегда постоянно и равно 2m. Перед началом преобразования все триггеры, регистры и блоки памяти должны быть обнулены. Формирователь 16 управляющих импульсов является вспомогательным блоком, обслуживающим работу преобразователя.

Определение текущих значений угла для каждого фазного гармонического сигнала в дискретные моменты времени с частотой генератора импульсов позволило использовать преимущества преобразования угла поворота в два фазных гармонических сигнала, относительный сдвиг по фазе между которыми равен удвоенному значению угла поворота вала (без учета коэффициента электрической редукции) и не зависит от смещения по фазе относительно опорного напряжения, что повышает точность предложенного способа по сравнению с известным. Дополнительное повышение точности путем снижения влияния случайных погрешностей в  раз при сохранении быстродействия обеспечивает следящее усреднение мгновенных значений угла поворота. Разрешающая способность предложенного способа определяется числом разрядов АЦП, предназначенных для определения текущих значений амплитуды фазных гармонических сигналов. Поэтому при реализации предложенного способа не требуется высокочастотного генератора импульсов, что упрощает его по сравнению с известным способом. Для выполнения операций формирования ортогональных значений по отношению к текущим значениям амплитуд первого и второго фазных гармонических сигналов, сравнения текущих значений амплитуд с их ортогональными значениями, определения отношения меньшего по модулю из сравниваемых значений к большему, арктангенсного преобразования отношений с учетом знаков сравниваемых значений и разности их модулей в текущие значения угла первого и второго фазных сигналов, формирования мгновенных значений кода угла поворота и скользящего усреднения можно вместо совокупности блоков 6 - 15 использовать микропроцессор.

раз при сохранении быстродействия обеспечивает следящее усреднение мгновенных значений угла поворота. Разрешающая способность предложенного способа определяется числом разрядов АЦП, предназначенных для определения текущих значений амплитуды фазных гармонических сигналов. Поэтому при реализации предложенного способа не требуется высокочастотного генератора импульсов, что упрощает его по сравнению с известным способом. Для выполнения операций формирования ортогональных значений по отношению к текущим значениям амплитуд первого и второго фазных гармонических сигналов, сравнения текущих значений амплитуд с их ортогональными значениями, определения отношения меньшего по модулю из сравниваемых значений к большему, арктангенсного преобразования отношений с учетом знаков сравниваемых значений и разности их модулей в текущие значения угла первого и второго фазных сигналов, формирования мгновенных значений кода угла поворота и скользящего усреднения можно вместо совокупности блоков 6 - 15 использовать микропроцессор.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ УГЛА ПОВОРОТА ВАЛА | 1993 |

|

RU2107390C1 |

| СПОСОБ ИЗМЕРЕНИЯ УГЛА ПОВОРОТА ВАЛА | 1995 |

|

RU2108664C1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1797161A1 |

| СПОСОБ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107334C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ АБОНЕНТОВ С ЦВМ | 1991 |

|

RU2018942C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1807560A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. Целью изобретения является повышение точности. Поставленная цель достигается тем, что формируют второй фазный гармонический сигнал сдвинутым относительно опорного по фазе на угол, пропорциональный дополнению угла до 2π , формируют ортогональные значения задержкой на π/2 текущих значений амплитуды первого фазного сигнала, сравнивают в те же дискретные моменты времени текущие значения амплитуды второго фазного сигнала с задержанием на π/2 значениями амплитуды этого же сигнала и определяют отношение меньшего по модулю сравниваемого значения к большему для второго фазного сигнала, осуществляют арктангенсное преобразование отношения с учетом знаков сравниваемых значений и разности их модулей в текущее значение угла второго фазного сигнала, формируют мгновенные значения угла поворота вала в виде разности текущих значений угла первого и второго фазных сигналов, осуществляют скользящее усреднение мгновенных значений угла поворота вала. 4 ил., 2 табл.

Способ преобразования угла поворота вала в код, основанный на преобразовании угла в два фазных гармонических сигнала, первый из которых сдвинут относительно опорного по фазе пропорционально углу поворота вала, сравнении в дискретные моменты времени текущих значений амплитуды первого фазного гармонического сигнала с ортогональными им значениями, определении отношения меньшего по модулю из сравниваемых значений к большему, арктангенсном преобразовании отношения с учетом знаков сравниваемых значений и разности их модулей в текущее значение угла первого фазного гармонического сигнала, формировании мгновенных значений кода угла поворота вала, отличающийся тем, что формируют второй фазный гармонический сигнал сдвинутым относительно опорного по фазе на угол, пропорциональный дополнению угла до 2π, формируют ортогональные значения задержкой на π/2 текущих значений амплитуды первого фазного гармонического сигнала, сравнивают в те же дискретные моменты времени текущие значения амплитуды второго фазного гармонического сигнала с задержанными на π/2 значениями амплитуды этого же сигнала и определяют отношение меньшего по модулю сравниваемого значения к большему для второго фазного гармонического сигнала, осуществляют арктангенсное преобразование отношения с учетом знаков сравниваемых значений и разности их модулей в текущее значение угла второго фазного гармонического сигнала, формируют мгновенные значения кода угла поворота вала в виде разности текущих значений угла первого и второго фазных гармонических сигналов, осуществляют скользящее усреднение мгновенных значений угла поворота вала.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, авторское свидетельство, 1365354, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| SU, авторское свидетельство, 1314459, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-04-10—Публикация

1993-05-31—Подача