Изобретение относится к вычислительной технике и интегральной электронике.

Известны интегральные логические элементы на КМОП-структурах с металлическими затворами. Эти структуры характеризуются большими значениями межэлектродных паразитных емкостей затвор-исток и затвор-сток, невысоким быстродействием и занимают большую площадь на кристалле.

От указанных недостатков свободны логические элементы на КМОП-структурах, выполненных с использованием изопланарной технологии с самосовмещенными поликремниевыми затворами. Однако отсутствие совмещения затворов р-канального и n-канального транзисторов КМОП-структуры в одной поликремниевой входной шине не позволяет уменьшить занимаемую площадь.

Наиболее близким к изобретению по технической сущности и достигаемому результату является интегральной логический элемент на КМОП-структурах. Элемент реализован с использованием современной изопланарной технологии с самосовмещенными поликремниевыми затворами. Кроме того, в элементе можно выделить входную зону, в которой затворы р- и n-канального транзисторов совмещены в общей поликремниевой входной шине.

К недостаткам следует отнести невозможность введения в элемент транзитной шины, отсутствие самостоятельной выходной зоны, изгибы проводников, снижающие быстродействие (при большой длине связей) и степень интеграции устройств на основе данного элемента.

Целью изобретения является уменьшение занимаемой площади и повышение быстродействия элемента и устройств на его основе, а также снижение затрат на проектирование микросхем в целом.

Цель достигается тем, что в интегральный логический элемент, содержащий полупроводниковую подложку первого типа проводимости с расположенной в ней областью "кармана" второго типа проводимости и соединенные с ними соответственно металлические шину питания и шину нулевого потенциала, две входные зоны, каждая из которых содержит расположенный в "кармане" второго типа проводимости транзистор первого типа проводимости и расположенный в подложке первого типа проводимости транзистор второго типа проводимости, затворы которых объединены и выполнены в виде общей входной поликремниевой шины, выходную зону, содержащую выходную шину, соединенную со стоками первого и второго транзисторов второго типа проводимости и первого транзистора первого типа проводимости, исток которого соединен со стоком второго транзистора первого типа проводимости , исток второго транзистора первого типа проводимости соединен с шиной нулевого потенциала, а истоки транзисторов второго типа проводимости соединены с шиной питания, введены зона транзита, содержащая поликремниевую транзитную шину, и соединенная с поликремниевой выходной шиной металлическая П-образная выходная шина, перпендикулярная поликремниевым шинам, причем расположенные между шинами питания и нулевого потенциала входные, выходная и транзитная зоны взаимозаменяемы вдоль логического элемента.

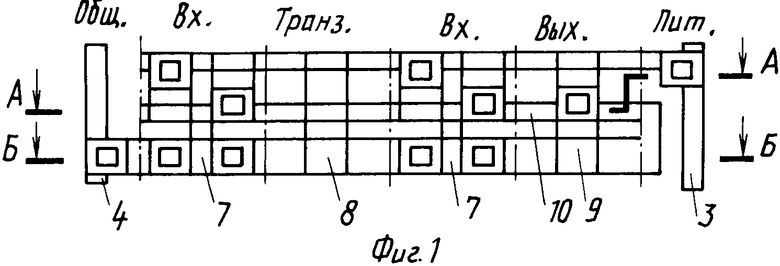

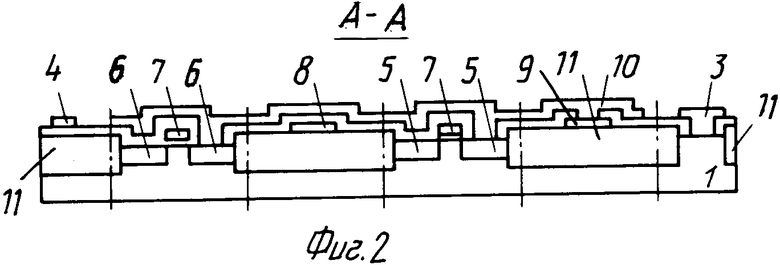

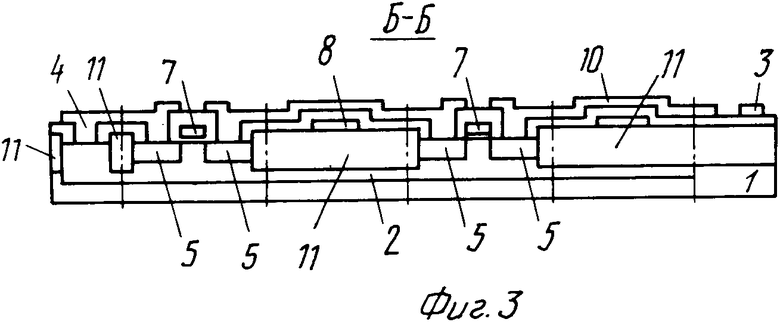

На фиг. 1 приведены топология и структура предлагаемого интегрального логического элемента; на фиг. 2 и 3 - разрезы А-А и Б-Б на фиг. 1.

Интегральный логический элемент содержит полупроводниковую подложку n-типа проводимости 1 с расположенной в ней областью "кармана" р-типа 2 и соединенные с ними соответственно металлические шину питания 3 и шину нулевого потенциала 4, две входные зоны Вх, содержащие n-канальные транзисторы 5 и р-канальные транзисторы 6, затворы которых объединены во входных поликремниевых шинах 7, выходную зону Вых с поликремниевой выходной шиной 9, соединенной с соответствующими электродами транзисторов, транзитную зону Транз с поликремниевой транзитной шиной 8, металлическую П-образную выходную шину 10. Выполненный по технологии "изопланар" элемент содержит разделительный диэлектрик 11. Штрихпунктирные линии обозначают границы зон.

Интегральный логический элемент работает следующим образом.

При подаче напряжения питания на шину 3 и сигналах логического 0 на шинах 7 р-канальные транзисторы открыты, а n-канальные закрыты, на шине 9 действует уровень логической 1. При действии различных по уровню сигналов на шинах 7 ситуация не изменяется, так как один из двух n-канальных транзисторов, соединенных последовательно, закрыт. Только при действии сигналов логической 1 на двух входах одновременно р-канальные транзисторы закрываются, а n-канальные открываются, и на выходе появляется уровень логического 0. Таким образом, устройство представляет собой двухвходовый логический элемент И-НЕ.

Предложенная конструкция позволила повысить основные характеристики интегрального логического элемента по сравнению с прототипом.

Введение в состав элемента транзитной (транзитных) шины и соответствующей зоны позволяет исключить обходные пути для межсоединений при обеспечении связей не между соседними элементами, а между элементами, стоящими через один, два и т.д. При этом достигается уменьшение площади, занимаемой элементом (приведенной) на 10-30% (в зависимости от числа введенных транзитов и числа элементов в составе БИС).

Взаимно перпендикулярное расположение поликремниевых и металлических шин и оригинальная конструкция металлической П-образной выходной шины позволили создать одинаковые по размерам и полностью топологически и электрически совместимые между собой по границам раздела (штрихпунктирные линии) структурно-топологические входные, выходную и транзитную зоны (примитивы). В результате появилась возможность произвольной перестановки зон (подстройки цоколевки выводов) в зависимости от предъявляемых требований. Такая топологическая инвариантность выводов позволит исключить излишние потери площади кристалла на изгибы сигнальных проводников, неизбежно возникающих при соединении типовых элементов с неперестраиваемой цоколевкой, и уменьшить их длину. В данном случае каждый последующий логический элемент при проектировании СБИС "пристыковывается" к предыдущему без зазоров под заданную предыдущим элементом цоколевку.

Кроме того, такая методология позволяет наращивать или сокращать при необходимости число входов и транзитов практически без ограничений введением или исключением дополнительных зон. В простейшем случае (отсутствие транзитных и наличие одной входной и выходной зон) элемент представляет собой КМОП-инвертор.

Перечисленные особенности позволяют уменьшить площадь, занимаемую блоками БИС на основе предлагаемого элемента, на 30-50% по сравнению с прототипом. Уменьшение длин связей обеспечивает повышение на 10-30% быстродействия микросхемы.

Предлагаемая регулярная конструкция элемента, собираемого из набора функциональных зон (примитивов), и методология легко адаптируются к САПР БИС, обуславливая снижение затрат на проектирование микросхем в целом.

За счет введения поликремниевой транзитной и металлической П-образной выходной шин, конструкции электрически и топологически совместимых зон получен положительный эффект, заключающийся в уменьшении занимаемой площади и повышении быстродействия элемента, а также снижении затрат на проектирование микросхем на его основе в целом.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1992 |

|

RU2022408C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1995 |

|

RU2094944C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1996 |

|

RU2115998C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1994 |

|

RU2079986C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1991 |

|

RU2006989C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1992 |

|

RU2062528C1 |

| БАЗОВЫЙ ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1667574A1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ-НЕ | 2000 |

|

RU2166837C1 |

| ИНТЕГРАЛЬНЫЙ КАСКАДНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ "ЯЙЛЕТКАН" | 2001 |

|

RU2215368C2 |

| ИНТЕГРАЛЬНЫЙ ПОЛЕВОЙ ТРАНЗИСТОР ШОТТКИ СО СТАТИЧЕСКОЙ ИНДУКЦИЕЙ | 2000 |

|

RU2183885C1 |

Использование: изобретение относится к вычислительной технике и интегральной электронике. Сущность изобретения: в интегральный логический элемент введены зона транзита, содержащая поликремниевую транзитную шину, и соединенная с поликремниевой выходной шиной металлическая П-образная выходная шина перпендикулярная поликремниевым шинам, причем расположенные между шинами питания и нулевого потенциала входные, выходная и транзитные зоны имеют одинаковые габаритные размеры и могут при необходимости взаимозаменяться в любом порядке вдоль элемента. 3 ил.

ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ, содержащий полупроводниковую подложку первого типа проводимости с расположенной в ней областью кармана второго типа проводимости и соединенные с ними соответственно металлическую шину питания и шину нулевого потенциала, две входные зоны, каждая из которых содержит расположенные в кармане транзистор первого типа проводимости и в подложке транзистор второго типа проводимости, затворы которых объединены и выполнены в виде общей входной поликремниевой шины, выходную зону, содержащую выходную поликремниевую шину, соединенную со стоками первого и второго транзисторов второго типа проводимости и первого транзистора первого типа проводимости, исток которого соединен со стоком второго транзистора первого типа проводимости, исток второго транзистора первого типа проводимости соединен с шиной нулевого потенциала, а истоки транзисторов второго типа проводимости соединены с шиной питания, отличающийся тем, что, с целью уменьшения занимаемой площади и повышения быстродействия элемента, а также снижения затрат на проектирование микросхем в целом, в него введена зона транзита, содержащая поликремниевую транзитную шину, и соединенная с поликремниевой выходной шиной металлическая П-образная выходная шина, перпендикулярная поликремниевым шинам, причем расположенные между шинами питания и нулевого потенциала входные, выходная и транзитная зоны взаимозаменяемы вдоль логического элемента.

| Пономарев М.Ф., Коноплев Б.Г | |||

| Конструирование и расчет микросхем и микропроцессоров | |||

| Учеб.пособие для вузов, М.: Радио и связь, 1986, рис.3.41. |

Авторы

Даты

1994-09-15—Публикация

1991-04-01—Подача