Каскадный интегральный логический модуль "ЯЙЛЕТКАН" относится к области вычислительной техники и интегральной электроники, а именно к логическим схемам, отличающимся по реализуемой логической операции, в частности схемам, в которых сигнал на выходе появляется при наличии входного сигнала только на одном входе.

Известен интегральный логический элемент (см. Bern Hocfflinger, Sie I. Lui and Branislav Vajdic, A Three - Dimentional CMOS Desigh Metodology, IEEE Transactions of Electron Devices, v. ED-31, N 2, 1984, fig.2), содержащий полупроводниковую подложку первого типа проводимости с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости, полупроводниковую область второго типа проводимости, расположенную над слоем разделительного диэлектрика и содержащую сток-истоковые области транзисторов первого типа проводимости, слои тонкого диэлектрика, металлическую шину питания, соединенную с истоковыми областями транзисторов первого типа проводимости, металлическую шину нулевого потенциала, расположенную над истоковой областью транзистора второго типа проводимости и соединенную с ней, а также полупроводниковой подложкой первого типа проводимости, две входные поликремнивые шины прямоугольной формы, являющиеся затворами транзисторов второго типа проводимости и расположенных над ними транзисторов первого типа проводимости, выходную металлическую шину, расположенную над областями элемента и соединенную со стоковыми областями транзисторов первого типа проводимости и стоковой областью транзисторов второго типа проводимости.

Недостатком известного интегрального логического элемента являются низкие функциональные возможности и сложность автоматизированного проектирования узлов на основе данного элемента, обусловленная фиксированным расположением входных и выходных шин, а также отсутствием транзитных шин.

Известен также интегральный логический элемент (см. Патент РФ 02115998, М. кл. Н 03 К 19/20; H 01 L 27/06, опубл. 20.07.98), содержащий полупроводниковую подложку первого типа проводимости с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости, полупроводниковую область второго типа проводимости, расположенную над слоем разделительного диэлектрика и содержащую сток-истоковые области транзисторов первого типа проводимости, слои тонкого диэлектрика, зону питания, содержащую металлическую шину питания, соединенную с истоковыми областями транзисторов первого типа проводимости, зону нулевого потенциала, содержащую металлическую шину нулевого потенциала, расположенную над истоковой областью транзистора второго типа проводимости и соединенную с ней, а также полупроводниковой подложкой первого типа проводимости, входную зону, содержащую транзистор первого типа проводимости, расположенный в полупроводниковой области второго типа проводимости над слоем разделительного диэлектрика, транзистор второго типа проводимости, расположенный в полупроводниковой подложке первого типа проводимости, входную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала, выполненную в виде буквы S в зеркальном отображении и являющуюся затвором транзистора первого типа проводимости, расположенного в полупроводниковой области второго типа проводимости под слоем разделительного диэлектрика, и затвором транзистора второго типа проводимости, расположенного в полупроводниковой подложке первого типа проводимости, выходную зону, содержащую выходную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала и выполненную в виде буквы S, выходную металлическую шину прямоугольной формы, расположенную над областями элемента перпендикулярно металлическим шинам питания и нулевого потенциала и соединенную с выходной поликремниевой шиной, а также со стоковыми областями транзисторов первого типа проводимости и стоковой областью транзистора второго типа проводимости, зону транзита, содержащую транзитную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала и выполненную в виде буквы S в зеркальном отображении, причем входные, выходная и транзитная зоны имеют одинаковые размеры, а условные границы входных зон, транзитной зоны, зоны питания и нулевого потенциала пересекают контактные окна, соединяющие металлическую шину питания и выходную металлическую шину с областями элемента.

Недостатками известного интегрального логического элемента являются низкие функциональные возможности, т.к. его нельзя использовать в сложных узлах для управления сложными процессами большой протяженности, а также сложность автоматизированного проектирования узлов на основе данного элемента и пониженное быстродействие, значительные потери тока и высокая помехоустойчивость.

Данные недостатки обусловлены конструктивными особенностями известного интегрального логического элемента.

Технической задачей предлагаемого изобретения является упрощение автоматизированного проектирования узлов, повышение функциональных возможностей с целью использования его для управления различными процессами любой протяженности, увеличение быстродействия при одновременном снижении помехоустойчивости и потерь тока.

Поставленный технический результат достигается тем, что модуль, содержащий входные и выходные звенья и шины, согласно изобретению, дополнительно содержит каскадно установленные логические модули, по меньшей мере три, каждый из которых включает исполняемый полупроводниковый переключатель, одну промежуточную входную шину и две промежуточные выходные шины управляемого сигнала и шину управляющего сигнала, связанную с упомянутым исполняемым полупроводниковым переключателем логического модуля, при этом упомянутые логические модули установлены каскадно, по меньшей мере, в виде двух каскадных звеньев, одно из которых является входным и одно выходным каскадными звеньями, причем в каждом последующем каскадном звене количество логических модулей равно количеству промежуточных выходных шин управляемого сигнала исполняемых полупроводниковых переключателей предыдущего каскадного звена, причем каждое каскадное звено содержит одну шину управляющего сигнала на все логические модули данного каскадного звена, а исполняемые полупроводниковые переключатели выходного каскадного звена соединяются с помощью исполняемых полупроводниковых ключей концевой выходной шины в комбинации И, ИЛИ-НЕ, ИЛИ, И-НЕ и т. д., обеспечивая один из вариантов логических схем, причем каждая выходная промежуточная шина управляемого сигнала очередного логического модуля в предыдущем каскадном звене соединена с входной промежуточной шиной управляемого сигнала последующего логического модуля последующего каскадного звена.

Между отличительными признаками и достигнутым техническим результатом существует следующая причинно-следственная связь.

В отличие от известных аналогов и прототипа выполнение каскадного интегрального логического модуля как минимум из двух каскадных звеньев, состоящих, по меньшей мере, из трех логических модулей, каждый из которых содержит исполняемый полупроводниковый переключатель, одну промежуточную входную и две промежуточные выходные шины управляемого сигнала и шину управляющего сигнала, связанную с упомянутым исполняемым полупроводниковым переключателем логического модуля в каскадном звене, позволит повысить его функциональные возможности, т.к. способно собирать любые логические схемы, т.е. реализовать полный набор неповторяющихся логических схем. Повышенные функциональные возможности каскадного интегрального логического модуля позволяют использовать его для управления различными процессами любой протяженности при незначительной потере тока и большой помехоустойчивости, поскольку независимо от каскадности (количества каскадных звеньев) в предлагаемом каскадном интегральном логическом модуле используются однородные элементы - логические модули, что также снижает сложность изделия и упрощает автоматизированное проектирование узлов, не повышает себестоимость.

По имеющимся у заявителя сведениям, совокупность существенных признаков заявляемого изобретения "Интегральный каскадный логический модуль "ЯЙЛЕТКАН" не известна из уровня техники, что позволяет сделать вывод о соответствии изобретения критерию "новизна".

По мнению заявителя, сущность заявляемого изобретения не следует главным образом из известного уровня техники, так как из него не выявляется вышеуказанное влияние на достигаемый технический результат - новое свойство объекта - совокупности признаков, которые отличают от прототипа заявляемое изобретение, что позволяет сделать вывод о соответствии изобретения "Интегральный каскадный логический модуль "ЯЙЛЕТКАН" критерию "изобретательский уровень".

Совокупность существенных признаков, характеризующих сущность изобретения, может быть многократно использована в производстве каскадных интегральных логических модулей с получением технического результата, заключающегося в невысокой себестоимости за счет упрощения автоматизированного проектирования узлов, повышении функциональных возможностей, увеличении быстродействия, что позволяет сделать вывод о соответствии изобретения "Интегральный каскадный логический модуль "ЯЙЛЕТКАН" критерию "промышленная применимость".

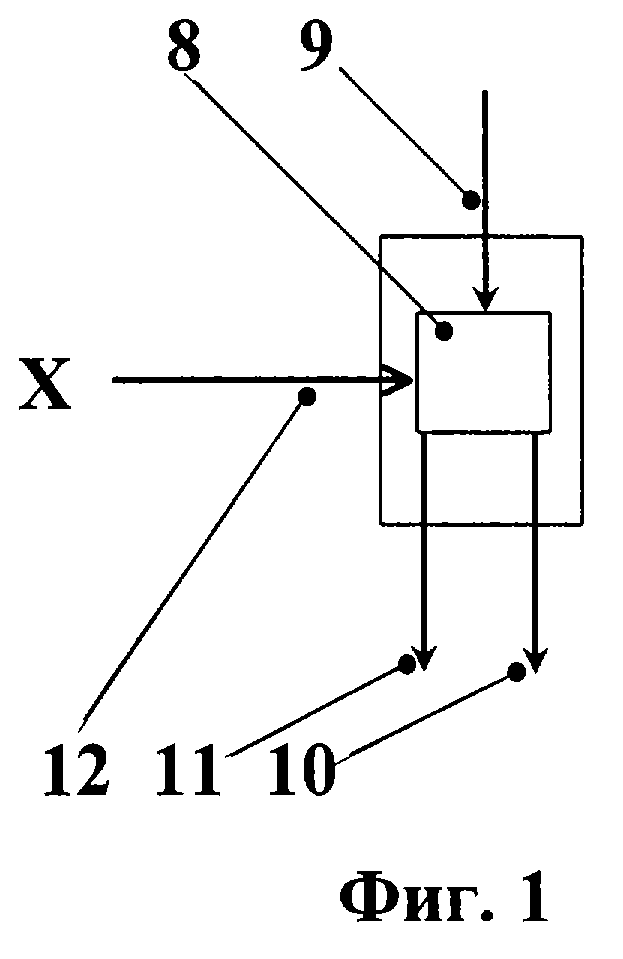

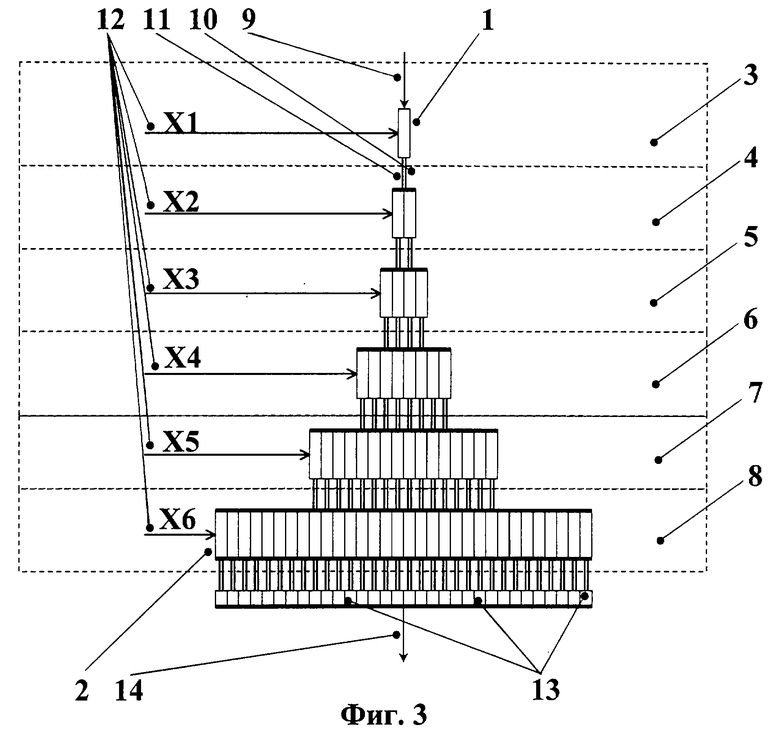

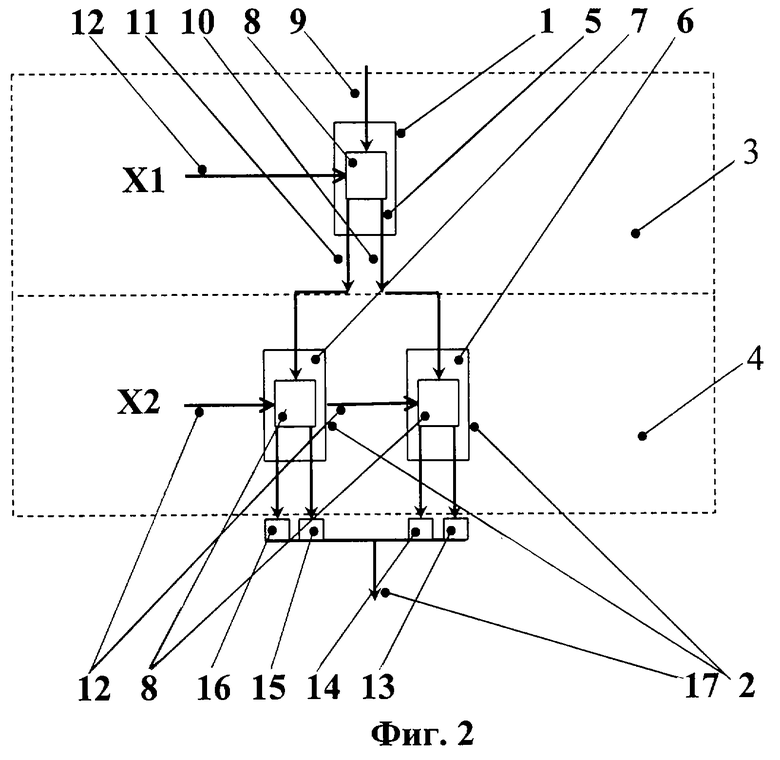

Сущность заявляемого изобретения поясняется примером конкретного получения предлагаемого интегрального каскадного логического модуля "ЯЙЛЕТКАН", где:

на Фиг.1 изображена составляющая часть интегрального каскадного логического модуля "ЯЙЛЕТКАН" - один логический модуль первого каскадного звена;

на Фиг. 2 изображен интегральный каскадный логический модуль, состоящий из двух каскадных звеньев, содержащих три логических модуля;

на Фиг. 3 изображен интегральный каскадный логический модуль, состоящий из шести каскадных звеньев, содержащих шестьдесят три логических модуля.

Интегральный каскадный логический модуль по первому примеру (Фиг.2) содержит одно входное каскадное звено 1 и одно выходное каскадное звено 2 ("Каскад - группа последовательно соединенных однотипных устройств", см. Политехнический словарь, третье издание, М.: Советская энциклопедия, 1989 г., стр. 214). В данном примере интегральный каскадный логический модуль состоит из минимального количества каскадных звеньев (двух каскадных звеньев) 3 и 4, которые одновременно являются входным каскадным звеном 1 и выходным каскадным звеном 2, и содержат три логических модуля 5, 6, 7, состоящих из однородных элементов, т.е. имеющих одинаковую структуру ("Модуль - унифицированный узел, оформленный конструктивно как самостоятельное изделие", см. Политехнический словарь, третье издание, М.: Советская энциклопедия, 1989 г., стр. 311). Первое каскадное звено 3, являющееся одновременно входным каскадным звеном 1, содержит один логический модуль 5, а два логических модуля 6 и 7 расположены во втором каскадном звене 4, являющемся одновременно выходным каскадным звеном 2. Каждый из логических модулей 5, 6, 7, содержит исполняемый полупроводниковый переключатель 8, одну промежуточную входную шину 9 и две промежуточные выходные шины 10, 11 управляемого сигнала и одну на все модули в одном каскадном звене шину 12 управляющего сигнала, связанную с упомянутым исполняемым полупроводниковым переключателем 8 логического модуля в каскаде, т. е. в данном интегральном каскадном логическом модуле каждое каскадное звено 3, 4 содержит одну шину 12 управляющего сигнала на все логические модули одного каскадного звена. В первом каскадном звене 3 по шине 12 управляющего сигнала на исполняемый полупроводниковый переключатель 8 поступают управляющие токи X1. Во втором каскадном звене 4 по шине 12 управляющего сигнала на исполняемый полупроводниковый переключатель 8 поступают управляющие токи Х2. Исполняемые полупроводниковые переключатели 8 соединяются в выходном каскадном звене 2 с помощью исполняемых полупроводниковых ключей 13, 14, 15, 16 концевой выходной шины 17 в комбинации И, ИЛИ-НЕ, ИЛИ, И-НЕ и т. д., обеспечивая один из вариантов логических схем. Каждая из выходных промежуточных шин 10, 11 очередного логического модуля в каждом каскадном звене соединена с одной входной промежуточной шиной 9 последующего логического модуля последующего каскадного звена.

Работа описанного выше интегрального каскадного логического модуля осуществляется следующим образом.

Обозначим наличие управляющих токов в шине 12 управляющего сигнала первого и второго каскадных звеньев соответственно логической единицей Х1=1 и Х2= 1, а отсутствие управляющих токов в шине 12 управляющего сигнала первого и второго каскадных звеньев соответственно логическим нулем Х1=0 и Х2= 0. Таким образом, при отсутствии управляющего сигнала на X1, т.е. Х1=0, управляющий ток на исполняемый полупроводниковый переключатель 8 логического модуля 5 первого каскадного звена 3 не поступает, а управляемый ток движется в цепи шин 9, 11. При наличии сигнала на X1, т.е. Х1=1, управляемый ток движется в цепи 9, 10. При отсутствии сигнала на Х2, т.е. Х2=0, управляющий ток на исполняемые полупроводниковые переключатели 8 логических модулей 6, 7 не поступает, а управляемый ток движется в цепи шин к исполняемому полупроводниковому ключу 16 или к исполняемому полупроводниковому ключу 14, в зависимости от наличия или отсутствия сигнала на X1, соответственно. При наличии сигнала на Х2, т.е. Х2=1, управляющий ток движется в цепи шин к исполняемому полупроводниковому ключу 15 или к исполняемому полупроводниковому ключу 13, в зависимости от наличия или отсутствия сигнала на X1, соответственно. Способами коммутации исполняемых полупроводниковых ключей 13, 14, 15, 16 можно показать следующие логические схемы.

Логический элемент И: осуществляется коммутацией исполняемого полупроводникового ключа 13, когда ток в цепи шин 9, 10 в направлении к исполняемому полупроводниковому ключу 13 появится только в случае Х1=1 и Х2=1.

Логический элемент ИЛИ: осуществляется коммутацией исполняемых полупроводниковых ключей 13, 14, 15, когда ток в цепи шин 9, 10 и 9, 11 в направлении к исполняемым полупроводниковым ключам 13, 14, 15 будет отсутствовать только в случае Х1=0 и Х2=0.

Логический элемент И-НЕ: осуществляется коммутацией исполняемых полупроводниковых ключей 14, 15, 16, когда ток в цепи шин 9, 10 и 9, 11 в направлении к исполняемым полупроводниковым ключам 14, 15, 16 будет отсутствовать только в случае Х1=1 и Х2=1.

Логический элемент ИЛИ-НЕ: осуществляется коммутацией исполняемого полупроводникового ключа 16, когда ток в цепи шин 9, 11 в направлении к исполняемому полупроводниковому ключу 16 будет появляться только в случае X1=0 и Х2=0.

Коммутируя исполняемые полупроводниковые ключи 13, 14, 15, 16, можно получить все известные логические бинарные схемы.

Интегральный каскадный логический модуль по второму примеру (Фиг.3) содержит одно входное каскадное звено 1 и одно выходное каскадное звено 2 соответственно первого каскадного звена и последнего каскадного звена. В данном примере интегральный каскадный логический модуль состоит из шести каскадных звеньев 3, 4, 5, 6, 7, 8, которые содержат шестьдесят три логических модуля, состоящих из однородных элементов, т.е. имеющих одинаковую структуру. Первое каскадное звено 3, являющееся одновременно входным каскадным звеном 1, содержит один логический модуль. Второе каскадное звено 4 содержит два логических модуля. Третье каскадное звено 5 содержит четыре логических модуля. Четвертое каскадное звено 6 содержит восемь логических модулей. Пятое каскадное звено 7 содержит шестнадцать логических модулей. Шестое каскадное звено 8, которое одновременно является и выходным каскадным звеном 2, содержит тридцать два логических модуля. Каждый из логических модулей содержит исполняемый полупроводниковый переключатель, одну промежуточную входную шину 9 и две промежуточные выходные шины 10, 11 управляемого сигнала и шину 12 управляющего сигнала, связанную с упомянутым исполняемым полупроводниковым переключателем логических модулей в каскадном звене. Каждый из шести каскадных звеньев 3, 4, 5, 6, 7, 8 содержит одну шину 12 управляющего сигнала на все логические модули данного каскадного звена.

В первом каскадном звене 3 по шине 12 управляющего сигнала на исполняемый полупроводниковый переключатель логического модуля поступают управляющие токи X1. Во втором каскадном звене 4 по шине 12 управляющего сигнала на исполняемый полупроводниковый переключатель каждого логического модуля поступают управляющие токи Х2. В третьем каскадном звене 5 по шине 12 управляющего сигнала на исполняемый полупроводниковый переключатель каждого логического модуля поступают управляющие токи Х3. В четвертом каскадном звене 6 по шине 12 управляющего сигнала на исполняемый полупроводниковый переключатель каждого логического модуля поступают управляющие токи Х4. В пятом каскадном звене 7 по шине 12 управляющего сигнала на исполняемый полупроводниковый переключатель каждого логического модуля поступают управляющие токи Х5. В шестом каскадном звене 8 по шине 12 управляющего сигнала на исполняемый полупроводниковый переключатель каждого логического модуля поступают управляющие токи Х6. Исполняемые полупроводниковые переключатели коммутируются в выходном каскадном звене 2 с помощью исполняемых полупроводниковых ключей 13 к концевой выходной шине 14 в различных комбинациях, обеспечивая один из 1,8•1019 вариантов логических схем. Каждая из выходных промежуточных шин 10, 11 очередного логического модуля в каждом каскадном звене соединена, как и в первом примере, с входной промежуточной шиной последующего логического модуля следующего каскадного звена.

Работа описанного выше модуля осуществляется аналогично первому примеру.

Предлагаемое изобретение "Интегральный каскадный логический модуль" позволит значительно упростить автоматизированное проектирование узлов, повысить функциональные возможности модуля, использовать его для управления различными процессами любой протяженности, увеличить быстродействие при одновременном снижении помехоустойчивости и потерь тока.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКАДНЫЙ ИНТЕГРАЛЬНЫЙ МОДУЛЬ ДИНАМИЧЕСКОЙ ПАМЯТИ "СИБЛ" | 2001 |

|

RU2218611C2 |

| КЛЮЧЕВОЙ ЭЛЕМЕНТ С ДИАГНОСТИКОЙ В РЕАЛЬНОМ ВРЕМЕНИ | 2014 |

|

RU2568655C1 |

| КЛЮЧЕВОЙ ЭЛЕМЕНТ С ВЫСОКИМ УРОВНЕМ БЕЗОПАСНОСТИ | 2014 |

|

RU2573891C1 |

| ПРИЕМНИК СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1997 |

|

RU2118054C1 |

| УСТРОЙСТВО КОНТРОЛЯ И УПРАВЛЕНИЯ СИГНАЛАМИ РЕЛЕЙНОЙ ЗАЩИТЫ И ПРОТИВОАВАРИЙНОЙ АВТОМАТИКИ | 2012 |

|

RU2479903C1 |

| СХЕМА СЧИТЫВАНИЯ СИГНАЛОВ ИЗ ЯЧЕЕК МАТРИЦЫ ФОТОДЕТЕКТОРОВ | 2008 |

|

RU2356177C1 |

| СИСТЕМА БЕСПЕРЕБОЙНОГО ЭЛЕКТРОПИТАНИЯ | 1992 |

|

RU2037249C1 |

| Тяговый инвертор электрогрузовика | 2024 |

|

RU2825486C1 |

| ПОЛУПРОВОДНИКОВОЕ КЛЮЧЕВОЕ УСТРОЙСТВО | 2003 |

|

RU2268545C2 |

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в расширении функциональных возможностей. Интегральный каскадный логический модуль содержит одно входное и одно выходное звенья, являющиеся каскадными звеньями (КЗ) соответственно первого и последнего каскадов (К), и выполнен в виде как минимум из двух К. Каждый К состоит, по меньшей мере, из трех интегральных логических модулей (ИЛМ), каждый из которых содержит исполняемый полупроводниковый переключатель (ИПП). ИПП имеет одну промежуточную входную шину и две промежуточные выходные шины управляемого сигнала и шину управляющего сигнала. Каждый К содержит одну шину управляющего сигнала на все ИЛМ данного К. Каждая выходная промежуточная шина очередного ИЛМ в каждом К соединена с входной промежуточной шиной ИЛМ следующего К. При этом ИПП выходного КЗ посредством исполняемых полупроводниковых ключей коммутируются к концевой выходной шине. 3 ил.

Интегральный каскадный логический модуль, содержащий одно входное и одно выходное звенья, являющиеся каскадными звеньями соответственно первого и последнего каскадов, и выполненный в виде как минимум из двух каскадов, которые состоят, по меньшей мере, из трех интегральных логических модулей, каждый из которых содержит исполняемый полупроводниковый переключатель, который имеет одну промежуточную входную шину и две промежуточные выходные шины управляемого сигнала и шину управляющего сигнала, причем каждый каскад содержит одну шину управляющего сигнала на все интегральные логические модули данного каскада, а каждая выходная промежуточная шина очередного интегрального логического модуля в каждом каскаде соединена с входной промежуточной шиной интегрального логического модуля следующего каскада, отличающийся тем, что исполняемые полупроводниковые переключатели выходного каскадного звена посредством исполняемых полупроводниковых ключей коммутируются к концевой выходной шине.

| Логический элемент | 1986 |

|

SU1401596A1 |

| Многофункциональный логический модуль | 1986 |

|

SU1405109A1 |

| GB 1429717, 24.03.1976 | |||

| Отопительная панель | 1987 |

|

SU1523859A1 |

| ХОРОВИЦ П | |||

| и др | |||

| Искусство схемотехники | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| - М.: Мир, 1993, с.245, рис.9.53. | |||

Авторы

Даты

2003-10-27—Публикация

2001-06-26—Подача