Изобретение относится к радиотехнике и может быть использовано в системах связи, применяющих широкополосные псевдослучайные сигналы.

Наиболее близким по технической сущности к предложенному является устройство поиска псевдослучайных последовательностей, содержащее перемножитель, генератор псевдослучайных последовательностей (ПСП), решающий блок, генератор тактовых импульсов, сумматор, запоминающий блок, буферный регистр, блок управления, регистр состояния генератора ПСП, коммутатор и ключ.

Целью изобретения является уменьшение времени поиска псевдослучайных последовательностей.

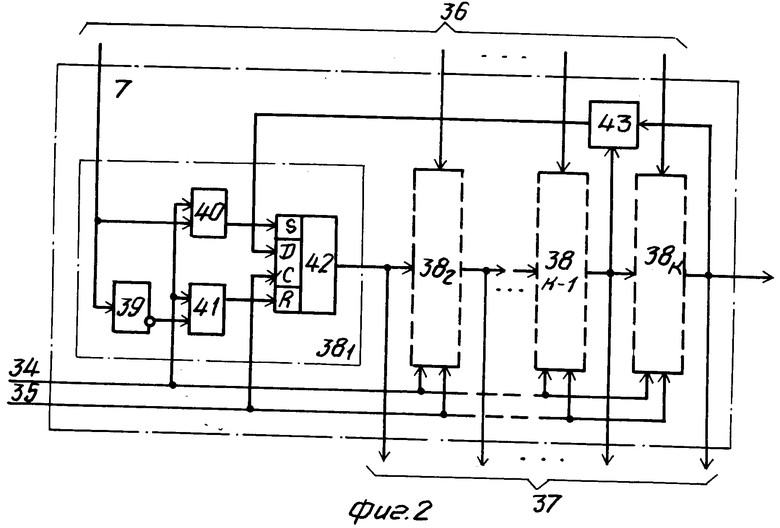

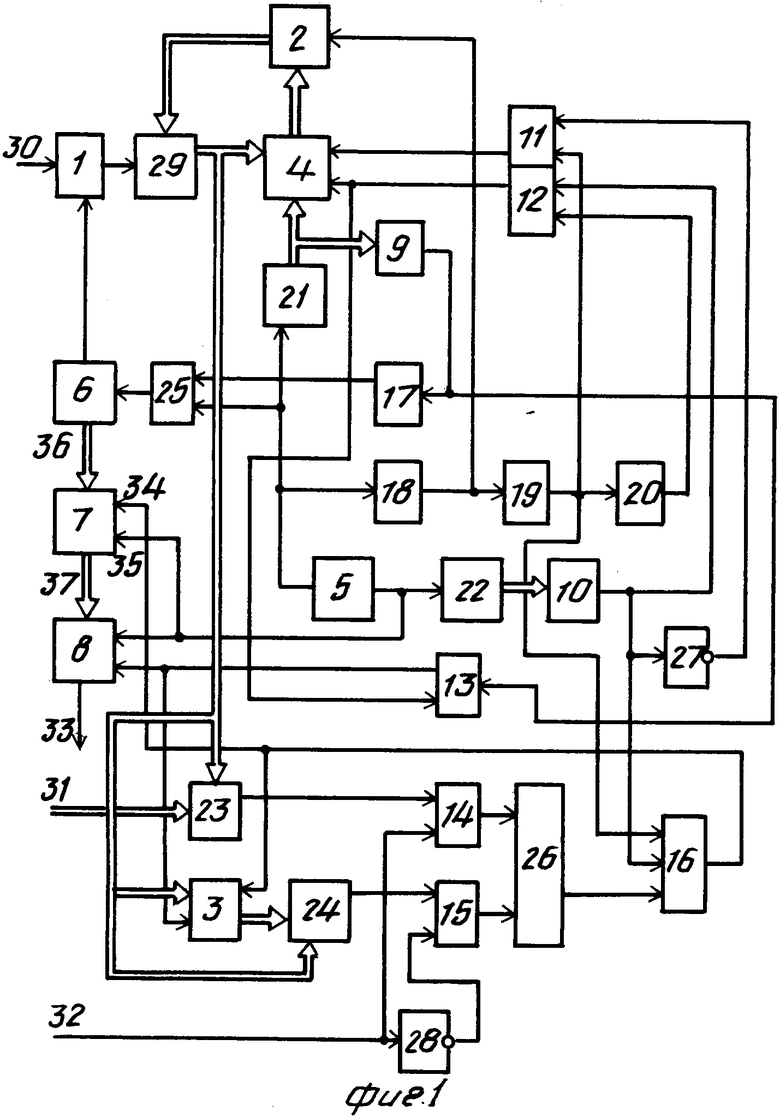

На фиг. 1 приведена структурная схема устройства поиска псевдослучайных последовательностей; на фиг. 2 - структурная схема генератора псевдослучайных последовательностей.

Устройство поиска псевдослучайных последовательностей (см. фиг. 1) содержит перемножитель 1, первый буферный регистр 2, второй буферный регистр 3, блок памяти 4, генератор 5 тактовых импульсов, первый, второй, третий генераторы 6-8 псевдослучайных последовательностей, первый и второй дешифраторы 9, 10, шестой, четвертый, третий, первый, второй, пятый элементы И 11-16, формирователь 17 импульсов, элементы 18-20 задержки с первого по третий соответственно, первый и второй счетчики 21, 22 импульсов, первый и второй блоки 23, 24 сравнения, второй и первый элементы ИЛИ 25, 26, первый и второй элементы НЕ 27, 28, сумматор 29, информационный вход 30, группу 31 установочных входов, вход 32 управления сигнала, выход 33, вход 34 записи блока 7, тактовый вход 35 блока 7, информационный вход и выход - 36, 37 блока 7.

Генератор псевдослучайных последовательностей 7 (см. фиг. 2) содержит группу 381-38К триггерных разрядов, в каждый из которых входят элемент НЕ 39, первый и второй элементы И 40, 41, триггер 42.

Устройство реализует два принципа:

постоянный поиск истинного значения (фазы) входной псевдослучайной последовательности (ПСП) и подстройка под эту фазу собственной, местной ПСП в моменты времени, кратные периоду принимаемой ПСП;

возможность принятия решения как по "жесткому" принципу (анализируется превышение некоторого наперед заданного порога числом элементов проверочной и принимаемой ПСП) и по "мягкому" принципу (выявлением максимального числа совпадений принимаемых элементов входной ПСП и элементов одной из проверочных ПСП).

В обоих случаях принятие решения сопровождается установкой внутренней ПСП в синфазное состояние с принимаемой ПСП в конце каждого интервала анализа.

Устройство работает следующим образом:

В исходном состоянии все ячейки блока памяти 4 обнулены, счетчики 21 и 22; регистр 3 - в нулевом состоянии, триггеры генератора 8 - в нулевом состоянии; в триггеры генератора 6 записана в любой фазе ПСП, по структуре аналогичная входной. Остальные блоки - в произвольном состоянии. Цепи начальной установки на фиг. 1 не показаны. Возможно и произвольное начальное состояние всех блоков устройства; в этом случае синфазность достигается после первого цикла анализа. На выходе 32 - управляющий сигнал. Он определяет режим работы - "мягкий" или "жесткий". Длительность цикла анализа равна периоду входной ПСП.

На фиг. 1 не показано также устройство синхронизации, обеспечивающее синхронность частоты сигналов с второго выхода генератора 5 и частоты входных информационных сигналов. Сигналы на первом и втором выходах генератора 5 имеют соответственно частоты l.n.fo и fo, где n - число элементов в ПСП, а l - произвольное положительное целое число. Все генераторы 6-8 вырабатывают ПСП одной и той же структуры.

Высокая частота на первом выходе генератора 5 вызывает формирование в генераторе ПСП (ГПСП) 6 ПСП в сжатом масштабе времени в сравнении с входной ПСП (для простоты примем в дальнейшем l= = 1). Работа устройства несколько отличается в различных ситуациях, из которых следует выделить (учитывая n - число символов ПСП):

работа во всех тактах опорной частоты, кроме последнего, и во всех тактах работы частоты fo, кроме последнего;

работа в последнем такте опорной частоты, во всех тактах частоты f1, кроме последнего;

работа во всех тактах опорной частоты, кроме последнего, в последнем, n-м такте частоты fo;

работа в последнем такте опорной частоты и в последнем также частоты fo.

Рассмотрим по отдельности работу устройства во всех ситуациях, например при "жестком" принятии решения о фазе ПСП (при этом сигнал на входе 32 постоянно имеет "единичное" значение ).

1. Тактовый импульс опорной частоты сдвигает ПСП в блоке 6. Производится перемножение ПСП из блока 6 с ПСП на входе 30 (ее элементом). Блок 1 может быть выполнен, например, на элементе типа "Равнозначность". Сигнал с блока 1 поступает на сумматор 29. Счетчик 21 задает адрес ячейки памяти блока 4, в которой накапливаются числа совпадений входной ПСП с соответствующими циклическими сдвигами внутренней ПСП. При соответствующем состоянии счетчика 21 на выходах блока 4 формируется код предыдущего числа совпадений; тактовым импульсом, задержанным на элементе 18, содержимое блока памяти переписывается в регистр 2; на выходе сумматора появляется текущее число совпадений. Этот код, задержанный на элементе 19, записывается в ту же ячейку блока 4. Задним фронтом тактового импульса счетчик 21 инкрементируется. Так происходит накопление данных для анализа.

2. Данная ситуация отличается от предыдущей тем, что при содержимом счетчика 21 n - 1 - последнем состоянии - срабатывает дешифратор 9; его сигнал поступает на формирователь импульсов, формирующий задержанный импульс, после окончания всех процессов, описанных в первой ситуации; этот импульс производит дополнительный сдвиг в генераторе 6, образуя в следующем цикле высокой частоты перемножение следующего элемента входной ПСП на новые циклические сдвиги местной ПСП. Так реализуются суммы чисел - при представлении входной ПСП в виде {x1,x2,...,xn}, а опорной ПСП - в виде [a1,a2,..., an} : в первой ячейке блока памяти 4 - {x1.a1 + x2˙a2 + ... xn˙an}, во второй ячейке блока памяти 4 - {x1˙a2 + x2˙a3 + ... + xn˙an} и т.д., в n-й ячейки блока памяти - {x1˙an + +x2a1 + ... + xn˙an-1}.

3. После каждого n-го такта опорной частоты инкрементируется содержимое счетчика 22, так как формируется импульс на выходе (втором) генератора 5. Этим же импульсом сдвигаются ПСП в блоках 7 и 8 (в первом цикле анализа содержимое разрядов блока 8 нулевое, т.е. в первом цикле на выходе 33 нулевой сигнал). После очередного импульса с второго выхода генератора 5 счетчик 22 переходит в состояние n - 1, срабатывает дешифратор 10 и устройство переходит к третьей ступени.

При этом аналогично осуществляется перемножение, заканчивая формирование требуемых сумм (на данном этапе осуществляется формирование последних слагаемых этих сумм). Аналогично сигналом с выхода элемента 18 предыдущее значение соответствующей суммы записывается в регистр 2; на выходе сумматора 29 формируется окончательное значение суммы; это значение сравнивается с порогом (сравнения производятся практически всегда, но лишь на n-м также частоты fo открыт элемент И 16. Если значение суммы больше порога, то сигнал с блока сравнения 23 проходит через элементы И 14, ИЛИ 26 и при появлении импульса с элемента задержки 19 - на элемент 16, записывая опорную ПСП в соответствующей фазе в генератор 7. Одновременно производится запись данной суммы в регистр 3, однако в "жестком" режиме это значения не имеет. Сигналом с выхода элемента задержки 20 через элемент И 12 производится сброс данной ячейки блока 4. В данной ситуации записи в эту ячейку нет, так как элемент И 11 закрыт сигналом с выхода НЕ 27.

Если в какой-либо следующий такт опорной частоты вновь будет зафиксировано превышение суммой порога, аналогично производится запись новой фазы опорной ПСП в блок 7.

4. В данной ситуации анализируется последняя сумма (n-й интервал опорной частоты и n-й интервал частоты fo). Осуществляется та же последовательность действий, что и в третьей ситуации, но, кроме того, аналогично ситуации второй производится формирование дополнительного импульса на сдвиг опорной частоты в блоке 6 (что обеспечивается формирователем 17); кроме того, сигналом с выхода элемента И 12 через открытый положительным сигналом с дешифратора 9 элемент И 12 производится запись выбранной фазы опорной частоты ПСП, записанной в блоке 7, в блок 8, а регистр 3 сбрасывается в "нуль".

В дальнейшем задним фронтом n-го импульса опорной частоты счетчик 21 переводится в "нуль", а следующим тут же импульсом частоты fo переводится в нулевое состояние счетчик 22; устройство переходит в исходное состояние, отличающееся от начального тем, что в генераторе 8 записана в нужной фазе ПСП, которая в дальнейшем будет сдвигаться в фазу с входной ПСП по тактовым импульсам частоты fo.

Аналогично в следующем цикле анализа вновь производится анализ фазы, описанный выше и в случае сбоя синхронизации в конце очередного цикла производится подстройка. Если сбоя фазы не произошло, то в регистр 8 будет записана ПСП в той же фазе, в которой она уже находится в нем, так что синфазность сохраняется. Устройство, таким образом, позволяет постоянно "отслеживать" фазу входной ПСП и подстраивать к ней внутреннюю фазу.

В "мягком" режиме принятия решения отличия следующие:

В данном режиме сигнал на входе 32 должен постоянно находиться на низком уровне. При этом отключается элемент И 14 и включается элементом 15 совокупность блоков 3 и 24, которая работает следующим образом.

На последнем, n-м также частоты fo с каждым тактом опорной частоты текущая сумма по всем элементам данного циклического сдвига опорной и входной ПСП сравнивается с максимальной из предыдущих (в начале данной ситуации - с нулевой) суммой. Если текущая сумма больше максимальной из предыдущих, сигнал с блока сравнения 24 происходит через элементы И 15, ИЛИ 26, И 16 и записывает данную фазу опорной частоты ПСП в блок 7, и текущую сумму - в регистр 3; так продолжается в течение всего последнего цикла счета счетчиком 21. После окончания в ситуации 4 аналогично производится запись выбранной фазы опорной ПСП в блок 8 и сброс регистра 2, подготавливающий его к следующему циклу работы. Таким образом, в данном режиме решение принимается "мягкое", т.е., выбирается на фаза ПСП, для которой сумма больше всех остальных сумм вне зависимости от конкретного порога - статистически наиболее вероятное решение.

Генератор ПСП работает следующим образом (см. фиг. 2, где приведен частный пример генератора ПСП на основе сдвигающего регистра, генерирующего ПСП максимальной длины). При числе разрядов регистра, равном К, на выходе блока 38К формируется ПСП длиной n = 2к - 1 символов. В общем случае в зависимости от числа разрядов 38 для получения ПСП максимальной длины подключаются вполне определенные выходы блоков 38 к входам сумматора по модулю "два" 43. Запись ПСП в любой фазе в генератор ПСП осуществляется подачей соответствующих потенциалов на входы группы 36 и подачей сигнала записи на вход 34; при этом соответствующие триггеры 42 устанавливаются в состояния, соответствующие сигналам на входах 36. Подачей тактовых импульсов на вход 35 осуществляется формирование на выходе 38К ПСП в последовательном виде, а на совокупности выходов 37 - ПСП - в параллельной форме.

Таким образом, предложенное устройство позволяет путем постоянного слежения за фазой входной последовательности осуществлять быструю подстройку к этой фазе фазы местной последовательности; кроме того, устройство расширяет область применения, позволяя работать как в "жестком", так и в "мягком" режиме принятия решения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| Устройство для передачи информации шумоподобными сигналами | 1984 |

|

SU1256239A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1991 |

|

RU2020554C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840275A1 |

| Устройство передачи информации шумоподобными сигналами | 1984 |

|

SU1352665A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОПОЛНЕНИЯ МНОЖЕСТВА | 1990 |

|

RU2022353C1 |

| Устройство для передачи и приема информации | 1984 |

|

SU1269174A1 |

| Устройство для приема частотно-манипулированных сигналов | 1984 |

|

SU1197129A1 |

| Адаптивное телеметрическое устройство | 1989 |

|

SU1635206A1 |

| Цифровой генератор функций | 1977 |

|

SU622070A1 |

Использование: в радиотехнике, в системах связи, применяющих широкополосные псевдослучайные сигналы. Сущность изобретения: устройство поиска псевдослучайных последовательностей (ПСП) содержит перемножитель 1, первый, второй буферные регистры 2, 3, блок памяти 4, генератор 5 тактовых импульсов, генераторы ПСП 6 - 8, дешифраторы 9, 19, элементы И 11 - 16, формирователи импульсов 17, элементы задержки 18 - 20, счетчики 21, 22 импульсов, блоки сравнения 23, 24, элементы ИЛИ 25, 26, элементы НЕ 27, 28, сумматор 29. Цель изобретения - уменьшение времени поиска псевдослучайных последовательностей. 2 ил.

УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащее последовательно соединенные перемножитель, к одному из входов которого подключен выход первого генератора псевдослучайных последовательностей (ПСП), сумматор, блок памяти и первый буферный регистр, выход которого соединен с другим входом сумматора, генератор тактовых импульсов (ТИ), первый блок сравнения и второй буферный регистр, отличающееся тем, что, с целью уменьшения времени поиска псевдослучайных последовательностей, введены дешифраторы, элементы И, второй и третий генераторы ПСП, формирователь импульсов, элементы задержки, счетчик импульсов, второй блок сравнения, элементы ИЛИ и элементы НЕ, при этом выходы сумматора соединены с информационными входами второго буферного регистра и с первой группой входов первого и второго блоков сравнения, выходы которых соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены с входами первого элемента ИЛИ, вторая группа входов первого блока сравнения является группой установочных входов устройства, а вторая группа входов второго блока сравнения соединена с выходами второго буферного регистра, первый выход генератора ТИ соединен с входом первого элемента задержки, счетным входом первого счетчика импульсов и первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом первого генератора ПСП, группа выходов которого соединена с информационными входами второго генератора ПСП, группа выходов которого соединена с информационными входами третьего генератора ПСП, выход которого является выходом устройства, второй выход генератора ТИ соединен со счетным входом второго счетчика импульсов и с тактовыми входами второго и третьего генераторов ПСП, выходы первого счетчика импульсов соединены с адресными входами блока памяти и входами первого дешифратора, выход которого соединен с первым входом третьего элемента И и с входом формирователя импульсов, выход которого соединен с вторым входом второго элемента ИЛИ, выходы второго счетчика импульсов соединены через второй дешифратор с первыми входами четвертого и пятого элементов И и с входом первого элемента НЕ, выход которого соединен с первым входом шестого элемента И, выход которого соединен с входом записи блока памяти, с входом сброса которого соединены выход четвертого элемента И и второй вход третьего элемента И, выход которого соединен с входом записи третьего генератора ПСП и входом сброса второго буферного регистра, выход первого элемента задержки соединен с входом второго элемента задержки и входом записи первого буферного регистра, выход второго элемента задержки соединен с вторыми входами пятого и шестого элементов И и входом третьего элемента задержки, выход которого соединен с вторым входом четвертого элемента И, выход первого элемента ИЛИ через пятый элемент И соединен с входами записи второго буферного регистра и второго генератора ПСП, причем второй вход первого элемента И соединен через второй элемент НЕ с вторым входом второго элемента И и является входом управляющего сигнала устройства.

| Устройство поиска псевдослучайных последовательностей | 1982 |

|

SU1104677A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-09-30—Публикация

1990-12-13—Подача