Изобретение относится к электросвязи и может использоваться в цифровых системах и сетях связи.

Цель изобретения - повышение помехоустойчивости устройства.

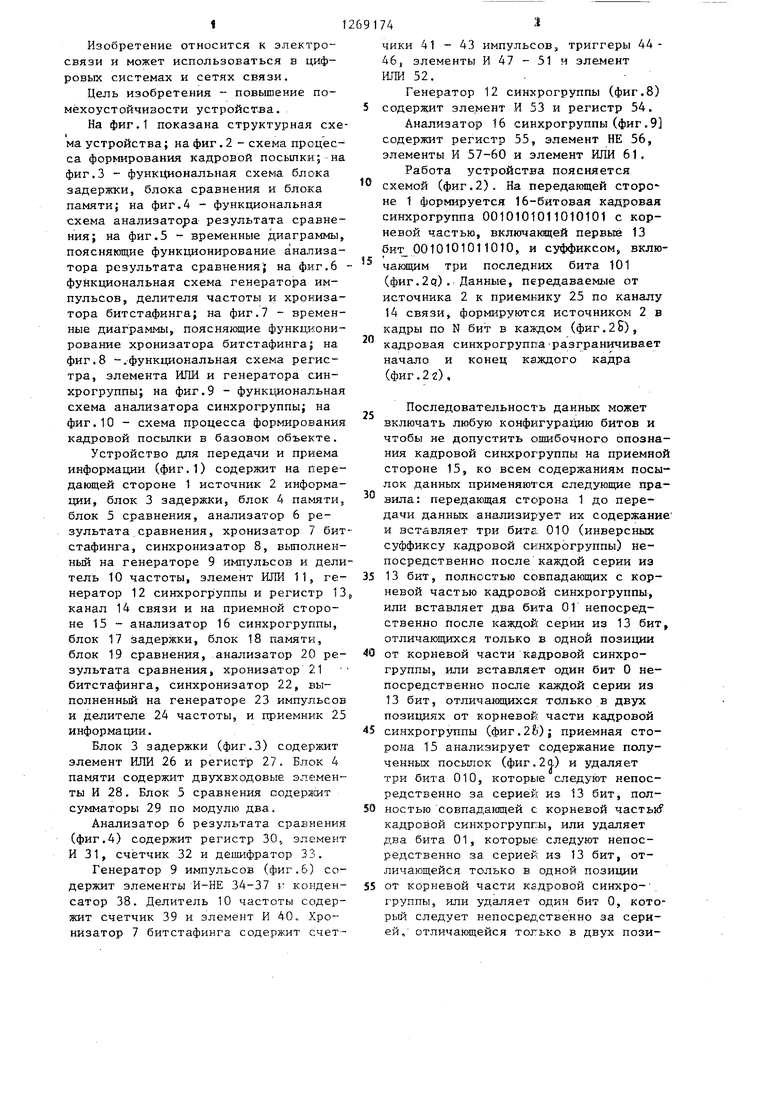

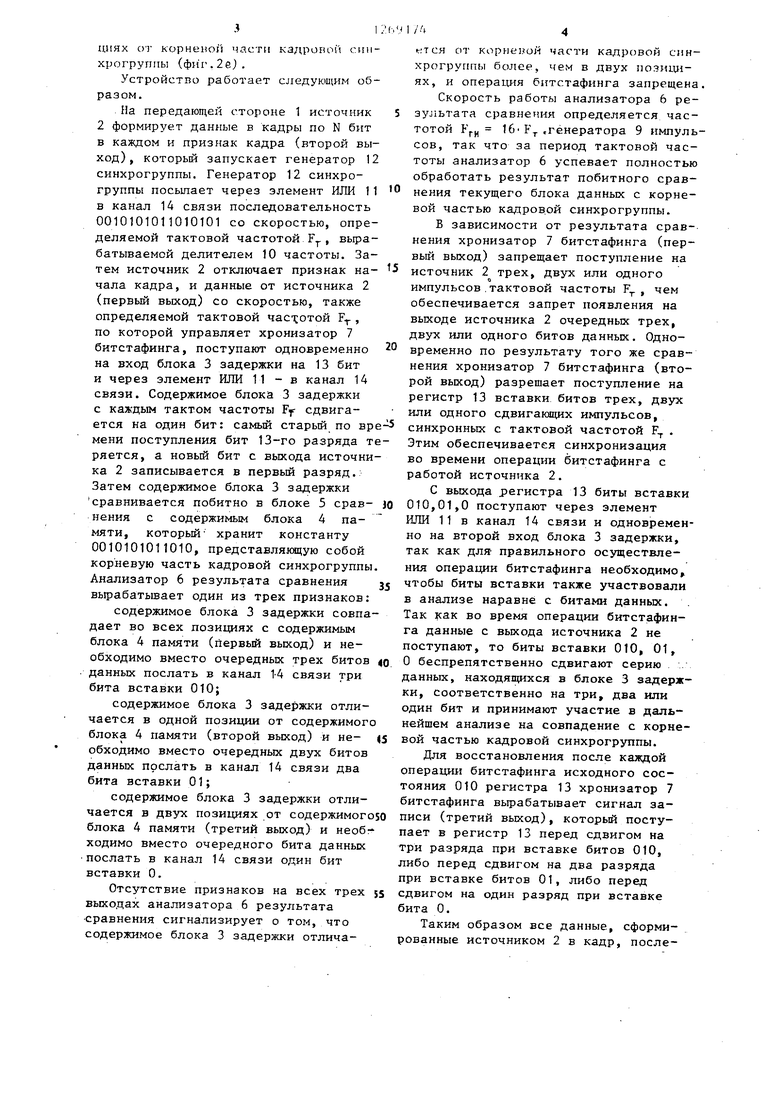

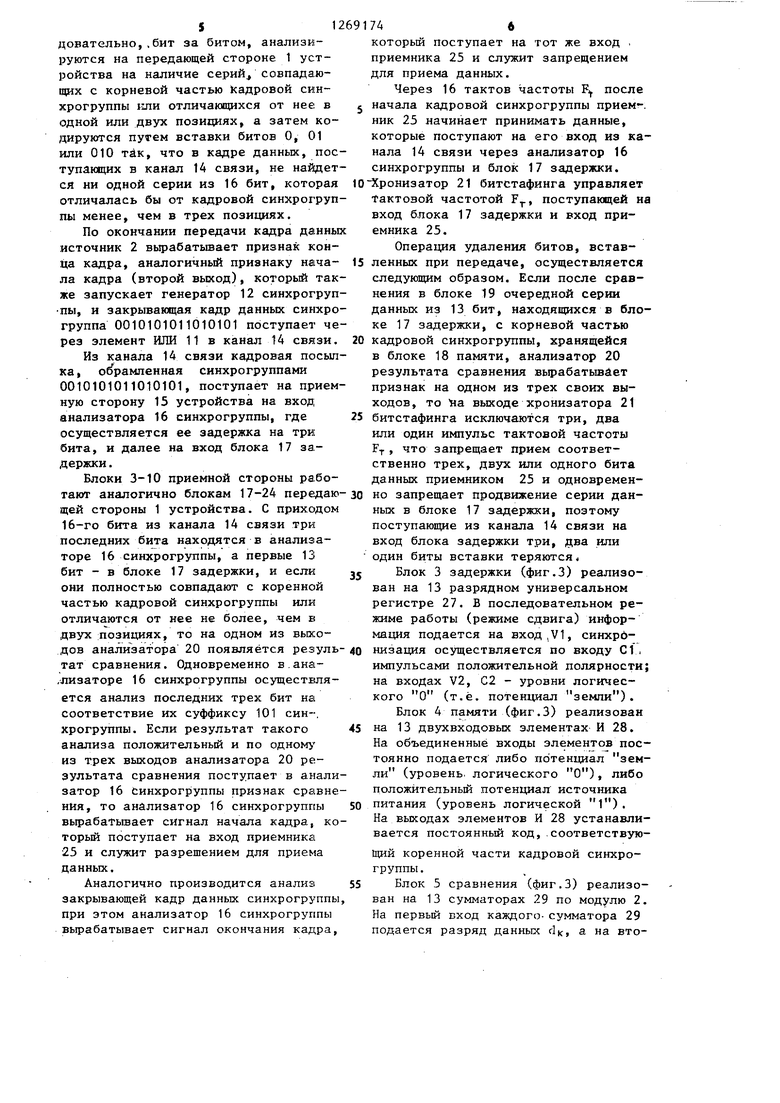

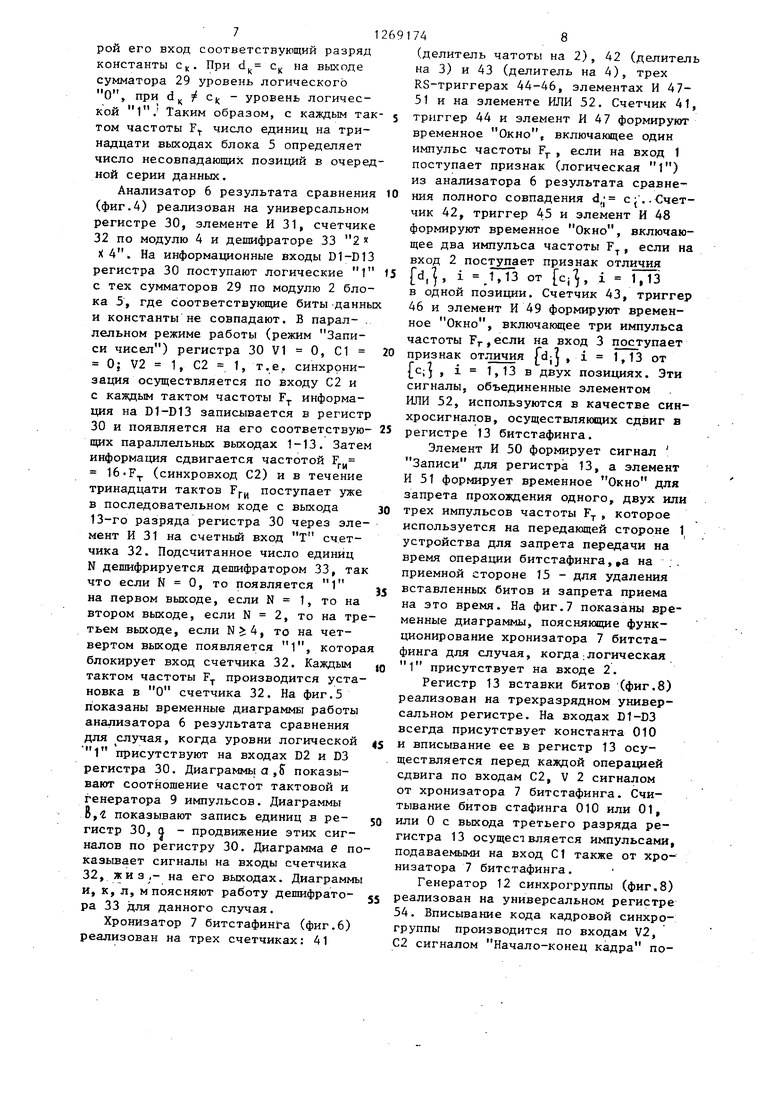

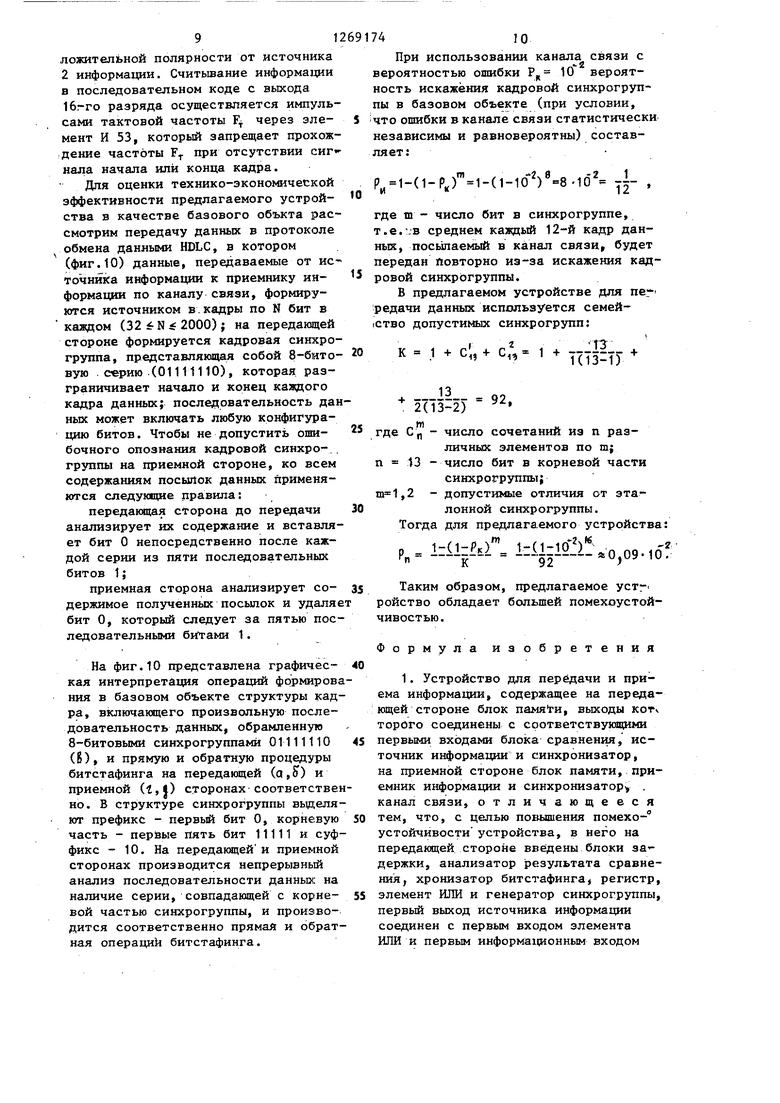

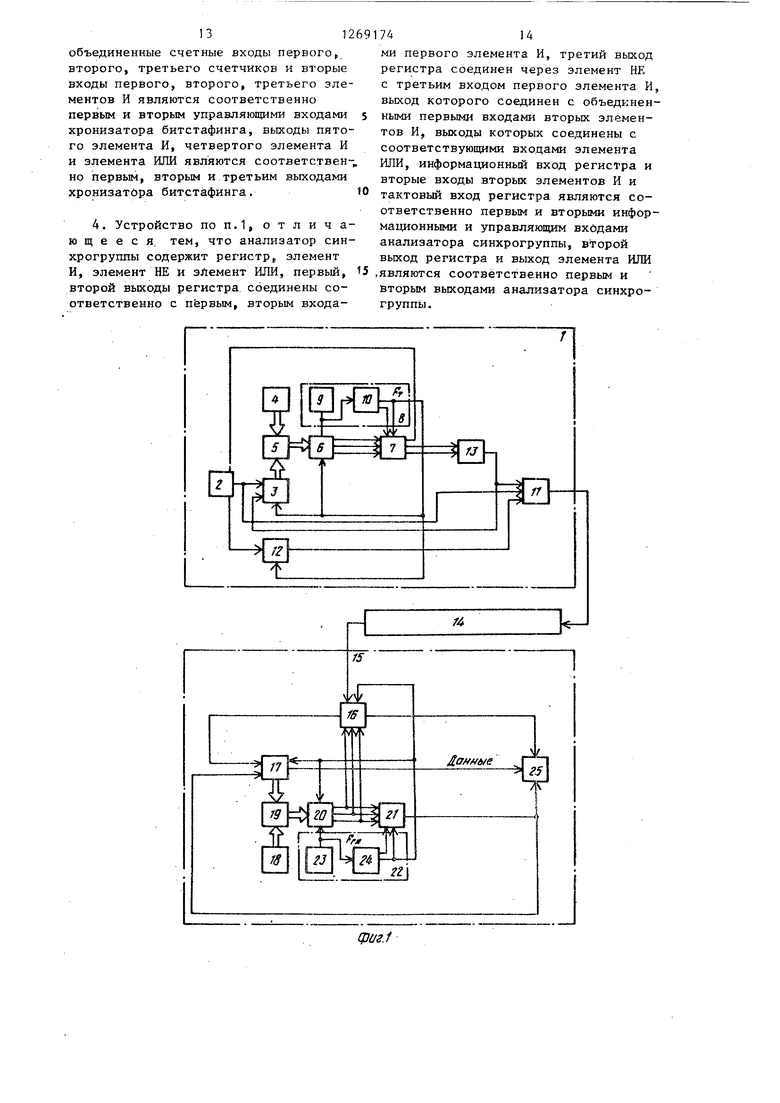

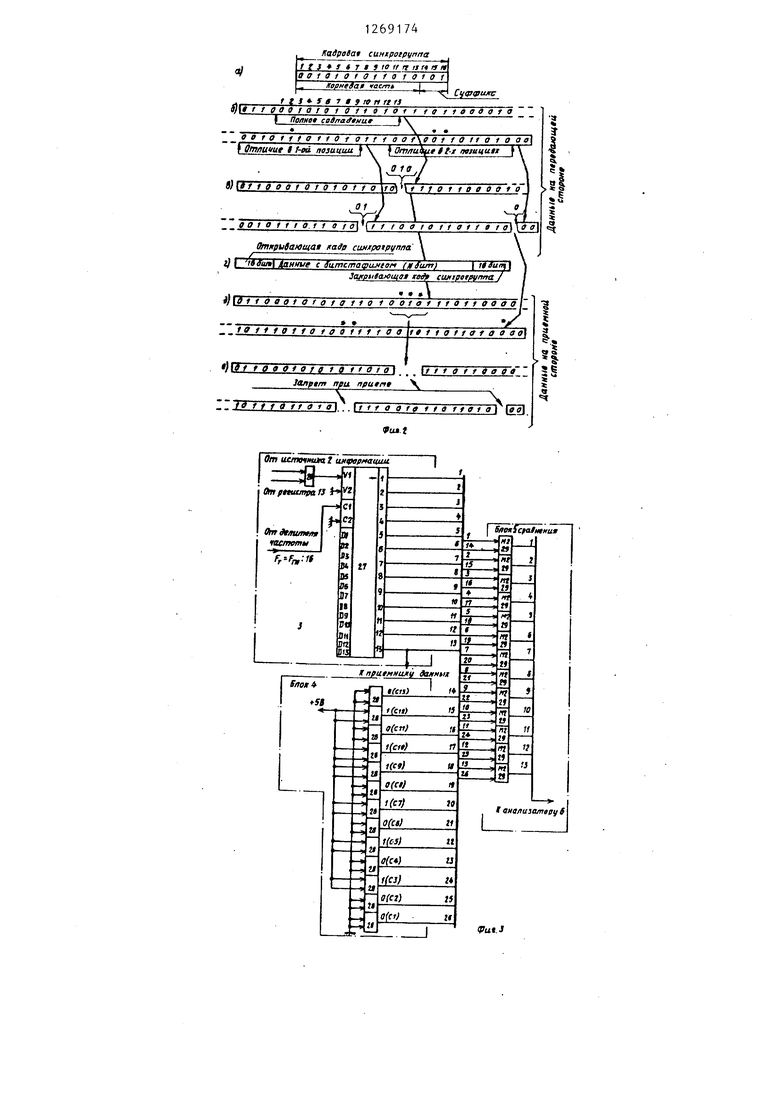

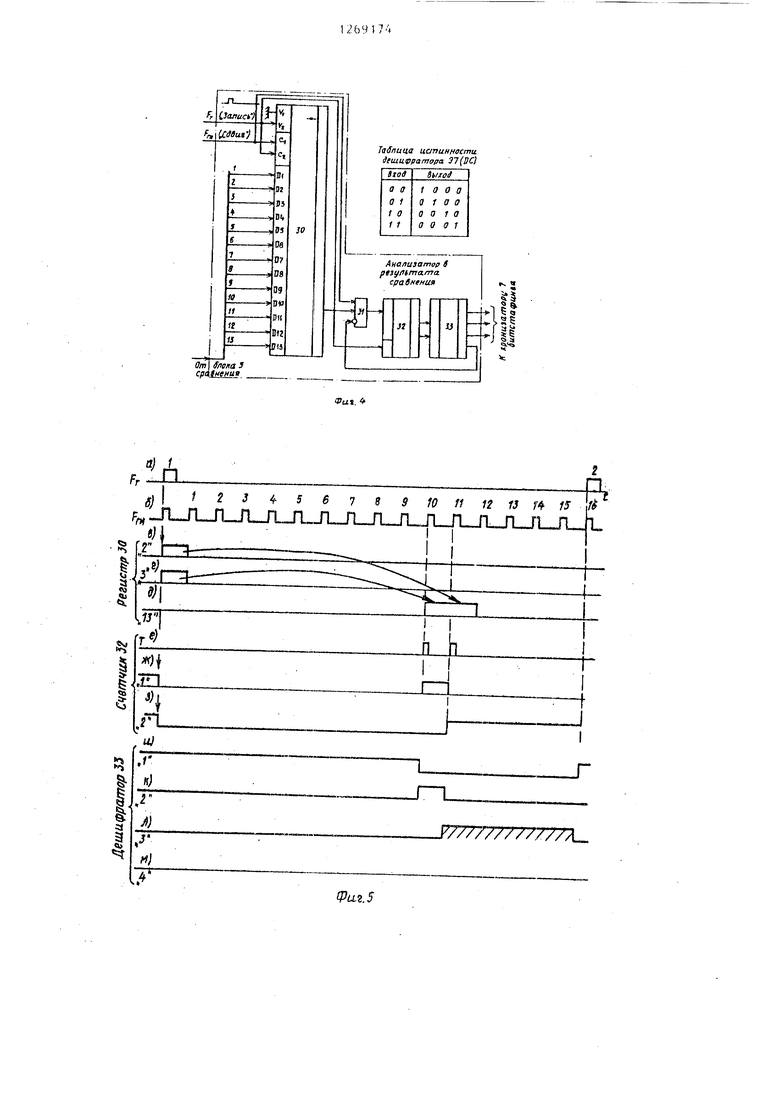

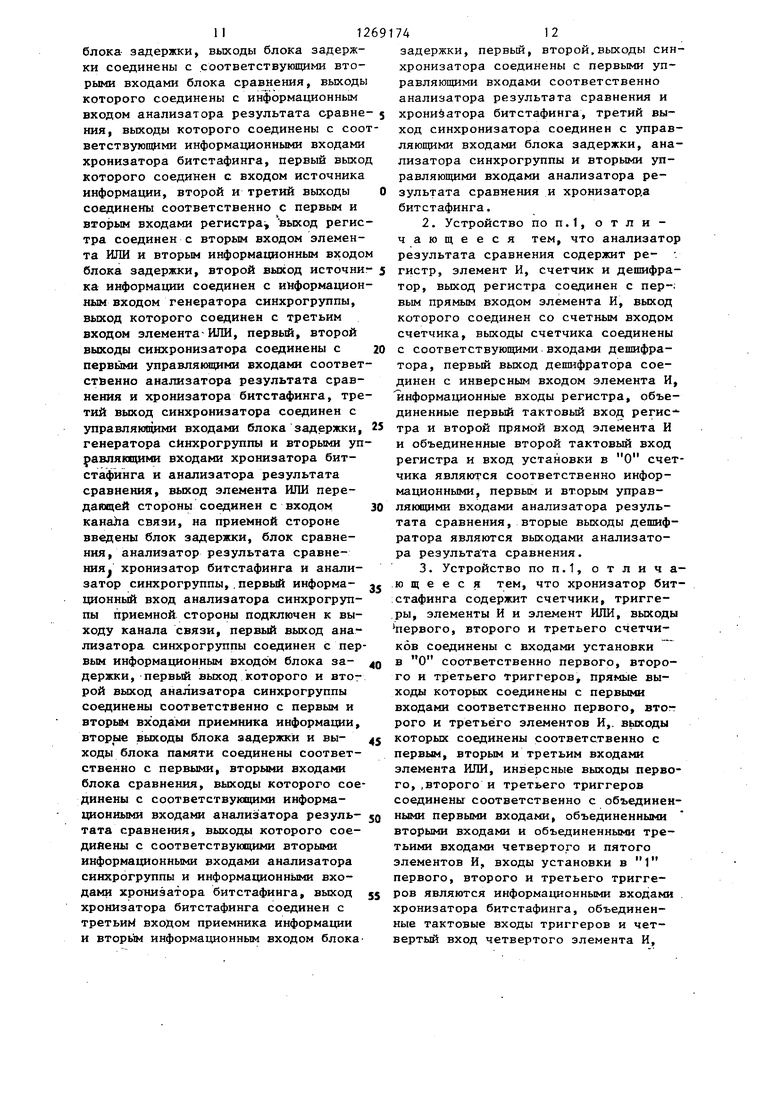

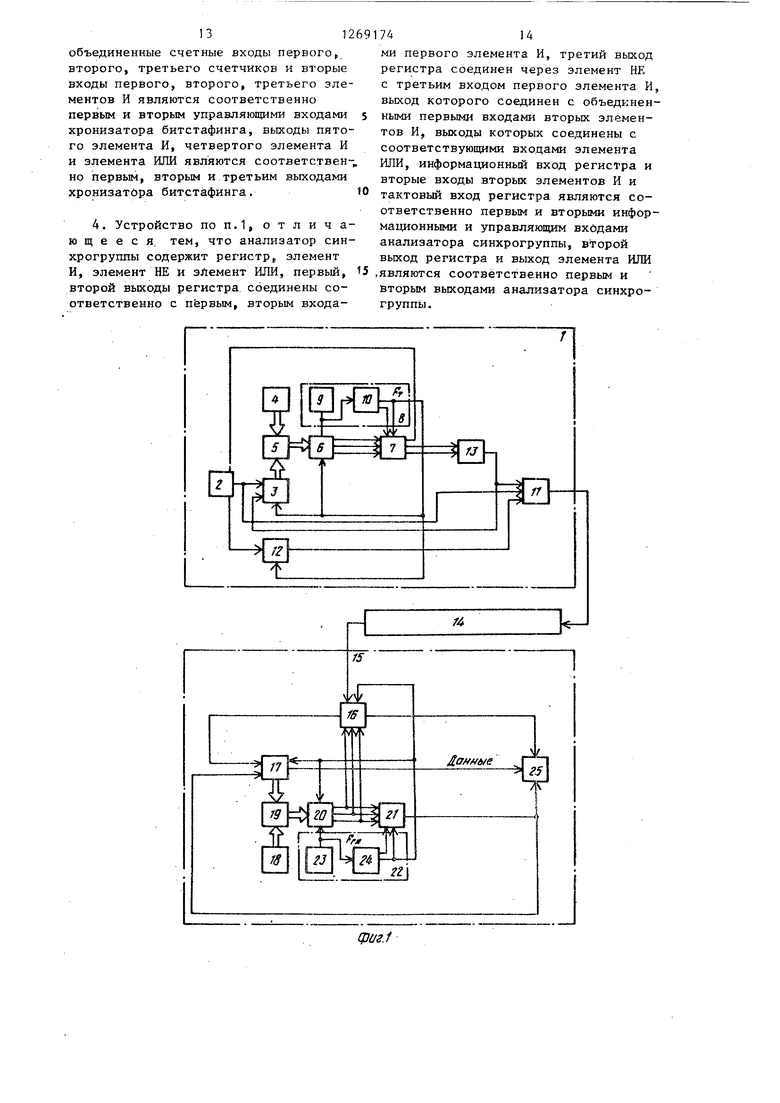

На фиг.1 показана структурная схема устройства; на фиг. 2 - схема процесса форьшрования кадровой посыпки; на фиг.З - функ1 иональная схема блока задержки, блока сравнения и блока памяти; на фиг.4 - функциональная схема анализатора результата сравнения; на фиг.З - временные диаграммы, поясняющие функционирование ана.пизатора результата сравнения} на фиг.6 функциональная схема генератора импульсов, делителя частоты и хронизатора битстафинга; на фиг.7 - временные диаграммы, поясняющие функид юнирование хронизатора битстафинга; на фиг.8 -.функциональная схема регистра, элемента ИЛИ и генератора синхрогруппы; на фиг.9 - функциональная схема анализатора синхрогруппы; на фиг.10 - схема процесса формирования кадровой посылки в базовом объекте.

Устройство для передачи и приема информации (фиг.1) содержит на передающей стороне 1 источник 2 информации, блок 3 задержки, блок 4 памяти, блок 5 сравнения, анализатор 6 результата , сравнения, хронизатор 7 битстафинга, синхронизатор 8, выполненный на генераторе 9 импульсов и делитель 10 частоты, элемент ИЛИ 11, генератор 12 синхрогруппы и регистр 13 канал 14 связи и на приемной стороне 15 - анализатор 16 синхрогруппы, блок 17 задержки, блок 18 памяти, блок 19 сравнения, анализатор 20 результата сравнения, хронизатор 21 битстафинга, синхронизатор 22, выполненньй на генераторе 23 импульсов и делителе 24 частоты, и приемник 25 информации.

Блок 3 задержки (фиг.З) содержит элемент ИЛИ 26 и регистр 27. Блок 4 памяти содержит двухвходовые элементы И 28. Блок 5 сравнения содержит сумматоры 29 по модулю два.

Анализатор 6 результата сравнения (фиг.4) содержит регистр 30, элемент И 31, счётчик 32 и дешифратор 32.

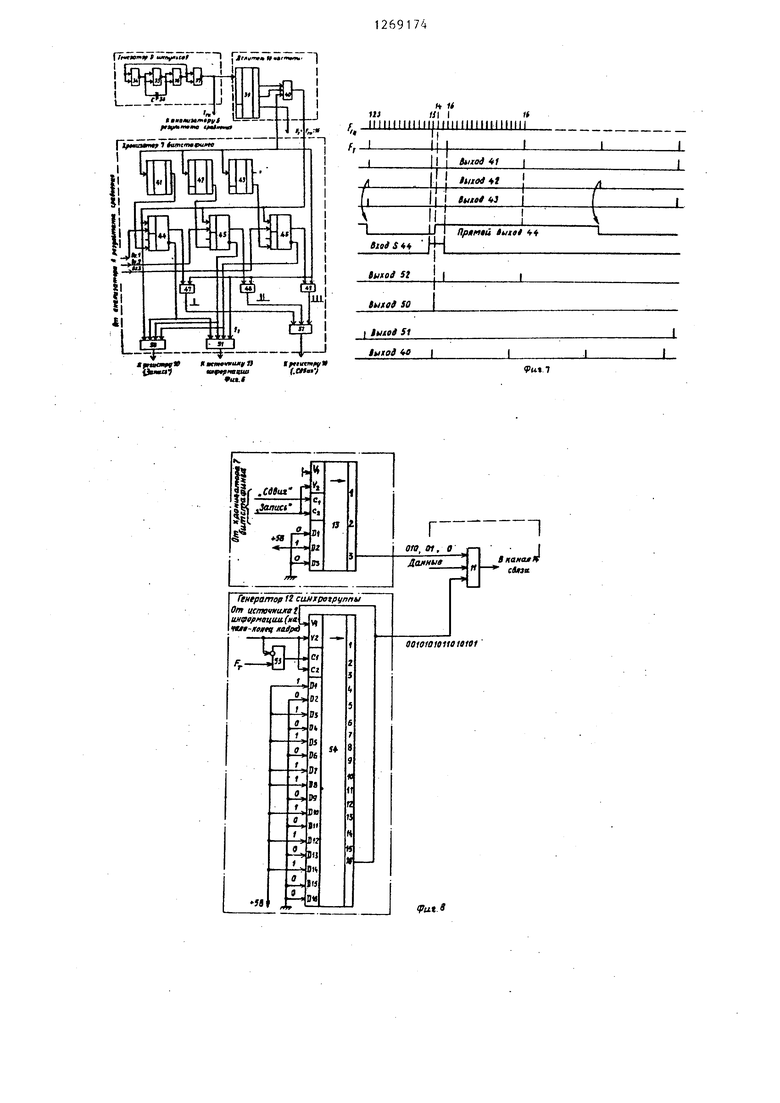

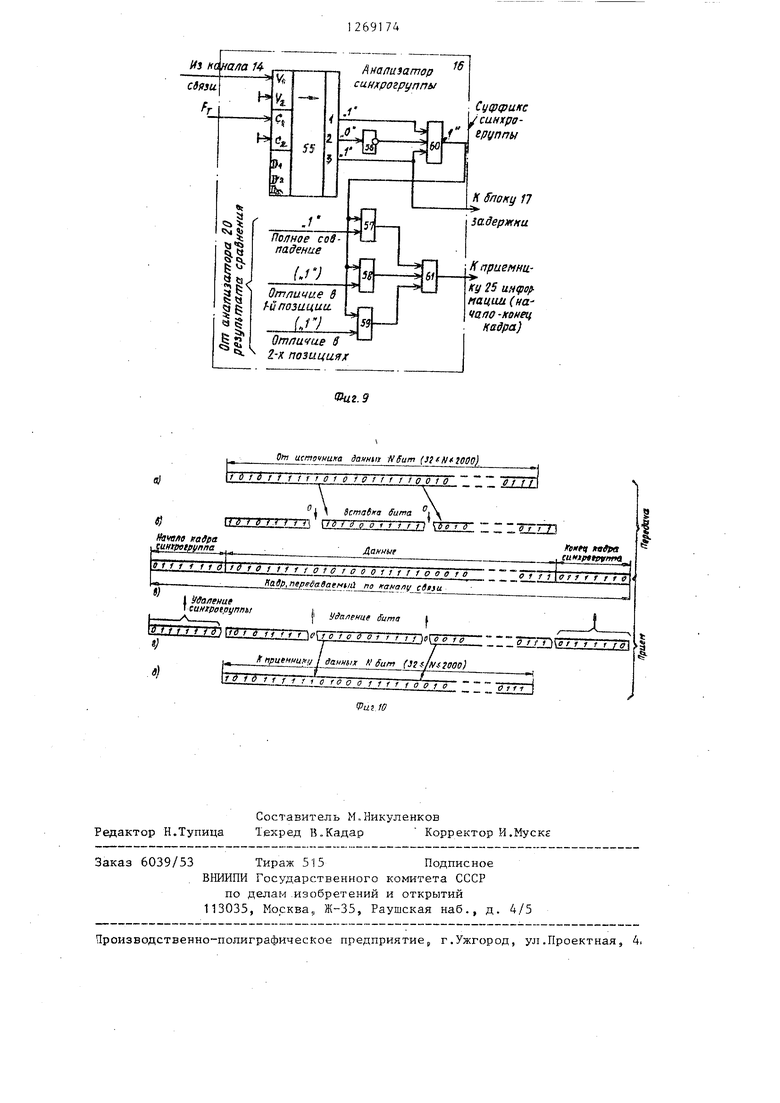

Генератор 9 импульсов (фиг.б) содержит элементы И-НЕ 34-37 i конденсатор 38. Делитель 10 частоты содержит счетчик 39 и элемент И 40. Хро-низатор 7 битстафинга содержит счетчики 41 - 43 импульсов, триггеры 4446, элементы И 47 - 51 и элемент ИЛИ 52..Генератор 12 синхрогруппы (фиг.8) содержит элемент И 53 и регистр 54.

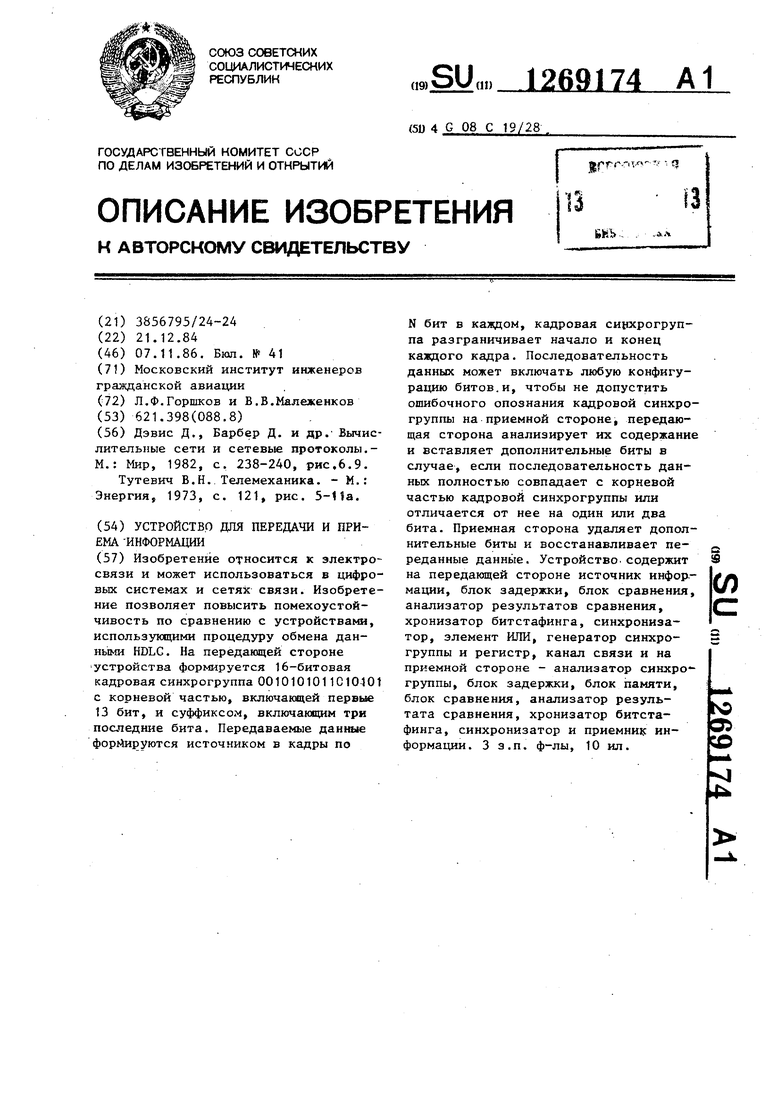

Анализатор 16 синхрогруппы (фиг.9 содержит регистр 55, элемент НЕ 56, элементы И 57-60 и элемент ИЛИ 61,

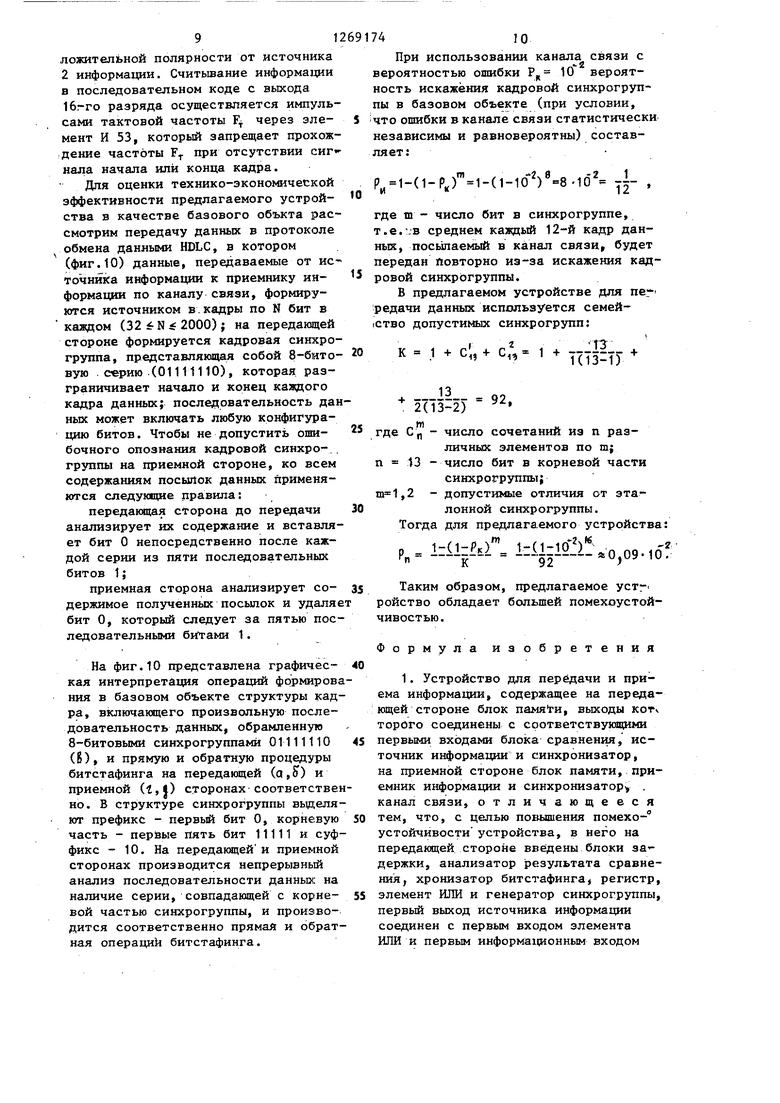

Работа устройства поясняется схемой (фиг.2). На передающей сторо не 1 формируется 16-битовая кадровая синхрогруппа 0010101011010101 с корневой частью, включающей первые 13 бит 0010101011010, и суффиксом, включакщим три последних бита 101 (фиг.2Q). Данные, передаваемые от источника 2 к приемнику 25 по каналу 14 связи, формируются источником 2 в кадры по N бит в каждом (фиг.2 S), кадровая синхрогруппаразграничивает начало и конец каждого кадра (фиг.2 г),

Последовательность данных может включать любую конфигурацию битов и чтобы не допустить ошибочного опознания кадровой синхрогруппы на приемно стороне 15, ко всем содержаниям посылок данных применяются следующие правила: передающая сторона 1 до передачи данных анализирует их содержани и вставляет три бите. 010 (инверсных суффиксу кадровой синхрогруппы) непосредственно после каждой серии из 13 бит, полностью совпадающих с корневой частью кадровой синхрогруппы, или вставляет два бита 01 непосредственно После каждой серии из 13 бит отличающихся только в одной позиции от корневой части кадровой синхрогруппы, или вставляет один бит О непосредственно после каждой серии из 13 бит, отличающихся только в двух позициях от корневой части кадровой синхрогруппы (фиг.2)); приемная сторона 15 анализирует содержание полученньк посылок (фиг, 20.) и удаляет три бита 010, которые следуют непосредственно за серией из 13 бит, полностью совпадающей с корневой 4acTbKf кадровой синхрогруппы, или удаляет два бита 01, которые следуют непосредственно за серией из 13 бит, отличающейся только в одной позиции от корневой части кадровой синхро-. группы, или уд;1ляет один бит О, которьй следует непосредственно за серией, отличающейся только в двух пози3

днях от корнено части Ka;ipo5iO i синхрогруппы (ф1П.2е).

Устройство работает следующим образом.

На передающей стороне 1 источник 2 формирует данные в кадры по N бит в каждом и признак кадра (второй выход), который запускает генератор 12 синхрогруппы. Генератор 12 синхрогруппы посьшает через элемент ИЛИ 11 в канал 14 связи последовательность 0010101011010101 со скоростью, определяемой тактовой частотой F, вырабатываемой делителем 10 частоты. Затем источник 2 отключает признак начала кадра, и данные от источника 2 (первый выход) со скоростью, также определяемой тактовой F , по которой управляет хронизатор 7 битстафинга, поступают одновременно на вход блока 3 задержки на 13 бит и через элемент ИЛИ 11 - в канал 14 связи. Содержимое блока 3 задержки с каждым тактом частоты Ff сдвигается на один бит: самьй старый по врмени поступления бит 13-го разряда тряется, а новый бит с выхода источника 2 записывается в первый разряд. Затем содержимое блока 3 задержки сравнивается побитно в блоке 5 сравнения с содержимым блока 4 памяти, который хранит константу 0010101011010, представляющую собой корневую часть кадровой синхрогруппы Анализатор 6 результата сравнения вырабатьшает один из трех признаков:

содержимое блока 3 задержки совпадает во всех позициях с содержимым блока 4 памяти (первый выход) и необходимо вместо очередных трех битов данных послать в канал 1-4 связи три бита вставки 010;

содержимое блока 3 задержки отличается в одной позиции от содержимог блока 4 памяти (второй выход) и необходимо вместо очередных двух битов данных послать в канал 14 связи два бита вставки 01;

содержимое блока 3 задержки отличается в двух позициях от содержимого блока 4 памяти (третий выход) и необходимо вместо очередного бита данных послать в канал 14 связи один бит вставки 0.

Отсутствие признаков на всех трех выходах анализатора 6 результата сравнения сигнализирует о том, что содержимое блока 3 задержки отличается от корне1.ой части кадровой синхрогруппы более, чем в двух nosHiyiях, и операгщя блтстафинга запрещена Скорость работы анализатора 6 результата сравнения определяется частотой К 16Р .генератора 9 импульсов, так что за период тактовой частоты анализатор 6 успевает полностью обработать результат побитного сравнения текущего блока данных с корневой частью кадровой синхрогруппы.

В зависимости от результата сравнения хронизатор 7 битстафинга (первый выход) запрещает поступление на источник 2 трех, двух или одного импульсов.тактовой частоты Р , чем обеспечивается запрет появления на выходе источника 2 очередных трех, двух или одного битов данных. Одновременно по результату того же сравнения хронизатор 7 битстафинга (второй выход) разрешает поступление на регистр 13 вставки битов трех, двух или одного сдвигающих импульсов, синхронных с тактовой частотой Р. . Этим обеспечивается синхронизация во времени операции битстафинга с работой источника 2.

С выхода регистра 13 биты вставки 010,01,0 поступают через элемент ИЛИ 11 в канал 14 связи и одновременно на второй вход блока 3 задержки, так как для- правильного осуществления операции битстафинга необходимо, чтобы биты вставки также участвовали в анализе наравне с битами данных. Так как во время операции битстафинга данные с выхода источника 2 не поступают, то биты вставки 010, 01, О беспрепятственно сдвигают серию данных, находящихся в блоке 3 задержки, соответственно на три, два или один бит и принимают участие в дальнейшем анализе на совпадение с корневой частью кадровой синхрогруппы.

Для восстановления после каждой операции битстафинга исходного состояния 010 регистра 13 хронизатор 7 битстафинга вьфабатывает сигнал записи (третий выход), который поступает в регистр 13 перед сдвигом на три разряда при вставке битов 010, либо перед сдвигом на два разряда при вставке битов 01, либо перед сдвигом на один разряд при вставке бита 0.

Таким образом все данные, сформированные источником 2 в кадр, последовательно,.бит за битом, анализируются на передающей стороне 1 устройства на наличие серий, совпадающих с корневой частью Кадровой синхрогруппы ипи отличающихся от нее в одной или двух пози1;иях, а затем кодируются путем вставки битов О, 01 или 010 TdK, что в кадре данных, пос тупающих в канал 14 связи, не найдет ся ни одной серии из 16 бит, которая отличалась бы от кадровой синхрогруп пы менее, чем в трех позициях. По окончании передачи кадра данных источник 2 вырабатьтает признак конца кадра, аналогичный признаку начала кадра (второй выход), который так же запускает генератор 12 синхрогруп пы, и закрывающая кадр данных синхро группа 0010101011010101 поступает че рез элемент ИЛИ 11 в канал 14 связи. Из канала 14 связи кадровая посылха, осрамленная синхрогруппами 0010101011010101, поступает на приемную сторону 15 устройства на вход анализатора 16 синхрогруппы, где осуществляется ее задержка на три бита, и далее на вход блока 17 задержки . Блоки 3-10 приемной стороны работают аналогично блокам 17-24 передающей стороны 1 устройства. С приходом 16-го бита из канала 14 связи три последних бита находятся в анализаторе 16 синхрогруппы, а первые 13 бит - в блоке 17 задержки, и если они полностью совпадают с коренной частью кадровой синхрогруппы или отличаются от нее не более, чем в двух позициях, то на одном из выходов анализатора 20 появляется результат сравнения. Одновременно в.ана/лизаторе 16 синхрогруппы осуществляется анализ последних трех бит на соответствие их суффиксу 101 син-. хрогруппы. Если результат такого анализа положительный и по одном из трех выходов анализатора 20 результата сравнения поступает в анали затор 16 Синхрогруппы признак сравне ния, то анализатор 16 синхрогруппы вьфабатьшает сигнал начала кадра, ко торьй поступает на вход приемника 25 и служит разрешением для приема данных. Аналогично производится анализ закрывающей кадр данных синхрогруппы при этом анализатор 16 синхрогруппы вырабатывает сигнал окончания кадра. который поступает на тот же вход . приемника 25 и служит запрещением для приема данных. Через 16 тактов частоты F после начала кадровой синхрогруппы прием-, ник 25 начинает принимать данные, которые поступают на его вход из канала 14 связи через анализатор 16 синхрогруппы и блок 17 задержки. Хронизатор 21 битстафинга управляет тактовой частотой F, поступающей на вход блока 17 задержки и вход приемника 25. Операция удаления битов, вставленных при передаче, осуществляется следующим образом. Если после сравнения в блоке 19 очередной серии данных из 13 бит, находящихся в блоке 17 задержки, с корневой частью кадровой синхрогруппы, хранящейся в блоке 18 памяти, анализатор 20 результата сравнения вырабатьшйет признак на одном из трех своих выходов, то а выходе хронизатора 21 битстафинга исключаются три, два или один импульс тактовой частоты FT, что запрещает прием соответственно трех, двух или одного бита данных приемником 25 и одновременно запрещает продвижение серии данных в блоке 17 задержки, поэтому поступающие из канала 14 связи на вход блока задержки три, два или один биты вставки теряются Блок 3 задержки (фиг.З) реализован на 13 разрядном универсальном регистре 27. В последовательном режиме работы (режиме сдвига) информация подается на вход,У1, синхрбнизация осуществляется по входу С1. импульсами положительной полярности; на входах V2, С2 - уровни логического О (т.е. потенциал земпи). Блок 4 памяти (фиг.З) реализован на 13 двухвходовых элементах И 28. На объединенные входы элементов постоянно подается либо потенциал земли (уровень, логического О), либо положительный потенциал источника питания (уровень логической 1). На выходах элементов И 28 устанавливается постоянный код,.соответствующий коренной части кадровой синхрогруппы . БЛОК 5 сравнения (фиг.З) реализован на 13 сумматорах 29 по модулю 2. На первый вход каждого- сумматора 29 подается разряд данных d(c, а на вто71

рой его вход соответствующий разряд константы CK. При d с на выходе сумматора 29 уровень логического О, при d f Cj, - уровень логической 1. Таким образом, с каждым так том частоты F число единиц на тринадцати выходах блока 5 определяет число несовпадающих позиций в очередной серии данных.

Анализатор 6 результата сравнения (фиг.4) реализован на универсальном регистре 30, элементе И 31, счетчике 32 по модулю 4 и дешифраторе 33 2 X 4. На информационные входы D1-D13 регистра 30 поступают логические 1 с тех сумматоров 29 по модулю 2 блока 3, где соответствующие биты данны и константы не совпадают. В парал- . лельном режиме работы (режим Записи чисел) регистра 30 VI О, С1 0; V2 1, С2 1, т.е. синхронизация осуществляется по входу С2 и с каждым тактом частоты F. информация на D1-D13 записывается в регистр 30 и появляется на его соответствующих параллельных выходах 1-13. Затем информация сдвигается частотой Fpy 16-F (синхровход С2) и в течение тринадцати тактов Fp поступает уже в последовательном коде с выхода 13-го разряда регистра 30 через элемент И 31 на счетный вход Т счетчика 32. Подсчитанное число единиц N дешифрируется дешифратором 33, так что если N О, то появляется 1 на первом выходе, если N 1, то на втором выходе, если N 2, то на третьем выходе, если , то на четвертом выходе появляется 1, которая блокирует вход счетчика 32. Каждым тактом частоты F производится установка в О счетчика 32. На фиг.5 показаны временные диаграммы работы анализатора 6 результата сравнения для случая, когда уровни логической присутствуют на входах D2 и D3 регистра 30. Диаграммь а ,5 показывают соотношение частот тактовой и генератора 9 импульсов. Диаграммы В,2 показывают запись единиц в регистр 30, а - продвижение этих сигналов по регистру 30. Диаграмма е показывает сигналы на входы счетчика 32, ж из,- на его выходах. Диаграммы и, к, л, мпоясняют работу дешифратора 33 для данного случая.

Хронизатор 7 битстафинга (фиг.6) реализован на трех счетчиках: 41

1748

(делитель чатоты на 2), 42 (делител на 3) и 43 (делитель на 4), трех RS-триггерах 44-46, элементах И 4751 и на элементе ИЛИ 52. Счетчик 41 триггер 44 и элемент И 47 формируют временное Окно, включающее один импульс частоты F, если на вход 1 поступает признак (логическая 1) из анализатора 6 результата сравнения полного совпадения d,; сj..Счетчик 42, триггер 45 и элемент И 48 формируют временное Окно, включающее два импульса частоты F, если н вход 2 поступает признак отличия d,, i J,13 от cj, i 1,1J в одной позиции. Счетчик 43, тригге 46 и элемент И 49 формируют временное Окно, включающее три импульса частоты FT- , если на вход 3 поступает признак отличия djV , i 1,13 от , i 1,13 в двух позициях. Эти сигналы, объединенные элементом ИЛИ 52, используются в качестве синхросигналов, осуществляющих сдвиг в регистре 13 битстафинга.

Элемент И 50 формирует сигнал Записи для регистра 13, а элемент И 51 формирует временное Окно для запрета прохождения одного, двух или трех импульсов частоты F, которое используется на передающей стороне 1 устройства для запрета передачи на время операции битстафинга,а на приемной стороне 15 - для удаления вставленньсх битов и запрета приема на это время. На фиг.7 показаны временные диаграммы, поясняющие функционирование хронизатора 7 битстафинга для случая, когда;логическая 1 присутствует на входе 2.

Регистр 13 вставки битов (фиг.8) реализован на трехразрядном универсальном регистре. На входах D1-D3 всегда присутствует константа 010 и вписывание ее в регистр 13 осуществляется перед каждой операцией сдвига по входам С2, V 2 сигналом от хронизатора 7 битстафинга. Считывание битов стафинга 010 или 01, или О с выхода третьего разряда регистра 13 осуществляется импульсами, подаваемыми на вход С1 также от хронизатора 7 битстафинга.

Генератор 12 синхрогруппы (фиг,8) реализован на универсальном регистре 54. Вписывание кода кадровой синхрогруппы производится по входам V2, С2 сигналом Начало-конец кадра по91ложитепьной полярности от источника 2 информации. Считьшание информаи(ии в последовательном коде с вькода 1бгго разряда осуществляется импульсами тактовой частоты Е, через злемент И 53, который запрещает прохождение частоты FT при отсутствии сиг-нала начала или конца кадра. Для оценки технико-экономической эффективности предлагаемого устройства в качестве базового объкта рассмотрим передачу данных в протоколе обмена данными HDLC, в котором (фиг.10) данные, передаваемые от источника информации к приемнику информации по каналу связи, формируются источником в.кадры по N бит в кавдом (32 i 2000); на передающей стороне формируется кадровая синхрогруппа, представляющая собой 8-битовую серию .(01111110), которая разграничивает начало и конец каждого кадра данных; последовательность дан ных может включать любую конфигурацию битов. Чтобы не допустить ошибочного опознания кадровой синхро- . группы на приемной стороне, ко всем содержаниям посылок данных применяются следующие правила: передающая сторона до передачи анализирует их содержание и вставляет бит О непосредственно после каждой серии из пяти последовательных битов 1; приемная сторона анализирует содержимое полученных посылок и удаляе бит О, который следует за пятью последовательными битами 1. На фиг.10 представлена графическая интерпретация операций формирова ния в базовом объекте структуры кадра, включаняцего произвольную последовательность данных, обрамленную 8-битовыми синхрогруппами 01111110 (В), и прямую и обратную процедуры битстафинга на передающей (а,) и приемной (l,j) сторонахсоответствен но. В структуре синхрогруппы вьзделяют префикс - первьй бит О, корневую часть - перйые пять бит 11111 и суффикс - 10. На передакмцейи приемной сторонах производится непрерывный анализ последовательности данньи: на наличие серии, совпадающей с корневой частью синхрогруппы, и производится соответственно прямая и обратная операций битстафинга. 74 При использовании канала связи с вероятностью ошибки Р 10 вероятность искажения кадровой синхрогруппы в базовом объекте (при условии, что ошибки в канале связи статистически независимы и равновероятны) составляет:(1-Р,) 1-(1-10).8.10 - , где m - число бит в синхрогруппе, т.е.:.в среднем каждый 12-й кадр данных, посьшаемый в канал связи будет передан Повторно из-за искажения кад ровой синхрогруппы. В предлагаемом устройстве для пег редачи данных используется семей(Ство допустимых синхрогрупп: Т( к 1 + с, + cf, + . . 92 2(13-2) где С„ - число сочетаний из п различных элементов по т; п 13 - число бит в корневой части синхрогруппы; ,2 - допустимые отличия от эталонной синхрогруппы. Тогда для предлагаемого устройства: Р Ы11РЕ.) Idliioi o 09-10 Грк92aujuy 1U. Таким образом, предлагаемое устгройство обладает большей помехоустойчивостью. Формула изобретения 1. Устройство для передачи и приема информации, содержащее на передающей стороне блок пaмяtи, выходы кот торого соединены с соответствующими первыми входами блока сравнения, источник информахщи и синхронизатор, на приемной стороне блок памяти, приемник информации и синхронизатору , канал Связи, отличающееся тем, что, с целью повышения помехо- устойчивости устройства, в него на передающей стороне введены блоки задержки, анализатор результата сравнения, хронизатор битстафинга регистр, элемент ИЛИ и генератор синхрогруппы, первый выход источника информации соединен с первым входом элемента ИЛИ и первым информационным входом

II1269

блока задержки, выходы блока задержки соединены с соответствующими вторыми входами блока сравнения, выходы которого соединены с информационным входом анализатора результата сравне- 5 ния, выходы которого соединены с соответствующими информационными входами хронизатора битстафинга, первый выход которого соединен с входом источника информации, второй и третий выходы О соединены соответственно с первым и вторым входами регистра выход регистра соединен с вторым входом элемента ИЛИ и вторым информационным входом блока задержки, второй выход источни- 5 ка информации соединен с информационным входом генератора синхрогруппы, выход которого соединен с третьим входом элемента-ИЛИ, первый, второй выходы синхронизатора соединены с 20 первыми управляюпщми входами соответственно анализатора результата сравнения и хронизатора битстафинга, третий выход синхронизатора соединен с управляющими входами блока задержки, 2S генератора синхрогруппы и вторыми управлякщиьш входами хронизатора битстафинга и анализатора результата сравнения, выход элемента ИЛИ передающей стороны соединен с входом 30 канала связи, на приемной стороне введены блок задержки, блок сравнения, анализатор результата сравнения, хронизатор битстафинга и анализатор синхрогруппы,.первый информа- j. ционный вход анализатора синхрогруппы приемной стороны подключен к выходу канала связи, первый выход анализатора синхрогруппы соединен с первым информационным входом блока за- до держки, первый выход которого и второй выход анализатора синхрогруппы соединены соответственно с первым и вторым вхЪдами приемника информации, вторые выходы блока задержки и вы- 45 ходы блока памяти соединены соответственно с первыми, вторыми входами блока сравнения, выходы которого соединены с соответствующими информационными входами анализатора резуль- JQ тата сравнения, выходы которого соедиЯены с соответствующими вторыми информационными входами анализатора синхрогруппы и информационными входами хронизатора битстафинга, выход js хронизатора битстафинга соединен с третьий входом приемника информахщи и BTopbiM информационным входом блока

17412

задержки, первый, второй,выходы синхронизатора соединены с первыми управляющими входами соответственно анализатора результата сравнения и хронизатора битстафинга, третий выход синхронизатора соединен с управляющими входами блока задержки, анализатора синхрогруппы и вторыми управляющими входами анализатора результата сравнения и хронизатора битстафинга.

2.Устройство по п.1, о т л и чающееся тем, что анализатор результата сравнения содержит регистр, элемент И, счетчик и дешифратор, выход регистра соединен с пер-, вым прямым входом элемента И, выход которого соединен со счетным входом счетчика, выходы счетчика соединены с соответствующими входами дешифратора, первый выход дешифратора соединен с инверсным входом элемента И, информационные входы регистра, объединенные первый тактовый вход регистра и второй прямой вход элемента И и объединенные второй тактовый вход регистра и вход установки в О счетчика являются соответственно информационными, первым и вторым управляющими входами анализатора результата сравнения, вторые выходы дешифратора являются выходами анализатора результата сравнения.

3.Устройство ПОП.1, отлича.ю щ е е с я тем, что хронизатор битстафинга содержит счетчики, триггеры, элементы И и элемент ИЛИ, выходы первого, второго и третьего счетчиков соединены с входами установки

в О соответственно первого, второго и третьего триггеров, прямые выходы которых соединены с первыми входами соответственно первого, второго и третьего элементов И,, выходы которых соединены соответственно с первым, вторым и третьим входами элемента ИЛИ, инверсные выходы первого, .второго и третьего триггеров соединены соответственно с объединенными первыми входами, объединенными вторыми входами и объединенными третьими входами четвертого и пятого элементов И., входы установки в 1 первого, второго и третьего триггеров являются информационными входами хронизатора битстафинга, объединенные тактовые входы триггеров и четвертый вход четвертого элемента И,

1312

объединенные счетные входы первого, второго, третьего счетчиков и вторые входы первого, второго, третьего элементов И являются соответственно первым и вторым управляющими входами хронизатора битстафинга, выходы пятого элемента И, четвертого элемента И и элемента ИЛИ являются соответственно первым, вторым и третьим выходами хронизатбра битстафинга,

4. Устройство по П.1, отличающееся, тем, что анализатор синхрогруппы содержит регистр, элемент И, элемент НЕ и элемент ИЛИ, первый, второй выходы регистра соединены соответственно с первым, вторым входа7414

ми первого элемента И, третий выход регистра соединен через элемент НЕ с третьим входом первого элемента И, выход которого соединен с объединенными первыми входами вторых элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, информационный вход регистра и вторые входы вторых элементов И и тактовый вход регистра являются соответственно первым и вторыми информационными и управляющим входами анализатора синхрогруппы, второй выход регистра и выход элемента ИЛИ

вляются соответственно первым и вторым выходами анализатора синхрогруппы.

2, r,

..:№

Kaifelat cuHtpotpynira

t t } f т f 10 If 1 tin ftn aa 1 a f 0 t a t f 0 r a f о n

r XOfHfiat П ,

f I S f в т в } ten tin

t t ff a в f a f f I a t1 в f оi i t a 11000010 Пата cattraftHut

« .

в в f О I 1 t о I 1 0 t о t ( 10 о 0 t f о ft о 1

Опличие I t-aa позиции t Omrukut t t-t пвтци.

, go t о t 1 I O.I 1 a /71(ittooieitottei

OmiipuSafeiifa кчвр сшироруппа

. / ,

i) Lfffui taH/fUf с SumcirapiLHton (Hfum)I Шищ

--i f fottotaetttfOe tettatfafaaaa

)Uf f a a Of a f a t a 11 о , o j t i a t t a в e Jetiptfit itfui nputnt

HfU. -t

г fttarrata. . ftfaet«fterf9 fa

- Ctf ftniuxc

%

lofpiilajoina mff ctanfetfi/ a / i

:x.

9u.t

TttSnuna истинности dsuiu.Vfamai a Э7()

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования и декодирования сигналов в системах передачи цифровых данных | 1980 |

|

SU1046959A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1145357A1 |

| Устройство для формирования циклического синхроимпульса | 1989 |

|

SU1725404A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Устройство формирования сигнала кадровойСиНХРОНизАции | 1979 |

|

SU843301A1 |

| Многоканальная телеизмерительная система | 1986 |

|

SU1310870A1 |

| Устройство синхронизации аппаратуры однокадровой передачи изображений | 1981 |

|

SU1022332A1 |

| Устройство определения конца блока циклического кода | 1987 |

|

SU1515381A2 |

| Синхрогенератор | 1989 |

|

SU1672586A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

Изобретение относится к электросвязи и может использоваться в цифровых системах и сетях связи. Изобретение позволяет повысить помехоустойчивость по сравнению с устройствами, использующими процедуру обмена данными HDLC. На передающей стороне устройства формируется 16-битовая кадровая синхрогруппа 0010101011C 10101 с корневой частью, включающей первые 13 бит, и суффиксом, включающим три последние бита. Передаваемые данные формируются источником в кадры по N бит в каждом, кадровая си1асрогруппа разграничивает начало и конец каяздого кадра. Последовательность данных может включать любую конфигурацию битов.и, чтобы не допустить ошибочного опознания кадровой синхрогруппы на приемной стороне, передающая сторона анализирует их содержание и вставляет дополнительные биты в случае, если последовательность данных полностью совпадает с корневой частью кадровой синхрогруппы или отличается от нее на один или два бита. Приемная сторона удаляет дополнительные биты и восстанавливает переданные данные. Устройство, содержит на передающей стороне источник инфор).(Л мации, блок задержки, блок сравнения, анализатор результатов сравнения, хронизатор битстафинга, синхронизатор, элемент ИЛИ, генератор синхрогруппы и регистр, канал связи и на приемной стороне - анализатор синхрогруппы, блок задержки, блок памяти, блок сравнения, анализатор результата сравнения, хронизатор битстафинга, синхронизатор и приемник информации. 3 з.п. ф-лы, 10 ил.

H тевнтшч/я

ftHUtmff

iw-v loftfiaeua fu.l

Фи 7

Отпичие в f-u позиции.

U)

Qmnufue S 1-к позициях

А на/ru за тор синхрогруппы

Сусрд икс синхрогруппы

К ffioKy 17

задержки

К приемнику 25 uftgiofнации (начаао -конец кадра)

| Дэвис Д., Барбер Д | |||

| и др | |||

| Вычислительные сети и сетевые протоколы.М.: Мир, 1982, с | |||

| Ручная тележка для грузов, превращаемая в сани | 1920 |

|

SU238A1 |

| Тутевич Б.Н. | |||

| Телемеханика | |||

| - М.: Энергия, 1973, с | |||

| Ребристый каток | 1922 |

|

SU121A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-11-07—Публикация

1984-12-21—Подача