Изобретение относится к вычислительной технике и может быть применено при построении арифметических устройств высокопроизводительных ЭВМ.

Целью изобретения является расширение функциональных возможностей устройства за счет того, что оно работает как в режиме умножения, так и в режиме сложения, упрощение процедур наращиваемости устройства и взаимозаменяемости его блоков.

В основу работы устройства заложен систолический способ умножения методом поэтапного сложения сдвигаемых на один разряд вправо множителя и частичных сумм произведения. В устройстве выполняемая комбинационной схемой функция интерпретируется как установление принадлежности входного набора аргументов булевой функции множеству наборов, на которых эта функция принимает значение логической "1" или логического "0". Установление принадлежности входного набора аргументов указанному множеству наборов выполняется с помощью операции пересечения над кубами покрытий функций суммы и функции переноса одноразрядного комбинационного сумматора. Разбиение всего процесса вычисления булевых функций суммы и переноса на элементарные, независимые друг от друга операции позволило организовать в устройстве конвейерную и матричную обработку данных с минимальным по времени тактом работы. В устройстве перед началом работы в ячейки систолических полусумматоров необходимо записать кубические покрытия функций суммы и функций переноса.

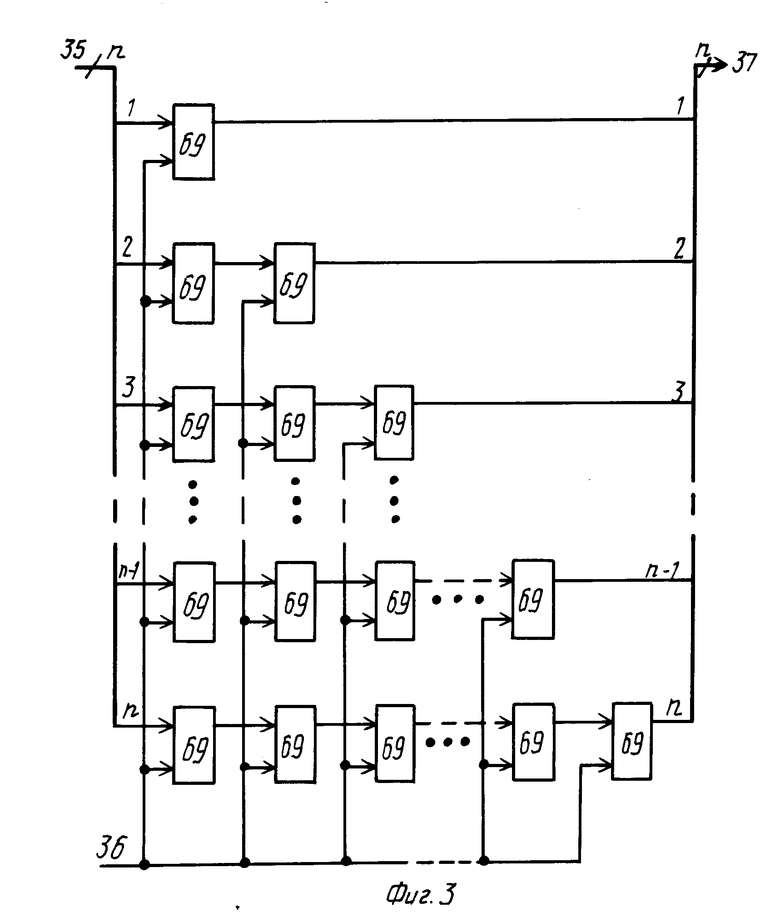

На фиг. 1 представлена функциональная схема множительного устройства; на фиг. 2 - функциональная схема одноразрядного систолического полусумматора; на фиг. 3 - схема блока задержки; на фиг. 4 - схема блока мультиплексоров; на фиг. 5 - схема вычислительной ячейки; на фиг. 6 - схема элемента свертки; на фиг. 7 - схема коммутатора; на фиг. 8 - временная диаграмма тактовых сигналов первой группы в режиме сложения; на фиг. 9 - временная диаграмма тактовых сигналов второй группы устройства.

Устройство (фиг. 1) содержит регистры 1-3 множимого, регистры 4-6 множителя, три группы элементов И 7-9, три блока 10-12 задержки, группу из n блоков 13 мультиплексоров, первую группу из n систолических полусумматоров 14, вторую группу из n систолических полусумматоров 15, первую группу из n информационных входов 16 устройства, вторую группу из n информационных входов 17 устройства, третью группу из трех информационных входов 18 устройства, четвертую группу из четырех информационных входов 19 устройства, пятую группу из четырех информационных входов 20 устройства, первый управляющий вход 21 устройства, второй управляющий вход 22 устройства, группу из трех входов 23 установки устройства, первую группу из девяти тактовых входов 24 устройства, вторую группу из шести тактовых входов 25 устройства, n групп по три выхода 26 суммы устройства, группу из трех выходов 27 переноса устройства, первую группу из четырех информационных входов 28 систолических полусумматоров 14, 15, вторую группу из трех информационных входов 29 систолических полусумматоров 14, 15, управляющий вход 30 систолических полусумматоров 14, 15, группу из трех входов 31 установки систолических полусумматоров 14, 15, группу из шести тактовых входов 32 систолических полусумматоров 14, 15, первую группу из четырех информационных выходов 33 систолических полусумматоров 14, 15, вторую группу из трех информационных выходов 34 систолических полусумматоров 14, 15, группу из n информационных входов 35 блоков 10-12 задержки, тактовый вход 36 блоков 10-12 задержки, группу из n информационных выходов 37 блоков 10-12 задержки, первую группу из трех информационных входов 38 блоков 13 мультиплексоров, вторую группу из трех информационных входов 39 блоков 13 мультиплексоров, третью группу трех информационных входов 40 блоков 13 мультиплексоров, четвертую группу из трех информационных входов 41 блоков 13 мультиплексоров, пятую группу из трех информационных входов 42-44 блоков 13 мультиплексоров, управляющий вход 45 блоков 13 мультиплексоров, установочный вход 46 блоков 13 мультиплексоров, тактовый вход 47 блоков 13 мультиплексоров и группу из трех информационных выходов 48 блоков 13 мультиплексоров.

Первая и вторая группы n систолических полусумматоров 14, 15 образуют три n-разрядных систолических сумматора с поразрядным последовательным переносом. Систолические сумматоры 14, 15 (фиг. 2) имеют одинаковую структуру и содержат матрицу 3х4 вычислительных ячеек 49, три элемента 50 свертки, четыре коммутатора 51, элемент НЕ 52, первый информационный вход 53 вычислительной ячейки 49, второй информационный вход 54 вычислительной ячейки 49, тактовый вход 55 вычислительной ячейки 49, первый информационный выход 56 вычислительной ячейки 49, второй информационный выход 57 вычислительной ячейки 49, группу из четырех информационных входов 58 элементов 50 свертки, установочный вход 59 элементов 50 свертки, первый тактовый вход 60 элементов 50 свертки, второй тактовый вход 61 элементов 50 свертки, третий тактовый вход 62 элементов 50 свертки, выход 63 результата элементов 50 свертки, входы 64-67 коммутаторов 51, выход 68 коммутаторов 51.

Блоки 10-12 задержки (фиг. 3) имеют одинаковую структуру и содержат m D-триггеров 69:

m= i

i

Блок 13 мультиплексоров (фиг. 4) содержит кольцевой распределитель 70 импульсов, элемент НЕ 71, три группы по шесть элементов И 72-74, три элемента ИЛИ 75-77. Три группы элементов И и соответствующие элементы ИЛИ в каждом блоке 13 мультиплексоров образуют три мультиплексора, которые работают от единого кольцевого распределителя импульсов.

Вычислительная ячейка 49 предназначена для выполнения элементарной операции пересечения компоненты входного набора аргументов с компонентой одного куба кубического покрытия функции переноса (в первой группе систолических полусумматоров 14) или функции суммы (во второй группе систолических полусумматоров 15). Вычислительная (фиг. 5) ячейка 49 содержит D-триггеры 78, 79 и элемент 80 неравнозначности.

Элемент 50 свертки предназначен для формирования результата пересечения входного набора аргументов с кубическим покрытием функции переноса (в первой группе систолических полусумматоров 14) или функции суммы (во второй группе систолических полусумматоров 15). Элемент 50 свертки (фиг. 6) содержит четыре RST-триггера 81-84, элемент ИЛИ 85 и D-триггер 86.

Коммутатор 51 (фиг. 7) содержит элементы И 87, 88 и элемент ИЛИ 89.

Устройство работает в трех режимах: режиме программирования, режиме сложения и режиме умножения.

В режиме программирования производится запись в устройство кубических покрытий, которые определяют функционирование устройства в остальных режимах работы.

В режимах сложения и умножения искомые суммы и произведения вычисляются путем выполнения операций над кубическими покрытиями (D-покрытиями или R-покрытиями) функции переносов (в первой группе систолических полусумматоров 14) и функции суммы (во второй группе систолических полусумматоров 15). D-покрытие (R-покрытие) некоторой булевой функции f - это представленная в кубической форме минимальная дизьюнктивная нормальная форма (МДНФ) прямой функции f (инверсной функции  ). МДНФ прямой функции f (инверсной функции

). МДНФ прямой функции f (инверсной функции  ) содержит все наборы, на которых функция f принимает значение логической "1" (логического "0"). D-покрытие (R-покрытие) состоит из кубов, количество которых равно количеству импликант МДНФ прямой функции f (инверсной функции

) содержит все наборы, на которых функция f принимает значение логической "1" (логического "0"). D-покрытие (R-покрытие) состоит из кубов, количество которых равно количеству импликант МДНФ прямой функции f (инверсной функции  ). Количество компонент куба равно количеству переменных МДНФ, а значениями компонент куба могут быть только три символа 0, 1, Х, где Х = {0, 1}. Каждый куб dε (rε) соответствует одной импликанте МДНФ прямой функции f (инверсной функции

). Количество компонент куба равно количеству переменных МДНФ, а значениями компонент куба могут быть только три символа 0, 1, Х, где Х = {0, 1}. Каждый куб dε (rε) соответствует одной импликанте МДНФ прямой функции f (инверсной функции  ) таким образом, что единичное (нулевое) значение компоненты куба соответствует прямому (инверсному) значению переменной в импликанте МДНФ (dε∈ D, rε ∈ R).

) таким образом, что единичное (нулевое) значение компоненты куба соответствует прямому (инверсному) значению переменной в импликанте МДНФ (dε∈ D, rε ∈ R).

Каждое из покрытий (D-покрытие или R-покрытие) однозначно определяет функционирование комбинационной схемы, поэтому используется только одно из них, а именно то покрытие, которое содержит меньшее количество кубов. В дальнейшем для простоты изложения рассматриваются только D-покрытия.

Например, n-разрядный комбинационный сумматор может быть представлен в виде n взаимосвязанных одноразрядных сумматоров. Функционирование i-го одноразрядного сумматора может быть описано с помощью функции переноса fп1 и функции суммы fc1 следующего вида: =

=  bipi-1∨a

bipi-1∨a pi-1∨aib

pi-1∨aib aibipi-1 (1)

aibipi-1 (1)

f =

=  p

p b

b a

a aibipi-1 где ai, bi - слагаемые в i-м разряде;

aibipi-1 где ai, bi - слагаемые в i-м разряде;

pi-1 - перенос из (i-1)-го разряда.

Кубические покрытия переноса (Dп1-покрытие) и суммы (Dс1 - покрытие) функций (1) имеют вид

D =

=

D

D =

=

Поскольку операция умножения чисел с фиксированной запятой может быть сведена к операциям сложения и сдвига, поэтому n-разрядный умножитель может быть выполнен на основе n-разрядного накапливающего сумматора. Накапливающий сумматор содержит память для хранения суммы в течение нескольких этапов суммирования, и поэтому представляет собой конечный автомат.

С помощью кубических покрытий можно определить функционирование также и конечного автомата, если представить его в виде схемы, состоящей из двух частей: комбинационной части и памяти. Комбинационная часть i-го одноразрядного накапливающего сумматора может быть описана с помощью функции переноса fп'' и функции суммы fc'' следующего вида: =

=  sipi-1∨a

sipi-1∨a pi-1∨ais

pi-1∨ais aisipi-1

aisipi-1

f =

=  p

p s

s a

a aisipi-1 (2) где Si - значение выхода элемента памяти i-го одноразрядного накапливающего сумматора, сохраняющего ранее накопленную сумму.

aisipi-1 (2) где Si - значение выхода элемента памяти i-го одноразрядного накапливающего сумматора, сохраняющего ранее накопленную сумму.

Кубические покрытия переноса (Dп''-покрытия) и суммы (Dc''-покрытия) функции (2) имеют вид

D =

=

D

D =

=

(3)

(3)

Перед началом работы устройства исходные покрытия (3) преобразуются в транспонированную форму и в режиме программирования записываются в первую 14 и вторую 15 группы систолических полусумматоров. Если после режима программирования следует режим сложения, тогда процесс преобразования покрытий (3) происходит следующим образом.

Dп'' - покрытие вначале представляется в виде

D =

=  и затем транспонируется аналогично известной операции транспонирования матриц. В итоге получают Dпсл-покрытие вида

и затем транспонируется аналогично известной операции транспонирования матриц. В итоге получают Dпсл-покрытие вида

D

(4) Dc''-покрытие вначале представляется в виде

(4) Dc''-покрытие вначале представляется в виде

D =

=

и затем транспонируется. В итоге получают Dcсл-покрытие вида

и затем транспонируется. В итоге получают Dcсл-покрытие вида

D

(5)

(5)

Далее покрытие (4) записывается в первую группу систолических полусумматоров 14, а покрытие (5) - во вторую группу систолических полусумматоров 15.

В режиме программирования на первый управляющий вход 21 поступает сигнал логической "1", который разрешает прохождение информации между соседними парами систолических полусумматоров 14, 15.

В течение 3˙n тактов через четвертую группу четырех информационных входов 19 поступает n Dпсл-покрытий построчно, начиная с первой строки (первого куба). Одновременно в течение 3˙n тактов через пятую группу четырех информационных входов 20 поступает n Dcсл-покрытий также построчно.

В каждом такте поступает очередная строка указанных покрытий и путем сдвига информация продвигается по систолической полусумматорам 14, 15. В конце режима программирования в каждом из систолических полусумматоров 14, 15 записано соответственно Dпсл-покрытие и Dcсл-покрытие.

Если после режима программирования следует режим умножения, то процесс преобразования кубических покрытий и запись их в устройство происходит следующим образом.

Dп''-покрытие вначале представляется в виде

D =

=

и затем транспонируется. В итоге получают Dпумн-покрытие вида

и затем транспонируется. В итоге получают Dпумн-покрытие вида

D

(6)

(6)

Dc''-покрытие вначале представляется в виде

D =

=

и затем транспонируется. В итоге получают Dcумн-покрытие вида

и затем транспонируется. В итоге получают Dcумн-покрытие вида

D

(7)

(7)

Далее аналогично в течение 3˙n тактов n Dnумн-покрытий записываются в первую группу систолических полусумматоров 14, а n Dcумн-покрытий - во вторую группу систолических полусумматоров 15.

По окончании записи кубических покрытий на первый управляющий вход 21 поступает сигнал логического "0", который запрещает прохождение информации между соседними парами систолических полусумматоров 14, 15.

В режиме сложения, который устанавливается подачей сигнала логического "0" на второй управляющий вход 22, устройство работает как три независимых n-разрядных накапливающих сумматора. Сложение в устройстве происходит путем выполнения ряда операций над покрытиями (4) и (5), ранее записанными в соответствующие систолические полусумматоры 14, 15. Этот процесс осуществляется по циклам, каждый из которых состоит из трех тактов.

При подаче сигнала логической "1" на установочный вход 23 устройство устанавливается в исходное, нулевое состояние.

На первую группу n информационных входов 16 в первом такте каждого цикла поступает n-разрядное число, которое записывается в один из регистров 1-3. Каждый из регистров 1-3 является входным регистром для соответствующего накапливающего сумматора. Согласно временной диаграмме (фиг. 8) в один и тот же регистр 1-3 новое число поступает через каждые два цикла. Таким образом, на первую группу n информационных входов 16 поочередно поступают слагаемые на все три накапливающих сумматора. Одновременно на вторую группу n информационных входов 17 каждый цикл поступает число, состоящее из единиц, которое записывается в регистры 4-6.

Информация из регистров 1-3 проходит через соответствующую группу элементов И 7-9 и во втором такте каждого третьего цикла записывается в соответствующий блок 10-12 задержки. С помощью блоков 10-12 задержки осуществляется задержка i-го разряда слагаемого на i циклов (i = 1-n).

Далее в третьем такте каждого цикла открывается путь прохождения информации из блоков 10-12 задержки через группу блоков 13 мультиплексоров. Через i-ю группу блоков 13 мультиплексоров поочередно проходят i-е разряды слагаемых и в первом такте следующего цикла поступают на i-е систолические полусумматоры 14, 15. В итоге i-й разряд К-го слагаемого поступает на i-й разряд R-го систолического накапливающего сумматора, и в течение трех циклов в i-м систолическом полусумматоре 14 происходит вычисление i-го разряда переноса Pih(k), а в i-м систолическом полусумматоре 15 - вычисление i-го разряда суммы Sih(k), где

h =

,h=1-3.

,h=1-3.

Значения переноса Рih(k) и суммы Sih(k) появляются на h-х выходах второй группы трех информационных выходов 34 i-х систолических полусумматоров 14 и 15 в третьем такте третьего цикла после поступления i-го разряда К-го слагаемого на h-е входы второй группы трех информационных входов 29 i-х систолических полусумматоров 14 и1 5.

Значение переноса Pih(k) в следующем цикле поступает через (i+1)-й блок 13 мультиплексоров на h-е входы второй группы трех информационных входов 29 (i+1)-х систолических полусумматоров 14, 15. Значение суммы Sih(k) в следующем цикле поступает через i-й блок 13 мультиплексоров на h-е входы второй группы трех информационных входов 29 i-х систолических полусумматоров 14 и 15. В итоге происходит прибавление к предыдущему содержимому каждого сумматора нового слагаемого.

Поскольку i-й разряд К-го слагаемого поступает на i-й разряд h-го сумматора со сдвигом во времени на один цикл относительно поступления (i-1)-го разряда на (i-1)-й разряд h-го сумматора, поэтому в третьем такте каждого цикла, начиная с третьего цикла после поступления первого разряда К-го слагаемого, на h-х выходах второй группы трех информационных выходов 34 первой и второй групп систолических полусумматоров 14 и 15 поочередно появляются значения переноса Pih(k) и суммы Sih(k) К-го слагаемого.

На входы второй группы трех информационных входов 29 i-х систолических полусумматоров 14 и 15 i-е разряды трех слагаемых тоже поступают со сдвигом во времени на один цикл относительно друг друга. Поэтому значения переноса Pih(k+1) и суммы Sih(k+1) появляются на (h+1)-х выходах второй группы трех информационных выходов 34 i-х систолических полусумматоров 14 и 15 со сдвигом во времени на один цикл относительно появления значений переноса Pih(k) и суммы Sih(k) на h-х выходах второй группы трех информационных выходов 34 i-х систолических полусумматоров 14 и 15.

Таким образом в устройстве реализован конвейерный и матричный принципы сложения, т. е. по окончании вычисления значений переноса Pih(k)и суммы Sih(k) на входы i-х систолических полусумматоров 14 и 15 поступают i-е разряды очередного, (К+3)-го слагаемого, причем в устройстве происходит одновременное сложение трех независимых друг от друга последовательностей слагаемых.

В режиме умножения, который устанавливается подачей сигнала логической "1" на второй управляющий вход 22, устройство работает как три независимых n-разрядных устройства умножения с фиксированной запятой. В устройстве реализован способ умножения, начиная с младших разрядов множимого, со сдвигом вправо множителя и частичных сумм произведения.

При подаче сигнала логической "1" на установочный вход 23 устройство устанавливается в исходное, нулевое состояние.

На первую группу h информационных входов 16 в первом такте в течение трех циклов поступают три n-разрядных множимых, каждое из которых записывается в один из регистров 1-3 согласно временной диаграмме (фиг. 8). Одновременно на вторую группу n информационных входов 17 в первом такте в течение трех циклов поступают три n-разрядных множителя, каждый из которых записывается в один из регистров 4-6.

Следующая пара сомножителей поступает в регистры 1-6 через 3˙n циклов. Так как интервал между поступлениями пар сомножителей в устройстве составляет 3˙n циклов, поэтому тактовые сигналы по первым трем входам первой группы девяти тактовых входов 24 поступают с периодом 3˙n циклов, а тактовые сигналы по остальным входам этой группы входов поступают с таким же периодом, как и в режиме сложения согласно временной диаграммы (фиг. 8).

Поскольку умножение каждой пары сомножителей осуществляется в устройстве одинаково, поэтому в дальнейшем рассматривается операция умножения только для множимого А = аn...а1 и множителя В = bn...b1, которые записываются соответственно в регистр 1 и в регистр 4.

Если младший разряд b1 множителя В равен единице, то содержимое регистра 1 передается через группу элементов И 7 и во втором такте первого цикла записывается в блок 10 задержки. Если разряд b1 равен нулю, то в блок 10 задержки записываются все нули.

В третьем такте этого цикла происходит сдвиг вправо (в сторону младших разрядов) содержимого регистра 4 и теперь разряд b2 множителя В разрешает или запрещает через два цикла передачу множимого А через группу элементов И 7.

Аналогично в течение 3˙n циклов происходит сдвиг вправо содержимого регистра 4 и в блок 10 задержки записывается либо множимое А, либо нулевой вектор в зависимости от значений разрядов множителя В. Как и в режиме сложения, в блоке 10 задержки осуществляется задержка i-го разряда множимого А на i циклов (i = 1,..., n).

Далее в третьем такте каждого цикла открывается путь прохождения информации от блока 10 задержки через группу n блоков 13 мультиплексоров. Через i-ю группу блоков 13 мультиплексоров проходит разряд аi множимого и в первом такте следующего цикла поступает на i-е систолические полусумматоры 14 и 15.

Начиная с третьего цикла после начала поступления первого разряда а1 множимого и в течение последующих 3˙(n-1) циклов на первых выходах второй группы трех информационных выходов 34 первый и второй групп n систолических полусумматоров 14 и 15 формируется первая частичная сумма произведения:

S1(1) = S11(1) S21(1),..., Si1(1),..., Sn1(1), которая получается путем сложения множимого А или нулевого вектора и начального нулевого состояния устройства:

S

i=1-n

i=1-n

Начиная с третьего цикла после начала поступления второго разряда а2 множимого и в течение последующих 3˙(n-1) циклов на первых выходах второй группы информационных выходов 34 первой и второй групп n систолических полусумматоров 14 и1 5 формируется (n+1)-разрядная вторая частичная сумма:

S1(2) = S11(2), S21(2),..., Si1(2),..., Sn1(2), Sn+11(2), которая получается путем сложения множимого А или нулевого вектора со сдвинутой на один разряд вправо первой частичной суммой S1(1)произведения:

S

i=1-n-1

i=1-n-1

Поскольку младший разряд S11(2) второй частичной суммы S1(2)вычислять не требуется, поэтому на первых выходах второй группы трех информационных выходов 34 первой и второй групп n систолических полусумматоров 14 и 15 формируется лишь n старших разрядов этой частичной суммы.

По аналогичному принципу формируется (n + j - 1)-разрядная j-я частичная сумма S1(j): на первых выходах второй группы трех информационных выходов 34 первой и второй групп n систолических полусумматоров 14 и 15 формируется лишь n старших разрядов этой частичной суммы, а ее младшие разряды сдвигаются вправо на один разряд в каждом цикле (j = 1-n).

Одновременно в устройстве происходит умножение еще двух пар сомножителей, которые записываются в регистры 2, 5 и 3, 6 и затем поступают соответственно на вторые и третьи входы второй группы трех информационных выходов 34 первой и второй групп n систолических полусумматоров 14 и 15.

Значения отдельных разрядов каждого произведения формируются со сдвигом во времени на один цикл относительно друг друга. Значения одноименных разрядов трех произведений также формируются со сдвигом во времени на один цикл относительно друг друга.

Таким образом, в устройстве реализован конвейерный и матричный принципы умножения, т. е. в одном умножителе происходит одновременное сложение всех частичных сумм произведения, а в устройстве в целом - одновременное умножение трех независимых друг от друга пар сомножителей.

Блок 13 мультиплексоров работает следующим образом.

Перед началом работы устройства все блоки 13 мультиплексоров устанавливаются в исходное состояние по приходе сигнала на установочный вход 46. В исходном состоянии в i-м блоке 13 мультиплексоров кольцевой распределитель 70 импульсов имеет на h-м (h = 1-3) выходе значение логической "1", а на остальных выходах - значение логического "0", где

h =

Во время работы устройства в третьем такте каждого цикла на тактовый вход 47 приходит сигнал и в результате импульс поочередно появляется на каждом из выходов кольцевого распределителя 70 импульсов.

В режиме сложения потенциал логического "0" на управляющем входе 45 разрешает прохождение информации на группу трех информационных выходов 48 поочередно от второй группы трех информационных входов 39, от пятой группы трех информационных входов 42-44 и от первой группы трех информационных входов 38.

В режиме умножения потенциал логической "1" на управляющем входе 45 разрешает прохождение информации на группу трех информационных выходов 48 поочередно от четвертой группы трех информационных входов 41, от третьей группы трех информационных входов 40 и от пятой группы трех информационных входов 42-44.

Три мультиплексора, каждый из которых образован группой из шести элементов И 72-74 и соответствующим элементом ИЛИ 75-77, коммутируют сигналы с одноименных групп информационных входов со сдвигом во времени на один цикл относительно друг друга.

Каждый из систолических полусумматоров первой 14 и второй 15 групп работают следующим образом.

В режиме программирования при наличии разрешающего сигнала (логической "1") на управляющем входе 30 происходит поступление кубических покрытий через первую группу четырех информационных входов 28.

В режимах сложения или умножения в i-х систолических полусумматорах 14 и 15 осуществляется вычисление функций (2) путем выполнения ряда операций над записанными ранее их кубическими покрытиями.

Традиционный метод вычисления бульевой функции f на входном наборе G ее аргументов с помощью комбинационной схемы можно интерпретировать как установление принадлежности входного набора G множеству наборов, на которых функция f принимает значение логической "1".

При использовании кубического представления булевых функций установление принадлежности входного набора G указанному множеству наборов может быть выполнено аналитически с помощью операции пересечения кубов. По определению операция пересечения куба а = а1 а2... аn и куба β=β1β2... βnобозначается как γ=a∩β и служит для выделения куба γ=γ1γ2...γn, являющегося общей частью кубов а и β. Значение компоненты γiопределяется по таблице, как γi=ai∩βi(j=1-n).

Знак 0 означает пустое пересечение. Например, если

а = 1 х 1 х 01, β= х 01 101, то куб γ равен

∩

Входной набор G принадлежит множеству наборов, на которых булева функция f принимает значение логической "1" (логического "0", если имеет место непустое пересечение набора G хотя бы с одним кубом D-покрытия (пустое пересечение набора G со всеми кубами D-покрытия) этой функции.

Следовательно, значение функции переноса fn'' (2) на h-м выходе второй группы трех информационных выходов 34 i-го систолического полусумматора 14 в режиме сложения при поступлении входного набора Ghможет быть определено следующим образом:

f (G

(G

(8) где d

(8) где d ;ε=1-4, h = 1-3.

;ε=1-4, h = 1-3.

Значение функции суммы fc'' (2) на h-м выходе второй группы трех информационных выходов 34 i-го систолического полусумматора 15 в режиме сложения при поступлении входного набора Ghi может быть определено следующим образом:

f (G

(G

(9) где d

(9) где d ;ε=1-4,h = 1-3.

;ε=1-4,h = 1-3.

Правила (8) и (9) справедливы также и для покрытий Dnсл и Dссл.

Аналогично определяется в режиме умножения значение функции fn''(fc'') на h-м выходе второй группы трех информационных выходов 34 i-х систолических полусумматоров 14 и 15.

Отличительной особенностью выполнения операций над кубами является возможность одновременной и независимой обработки отдельных компонент кубов. Благодаря указанной особенности процесс выполнения операции пересечения входных наборов аргументов булевой функции с кубами кубического покрытия этой функции распараллеливается с помощью матрицы ячеек 49.

В режиме сложения последовательность k-разрядных входных наборов

G1, G2, G3, . .., Gk,... образуется из трех независимых друг от друга последовательностей

G1, G4, G7,..., Gk,...

G2, G5, G8,..., Gk+1,... (10)

G3, G6, G9,..., Gk+2,..., которые поступают на входы трех систолических сумматоров следующим образом.

На входы h-го систолического сумматора поступает входной набор

Gh = (Gh1Gh2,..., Ghi,..., Ghn), где

h =

h=1-3

h=1-3

На h-й вход второй группы трех информационных входов 29 i-х систолических полусумматоров 14 и 15 в i-м цикле работы устройства поступает набор

Ghi = (pi-

После поступления компоненты pi-1h-3 в третьем такте этого цикла на h-м выходе второй группы трех информационных выходов 34 i-го систолического полусумматора 14 формируется значение компоненты pih, а на h-м выходе второй группы трех информационных выходов 34 i-го систолического полусумматора 15 - значение компоненты Sih. На следующем цикле на h-й вход второй группы трех информационных входов 29 i-х систолических полусумматоров 14 и 15 поступает новый набор:

Gih+3 = (pi-1h aih+3Sih), начиная с компоненты Sih.

Компоненты набора Ghi на h-й вход второй группы трех информационных входов 29 i-х систолических полусумматоров 14 и 15 поступают раньше на один цикл относительно поступления одноименных компонент набора Gh+1i на (h+1)-й вход второй группы трех информационных входов 29 i-х систолических полусумматоров 14 и 15, а также относительно поступления одноименных компонент набора Ghi+1 на h-й вход второй группы трех информационных входов 29 (i+1)-х систолических полусумматоров 14 и 15.

Процесс вычислений в матрице вычислительных ячеек 49 i-го систолического полусумматора 14 начинается с активизации вычислительных ячеек 49 первой строки.

В первом такте i-го цикла работы на вход 54 указанных вычислительных ячеек 49 поступает компонента Sih-3 входного набора Ghi, а также происходит циклический сдвиг сверху вниз по столбцам содержимого ячеек 49. Вследствие этого сдвига на входы 53 ячеек 49 первой строки поступают компоненты первого куба покрытия Dnсл. На выходе 57 указанных ячеек 49 получаются результаты операций пересечения компоненты Sih-3 c компонентами первого куба покрытия Dnсл.

В первом такте i-го цикла работы первый элемент 50 свертки устанавливается в исходное состояние, и во втором такте по группе четырех информационных входов 58 в него поступает результат из ячеек 49 и запоминается.

В последующих двух циклах работы на входы 53 ячеек 49 первой строки поступают компоненты второго и третьего куба покрытия Dnсл, а на входы 54 - компоненты aih и pih-3. Полученные результаты операций пересечения от ячеек 49 первой строки также запоминаются в первом элементе 50 свертки, а в третьем такте (i+2)-го цикла на выходе 63 этого элемента 50 свертки формируется общий результат операции пересечения входного набора Ghi со всеми кубами покрытия Dnсл, т.е. вычисляется функция fn''(Ghi) согласно правилу (8) (h = 1).

С задержкой на один цикл (два цикла) на выходе 63 второго (третьего) элемента 50 свертки вычисляется функция fn''(G2i) (fn''(G3i)). На следующем цикле после вычисления функции fn''(G3i) на выходе 63 первого элемента 50 свертки i-го систолического полусумматора 14 вычисляется функция fn''(G4i) и т.д.

Одновременно с вычислением функций fn''(Ghi) аналогично происходит вычисление функций fc''(Ghi) согласно правилу (9) на выходах 63 элемента 50 свертки i-го систолического полусумматора 15.

Таким образом, в устройстве происходит накопление сумм трех последовательностей (10).

Общее время сложения n-разрядного числа к ранее накопленной сумме в устройстве составляет n+2 циклов.

В режиме умножения на входы трех систолических сумматоров поступают три последовательности наборов (10), причем в каждой последовательности n наборов

Gh, Gh+3,..., Gh+3(n-1)-1) связан с одной парой сомножителей.

На h-й вход второй группы трех информационных входов 29 i-х систолических полусумматоров 14 и 15 в i-м цикле работы устройства поступает набор

Ghi = (aihSi+1h-3 Pih-3), начиная с компоненты Рih-3 переноса с i-го разряда. Затем на этот же вход в течение последующих двух циклов поступают компоненты Si+1h+3(i+1)-го разряда предыдущей суммы и компонента ahi i-го разряда множимого. Поскольку исходное состояние устройства принимается нулевым, поэтому в i-м цикле работы Si+1h-3 = 0 (i = 1 - n - 1) и Рih-3 = 0(i = 1 - n).

После поступления компоненты aih в третьем такте этого цикла на h-м выходе второй группы трех информационных выходов 34 i-го систолического полусумматора 14 формируется значение компоненты Pih, а на h-м выходе второй группы трех информационных выходов 34 i-го систолического полусумматора 15 - значение компоненты Sih. На следующем цикле на h-й вход второй группы трех информационных входов 29 i-х систолических полусумматоров 14 и 15 поступает новый набор

Gih+3 = (aih+3Si+1hРih), начина с компоненты Рih.

Процесс вычислений в матрице ячеек 49 i-х систолических полусумматоров 14 и 15 в режиме умножения осуществляется так же, как и в режиме сложения. Общее время умножения двух n-разрядных чисел в устройстве составляет 4˙n-1 циклов.

Вычислительная ячейка 49 работает следующим образом.

В первом такте каждого цикла по входу 53 в D-триггер 78 записывается очередная компонента dεh куба dε=(dε1dε2dε3) D-покрытия. Одновременно по входу 54 в D-триггере 79 записывается компонента qihнабора Ghi= (g1hg2hg3h). По окончании записи соответствующей информации в D-триггеры 78 и 79 выполняется операция пересечения компонент:

g

Поскольку значениями компонент gih и dεh могут быть только ноль и единица, поэтому кубическая операция пересечения в ячейке 49 совпадает с логической операцией неравнозначности:

g

Таким образом, на выходе 57 ячейки 49 будет значение логической "1" (логического "0"), если имеется пустое (непустое) пересечение компонент gih и dεh.

В i-х систолических полусумматорах 14 и 15 h-й элемент 50 свертки работает следующим образом.

Перед началом работы устройства на установочный вход 59 приходит сигнал, который устанавливает D-триггер 86 в нулевое состояние.

В первом такте i-го цикла работы по сигналу, поступающему по входу 62, RST-триггеры 81-84 устанавливаются в нулевое состояние.

В ε-й RST-триггер 81-84 в конце первого такта i-го, (i+1)-го и (i+2)-го циклов по группе четырех информационных входов 58 поступает результат операции пересечения компонент gih и dεh от ячейки 49, находящейся в h-й строке и в ε-м столбце (h = 1-3; ε= 1-4). Этот результат поступает на S-вход ε-го RST-триггера 81-84, и если

g

Во втором такте (i+2)-го цикла в ε-м RST-триггере 81-84 формируется результат пересечения всех компонент набора Ghi с компонентами ε-го куба dε кубического покрытия. При пустом (непустом) пересечении набора Ghi с кубом dε ε-й RST-триггер 81-84 находится в единичном (нулевом) состоянии.

Если хотя бы один RST-триггер 81-84 находится в нулевом состоянии, то в третьем такте (i+2)-го цикла по приходе тактового сигнала на вход 61 D-триггера 86 устанавливается в единичное состояние. Если все RST-триггеры 81-84 находятся в единичном состоянии, то в третьем такте (i+2)-го цикла D-триггер 86 устанавливается в нулевое состояние.

Таким образом, в течение трех циклов формируется результат операции пересечения входного набора Ghi с кубами кубического покрытия булевой функции согласно правилу (8) или (9).

В первом такте (i+3)-го цикла по сигналу, поступающему по входу 62, RST-триггеры 81-84 устанавливаются в нулевое состояние и начинается формирование операции пересечения очередного входного набора с кубами кубического покрытия булевой функции. Сигналы на вход 62 приходят через каждые три цикла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Систолический автомат | 1990 |

|

SU1732340A1 |

| Систолическая структура для вычисления логических функций | 1989 |

|

SU1654809A1 |

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ | 1991 |

|

RU2011215C1 |

| Устройство для вычисления булевых функций | 1988 |

|

SU1683002A1 |

| Ячейка однородной структуры | 1990 |

|

SU1778757A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ЧИСЛОВЫХ МАТРИЦ | 1991 |

|

RU2022334C1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ МАТРИЦ КАРТИН-ИЗОБРАЖЕНИЙ | 1991 |

|

RU2018916C1 |

Изобретение относится к вычислительной технике и может быть применено при построении арифметических устройств высокопроизводительных ЭВМ. Целью изобретения является расширение функциональных возможностей устройства за счет того, что оно работает как в режиме умножения, так и в режиме сложения, упрощение процедур наращиваемости устройства и взаимозаменяемости его блоков. Устройство может работать как три независимых n-разрядных накапливающих сумматора или три независимых n разрядных умножителя. В режиме умножения (сложения) в регистры 1-3 записываются множимые (слагаемые), а в регистры 4-6 - множитель (единичный вектор). Затем операнды через группы элементов И 7-9, блоки 10-12 задержки и n блоков 13 мультиплексоров поступают на первую группу n систолических полусумматоров 14 и на вторую группу n систолических полусумматоров 15, где происходит вычисление искомых сумм и произведений. Суммы и произведения в устройстве вычисляются путем выполнения операций над кубическими покрытиями функции переносов и функции суммы, которые ранее, в режиме программирования, записываются соответственно в первую 14 и вторую 15 группы систолических полусумматоров. 3 з.п. ф., 1 табл., 9 ил.

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-10-30—Публикация

1992-01-31—Подача