Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных машинах для преобразования чисел из минимальной формы избыточной системы счисления.

Известна структурная схема дешифратора четырехразрядного кода (1). Основной недостаток аналога - низкая помехоустойчивость из-за неспособности контроля поступающей информации и из-за неспособности использовать помехоустойчивые коды.

Наиболее близкой к предлагаемому по технической сущности является схема трехразрядного линейного дешифратора, которая состоит из блока входов элементов И и блока выходов, причем второй, четвертый и шестой являются инверсными соответственно по отношению к первому, третьему и пятому входам, входы дешифратора составляют блок входов, первый вход блока входов соединен с первыми входами пятого, шестого, седьмого и восьмого элементов И блока элементов И, второй вход соединен с первыми входами первого, второго, третьего и четвертого элементов И, третий вход соединен с вторыми входами третьего, четвертого, седьмого и восьмого элементов И, четвертый вход соединен с вторыми входами первого, второго, пятого и шестого элементов И, пятый вход соединен с третьими входами второго, четвертого, шестого и восьмого элементов И, шестой вход соединен с третьими входами первого, третьего, пятого и седьмого элементов И, выходы элементов И составляют блок выходов и являются выходами дешифратора (2).

Основные недостатки прототипа низкая помехоустойчивость из-за неспособности использовать коды избыточных систем счисления и необнаружения ошибок в поступающей информации.

Цель изобретения - повышение помехоустойчивости и достоверности за счет использования (дешифрации) кодов минимальной формы t1 - избыточной системы счисления и за счет обнаружения ошибок в поступающей информации.

Сложность современных вычислительных машин приводит к большому количеству отказов, нарушающих их работоспособность, сбоев вызывающих кратковременное нарушение работоспособности, перемежающихся отказов, многократно возникающих сбоев одного и того же характера. Одним из основных путей повышения надежности вычислительной техники является введение избыточности. Наиболее эффективным является введение естественной избыточности. Например, путем использования минимальной формы t1 - избыточной системы счисления.

Любое натуральное n-разрядное число А представлено в избыточной системе счисления многочленом

A= asΨ(s)

asΨ(s)

(1)

Условие:

a =

=

задает минимальную форму изображения чисел, характеризующуюся в общем случае наличием в пяти соседних разрядах не более одной единицы. Мощность n-разрядного кода минимальной формы определяется значением Ψ (n+1), а число единиц в коде выражением

задает минимальную форму изображения чисел, характеризующуюся в общем случае наличием в пяти соседних разрядах не более одной единицы. Мощность n-разрядного кода минимальной формы определяется значением Ψ (n+1), а число единиц в коде выражением

wм(n)=wм(n-1)+wм(n-s)+ Ψ (n-1);

wм(0)=wм(1)=0; wм(2)=1.

Дешифрация преобразователем производится обратным преобразованием условия (2). Контроль ошибок в поступающих двоичных последовательностях производится за счет организации связей таким образом, что искаженная информация при поступлении на входы преобразователя не проходит на выходы последнего, за исключением случая, когда искажение приводит к трансформации одной разрешающей комбинации в другую. Но применяемая система счисления с естественной избыточностью значительно снижает вероятность такого события, поэтому вероятность обнаружения ошибки сильно возрастет. Т.е. контроль осуществляется сравнением наличия сигнала на входах и на выходах устройства. Если сигналы на входах и на выходах отсутствуют, или, если сигналы на входах и на выходах есть, то информация без ошибок. Если на входах есть сигналы, а на выходах их нет, значит информация искажена. Функции сравнения выполняет элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. Сигнал о поступлении искаженной двоичной комбинации элемент ИСКЛЮЧАЮЩЕЕ ИЛИ передает на контрольный выход. Информация, снимаемая с контрольного выхода, может использоваться для вычисления интенсивности ошибок, для стирания записанной искаженной информации и для переспроса в системах с обратной связью.

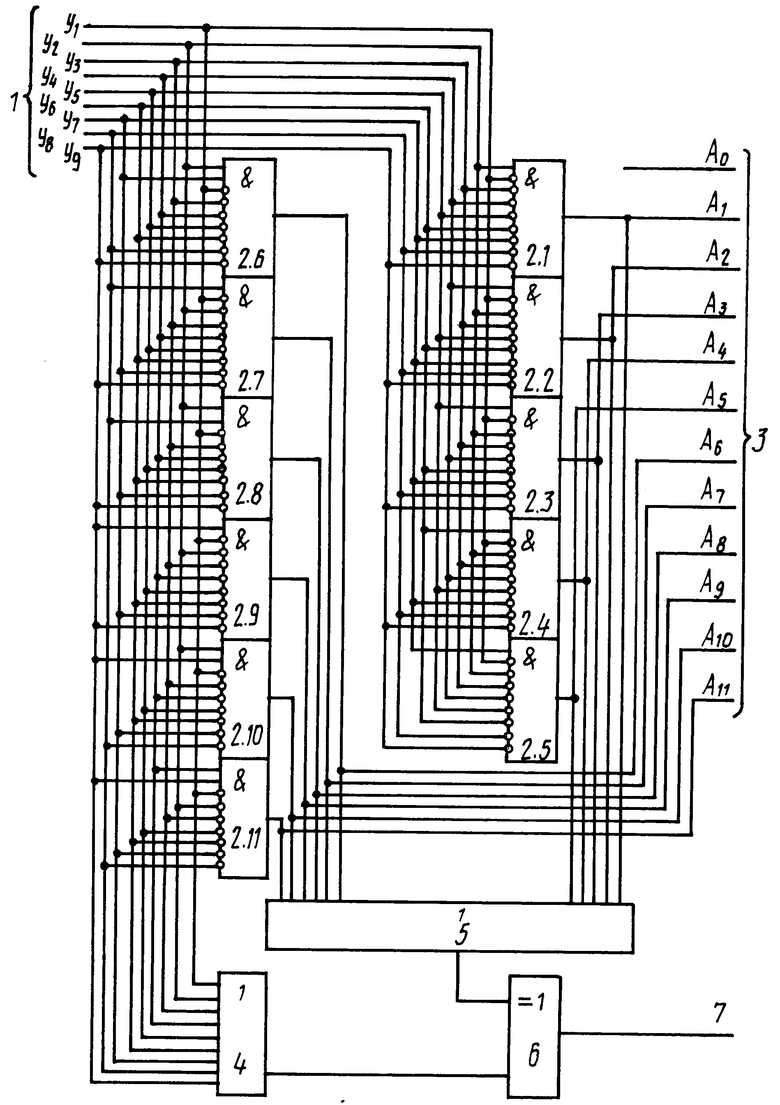

На чертеже изображена структурная схема преобразователя кодов (для n= 9), которая содержит входы 1, элементы И 21-211, выходы 3, первый элемент ИЛИ 4, второй элемент ИЛИ 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и контрольный выход 7.

Элементы И 21-211 производят дешифрацию неискаженной комбинации минимальной формы t1-избыточной системы счисления в унитарный код числа.

На выход 3 выдается унитарный код числа из преобразователя.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6 формирует единичный сигнал о поступлении на входы преобразователя искаженной комбинации.

Контрольный выход 7 выдает единичный сигнал о поступлении на входы преобразователя искаженной комбинации.

Преобразователь работает следующим образом.

Пусть на входы преобразователя информации не поступает или поступила нулевая комбинация. На выходах первого элемента ИЛИ 4 и второго элемента ИЛИ 5 будут нулевые сигналы и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6 не формирует сигнал о поступлении искаженной комбинации на входы 1.

Если на входы 1 поступила не нулевая неискаженная комбинация, то на выходах 3 преобразователя установится унитарный код числа, при этом с выхода первого элемента ИЛИ 4 и с выхода второго элемента ИЛИ 5 соответственно на первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 поступят единичные сигналы и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6 не сформирует сигнал о поступлении искаженной комбинации.

Если на входы 1 поступила не нулевая искаженная комбинация, то на выходах 3 преобразователя установится нулевая комбинация. На выходе первого элемента ИЛИ 4 появится единичный сигнал, а на выходе второго элемента ИЛИ 5 появится нулевой сигнал и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6 сформирует единичный сигнал, фиксирующий поступление искаженной комбинации на входы 1.

Контрольный выход 7 выдаст из преобразователя сигнал, сформированный элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 6.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕШИФРАЦИИ ФИБОНАЧЧИЕВЫХ P-КОДОВ | 1992 |

|

RU2050691C1 |

| Устройство приведения кодов Фибоначчи к минимальной форме | 1986 |

|

SU1427577A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОРРЕКТИРУЮЩЕЙ СИСТЕМЕ СЧИСЛЕНИЯ | 1990 |

|

RU2022341C1 |

| Шифратор фибоначчиевых р-кодов | 1987 |

|

SU1483644A1 |

| Устройство для сравнения чисел | 1988 |

|

SU1520506A1 |

| Устройство для распределения заданий процессорам | 1989 |

|

SU1615721A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В СИМВОЛЬНОМ КОДЕ | 1991 |

|

RU2021644C1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Преобразователь кодовых форм | 1988 |

|

SU1545329A1 |

| Устройство для контроля структурного кода | 1990 |

|

SU1748256A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных машинах для преобразования чисел из минимальной формы избыточной системы счисления. Цель изобретения - повышение помехоустойчивости и достоверности за счет использования (дешифрации) кодов минимальной формы t1 -избыточной системы счисления и за счет обнаружения ошибок в поступающей информации. Эта цель достигается путем введения двух элементов ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, контрольного выхода и соответствующих связей. Предлагаемый преобразователь может преобразовывать числа из минимальной формы t1 -избыточной системы счисления в унитарный код чисел и обнаруживать ошибки. 1 ил.

ПРЕОБРАЗОВАТЕЛЬ КОДОВ, содержащий первый - восьмой элементы И, выходы которых являются одноименными информационными выходами преобразователя, первые инверсные входы первого, третьего, пятого и седьмого элементов И объединены и являются первым входом преобразователя, первые прямые входы шестого и восьмого элементов И объединены и являются вторым входом преобразователя, вторые инверсные входы первого и пятого элементов И и первые инверсные входы второго и шестого элементов И объединены и являются третьим входом преобразователя, отличающийся тем, что, с целью повышения помехоустойчивости и достоверности преобразователя, в него введен девятый - одиннадцатый элементы И, элементы ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является контрольным выходом преобразователя, выходы первого и второго элементов ИЛИ соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые инверсные входы второго и шестого элементов И и первые инверсные входы четвертого, восьмого - одиннадцатого элементов И и первый вход первого элемента ИЛИ подключены к первому входу преобразователя, прямой вход первого элемента И, первый прямой вход десятого элемента И, вторые инверсные входы третьего, четвертого, седьмого, девятого и одиннадцатого элементов И, третьи инверсные входы второго и пятого элементов И и второй вход первого элемента ИЛИ подключены к второму входу преобразователя, третьи инверсные входы третьего, четвертого, седьмого, девятого и одиннадцатого элементов И, вторые инверсные входы восьмого и десятого элементов И и третий вход первого элемента ИЛИ подключены к третьему входу преобразователя, третьи инверсные входы первого, шестого, восьмого и десятого элементов И, четвертые инверсные входы третьего, четвертого, пятого, седьмого и девятого элементов И, прямой вход второго элемента И, первый прямой вход одиннадцатого элемента И и четвертый вход первого элемента ИЛИ объединены и являются четвертым входом преобразователя, четвертые инверсные входы первого, второго, шестого, восьмого, десятого и одиннадцатого элементов И, пятые инверсные входы четвертого, пятого, седьмого и девятого элементов И, прямой вход третьего элемента И и пятый вход первого элемента ИЛИ объединены и являются пятым входом преобразователя, пятые инверсные входы первого, второго, третьего, шестого, восьмого, десятого и одиннадцатого элементов И, шестые инверсные входы пятого, седьмого, девятого элементов И, прямой вход четвертого элемента И и шестой вход первого элемента ИЛИ объединены и являются шестым входом преобразователя, шестые инверсные входы первого - четвертого,восьмого, десятого и одиннадцатого элементов И, седьмые инверсные входы седьмого и девятого элементов И, прямой вход пятого элемента И, второй прямой вход шестого элемента И и седьмой вход первого элемента ИЛИ объединены и являются седьмым входом преобразователя, седьмые инверсные входы первого - пятого, десятого и одиннадцатого элементов И, шестой инверсный вход шестого элемента И, прямой вход седьмого элемента И, второй прямой вход восьмого элемента И и восьмой вход первого элемента ИЛИ объединены и являются седьмым входом преобразователя, восьмые инверсные входы первого - пятого, седьмого и девятого элементов И, седьмые инверсные входы шестого, восьмого, десятого и одиннадцатого элементов И, прямой вход девятого элемента И, вторые прямые входы десятого и одиннадцатого элементов И и девятый вход первого элемента ИЛИ объединены и являются девятым входом преобразователя, первый - одиннадцатые входы второго элемента ИЛИ подключены к выходам одноименных элементов И,выходы девятого - одиннадцатого элементов И являются одноименными информационными выходами преобразователя.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Самофалов К.Г | |||

| Цифровые электронные вычислительные машины | |||

| Киев, Вища школа, 1983, с.117, рис.3,4. | |||

Авторы

Даты

1994-11-15—Публикация

1991-07-15—Подача