Изобретение относится к автоматике и вычислительной технике и может быть использовано в гибких вычислительных машинах для преобразования информации из минимальной формы в оптимальную t, системы счисления.

Целью изобретения является расширение области применения за счет преобразования информации из минимальной формы в оптимальную форму t, системы счисления.

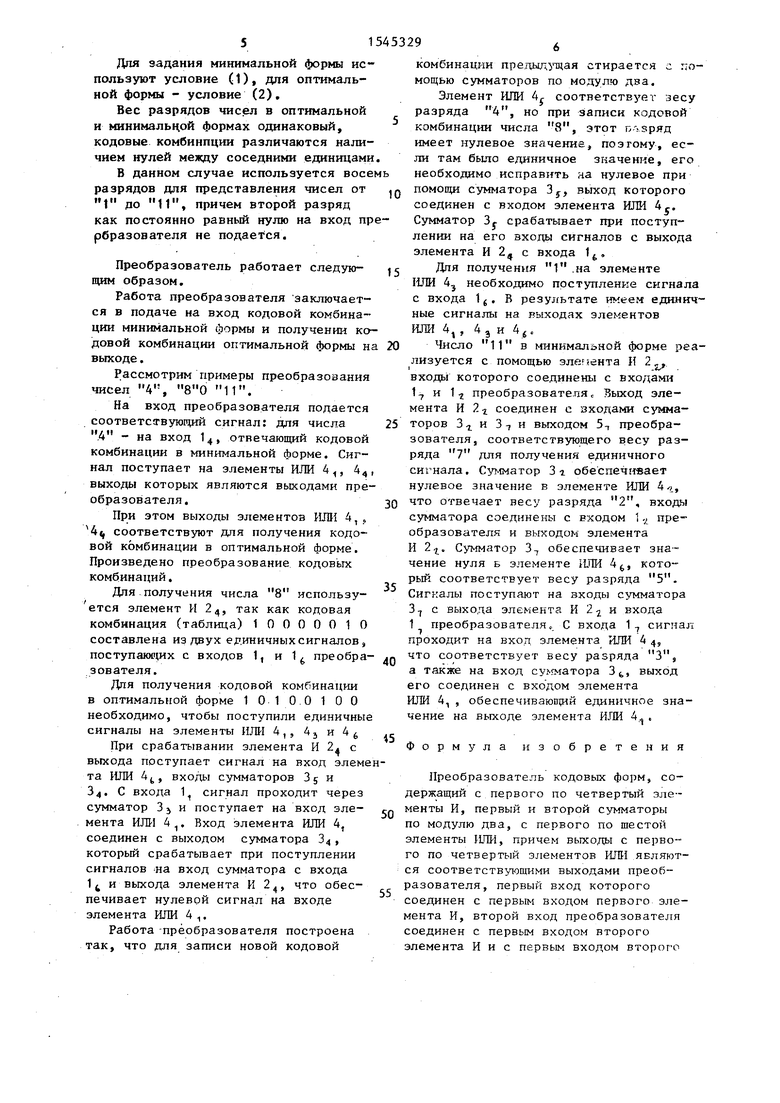

На чертеже представлена схема комбинационного преобразователя кодовых форм (для п 8, п - разрядность ко- да).

Преобразователь содержит с первого по седьмой входы 1, - 17 соответственно, с первого по четвертый элементы И 2j - 2 соответственно, с первого по восьмой сумматоры З-i - 3j соответственно, с первого по шестой элементы ИЛИ 4t - 4t соответственно, с первого по седьмой выходы 5, - 57 соответственно.

Лобое натуральное число А в избыточной t, системе счисления представлено многочленно

5.1

),

где п - разрядность кода, y(s) - вес s-ro разряда кода, ц, (s) - V,(s-2) + v,(s-3)i V (0) V(D - I

Для представления натурального ряда чисел в минимальной форме имеет место соотношение

1, при у,(з+2) 4 А - X akvk

v(s+2)/„

0, при if,(s+1) - A- jr a ,4iK( 1)

причем минимальная форма характеризуется в общем случае наличием в пяти соседних разрядах не более одной единицы. Для представления натурального ряда чисел в оптимальной форме имеет место соотношение

1 , при Ф,( Ks+1); О, при Ф,

п ,(s) Ј А - 2 а„ VK

кг

,(s) А - И akvk,(2)

L, «

KrS

где «I /s) - вес s-го разряда в оптимальной форме

Ф,(з) Ф, (в - 2) + ,(s -3) + 1,

причем в общем случае оптимальная форма характеризуется наличием между соседними единицами не менее одного и не более двух нулей.

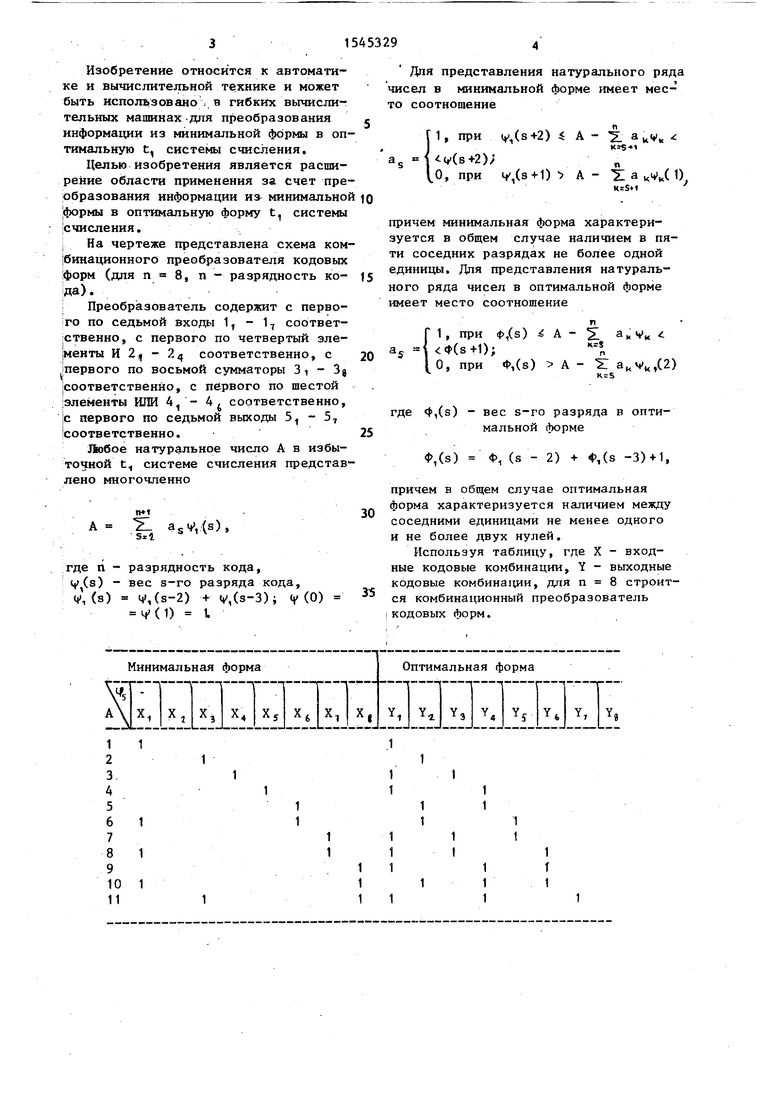

Используя таблицу, где X - входные кодовые комбинации, Y - выходные кодовые комбинации, для п 8 строится комбинационный преобразователь кодовых форм.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный преобразователь форм кода | 1988 |

|

SU1559413A1 |

| Устройство для определения направления и угла поворота вращающегося объекта | 1991 |

|

SU1786441A1 |

| Устройство для преобразования двоичного равновесного кода в двоичный позиционный код | 1988 |

|

SU1557684A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Преобразователь перемещения в код | 1986 |

|

SU1405115A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2013 |

|

RU2541869C1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1080176A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для декодирования кода Рида-Соломона /15,12/ | 1985 |

|

SU1290540A1 |

Изобретение относится к атоматике и вычислительной технике и может быть использовано в гибких АСУ и ЭВМ для проебразования минимальной формы числа в оптимальную форму этого же числа. Изобретение позволяет расширить область применения за счет преобразования информации из минимальной формы в оптимальную форму T1 системы счисления. Преобразователь для восьмиразрядного числа содержит элементы И 21 - 24, сумматоры 31 - 38 по модулю два, элементы ИЛИ 41 - 46, входы 11 - 17 преобразователя, выходы 51 - 57 преобразователя. При подаче на входы 11 - 17 кода минимальной формы число единиц в (S-1)-м, (S-6)-м разрядах этого кода посредством элементов И 2 и сумматоров 3 по модулю два преобразуется в одну единицу, поступающую на соответствующие входы элементов ИЛИ 4, выходы которых связаны с выходами 51 - 57 преобразователя для получения оптимальной формы числа. Комбинационный преобразователь кодовых форм может применяться в гибких вычислительных средствах с перестраиваемой информационной структурой. 1 ил., 1 табл.

1

1

1

1

Для задания минимальной формы используют условие (1), для оптимальной формы - условие (2).

Вес разрядов чисел в оптимальной и минимальной формах одинаковый, кодовые комбинации различаются наличием нулей между соседними единицами.

В данном случае используется восемь разрядов для представления чисел от J 1 до 11, причем второй разряд как постоянно равный нулю на вход пре- рбразователя не подается.

15

Преобразователь работает следующим образом.

Работа преобразователя заключается в подаче на вход кодовой комбинации минимальной формы и получении кодовой комбинации оптимальной формы на 20 выходе.

Рассмотрим примеры преобразования чисел 4, 11.

На вход преобразователя подается соответствующий сигнал: для числа 4 - на вход 14, отвечающий кодовой комбинации в минимальной Лорме. Сигнал поступает на элементы ИЛИ 4.,, 4«, выходы которых являются выходами преобразователя .

При этом выходы элементов ИЛИ 4,. 4 соответствуют для получения кодовой комбинации в оптимальной форме. Произведено преобразование кодовых комбинаций.

Для получения числа 8 чспочьзу- ется элемент И 24, так как кодовая комбинация (таблица) 1 О О О О О 1 О составлена из двух единичных сигналов,

30

35

комбинации числа 8, этот с.ряд имеет нулевое значение, поэтому, ес ли там было единичное эг.аченме, ег необходимо исправить ча нулевое при помощи сумматора 3f) выход которого соединен с входом элемента ИЛИ 4. Сумматор 3, срабатывает при поступлении на его входы сигналов с выход элемента И 24 с входа 1t.

Для получения 1 на элементе

ИЛИ 4Э необходимо поступление сигна с входа 14. В результате един ные сигналы на рыходах элементов ИЛИ 4, , 43 и 4«.

Число 11 в минимальной форме р лизуется с помощью элемента И 2, входы которого соединены с входами 1 -, и 1 г преобразоватепя, Вькод элемента И 2г соединен с входами сумма 25 торов 3 г и 37 и выходом 5-, преобразователя, соответствующего весу раз ряда 7 для получения единичного

си.нала. Сумматор Зг обеспечивает нулевое значение в шементе ИЛИ 4-, что отвечает весу разряда 2, вход сумматора соединены с жодом 1 . пре образователя и внходом элемента И 2г. Сумматор 37 обеспечивает значение нуля ь эчементе ЫИ 4Ь, который соответствует весу разряда 5. Сиггалы поступают на пходы сумматор 37 с выхоча элемента И 2t и нхода 1 преобразователя. С входа 17 сигм проходит на вход элемента ИЛИ 4 j,

поступающих с входов 1, и 1 преобра- 4Q что соответствует весу разряда 3,

а также на вход cvi матора 3t, выход его соединен с входом элемента ИЛИ 4, , обеспечивающий единичное зн чение на выходе элемента ИШ1 Д1 .

эователя.

Для получения кодовой комГинации в оптимальной форме 10100100 необходимо, чтобы поступили единичные

сигналы на элементы ИЛИ 4.

и 4

б При срабатывании элемента И 2« с

выхода поступает сигнал на вход элемента ИЛИ 4t, входы сумматоров 3$ и 3.4. С входа 1, сигнал проходит через сумматор 3} и поступает на вход элемента ИЛИ

1

Вход элемента ИЛИ 4,

соединен с выходом сумматора 34, который срабатывает при поступлении сигналов на вход сумматора с входа 1t и выхода элемента И 24, что обеспечивает нулевой сигнал на входе элемента ИЛИ 4 ,.

Работа преобразователя построена так, что для записи новой кодовой

комбинации предыдущая стирается , :,о- мощью сумматоров по моцулч) .

Элемент ИЛИ 4f соответструе jecy

разряда

но при записи к довой

Q

5

комбинации числа 8, этот с.ряд имеет нулевое значение, поэтому, если там было единичное эг.аченме, его необходимо исправить ча нулевое при помощи сумматора 3f) выход которого соединен с входом элемента ИЛИ 4. Сумматор 3, срабатывает при поступлении на его входы сигналов с выхода элемента И 24 с входа 1t.

Для получения 1 на элементе

ИЛИ 4Э необходимо поступление сигнала с входа 14. В результате единичные сигналы на рыходах элементов ИЛИ 4, , 43 и 4«.

Число 11 в минимальной форме реализуется с помощью элемента И 2, входы которого соединены с входами 1 -, и 1 г преобразоватепя, Вькод элемента И 2г соединен с входами сумма- 5 торов 3 г и 37 и выходом 5-, преобразователя, соответствующего весу разряда 7 для получения единичного

си.нала. Сумматор Зг обеспечивает нулевое значение в шементе ИЛИ 4-, что отвечает весу разряда 2, входы сумматора соединены с жодом 1 . преобразователя и внходом элемента И 2г. Сумматор 37 обеспечивает значение нуля ь эчементе ЫИ 4Ь, который соответствует весу разряда 5. Сиггалы поступают на пходы сумматора 37 с выхоча элемента И 2t и нхода 1 преобразователя. С входа 17 сигмал, проходит на вход элемента ИЛИ 4 j,

что соответствует весу разряда 3,

а также на вход cvi матора 3t, выход его соединен с входом элемента ИЛИ 4, , обеспечивающий единичное значение на выходе элемента ИШ1 Д1 .

Формула изобретения

Преобразователь кодовых форм, содержащий с первого по четвертым i ie - менты И, первый и второй сумматоры по модулю два, с первого rio шестой элементы ИЛИ, причем выходы с первого по четвертый элементов ИЛИ являются соответствуюшими выходами преобразователя, первый вход которого соединен с первым входом первого элемента И, второй вход преобратователя соединен с первым входом второго элемента И и с первым входом втором

сумматора по модулю два, третий вход преобразователя соединен с первым входом первого элемента ИЛИ, первые входы третьего и четвертого элементов И соединены с первым входом преобразователя, выход первого элемента И соединен с первым входом второго элемента ИЛИ, четвертый вход преобразователя соединен с первым входом четвертого элемента ИЛИ, пятый вход преобразователя соединен с первым входом первого сумматора по модулю два, отличающийся тем, что, с целью расширения области при- менения за счет преобразования информации из минимальной формы в оптимальную форму Ц системы счисления, он содержит с третьего по восьмой сумматоры по модулю два, причем первый вход преобразователя соединен с первым входом третьего сумматора по модулю два, третий вход преобразователя соединен с первым входом третьего элемента ИЛИ, четвертый вход преоб- разователя соединен с вторым входом первого элемента ИЛИ, пятый вход преобразователя соединен с вторым входом первого элемента И, шестой вход преобразователя соединен с вторым входом четвертого элемента И, первыми входами четвертого и пятого сумматоров по модулю два и вторым входом третьего элемента ИЛИ, седьмой вход i преобразователя соединен с вторыми входами второго и третьего эпемен- тов И, первыми входами шестого и седьмого сумматоров по модулю два и вторым входом четвертого элемента

ИЛИ, выход первого элемента И соединен с вторым входом первого сумматора по модулю два, первым -ходом восьмого сумматора по модулю два и первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом пятого сумматора по модулю два, второй вход которого соединен с вторым входом четвертого сумматора по модулю два, первым входом шестого элемента ИЛИ и выходом четвертого элемента И, выходы пятого и шестого элементов ИЛИ и выход второго элемента И являются соответственно пятым, шестым и седьмым выходами преобразователя, выход второго элемента И соединен с вторым входом второго сумматора по модулю два и вторым входом седьмого сумматора по модулю два, выход которого соединен с вторым входом шестого элемента ИЛИ, выход третьего элемента И соединен с вторыми входами третьего и шестого сумматоров по модулю два и вторым входом второго элемента ИЛИ, третий вход которого соединен с РЫХОДОМ второго сумматора по модулю два, выход третьего сумматора по модулю два соединен с вторым входом восьмого сумматора по модулю два, выход которого соединен с третьим входом первого элемента ИЛИ, четвертый и пятый входы которого соединены соответственно с выходами четвертого и шестого сумматоров по модулю два, пыход первого сумматора по модулю два соединен с четвертым входом второго и третьим входом четвертого олементов ИЛИ.

| Устройство для приведения @ -кодов Фибоначчи к минимальной форме | 1982 |

|

SU1092489A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода | 1987 |

|

SU1427573A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

Авторы

Даты

1990-02-23—Публикация

1988-05-25—Подача