Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов.

Известно устройство, предназначенное для выполнения цифровой фильтрации, содержащее формирователь импульсов, адресный счетчик, блок памяти рангов коэффициентов отсчетов, мультиплексор, блок синхронизации. Фильтрация сигналов производится по формуле свертки [1].

Это устройство обладает узким кругом функциональных возможностей, низкой степенью унификации, значительными аппаратными затратами.

Известно также устройство, предназначенное для выполнения цифровой фильтрации, содержащее входной и выходной регистры, адресные счетчики, опорный генератор, постоянное запоминающее устройство, микропроцессорные секции со схемой ускоренного переноса [2].

Это устройство обладает широким кругом функциональных возможностей и высокой степенью унификации.

Процесс перестройки и адаптации алгоритма вычислений под конкретный алгоритм ЦОС в этом устройстве обеспечивается посредством соответствующих изменений программы, не затрагивающих схемы соединений и структуры процессора в целом. Однако данное устройство обладает низким быстродействием, что обусловлено программной, а не аппаратной реализацией процедуры вычислений. Любая операция в таком процессоре требует несколько микрокоманд, каждая из которых представляет собой элементарные логические операции, операции сдвига, извлечения из памяти, пересылки и т.д. ПЗУ микрокоманд содержит как адрес того, где находятся операнды, так и информацию о том, какие операции нужно с ними произвести. Следовательно вычисление одного отсчета, например, по формуле свертки может потребовать выполнения от нескольких десятков до нескольких сотен микрокоманд. Достижимая частота дискретизации у данного устройства составляет порядка единиц килогерц при порядке НЦФ десятки.

Цель изобретения - повышение быстродействия.

Это достигается тем, что в устройство цифровой фильтрации, содержащее первый, второй и третий адресные счетчики, адресные входы которого подключены к выходам опорного генератора, а выходы первого и второго из которых подключены соответственно к первому и второму адресным входам первого блока постоянной памяти, а также входной регистр, информационный вход которого является входом устройства цифровой фильтрации, выходом которого является выход выходного регистра, между выходом третьего адресного счетчика и информационным входом выходного регистра включены последовательно второй блок постоянной памяти, оперативное запоминающее устройство (ОЗУ) и умножитель-накопитель, между выходом третьего адресного счетчика и информационным входом умножителя-накопителя включен блок памяти коэффициентов, другой адресный вход которого объединен с другим адресным входом второго блока постоянной памяти и с первым адресным входом первого блока постоянной памяти, управляющий выход которого соединен с управляющими входами ОЗУ, входного и выходного регистров и умножителя-накопителя, а адресный выход - с другим адресным входом ОЗУ, при этом выход умножителя-накопителя объединен с выходом входного регистра и входом-выходом ОЗУ.

Предлагаемое устройство содержит минимальное число типов элементов: адресные счетчик, оперативно запоминающее устройство (ОЗУ), блоки памяти адреса ОЗУ, памяти коэффициентов, реализованные на постоянных программируемых запоминающих устройствах (ППЗУ), умножитель-накопитель, регистр, предусматривает возможность реализации при помощи такого устройства различных устройств цифровой обработки, например нерекурсивного цифрового фильтра (НФЦ), рекурсивного цифрового фильтра (РЦФ), каскадного включения фильтров, систем ступенчатого преобразования частоты дискретизации, многоканального цифрового фильтра, дискретных преобразователей Фурье и обеспечивает высокое быстродействие.

Сопоставительный анализ заявляемого решения с прототипом показывает, что заявляемое устройство отличается от известного тем, что между выходом третьего адресного счетчика и информационным входом выходного регистра включены последовательно второй блок постоянной памяти ОЗУ и умножитель-накопитель, а между выходом третьего адресного счетчика и информационным входом умножителя-накопителя включен блок памяти коэффициентов.

Таким образом, предложенное устройство соответствует критерию изобретения "новизна". При анализе известных и заявляемого устройств установлено, что у заявляемого устройства появляются свойства, не совпадающие со свойствами известных решений, поэтому оно обладает существенными отличиями.

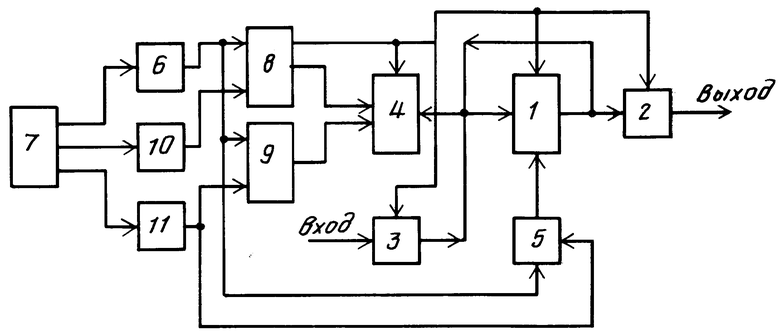

На чертеже изображена функциональная схема устройства.

Устройство цифровой обработки сигналов содержит умножитель-накопитель 1, выход которого подключен к входу выходного регистра 2, к выходу входного регистра 3, к входу-выходу оперативно-запоминающего устройства отсчетов входного сигнала ОЗУ и к первому информационному входу умножителя-накопителя 1, второй информационный вход которого соединен с выходом блока 5 памяти коэффициентов, реализованного на ППЗУ, группы адресных входов которого соединены с выходами адресного счетчика 6, вход которого соединен с выходом опорного генератора 7, первый и второй блоки 8, 9 постоянной памяти, реализованные на ППЗУ, адресные выходы которых подключены к адресным входам оперативно запоминающего устройства отсчетов входного сигнала, а управляющие выходы первого блока 8 постоянной памяти соединены с входами управления оперативно-запоминающего устройства 4, входного и выходного регистров 3, 2, умножителя-накопителя 1, первая группа адресных входов первого блока 8 постоянной памяти соединена с выходами первого адресного счетчика 6 и с первой группой адресных входов второго блока 9 постоянной памяти, вторая группа адресных входов первого блока 8 постоянной памяти соединена с выходами второго адресного счетчика 10, вход которого соединен с вторым выходом опорного генератора 7, вторые группы адресных входов второго блока 9 постоянной памяти и блока 5 памяти коэффициентов подключены к адресным выходам третьего адресного счетчика 11, вход которого соединен с третьим выходом опорного генератора 7.

Описание работы устройства.

Организация адресации ячеек ОЗУ 4 и ППЗУ 5, 8, 9 коэффициентов алгоритма обработки при реализации свертки вида

Yj=  hix(t-i), (1) где hi - коэффициенты импульсной характеристики (КИХ);

hix(t-i), (1) где hi - коэффициенты импульсной характеристики (КИХ);

x(t-i) - отсчеты входного сигнала, осуществляется посредством сдвига адреса ячеек ОЗУ 4 входных отсчетов относительно адреса ППЗУ коэффициентов 5 ИХ (КИХ) синхронно с вычислением каждого выходного отсчета. Адрес ОЗУ 4 линии задержки и ППЗУ 5 КИХ задается счетчиком 6, коэффициент пересчета (число состояний) которого К1 выбирается из условия К1 ≥N. Один полный цикл работы счетчика 6 соответствует вычислению одного отсчета сигнала Yj. Коды состояний счетчика 10 разбивают адресное пространство ПЗУ 8 на К2сектора, где К2 ≥N - коэффициент пересчета счетчика 10. В каждом секторе записываются последовательности адресов ОЗУ, причем к-я последовательность адресов, соответствующая к-му состоянию счетчика 10 (К=0, К2-1), отличается от (К-1)-й последовательности циклическим сдвигом элементов (адресов ОЗУ) на одну позицию. Таким образом, смена состояния счетчика 10, происходящая после вычисления каждого отсчета сигнала Yj, вызывает циклическое смещение адресов ячеек ОЗУ относительно адресов ячеек ПЗУ коэффициентов (смещение сигнала в линии задержки), обеспечивая тем самым выполнение операции свертки.

При реализации многоканальных (n-канальных) устройств, устройств с параллельным включением и рекурсивных или нерекурсивных цифровых фильтров, а также при выполнении преобразований, требующих многократного выполнения однотипных операций, используются счетчик 11 с коэффициентом пересчета n, и второй блок постоянной памяти 9, посредством которых поле адресов ОЗУ разбивается на n "страниц", смена которых производится при изменении состояния счетчика 11, осуществляемого при переходе от одного из параллельных устройств к другому или при переходе от одной однотипной операции к следующей. При этом на счетный вход счетчика 6 от опорного генератора поступает последовательность импульсов с частотой F, определяемой сложностью реализуемых устройств (например, фильтров) и предельным быстродействием блоков, входящих в состав устройства, прежде всего временем умножения УН1. На счетный вход счетчика 11 поступает последовательность импульсов с частотой F/К1, на вход счетчика 10 - с частотой F/К1 ˙n.

При реализации каскадного включения ЦФ на данном устройстве, например, для случая ступенчатого преобразования частоты дискретизации достаточно соответствующим образом изменить программу ППЗУ 8, 9 адреса ОЗУ 4 ЛЗ и задать новый кратный периоду отдельных звеньев период обновления адреса ОЗУ 4 с помощью счетчика 11.

Посредством изменения программы ППЗУ 8 и 9 осуществляется реализация рекурсивных алгоритмов ЦОС. Управление режимом работы умножителя-накопителя 1, его тристабильным выходным каскадом, а также ОЗУ и входным и выходным регистрами осуществляется также с помощью ППЗУ 8, куда для этих целей записывается управляющая программа.

Высокое быстродействие в предлагаемой структуре обеспечивается за счет аппаратной реализации основной процедуры ЦОС умножения с накоплением с помощью умножителя-накопителя УН1 и возможности организации конвейерного режима работы. При этом в ПЗУ 5 хранятся коэффициенты обработки (например КИХ), а в ПЗУ 8, 9 - непосредственно адрес ячеек ОЗУ 4, памяти входных отсчетов обрабатываемого сигнала при реализации НЦФ, а также и выходных отсчетов для РЦФ или промежуточных результатов при реализации других алгоритмов ЦОС.

Конвейерный режим работы организуется посредством одновременного формирования адреса ОЗУ, выборки требуемого отсчета из ОЗУ и коэффициента обработки из ПЗУ, а также выполнения операции алгоритма ЦОС.

Так, например, при реализации НЦФ порядка N по выражению (1) максимально возможная частота дискретизации фильтра равна

Fд=  =

=  или для случая многоканального режима работы

или для случая многоканального режима работы

Fд=  =

=  где tзад - большее из времен формирования адреса ОЗУ, формирования адреса ПЗУ КИХ, выборки содержимого ОЗУ, одного умножения с накоплением;

где tзад - большее из времен формирования адреса ОЗУ, формирования адреса ПЗУ КИХ, выборки содержимого ОЗУ, одного умножения с накоплением;

tRg - время записи в выходной регистр.

Реально tзад определяется временем умножения с накоплением. Достижимые частоты дискретизации при этом составляют порядка сотен килогерц при порядках НЦФ десятки.

Предложенное устройство цифровой фильтрации позволяет по сравнению с прототипом повысить быстродействие устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С НЕЛИНЕЙНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ (ИКМ) | 1998 |

|

RU2143790C1 |

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

| Способ формирования и приема телевизионного сигнала при передаче изображения и система для его осуществления | 1986 |

|

SU1453619A1 |

| Многоканальное устройство для ввода аналоговых данных | 1986 |

|

SU1335972A1 |

| Способ анализа спектра сигналов и устройство для его осуществления | 1988 |

|

SU1573432A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в устройстве, содержащем первый 6, второй 10 и третий 11 адресные счетчики, адресные входы которых подключены к выходам опорного генератора 7, а выходы первого и второго из которых подключены соответственно к первому и второму адресным входам первого блока 8 постоянной памяти, а также входной регистр 3, информационный вход которого является входом устройства цифровой фильтрации, выходом которого является выход выходного регистра 2, между выходом третьего адресного счетчика 11 и информационным входом выходного регистра 2 включены последовательно второй блок 9 постоянной памяти, оперативное запоминающее устройство (ОЗУ) 4 и умножитель-накопитель 1, между выходом третьего адресного счетчика и информационным входом умножителя-накопителя 1 включен блок 5 памяти коэффициентов, другой адресный вход которого объединен с другим адресным входом второго блока 9 постоянной памяти и с первым адресным входом первого блока 8 постоянной памяти, управляющий выход которого соединен с управляющими входами ОЗУ, входного и выходного регистров и умножителя-накопителя, а адресный выход - с другим адресным входом ОЗУ, при этом выход умножителя-накопителя 1 объединен с выходом входного регистра 3 и входом-выходом ОЗУ. 1 ил.

ЦИФРОВОЙ ФИЛЬТР, содержащий первый, второй и третий адресные счетчики, адресные входы которых подключены к выходам опорного генератора, а выходы первого и второго счетчиков - соответственно к первому и второму адресным входам первого блока постоянной памяти, а также входной регистр, информационный вход которого является входом цифрового фильтра, выходом которого является выход выходного регистра, отличающийся тем, что, с целью повышения быстродействия, между выходом третьего адресного счетчика и информационным входом выходного регистра включены последовательно второй блок постоянной памяти, оперативной запоминающее устройство и умножитель-накопитель, между выходом третьего адресного счетчика и информационным входом умножителя-накопителя включен блок памяти коэффициентов, другой адресный вход которого объединен с другим адресным входом второго блока постоянной памяти и с первым адресным входом первого блока постоянной памяти, управляющий выход которого соединен с управляющими входами оперативного запоминающего устройства, входного и выходного регистров и умножителя-накопителя, а адресный выход - с другим адресным входом оперативного запоминающего устройства, при этом выход умножителя-накопителя объединен с выходом входного регистра и входом-выходом оперативного запоминающего устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Рекурсивные фильтры на микропроцессорах | |||

| Под ред | |||

| А.Г.Остапенко | |||

| М.: Радио и связь, 1988, с.64-65, рис.3.1. | |||

Авторы

Даты

1994-11-30—Публикация

1990-07-02—Подача