Изобретение относится к радиотехнике, в частности, к радиолокационным и гидролокационным системам.

Цель изобретения - повышение помехозащищенности путем пеленгации помехо- носителей.

В процессе адаптации система обеспечивает пеленгацию помехоносителей с точностью до углового направления ДОС, а также качественную оценку мощности помехоносителей.

В основе работы системы лежит процедура ортогонализации ковариационной мат- : рицы с помощью процедуры Грамма-Шмидта. При этом в первую очередь производится компенсация по лучам, имеющим максимальную мощность помех. Одновременно контролируется мощность помех в других каналах-, и при снижении ее ниже заданного порога соответствующие каналы исключаются из рассмотрения в качестве компенсационных.

Аппаратно процессор адаптации содержит отдельные блоки адаптации и фильтрации. При этом блоки адаптации выполнены на основе векторных процессоров, обеспечивающих линейные преобразования строк матриц. Блок управления содержит ОЗУ дескрипторов с набором трех управляющих счетчиков, что позволяет при сортировке строк матрицы избегать пересылок больших массивов информации, обходясь лишь преобразованиями дескрипторов.

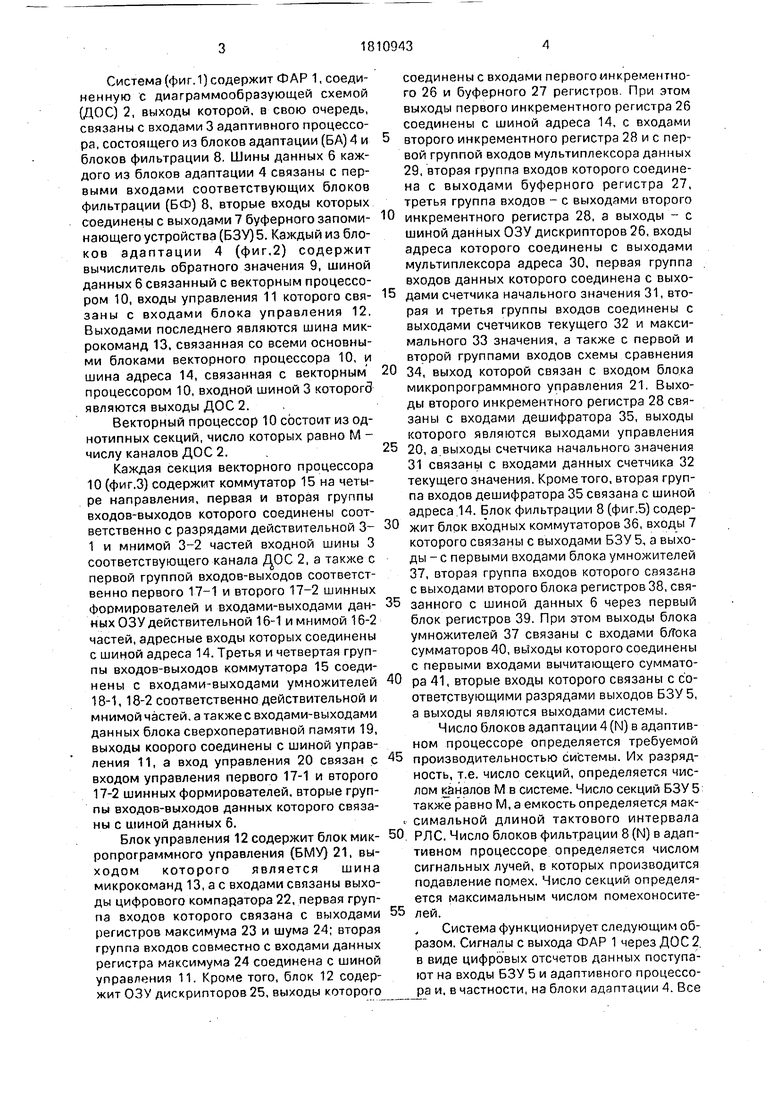

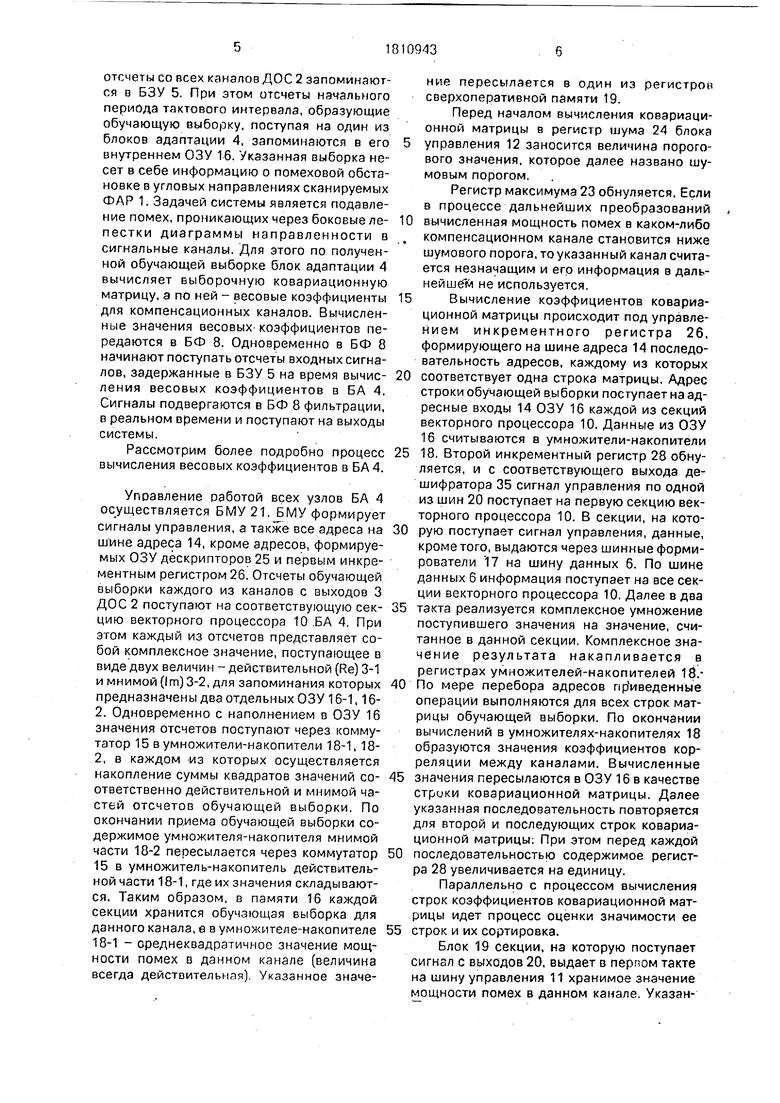

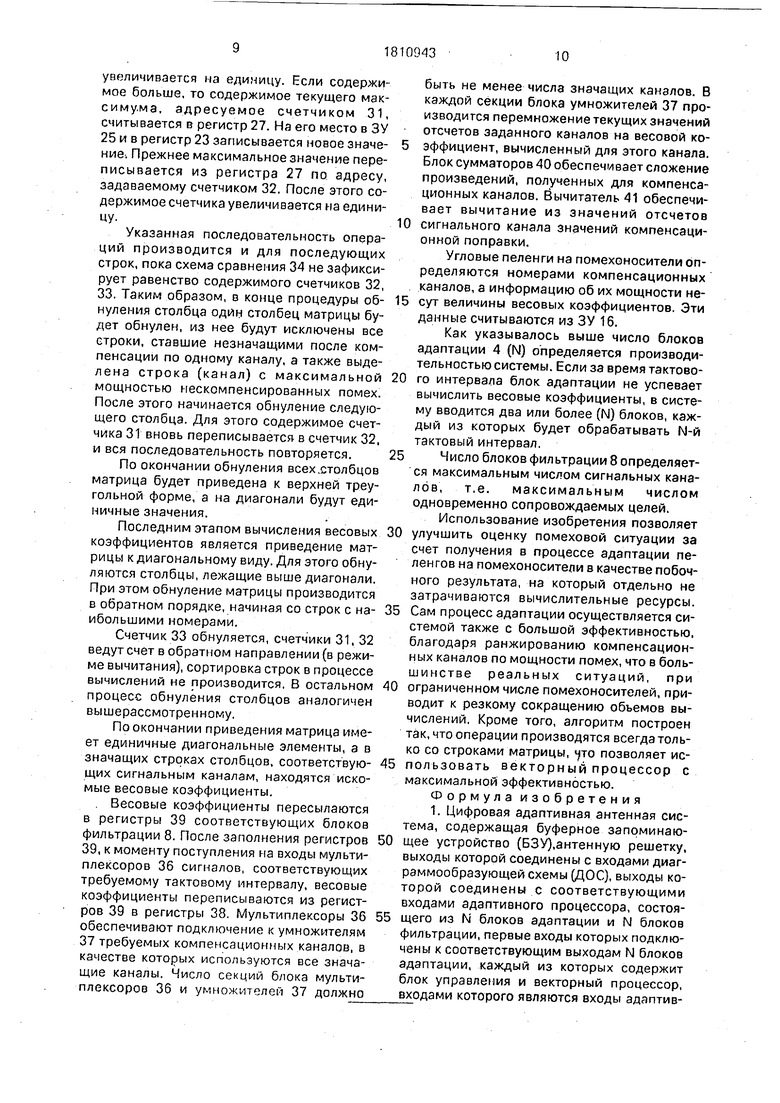

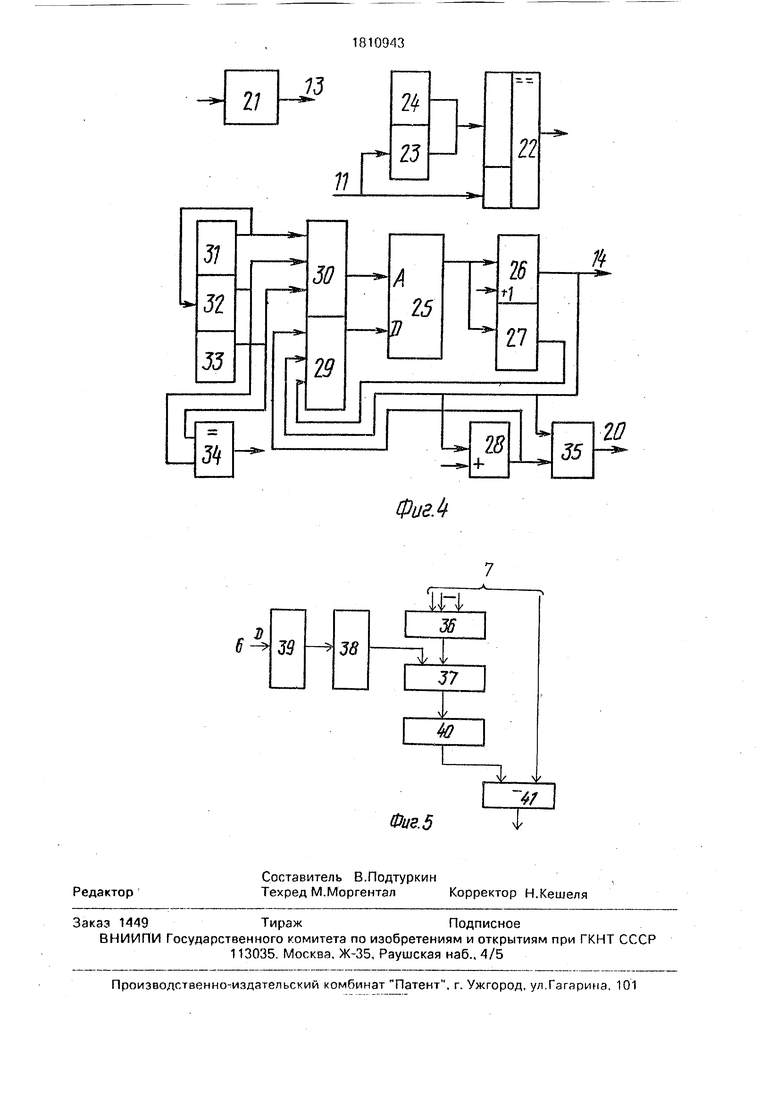

На фиг.1 приведена структурная схема системы; на фиг.2 - структурная схема блока адаптации; на фиг.З - структурная схема одной секции векторного процессора; на фиг.4 - структурная схема блока управления; на фиг.5 - структурная схема блока фильтрации.

00

о ю

I.

СА)

Система (фиг. 1) содержит ФАР 1, соединенную с диаграммообразующей схемой (ДОС) 2, выходы которой, в свою очередь, связаны с входами 3 адаптивного процессора, состоящего из блоков адаптации (БА) 4 и блоков фильтрации 8. Шины данных 6 каждого из блоков адаптации 4 связаны с первыми входами соответствующих блоков фильтрации (БФ) 8, вторые входы которых соединены с выходами 7 буферного запоминающего устройства (БЗУ) 5. Каждый из бло- ков адаптации 4 (фиг.2) содержит вычислитель обратного значения 9, шиной данных 6 связанный с векторным процессором 10, входы управления 11 которого связаны с входами блока управления 12. Выходами последнего являются шина микрокоманд 13, связанная со всеми основными блоками векторного процессора 10, и шина адреса 14, связанная с векторным процессором 10, входной шиной 3 которого1 являются выходы ДОС 2.

Векторный процессор 10 состоит из однотипных секций, число которых равно М - числу каналов ДОС 2.

Каждая секция векторного процессора 10 (фиг.З) содержит коммутатор 15 на четыре направления, первая и вторая группы входов-выходов которого соединены соответственно с разрядами действительной 3- 1 и мнимой 3-2 частей входной шины 3 соответствующего канала ДОС 2, а также с первой группой входов-выходов соответственно первого 17-1 и второго 17-2 шинных Формирователей и входами-выходами данных ОЗУ действительной 16-1 и мнимой 16-2 частей, адресные входы которых соединены с шиной адреса 14. Третья и четвертая группы входов-выходов коммутатора 15 соединены с входами-выходами умножителей 18-1, 18-2 соответственно действительной и мнимой частей, а также с входами-выходами данных блока сверхоперативной памяти 19, выходы коорого соединены с шиной управления 11, а вход управления 20 связан с входом управления первого 17-1 и второго 17-2 шинных формирователей, вторые группы входов-выходов данных которого связаны с шиной данных 6.

Блок управления 12 содержит блок микропрограммного управления (БМУ) 21, выходом которого является шина микрокоманд 13, а с входами связаны выходы цифрового компаратора 22, первая группа входов которого связана с выходами регистров максимума 23 и шума 24; вторая группа входов совместно с входами данных регистра максимума 24 соединена с шиной управления 11. Кроме того, блок 12 содержит ОЗУ дискрипторов 25, выходы которого

соединены с входами первогоинкрементно- го 26 и буферного 27 регистров. При этом выходы первого инкрементного регистра 26 соединены с шиной адреса 14, с входами

второго инкрементного регистра 28 и с первой группой входов мультиплексора данных 29, вторая группа входов которого соединена с выходами буферного регистра 27, третья группа входов - с выходами второго

0 инкрементного регистра 28, а выходы - с шиной данных ОЗУ дискрипторов 26, входы адреса которого соединены с выходами мультиплексора адреса 30, первая группа входов данных которого соединена с выхо5 дами счетчика начального значения 31, вторая и третья группы входов соединены с выходами счетчиков текущего 32 и максимального 33 значения, а также с первой и второй группами входов схемы сравнения

0 34, выход которой связан с входом блока микропрограммного управления 21. Выходы второго инкрементного регистра 28 связаны с входами дешифратора 35, выходы которого являются выходами управления

5 20, а выходы счетчика начального значения 31 связаны с входами данных счетчика 32 текущего значения. Кроме того, вторая группа входов дешифратора 35 связана с шиной адреса .14. Блок фильтрации 8 (фиг.5) содер0 Жит блок входных коммутаторов 36, входы 7 которого связаны с выходами БЗУ 5, а выходы - с первыми входами блока умножителей 37, вторая группа входов которого связана с выходами второго блока регистров 38, свя5 занного с шиной данных 6 через первый блок регистров 39. При этом выходы блока умножителей 37 связаны с входами б/Тока сумматоров 40, выходы которого соединены с первыми входами вычитающего суммато0 ра 41, вторые входы которого связаны с соответствующими разрядами выходов БЗУ 5, а выходы являются выходами системы.

Число блоков адаптации 4 (N) в адаптивном процессоре определяется требуемой

5 производительностью системы. Их разрядность, т.е. число секций, определяется числом каналов Мв системе. Число секций БЗУ 5 также равно М, а емкость определяется мак- v симальной длиной тактового интервала

0 РЛС. Число блоков фильтрации 8 (N) в адаптивном процессоре определяется числом сигнальных лучей, в которых производится подавление помех. Число секций определяется максимальным числом помехоносите5 лей.

Система функционирует следующим образом. Сигналы с выхода ФАР 1 через ДОС 2. в виде цифровых отсчетов данных поступают на входы БЗУ 5 и адаптивного процессора и. в частности, на блоки адаптации 4. Все

отсчеты со всех каналов ДОС 2 запоминаются в БЗУ 5. При этом отсчеты начального периода тактового интервала, образующие обучающую выборку, поступая на один из блоков адаптации 4, запоминаются в его внутреннем ОЗУ 16. Указанная выборка несет в себе информацию о помеховой обстановке в угловых направлениях сканируемых ФАР 1. Задачей системы является подавление помех, проникающих через боковые ле- пестки диаграммы направленности в сигнальные каналы. Для этого по полученной обучающей выборке блок адаптации 4 вычисляет выборочную ковариационную матрицу, а по ней - весовые коэффициенты для компенсационных каналов. Вычисленные значения весовых-коэффициентов передаются в БФ 8. Одновременно в Б Ф 8 начинают поступать отсчеты входных сигналов, задержанные в БЗУ 5 на время вычис- ления весовых коэффициентов в БА 4. Сигналы подвергаются в БФ 8 фильтрации, в реальном времени и поступают на выходы системы.

Рассмотрим более подробно процесс вычисления весовых коэффициентов в БА4.

Управление работой всех узлов БА 4 осуществляется БМУ 21. БМУ формирует сигналы управления, а также все адреса на шине адреса 14, кроме адресов, формируемых ОЗУ дескрипторов 25 и первым инкре- ментным регистром 26. Отсчеты обучающей выборки каждого из каналов с выходов 3 ДОС 2 поступают на соответствующую сек- цию векторного процессора 10 .БА 4. При этом каждый из отсчетов представляет собой комплексное значение, поступающее в виде двух величин - действительной (Re) 3-1 и мнимой (Im) 3-2, для запоминания которых предназначены два отдельных ОЗУ 16-1,16- 2. Одновременно с наполнением в ОЗУ 16 значения отсчетов поступают через коммутатор 15 в умножители-накопители 18-1,18- 2, в каждом из которых осуществляется накопление суммы квадратов значений со- ответственно действительной и мнимой частей отсчетов обучающей выборки. По окончании приема обучающей выборки содержимое умножителя-накопителя мнимой части 18-2 пересылается через коммутатор 15 в умножитель-накопитель действительной части 18-1, где их значения складываются. Таким образом, в памяти 16 каждой секции хранится обучающая выборка для данного канала, в в умножителе-накопителе 18-1 - среднеквадратичное значение мощности помех в данном канале (величина всегда действительная). Указанное значение пересылается в один из регистров сверхоперативной памяти 19.

Перед началом вычисления ковариационной матрицы в регистр шума 24 блока управления 12 заносится величина порогового значения, которое далее названо шумовым порогом.

Регистр максимума 23 обнуляется. Если в процессе дальнейших преобразований вычисленная мощность помех в каком-либо компенсационном канале становится ниже шумового порога, то указанный канал считается незначащим и его информация в дальнейшей не используется.

Вычисление коэффициентов ковариационной матрицы происходит под управлением инкрементного регистра 26, формирующего на шине адреса 14 последовательность адресов, каждому из которых соответствует одна строка матрицы. Адрес строки обучающей выборки поступает на адресные входы 14 ОЗУ 16 каждой из секций векторного процессора 10. Данные из ОЗУ 16 считываются в умножители-накопители 18. Второй инкрементный регистр 28 обнуляется, и с соответствующего выхода дешифратора 35 сигнал управления по одной из шин 20 поступает на первую секцию векторного процессора 10. В секции, на которую поступает сигнал управления, данные, кроме того, выдаются через шинные формирователи 17 на шину данных 6. По шине данных 6 информация поступает на все секции векторного процессора 10. Далее в два такта реализуется комплексное умножение поступившего значения на значение, считанное в данной секции. Комплексное значение результата накапливается в регистрах умножителей-накопителей 18/ По мере перебора адресов приведенные операции выполняются для всех строк матрицы обучающей выборки. По окончании вычислений в умножителях-накопителях 18 образуются значения коэффициентов корреляции между каналами. Вычисленные значения пересылаются в ОЗУ 16 в качестве строки ковариационной матрицы. Далее указанная последовательность повторяется для второй и последующих строк ковариационной матрицы; При этом перед каждой последовательностью содержимое регистра 28 увеличивается на единицу.

Параллельно с процессом вычисления строк коэффициентов ковариационной матрицы идет процесс оценки значимости ее строк и их сортировка.

Блок 19 секции, на которую поступает сигнал с выходов 20, выдает в перпом такте на шину управления 11 хранимое значение мощности помех в данном канале. Указанное значение поступает в блок управления 12, на компаратор 22. где сравнивается с содержимым регистра шума 24. Если мощность ниже уровня шумового порога, увеличивается на единицу содержимое счетчика конечного значения 33 и прекращаются дальнейшие вычисления текущей строки ковариационной матрицы. Если мощность выше шумового порога, то номер канала с выхода регистра 28 через мультиплексор 29 заносится в ЗУ 26 по адресу, формируемому счетчиком текущего значения 32. В следующем такте производится сравнение мощности помех, поступающей на компаратор 22, с содержимым регистра максимума 23. Если мощность меньше, содержимое счетчика 32 увеличивается на единицу; если больше, текущее значение мощности с шины 11 загружается в регистр 23. На адресные входы ЗУ 26 коммутируется содержимое счетчика начального значения. По этому адресу из ЗУ 26 считывается дескриптор строки со ста- рым.максимальным значением и переписывается в буферный регистр 27, а в ЗУ заносится с выхода регистра 28 значение нового максимума. Затем на адресные входы ЗУ 26 вновь коммутируется содержимое счетчика 32 и производится запись в ЗУ 26 дескриптора с выходов регистра 27. Затем содержимое счетчика 32 увеличивается на единицу.

Таким образом, после вычисления коэффициентов ковариационной матрицы по нулевому адресу ЗУ дескрипторов 25 содержится номер строки ковариационной матрицы с максимальным диагональным элементом, а содержимое счетчика конечного значения 33 равно числу значащих строк в матрице. После этого начинается процесс приведения ковариационной матрицы к верхней треугольной форме. Для этого поочередно обнуляются элементы столбцов матрицы, расположенные ниже диагонали.

Рассмотрим процесс обнуления одного столбца матрицы. Обнуляется содержимое регистра 23. В счетчик текущего значения 32 переписывается содержимое счетчика начального значения 31, и по этому адресу из ЗУ 25 считывается номер строки с максимальным диагональным элементом. Номер строки переписывается в первый и второй инкрементные регистры 26, 28. Содержимое счетчика в виде адреса по шине 14 поступает на секции векторного процессора 10. В каждой секции по указанному адресу из ОЗУ 16 значения коэффициентов данной строки считываются через мультиплексор 15 в регистры умножителей-накопителей 18. Значение диагонального элемента из секции, выбранной сигналом на соответствующем разряде шин 20, поступает, кроме того, по шине данных 6 в вычислитель обратного значения 9. В блоке 9 вычисляется обратное значение коэффициента. Вычисленное обратное значение поступает по шине данных 6 на секции векторного процессора 10 и перемножается в умножителях-накопителях 18с соответствующими коэффициентами строки. При этом значение

0 диагонального элемента становится единичным, остальные элементы нормируются по отношению к нему. Все значения записью ваются обратно в ОЗУ 16 и, кроме того, фиксируются в регистрах умножителей-на5 копителей 18. Одновременно содержимое счетчика 32 увеличивается на единицу. Из ЗУ 25 в регистр 26 и на шину адреса 14 считывается следующий номер строки. Указанный адрес, поступая на ОЗУ 16 вектор0 ного процессора 10, выбирает из них коэффициенты следующей строки матрицы, которые переписываются в накопительные регистры умножителей-накопителей 18. Одновременно на дешифратор 35 подается ад5 рее из регистра 28 и выбранное значение коэффициента из соответствующей секции векторного процессора 10 поступает по шине данных 6 на все секции. Указанное значение поступает на умножители-накопители

0 18, умножается на коэффициенты нормированной строки, хранимые в буферных регистрах умножителей-накопителей 18, и полученные результаты вычитаются из содержимого накопительного регистра. Пол- 5 ученные новые .коэффициенты строки переписываются обратно в ОЗУ 16. При этом коэффициент, соответствующий обнуляемому столбцу, будет равен нулю. Одновременно адрес с шины 14 подается на

0 вторую группу входов дешифратора 35, который формирует строб на разряде шины 20, соответствующем диагональному элементу текущей строки. В выбранной таким образом секции указанный коэффициент

5 фиксируется в блоке 19 (как значение мощности помех в канале) и выдается по шине управления 11 в блок управления 12, где на компараторе 22 сравнивается с содержи- ьмым регистра шума 24. Если значение мень0 ше шумового порога, тогда из ЗУ 25 по адресу счетчика 33 считывается в регистр 27 номер строки, который записывается по адресу, поступившему от счетчика 32, а содержимое счетчика 33 уменьшается на единицу.

5 Таким образом, строка исключается из списка значащих. Если значение превышает шумовой порог, то производится сравнение с текущим содержимым регистра максимума 23. Если значение меньше текущего максимума, то содержимое счетчика 32

увеличивается на единицу. Если содержимое больше, то содержимое текущего максимума, адресуемое счетчиком 31, считывается в регистр 27. На его место в ЗУ 25 и в регистр 23 записывается новое значение. Прежнее максимальное значение пере- писывается из регистра 27 по адресу, задаваемому счетчиком 32. После этого содержимое счетчика увеличивается на единицуУказанная последовательность операций производится и для последующих строк, пока схема сравнения 34 не зафиксирует равенство содержимого счетчиков 32, 33. Таким образом, в конце процедуры обнуления столбца один столбец матрицы будет обнулен, из нее будут исключены все строки, ставшие незначащими после компенсации по одному каналу, а также выделена строка (канал) с максимальной мощностью нескомпенсированных помех. После этого начинается обнуление следующего столбца. Для этого содержимое счетчика 31 вновь переписывается в счетчик 32, и вся последовательность повторяется.

По окончании обнуления всех.столбцов матрица будет приведена к верхней треугольной форме, а на диагонали будут единичные значения.

Последним этапом вычисления весовых коэффициентов является приведение матрицы к диагональному виду. Для этого обнуляются столбцы, лежащие выше диагонали. При этом обнуление матрицы производится в обратном порядке, начиная со строк с наибольшими номерами.

Счетчик 33 обнуляется, счетчики 31. 32 ведут счет в обратном направлении (в режиме вычитания), сортировка строк в процессе вычислений не производится. В остальном процесс обнуления столбцов аналогичен вышерассмотренному.

По окончании приведения матрица имеет единичные диагональные элементы, а в значащих строках столбцов, соответствующих сигнальным каналам, находятся искомые весовые коэффициенты.

. Весовые коэффициенты пересылаются в регистры 39 соответствующих блоков фильтрации 8. После заполнения регистров 39, к моменту поступления на входы мультиплексоров 36 сигналов, соответствующих требуемому тактовому интервалу, весовые коэффициенты переписываются из регистров 39 в регистры 38. Мультиплексоры 36 обеспечивают подключение к умножителям 37 требуемых компенсационных каналов, в качестве которых используются все значащие каналы. Число секций блока мультиплексоров 36 и умножителей 37 должно

быть не менее числа значащих каналов. В каждой секции блока умножителей 37 производится перемножение текущих значений отсчетов заданного каналов на весовой ко- 5 эффициент, вычисленный для этого канала. Блок сумматоров 40 обеспечивает сложение произведений, полученных для компенсационных каналов. Вычитатель 41 обеспечивает вычитание из значений отсчетов

0 сигнального канала значений компенсационной поправки.

Угловые пеленги на помехоносители определяются номерами компенсационных каналов, а информацию об их мощности не5 сут величины весовых коэффициентов. Эти данные считываются из ЗУ 16.

Как указывалось выше число блоков адаптации 4 (N) определяется производительностью системы. Если за время тактово0 го интервала блок адаптации не успевает вычислить весовые коэффициенты, в систему вводится два или более (N) блоков, каждый из которых будет обрабатывать М-й тактовый интервал.

5 Число блоков фильтрации 8 определяется максимальным числом сигнальных каналов, т.е. максимальным числом одновременно сопровождаемых целей. Использование изобретения позволяет

0 улучшить оценку помеховой ситуации за счет получения в процессе адаптации пеленгов на помехоносители в качестве побочного результата, на который отдельно не затрачиваются вычислительные ресурсы.

5 Сам процесс адаптации осуществляется системой также с большой эффективностью, благодаря ранжированию компенсационных каналов по мощности помех, что в боль- шинстве реальных ситуаций, при

0 ограниченном числе помехоносителей, приводит к резкому сокращению объемов вычислений. Кроме того, алгоритм построен так, что операции производятся всегда только со строками матрицы, что позволяет ис5 пользовать векторный процессор с максимальной эффективностью. Формула изобретения 1. Цифровая адаптивная антенная система, содержащая буферное запрминаю0 щее устройство (БЗУ),антенную решетку, выходы которой соединены с входами диаг- рэммообразующей схемы (ДОС), выходы которой соединены с соответствующими входами адаптивного процессора, состоя5 щего из N блоков адаптации и N блоков фильтрации, первые входы которых подключены к соответствующим выходам N блоков адаптации, каждый из которых содержит блок управления и векторный процессор, входами которого являются входы адаптивного процессора, отличающаяся тем, что, с целью повышения помехозащищенности путем пеленгации помехоносителей, вторые входы N блоков фильтрации подключены к выходам буферного запоминающего устройства, входы которого соединены с соответствующими входами адаптивного процессора, введен вычислитель обратного значения, входы данных которого соединены с входами данных векторного процессора, управляющие выходы которого соединены с управляющими входами блока управления, адресные выходы которого соединены с адресными входами векторного процессора, блок управления состоит из блока микропрограммного управления, шина микрокоманд которого соединена с шинами микрокоманд векторного процессора, оперативного запоминающего устройства (ОЗУ) дескрипторов, выходы которого соединены с входами первого инкрементного регистра и буферного регистра, выходы которого соединены с первыми входами мультиплексора данных, вторые входы которого соединены с входами второго инкрементного регистра, первыми входами дешифратора и адресными выходами первого инкрементного регистра, которые являются адресными выходами блока сравнения, выходы второго инкрементного регистра соединены с вторыми входами дешифратора и третьими входами мультиплексора данных, выходы которого соединены с входами данных ОЗУ дескрипторов, адресные входы которых подключены к выходам мультиплексора адреса, первые входы которого соединены с выходами счетчика начального значения и установочными входами счетчика текущего значения, выходы которого соединены с первыми входами схемы сравнения и вторыми входами мультиплексора адреса, третьи входы которого соединены с выходами счетчика конечного значения и вторыми входами схемы сравнения, выходы которой соединены с входами блока микропрограммного управления и выходами цифрового компаратора, первые входы которого соединены с выходами регистра шума и регистра максимума, входы которого соединены с вторыми входами цифрового компаоатора и являются управляющими входами блока управления, при

этом выходы дешифратора являются выходами управления блока управления.

2. Система по п. 1,отличающаяся тем, что векторный процессор содержит М

секций, каждая из которых состоит из четы- рехканального коммутатора, ОЗУ действительной и мнимой частей, умножителей-накопителей действительной и мнимой частей, блока сверхоперативной

памяти, первого и второго шинных формирователей, при этом адресными входами векторного процессора являются адресные входы ОЗУ действительной и мнимой частей, соответствующие входы которых являются входами векторного процессора и соединены соответственно, с первыми входами - выходами первого и второго шинных формирователей и соответственно с первыми и вторыми входами - выходами четырехканального коммутатора, третьи входы - выходы которого соединены с входами - выходами умножителя-накопителя действительной части и первыми входами - выходами блока сверхоперативной памяти, вторые

входы - выходы которого соединены с четвертыми входами - выходами четырехка- нального коммутатора и входами - выходами умножителя-накопителя мнимой части, при этом вторые входы первого и

второго шинных формирователей являются входами данных векторного процессора, а третьи входы которых и третьи входы блока сверхоперативной памяти являются входами управления, выходы блока сверхоперативной памяти являются управляющими выходами векторного процессора.

3. Система по п.1,отличающаяся тем, что блок фильтрации содержит блок коммутаторов, выходы которых соединены с

первыми входами блока умножителей, выходы которого соединены с входами блока сумматоров, выходы которого соединены с первыми входами вычитающего сумматора, вторые входы которого и входы блока коммутатора являются вторыми входами блока фильтрации, выходами которого являются выходы вычитающего сумматора, вторые входы блока умножителей подключены к выходу первого блока буферных регистров,

вход которого подключен к выходу второго блока буферных регистров, вход которого является входом данных блока фильтрации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для автоматической дефектометрии | 1983 |

|

SU1190253A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Устройство автоматического получения и обработки изображений | 2019 |

|

RU2707714C1 |

| Устройство для векторно-растрового преобразования шрифтов | 1983 |

|

SU1201174A1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО БИНС | 2011 |

|

RU2469376C1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| НЕЙРОПРОЦЕССОР | 2011 |

|

RU2473126C1 |

| Перестраиваемый цифровой фильтр с программируемой структурой | 2016 |

|

RU2631976C2 |

Использование: в радиотехнике, в частности в радиолокационных и гидролокационных системах. Сущность изобретения: цифровая адаптивная антенная система содержит буферное запоминающее устройство,антенную решетку, диаграммообразующую схему, адаптивный процессор, состоящий из N блоков адаптации, N блоков фильтрации,вычислитель обратного значения, векторный процессор, блок управления, состоящий из блока микропрограммного управления, оперативного запоминающего устройства, дескрипторов, инкрементного и буферного регистров, мультиплексора данных, дешифратора, блока сравнения. 2 з.п,ф-лы, 5 ил.

фиг.1

Фи г. 2

Фиг.З

Фиг Л

| Цифровая адаптивная фазированная антенная система (ее варианты) | 1982 |

|

SU1228172A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-04-23—Публикация

1990-07-18—Подача