Изобретение относится к вычислительной технике и передаче данных и может быть использовано для полного уплотнения оптимальной формы t - кода оптимальной t - системы счисления.

Наиболее близким по технической сущности к предлагаемому является регистр сдвига t-кода, содержащий n-триггеров (n-разрядность кода) и n-блоков входной логики, причем выход k-го блока входной логики (k=1÷n) соединен с информационным входом k-го триггера, выход p-го триггера соединен с первым входом (p+1)-го блока входной логики (p=1÷[n-1]), вход последовательного занесения информации соединен с первым входом первого блока входной логики, выход n-го триггера является выходом регистра, тактовый вход и вход сброса которого соединены соответственно с входами разрешения приема и установки в ноль триггеров с 1-го по n-й, входы параллельного занесения информации соединены со вторыми входами соответствующих блоков входной логики, третьи входы которого объединены, установочный вход регистра соединен с третьим входом первого блока входной логики, выход m-го триггера (M=1 ÷ [n-t-1] соединен с четвертым входом (M+t+1) и блока входной логики, при этом блок входной логики содержит триггер, два элемента И, элемент ИЛИ, причем с первого по четвертый входы и выход блока входной логики соединены соответственно с первым входом второго элемента И, с первым входом элемент ИЛИ, с входом разрешения приема, с первым входом первого элемента ИЛИ, прямой и инверсный выходы триггера соединены с вторыми входами соответственно первого и второго элементов И, выходы которых соединены с вторым и третьим входами элемента ИЛИ, первый вход первого элемента И соединен с информационным входом триггера.

Недостатком этого устройства является низкое быстродействие за счет неполного уплотнения оптимальной формы t-кода.

Изобретение предназначено для повышения быстродействия устройства за счет полного уплотнения оптимальной формы t-кода.

Это достигается тем, что в устройство, содержащее n триггеров (n-разрядность кода) и n блоков входной логики, причем выход k-го блока входной логики (k=  ) соединен с информационным входом k-го триггера, выход p-го триггера соединен с первым входом (p+1)-го блока входной логики (p=

) соединен с информационным входом k-го триггера, выход p-го триггера соединен с первым входом (p+1)-го блока входной логики (p=  ), вход последовательного занесения информации устройства соединен с первым входом первого блока входной логики, выход n-го триггера является выходом устройства, тактовый вход и вход сброса которого соединены соответственно с входами разрешения приема и установки в ноль триггера с первого по n-1, входы параллельного занесения информации устройства соединены со вторыми входами соответствующих блоков входной логики, третьи входы которых объединены и соединены с установочным входом устройства, выход М-го триггера ( M=

), вход последовательного занесения информации устройства соединен с первым входом первого блока входной логики, выход n-го триггера является выходом устройства, тактовый вход и вход сброса которого соединены соответственно с входами разрешения приема и установки в ноль триггера с первого по n-1, входы параллельного занесения информации устройства соединены со вторыми входами соответствующих блоков входной логики, третьи входы которых объединены и соединены с установочным входом устройства, выход М-го триггера ( M=  ) соединены с четвертым входом (M+t+1)-го блока входной логики, введены m2t-входовых элементов ИЛИ-НЕ (m=n-2t-1), причем выходы триггеров с (k+1)-го по (k+2t)-й соединены соответственно с входами с первого по 2t-й соответствующих m элементов ИЛИ-НЕ, выходы триггеров с первого по n-t-1-й соединены с пятыми входами (М+t+1)= x блоков входной логики, а выходы m элементов ИЛИ-НЕ соединены соответственно с шестыми входами (k+2t+1)-x блоков входной логики, каждый из которых содержит первый, второй, третий и четвертый элементы И, первый и второй элементы ИЛИ и первый и второй D-триггеры, причем первый вход блока входной логики соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, первый вход которого является вторым входом блока входной логики, третий вход которого соединен с синхровходами первого и второго D-триггеров, информационный вход первого D-триггера соединен с первым входом третьего элемента И и является четвертым входом блока входной логики, пятый вход которого соединен с первым входом четвертого элемента И, выход третьего и четвертого элементов И соединены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с третьим входом первого элемента ИЛИ, выход которого является выходом блока входной логики, шестой вход которого соединен с информационным входом второго D-триггера, прямой и инверсный выходы которого соединены соответственно со вторыми входами четвертого и третьего элементов И, а прямой и инверсный выходы первого D-триггера соединены соответственно со вторыми входами второго и первого элементов И.

) соединены с четвертым входом (M+t+1)-го блока входной логики, введены m2t-входовых элементов ИЛИ-НЕ (m=n-2t-1), причем выходы триггеров с (k+1)-го по (k+2t)-й соединены соответственно с входами с первого по 2t-й соответствующих m элементов ИЛИ-НЕ, выходы триггеров с первого по n-t-1-й соединены с пятыми входами (М+t+1)= x блоков входной логики, а выходы m элементов ИЛИ-НЕ соединены соответственно с шестыми входами (k+2t+1)-x блоков входной логики, каждый из которых содержит первый, второй, третий и четвертый элементы И, первый и второй элементы ИЛИ и первый и второй D-триггеры, причем первый вход блока входной логики соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, первый вход которого является вторым входом блока входной логики, третий вход которого соединен с синхровходами первого и второго D-триггеров, информационный вход первого D-триггера соединен с первым входом третьего элемента И и является четвертым входом блока входной логики, пятый вход которого соединен с первым входом четвертого элемента И, выход третьего и четвертого элементов И соединены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с третьим входом первого элемента ИЛИ, выход которого является выходом блока входной логики, шестой вход которого соединен с информационным входом второго D-триггера, прямой и инверсный выходы которого соединены соответственно со вторыми входами четвертого и третьего элементов И, а прямой и инверсный выходы первого D-триггера соединены соответственно со вторыми входами второго и первого элементов И.

Таким образом, сущность изобретения состоит в расширении функциональных возможностей устройства путем введения M(2t)-входовых логических элементов ИЛИ-НЕ, соответствующих связей и блоков входной логики новой структуры.

Общая форма числа А в оптимальной форме t-кода имеет вид:

A = 1 1

1 1 0 ... 01

1 0 ... 01 (1) где m - число единиц, содержащихся в кодограмме;

(1) где m - число единиц, содержащихся в кодограмме;

ki - число нулей после каждой единицы, при этом

ki=t÷2t, i= ; t - натуральное число.

; t - натуральное число.

Из этой формулы видно, что для нее характерно наличие после каждой единицы пакетов из нулей, причем их число не больше 2t и не меньше t. Сущность работы устройства заключается в пропуске t нулей после каждой единицы, и единицы в случае, если перед ней находится 2t нулей. Это дает возможность увеличить пропускную способность канала связи за счет полного уплотнения кодовой комбинации.

Изобретение поясняется фиг.1 и 2.

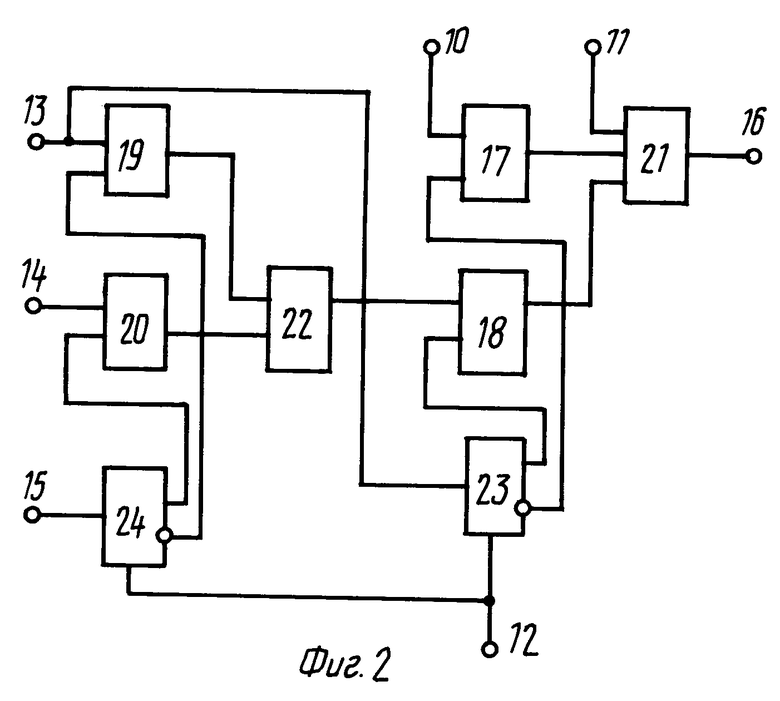

На фиг.1 изображена структурная схема предлагаемого устройства для t=1. Устройство (фиг. 1) содержит n триггеров 1.1-1.n, n блоков входной логики 2.1-2. n, 2t-входовые логические элементы ИЛИ-НЕ 3.1-3.m, входы 4.1-4.n параллельного занесения информации устройства, вход 5 последовательного занесения информации устройства, установочный вход 6 устройства, тактовый вход 7 устройства, вход сброса 8 устройства, выход 9 устройства.

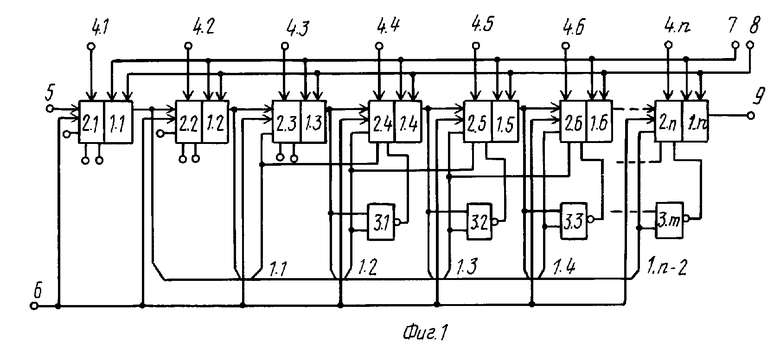

На фиг.2 изображена функциональная схема блока входной логики, который содержит элементы И 17-20, ИЛИ 21-22, D-триггеры 23-24, входы 10-15 блока входной логики, выход 16 блока входной логики.

Выход блока входной логики 2.k(k= ) соединен с информационным входом триггера 1. k, выход триггера 1.p соединен с первым входом блока входной логики 2. p+1(p=

) соединен с информационным входом триггера 1. k, выход триггера 1.p соединен с первым входом блока входной логики 2. p+1(p= ), вход 5 последовательного занесения информации устройства соединен с первым входом блока входной логики 2.1. Выход триггера 1.n является выходом 9 устройства, тактовый вход 7 и вход сброса 8 которого соединены соответственно с входами разрешения приема и установки в ноль триггеров 1.1-1.n, входы 4.1-4.n параллельного занесения информации устройства соединены со вторыми входами блоков входной логики 2.1-2.n, третьи входы которых объединены и соединены с установочным входом 6 устройства. Выход триггера 1.m (m=

), вход 5 последовательного занесения информации устройства соединен с первым входом блока входной логики 2.1. Выход триггера 1.n является выходом 9 устройства, тактовый вход 7 и вход сброса 8 которого соединены соответственно с входами разрешения приема и установки в ноль триггеров 1.1-1.n, входы 4.1-4.n параллельного занесения информации устройства соединены со вторыми входами блоков входной логики 2.1-2.n, третьи входы которых объединены и соединены с установочным входом 6 устройства. Выход триггера 1.m (m= ) соединен с четвертым входом блока входной логики 2. m+t+1, выходы триггеров 1.k+1-1.k+2t соединены соответственно с входами с первого по 2t-й соответствующих элементов ИЛИ-НЕ 3.1-3.m(m=n-2t-1), выходы триггеров 1.1-1. n-t-1 соединены с пятыми входами блоков входной логики 2.m+t+1. Выходы элементов ИЛИ-НЕ 3.1-3.m соединены соответственно с шестыми входами блоков входной логики 2.k+2t+1.

) соединен с четвертым входом блока входной логики 2. m+t+1, выходы триггеров 1.k+1-1.k+2t соединены соответственно с входами с первого по 2t-й соответствующих элементов ИЛИ-НЕ 3.1-3.m(m=n-2t-1), выходы триггеров 1.1-1. n-t-1 соединены с пятыми входами блоков входной логики 2.m+t+1. Выходы элементов ИЛИ-НЕ 3.1-3.m соединены соответственно с шестыми входами блоков входной логики 2.k+2t+1.

Блок входной логики 2.k (фиг.2) содержит элементы И 17-20, ИЛИ 21, 22 и D-триггеры 23, 24. Вход 11 блока входной логики соединен с первым входом элемента ИЛИ 21, второй вход которого соединен с выходом элемента И 17, первый вход которого является входом 10 блока входной логики, вход 12 которого соединен с синхровходами D-триггеров 23, 24. Информационный вход D-триггера 23 соединен с первым входом элемента И 19 и является входом 13 блока входной логики, вход 14 которого соединен с первым входом элемента И 20. Выходы элементов И 19 и 20 соединены с первым и вторым входами элемента ИЛИ 22, выход которого соединен с первым входом элемента И 18, выход которого соединен с третьим входом элемента ИЛИ 21, выход которого является выходом 16 блока входной логики, вход 15 которого соединен с информационным входом D-триггера 24, прямой и инверсный выходы которого соединены соответственно со вторыми входами элементов И 20 и 19, а прямой и инверсный выходы D-триггера 23 соединены соответственно со вторыми входами элементов И 18 и 17.

Триггеры 1.1-1.n и блок входной логики 2.1-2.n предназначены для запоминания информации и образования сокращенной комбинации с целью дальнейшей передачи, 2t-входовые элементы ИЛИ-НЕ предназначены для управления сокращением единиц при наличии перед ними 2t-нулей. Входы 4.1-4.n - для параллельной записи информации сокращают время записывания кодограммы в регистр. Вход 5 - для последовательной записи, если это необходимо. Установочный вход 6 - для управления процессом сокращения в области входной логики. Первый импульс подается после занесения кодограммы в регистр, преобразует путь перемещения кода при считывании, второй импульс подается после считывания информации для сброса триггеров 1.1-1.n и устройства в целом в исходное состояние, подготавливая его к следующей комбинации. Тактовый вход 7 - для синхронизации работы триггеров 1.1-1.n при записи-считывании, вход 8 - для сброса триггеров в ноль. Выход 9 - для выдачи сокращенного кода.

Вход 10 блока входной логики (фиг.2) - для последовательной, вход 11 - для параллельной записи информации, выход 13, 14, 15 - для организации сокращения кодограммы, вход 12 - для управления процессом сокращения, выход 16 - для занесения кодограммы в разряды триггеров 1.1-1.n.

Вновь введенные логические элементы ИЛИ-НЕ и блоки входной логики новой структуры, соответствующие связи обеспечивают положительный эффект действия устройства.

Устройство работает следующим образом. В исходном состоянии триггеры 1.1-1. n (фиг.1), D-триггеры 23 и 24 блоков входной логики (фиг.2) - в нулевом состоянии. В триггеры 1.1-1.n (фиг.1) устройства заносится код (пусть t= 1) через соответствующие входы 4.1-4.n или 5, параллельно или последовательно. Причем код заносится старшим разрядом в триггер 1.1, а младшим - в триггер 1. n, счет кодовой комбинации происходит младшим разрядом вперед. После занесения кодограммы в регистр на вход 6 подается установочный импульс, который проходит на синхровходы триггеров 23, 24 блоков входной логики 2.1-2. n. Пусть в триггеры 1.1, 1.4 записана единица, в триггеры 1.2, 1.3, 1.5 - нули. Тогда триггеры 24, 23 в блоке входной логики 2.6 перейдут в единичное состояние, так как их входы соединены соответственно с выходом элемента 3.1 ИЛИ-НЕ и выходом триггера 1.4, которые находятся в единичном состоянии, в блоке 2.3 входной логики триггер 23 перейдет в единичное состояние, триггер 24 останется в нулевом, так как его вход свободен.

Таким образом, триггер 24 блока входной логики 2.3 включит канал передачи информации 1.1-1.3, а триггеры 23, 24 блока входной логики 2.6 включат канал 1.3-1.6 таким образом, триггеры 1.2, 1.4, 1.5 перестают участвовать в сдвиге кода. Таким образом, если триггеры 23, 24 в нулевом состоянии (фиг. 2), то код при сдвиге перемещается по каналу: вход блока 10, элемент 17И, элемент 21ИЛИ, выход 16. Если триггер 23 в единичном состоянии, а триггер 24 в нулевом, то код при сдвиге перемещается по каналу: вход 13 блока, элемент 17И, элемент 22 ИЛИ, элемент 18И, элемент 21 ИЛИ, выход 16 блока (фиг.2). Если триггеры 23, 24 в единичном состоянии, то код перемещается по каналу: вход блока 14, элемент 20 И, элемент 22 ИЛИ, элемент 18 И, элемент 21 ИЛИ, выход блока 16 (фиг.2).

За счет перехода при считывании кодовой комбинации через один нулевой символ, через единичный и нулевой символы одновременно происходит полное сокращение длины кодовой комбинации.

После считывания кода на вход 6 подается второй импульс, на вход 8 - импульс сброса триггеров 1.1-1. n в ноль, после чего устройство готово к приему следующей кодовой комбинации.

Особенностью устройства является считывание информации младшим разрядом вперед. Если необходимо считывать в другую сторону, то нужно применить триггерный регистр с реверсным сдвигом.

Предлагаемое устройство позволит увеличить пропускную способность канала связи максимум в (2t) раза, время преобразования кода определяется только задержкой срабатывания триггеров 23 и 24 и элементов блока входной логики, т.е. обладает большим быстродействием. Уменьшение времени передачи t-колда позволяет снизить число каналов в многоканальной системе связи при одинаковом времени передачи.

Блок входной логики может применяться во всех подобных случаях, когда после и перед единицей определенное количество нулей.

Положительный эффект устройства заключается в полном уплотнении (сжатии) t-кода оптимальной формы, чем устраняется его структурная избыточность. Производный положительный эффект состоит в сокращении времени передачи кода и емкости в памяти для его хранения, а также в возможности реализации активной отказоустойчивости (за счет локализации и исключения искаженных символов) информационных систем.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для уплотнения @ -кода | 1989 |

|

SU1683179A1 |

| Устройство для уплотнения пакетной формы @ -кода | 1988 |

|

SU1619405A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК P-КОДОВ ФИБОНАЧЧИ | 1992 |

|

RU2045131C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В СИМВОЛЬНОМ КОДЕ | 1991 |

|

RU2021644C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК I-КОДОВ ФИБОНАЧЧИ | 1992 |

|

RU2045130C1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1991 |

|

RU2025772C1 |

| МАТРИЧНЫЙ КОММУТАТОР С ПРОГРАММИРУЕМОЙ ЛОГИКОЙ | 2003 |

|

RU2251792C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| Устройство для контроля оптимальных Р-кодов Фибоначчи | 1987 |

|

SU1471193A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2212715C2 |

Изобретение относится к вычислительной технике и передачи данных и может быть использовано для полного уплотнения оптимальной формы t-кода оптимальной t-системы счисления. Устройство для уплотнения оптимальной формы t-кода содержит n триггеров 1.1 ... 1.n, n блоков входной логики 2.1 ... 2. n, m 2t-входовых логических элементов ИЛИ - НЕ 3.1 ... 3.m, n входов 4.1 ... 4. n параллельного занесения информации, вход 5 последовательного занесения информации, установочный вход 6, тактовый вход 7, вход сброса 8 и выход 9, соединенные между собой функционально. 1 з.п.ф-лы, 2 ил.

) соединен с информационным входом K-го триггера, выход P-го триггера соединен с первым входом (P + 1)-го блока входной логики (P=

) соединен с информационным входом K-го триггера, выход P-го триггера соединен с первым входом (P + 1)-го блока входной логики (P=  ) , вход последовательного занесения информации устройства соединен с первым входом первого блока входной логики, выход n-го триггера является выходом устройства, тактовый вход и вход сброса которого соединены соответственно с входами разрешения приема и установки в "0" триггеров с первого по n-й, входы параллельного занесения информации устройства соединены с вторыми входами соответствующих блоков входной логики, третьи входы которых объединены и соединены с установочным входом устройства, выход M-го триггера (M =

) , вход последовательного занесения информации устройства соединен с первым входом первого блока входной логики, выход n-го триггера является выходом устройства, тактовый вход и вход сброса которого соединены соответственно с входами разрешения приема и установки в "0" триггеров с первого по n-й, входы параллельного занесения информации устройства соединены с вторыми входами соответствующих блоков входной логики, третьи входы которых объединены и соединены с установочным входом устройства, выход M-го триггера (M =  ) соединен с четвертым входом (M + t + 1)-го блока входной логики, отличающееся тем, что в него введены m 2t-входовых элементов ИЛИ - НЕ (m = n - 2t - 1), причем выходы триггеров с (K + 1)-го по (k + 2t)-й соединены соответственно с входами с первого по 2t-й соответствующих m элементов ИЛИ - НЕ, выходы триггеров с первого по (n - t - 1)-й соединены с пятыми входами (M + t + 1)-х блоков входной логики, а выходы m элементов ИЛИ - НЕ соединены соответственно с шестыми входами (K + 2t + 1)-х блоков входной логики.

) соединен с четвертым входом (M + t + 1)-го блока входной логики, отличающееся тем, что в него введены m 2t-входовых элементов ИЛИ - НЕ (m = n - 2t - 1), причем выходы триггеров с (K + 1)-го по (k + 2t)-й соединены соответственно с входами с первого по 2t-й соответствующих m элементов ИЛИ - НЕ, выходы триггеров с первого по (n - t - 1)-й соединены с пятыми входами (M + t + 1)-х блоков входной логики, а выходы m элементов ИЛИ - НЕ соединены соответственно с шестыми входами (K + 2t + 1)-х блоков входной логики.

| Авторское свидетельство СССР N 1487197, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-12-15—Публикация

1991-08-02—Подача