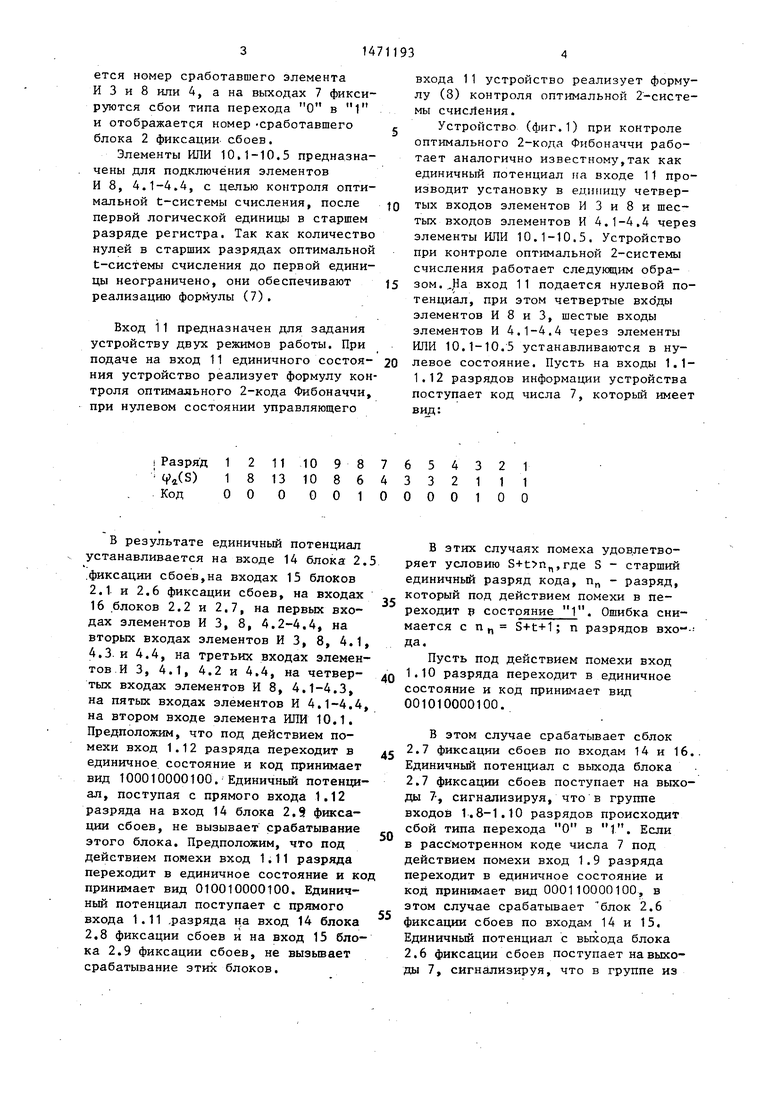

Блок 2 фиксации сбоев (фиг.2) содержит элемент И 12, элемент ИЛИ 13, входы 14-16.

В двоичной оптимальной t-системе счисления для заданного целого и любого натурального С существует представление в виде

С 11С5ф(8), (1)

где Cg 1 при (P (S-l)iC - 40 (K)i(S),

иначе Cg О,

где Ф. (S) - мощность оптимального t-кода;

{О, при , tM(2)

P(t)(S-t-j) + 1,пpи , 50 h«

V(S) - мощность оптимального t-кода Фибоначчи,

О, при , L, при Oi&tP,

V.(S-t-j),пpи .

)

(3)

,.., + Va

k,4-t

Va, Va

)Л

к,t

)A (7)

V(a.., Ла.-г.Л... a,., ) A A( Va, V... Уа„, Va)Y

,4ti., ..Л1,, Л

Ла

K.t3t

)Л

(K,.,..

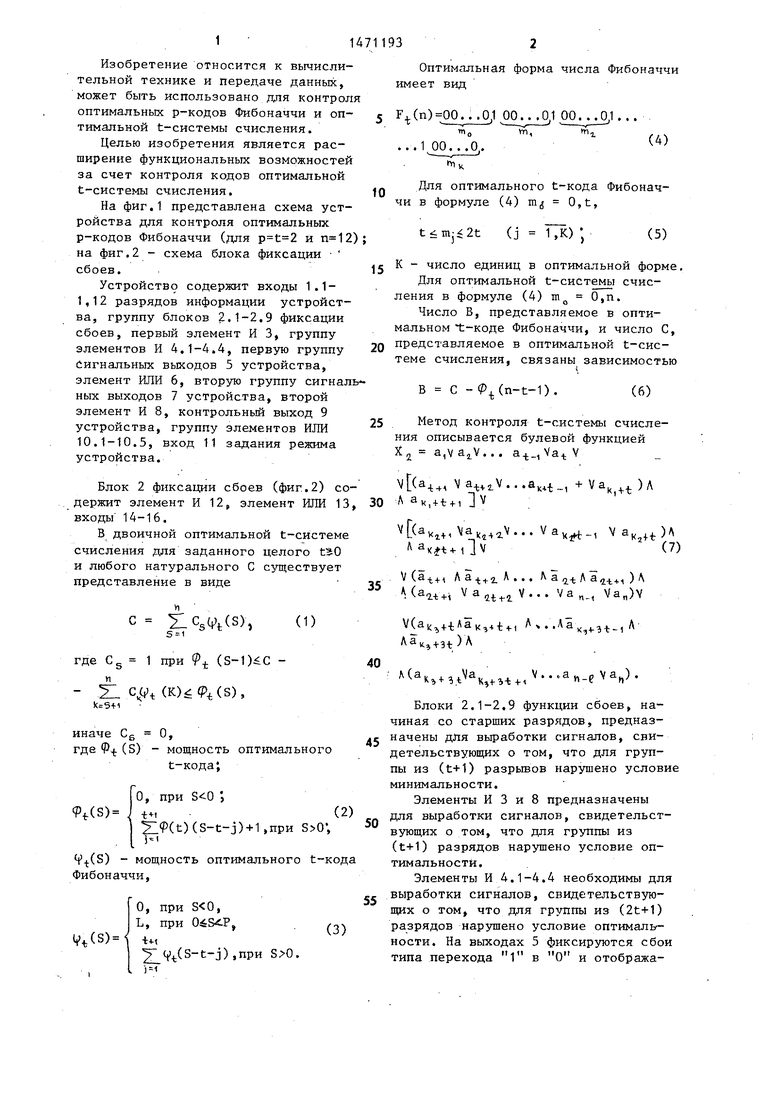

Блоки 2.1-2,9 функции сбоев, начиная со старших разрядов, предназначены для выработки сигналов, свидетельствующих о том, что для группы из (t+1) разрьтов нарушено условие минимальности.

Элементы И 3 и 8 предназначены для выработки сигналов, свидетельствующих о том, что для группы из (t+1) разрядов нарушено условие оптимальности.

Элементы И 4.1-4.4 необходимы для выработки сигналов, свидетельствующих о том, что для грзтпы из (2t+1) разрядов нарушено условие оптимальности. На выходах 5 фиксируются сбои типа перехода 1 в О и отображается номер сработавшего элемента И 3 и 8 или 4, а на выходах 7 фиксируются сбои типа перехода О в 1 и отображается номер -сработавшего блока 2 фиксации сбоев.

Элементы ИЛИ 10.1-10.5 предназначены для подключения элементов И 8, 4.1-4.4, с целью контроля оптимальной t-системы счисления, после первой логической единицы в старшем разряде регистра. Так как количество нулей в старших разрядах оптимальной й-системы счисления до первой единицы неограничено, они обеспечивают реализацию форйулы (7).

Вход 11 предназначен для задания устройству двух режимов работы. При подаче на вход 11 единичного состоя- ния устройство реализует формулу контроля оптимального 2-кода Фибоначчи, при нулевом состоянии управляющего

входа 11 устройство реализует формулу (8) контроля оптимальной 2-систе- мы счисления.

Устройство (фиг.1) при контроле оптимального 2-кода Фибоначчи работает аналогично известному,так как единичный потенциал на входе 11 производит установку в единицу четвертых входов элементов И 3 и 8 и шестых входов элементов И 4.1-4.4 через элементы ИЛИ 10.1-10.5. Устройство при контроле оптимальной 2-системы счисления работает следующим образом. „На вход 11 подается нулевой потенциал, при этом четвертые входы элементов И 8 и 3, шестые входы элементов И 4.1-4.4 через элементы ИЛИ 10.1-10.5 устанавливаются в нулевое состояние. Пусть на входы 1.1- 1.12 разрядов информации устройства поступает код числа 7, который имеет вид:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок | 1987 |

|

SU1578811A1 |

| Устройство для контроля оптимальных @ -кодов Фибоначчи | 1983 |

|

SU1149261A1 |

| Устройство для контроля @ -кодов Фибоначчи | 1983 |

|

SU1149262A1 |

| Устройство для обнаружения и исправления однократных ошибок оптимальных р-кодов Фибоначчи | 1987 |

|

SU1479932A1 |

| Устройство для обнаружения ошибок в пакетном @ -коде | 1987 |

|

SU1483645A1 |

| Устройство для контроля кодов | 1987 |

|

SU1552382A1 |

| Устройство для контроля р-кодовфибОНАччи | 1979 |

|

SU817718A1 |

| Устройство для контроля @ -кодов | 1988 |

|

SU1711335A1 |

| Устройство для контроля 2-кода Фибоначчи | 1988 |

|

SU1662009A1 |

| Устройство для обнаружения и исправления ошибок в @ -кодах Фибоначчи | 1986 |

|

SU1441400A1 |

Изобретение относится к вычислительной технике и передаче данных, может быть использовано для контроля оптимальных P - кодов Фибоначчи и оптимальной T - системы счисления. Цель изобретения - расширение функциональных возможностей за счет контроля кодов оптимальной T - системы счисления. Поставленная цель достигается тем, что устройство, содержащее группу блоков 2 фиксации сбоев, первый элемент И 3, группу элементов И 4, элемент ИЛИ 6 и второй элемент И 8, содержит группу элементов ИЛИ 10 с соответствующими связями. 2 ил.

I Разряд 12 11 10987654321

ViCS) 1813 10 8643321 11

Код 00 О 0010000100

В результате единичный потенциал устанавлив-ается на входе 14 блока 2. .фиксации сбоев,на входах 15 блоков 2.1 и 2,6 фиксации сбоев, на входах 16 блоков 2.2 и 2.7, на первых входах элементов И 3, 8, 4.2-4.4, на вторых входах элементов ИЗ, 8, 4.1, 4.3. и 4.4, на третьих входах элементов И 3, 4.1, 4.2 и 4.4, на четвер- тых входах элементов И 8, 4.1-4.3, на пятых входах элементов И 4.1-4.4, на втором входе элемента НИИ 10.1. Предположим, что под действием помехи вход 1.12 разряда переходит в единичное состояние и код принимает вид 100010000100. Единичный потенциал, поступая с прямого входа 1.12 разряда на вход 14 блока 2.9 фиксации сбоев, не вызывает срабатывание этого блока. Предположим, что под действием поиехи вход 1.11 разряда переходит в единичное состояние и ко принимает вид 010010000100. Единичный потенциал поступает с прямого входа 1.11 .разряда на вход 14 блока 2.8 фиксации сбоев и на вход 15 блока 2.9 фиксации сбоев, не вызьшает срабатывание этих блоков.

5

Q с

5

В этих случаях помеха удовлетворяет условию ,гдe S - старший единичный разряд кода, п„ - разряд, который под действием помехи в переходит р состояние 1. Ошибка снимается с п„ S+t+1 ; п разрядов вхо-- да.

Пусть под действием помехи вход 1.10 разряда переходит в единичное состояние и код принимает вид 001010000100.

В этом случае срабатывает сблок 2.7 фиксации сбоев по входам 14 и 16.. Единичный потенциал с выхода блока 2.7 фиксации сбоев поступает на выходы 7, сигнализируя, что в группе входов 1.8-1.10 разрядов происходит сбой типа перехода О в 1. Если в рассмотренном коде числа 7 под действием помехи вход 1.9 разряда переходит в единичное состояние и код принимает вид 000110000100, в этом случае срабатывает блок 2.6 фиксации сбоев по входам 14 и 15. Единичный потенциал с выхода блока 2.6 фиксации сбоев поступает на выходы 7, сигнализируя, что в группе из

5

входов 1.7-1.9 разрядов происходит сбой типа перехода О в 1.

Пусть под действием помехи вход 1.7 разряда переходит в единичное состояние и код принимает вид 000011000100. Срабатывает блок 2.5 фиксации сбоев по входам 14 и 15 и сигнал помехи передается с блока 2.5 фиксации сбоев на выходы 7. Если под действием помехи вход 1.6 разряда переходит в единичное состояние и код принимает вид 000010100100, срабатывает блок 2.5 фиксации сбоев по вхо- дам 14 и 16 и сигнал помехи передается с блока 2.5 фиксации сбоев на выходы 7. Если под действием помехи вход 1,5 разряда переходит в единичное состояние и код принимает вид 000010010100, срабатывает по входам 14 и 16 блок 2.2 фиксации сбоев и передает сигнал на выходы 7. Если под действием помехи вход 1.4 разряда переходит в единичное состо- яние и код принимает вид 00001000110 срабатывает по входам 14 и 15 блок 2,1 фиксации сбоев и передает сигнал на выходы 7.

Если в единичное состояние пере- ходят входы 1.1 или 1.2 разрядов, единичные потенциалы, сигнализирующие об искажении оптимальной 2-сис- темы счисления, поступают на соответствующие входы элемента ИЛИ 6 и вы- ходы 7.

Предположим, что под действием помехи вход 1.8 разряда переходит в нулевое состояние. Тогда код принимает вид 000000000100. Этот, код не является нарушением оптимальной t-системы счисления. Пусть под действием помехи вход 1.3 разряда переходит в нулевое состояние. Тогда код принимает вид 000010000000.

Единичньй потенциал установится на выходе элемента И 8, этот единичный потенциал поступает на выходы 5, указьшая, что.в группе из входов 1.3-1.5 разрядов происходит сбой ти- па перехода 1 в О и через элемент ИЛИ 6 устанавливается на конт-, рольном выходе 9,

Таким образом, наряду с сохранением эффективности контроля оптималь ного t-кода Фибоначчи, предлагаемое устройство дополнительно обеспечивав ет обнаружение всех однократных сбо-- ев типа переход О в 1 и типа

g 5 0 5

О

о 5

5

переход 1 в О, кроме S-ro разряда в оптимальной системе счисления .

Ошибки большей кратности обнаруживаются устройством частично. Если в рассматриваемом коде числа 1 под действием помехи в единичное состояние переходит вход 1.4 разряда, а вход 1.3 разряда одновременно переходит в нулевое состояние, не происходит нарушения формы числа в оптимальной t-системе счисления и устройство не вьщает сигнал ошибки. Если в рассматриваемом коде числа 7 под действием помехи в единичное состояние переходит вход 1.6 разряда, а вход 1.3 разряда переходит одновременно в нулевое состояние, на входах 14 и 16 блока 2.5 фиксации сбоев устанавливается единичный потенциап, который вызывает его срабатывание. С блока 2.5 фиксации сбоев сигнал .ошибки поступает на выходы 7 устройства.

Формула изобретения

Устройство для контроля оптимальных р-кодов Фибоначчи, содержащее группу блоков фиксации сбоев, два элемента И, группу элементов И и элемент ИЛИ, причем прямые входы с первого по р-й разрядов информационного входа устройства, выходы блоков фиксации сбоев группы, первого и второго элементов И и элементов И группы соединены соответственно с входами элемента ИЛИ, выход которого является контрольным выходом устройства, прямой вход j-ro разряда информационного входа устройства (j (р+1)...п, п - количество разрядов информационного входа) соединен с первым входом ( блока фиксации сбоев группы и с (k+1)-M входом (j-p+k-1)- го блока фиксации сбоев группы (k 1...р), инверсньп вход j-ro разряда информационного входа устройства соединен с (n-j+1)-M входом первого элемента И, с (2p+2-j)-M входом второго элемента И и с (Зр+2+m- -j)-M входом т-го элемента И группы (т 1...п-Зр-2), выход первого элемента И, выходы элементов И группы и выход второго элемента И являются первой группой сигнальных выходов устройства, прямые входы с первого

по р-й разрядов информационного входа устройства и выходы блоков фиксации сбоев группы являются второй группой сигнальных выходов устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет контроля кодов оптимальной t-системы счисления (tijop), оно содержит группу элементов ИЛИ, причем вход задания режима устройства соединен с первым входом (n-3t-1)-ro элемента ИЛИ группы и с ()-M входом первого элемента И, вькод (г+1)-го элемента ИЛИ группы (г 1...П - 3t - 2) сое/4

динен с первым входом г-го элемента ИЛИ группы и с (2t+2)-M входом г-го элемента И группы, выход первого элемента ИЛИ группы соединен с (t+2)-M входом второго элемента И, прямые входы с (2t+2)-ro по (Зt+2)-й разрядов информационного входа устройства соединены соответственно с вхо-- дами с второго по (t+2)-й первого элемента ИЛИ группы, прямые входы с (3t+3)-ro по п-й разрядов информационного входа устройства соединены соответственно с вторыми входами с второго по (п-Зь-1)-й элементов ИЛИ группы.

Фиг.

| Устройство для контроля пакетных @ кодов | 1985 |

|

SU1293731A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-07—Публикация

1987-09-29—Подача