Изобретение относится к вычислительной технике и может быть использовано для построения параллельных коммутационных устройств в универсальных системах и структурах высокой производительности, ориентированных на реализацию в виде СБИС.

Известно устройство коммутации, содержащее блок памяти, первый и второй адресные блоки, матричный коммутатор, счетчик, регистр, третий адресный блок (авт. св. N 1211870). Известно коммутационное устройство, содержащее матрицу из MxN-матричных переключателей, каждый из которых содержит матрицу D-триггеров, состоящую из n строк, m столбцов и nxm-управляемых ключей, а кроме того, D-триггеров (m+1)-го управляющего столбца матрицы, основные и дополнительные буферные формирователи, двухвходовые элементы (авт. св. N 1307572). Недостатком известных устройств является низкая надежность, обусловленная отсутствием элементов, позволяющих восстановить его работоспособность в случае отказа коммутационного поля.

Известен матричный коммутатор, содержащий n горизонтальных и n вертикальных коммутируемых шин, в каждой точке пересечения которых расположен коммутационный узел, а также n узлов подключения абонентов, перепрограммируемое постоянное запоминающее устройство и блок управления настройкой [1].

Известен многоканальный резервированный коммутатор, содержащий N блоков коммутации, дополнительный блок коммутации, ключей информационную шину, входы начальной установки и записи, входную и выходную шины (авт. св. N 1483623). Недостатком известных устройств является низкая надежность, сложность управления настройкой элементами коммутации.

Известен многоканальный коммутатор, содержащий N основных блоков, дополнительный блок, первую группу N релейных элементов, входы которых соединены с выходом соответствующего основного блока, а управляющие входы соединены с первой выходной шиной дополнительного блока, входы соединены с первой выходной шиной дополнительного блока, входы записи шины адреса и входные шины основных и дополнительного блоков соединены с одноименными входами и шинами многоканального коммутатора, каждый из основных блоков содержит адресный селектор, вход которого соединен с шиной адреса, блока, элемент И, первый вход которого подключен к входу записи блока, выход элемента И соединен с входом записи регистра, выход которого через дешифратор соединен с управляющими входами K релейных элементов, входы которых соединены с соответствующими цепями входной шины, а выходы объединены и подключены к выходу основного блока, дополнительный блок содержит адресный селектор, вход которого соединен с адресной шиной, а выход - с S-входом триггера, вторую группу релейных элементов, содержащую N строк и K столбцов, третью группу релейных элементов, содержащую N подгрупп N релейных элементов, выход каждого релейного элемента первой группы релейных элементов подключен к соответствующей цепи выходной шины и объединенным выходам релейных элементов соответствующей подгруппы третьей группы релейных элементов, входы одноименных релейных элементов подгрупп третьей группы объединены и подключены к объединенным выходам K-релейных элементов одноименной строки второй группы релейных элементов, входы которых соединены с одноименными цепями входной шины, управляющие входы релейных элементов второй и третьей групп релейных элементов, подключенных соответственно к второй и третьей выходным шинам дополнительного блока, шина данных многоканального коммутатора соединена с одноименными шинами основных и дополнительного блоков, вход начальной установки соединен с одноименным входом дополнительного блока, в каждом основном блоке его шина данных соединена с информационным входом регистра, а выход селектора адреса соединен с вторым входом элемента И.

Недостатком прототипа является то, что для контроля работоспособности коммутатора необходим специальный режим работы, позволяющий с помощью внешнего оборудования произвести его тестирование. По его завершении возможно восстановление работоспособности коммутатора и дальнейшая работа. Однако отказ коммутатора может произойти и после окончания режима его тестирования, а именно в процессе его непосредственной работы при перепрограммировании структуры. Но в этом случае пользователь вычислительной системы, в которой он используется, будет работать с коммутатором как с работоспособным и получать ложные результаты.

Целью изобретения является повышение надежности за счет самовосстановления работоспособности.

Достигается это тем, что в многоканальный коммутатор введена четвертая группа N-релейных элементов, первый и второй входы последних соединены соответственно с одноименными цепями выходной шины и одноименными выходами адресных селекторов N-основных блоков, соединенных, кроме того, с шиной селекции дополнительного блока, пятый и шестой вход которого соединен соответственно с первыми и вторыми выходами N-релейных элементов четвертой группы, а K цепей входной шины соединены с одноименными цепями третьего входа N-релейных элементов четвертой группы.

Кроме того, поставленная цель достигается тем, что дополнительный блок содержит первые группы элементов И, регистров, элемент ИЛИ, регистр, первый, второй элемент задержки, схему сравнения, группу схем сравнения, преобразователь сопротивление - код, вторые группы элементов И, регистров, первую и вторую группу дешифраторов, цепи шины селекции дополнительного блока подключены к первым входам соответствующих элементов И первой группы и одноименным входам элемента ИЛИ, выход которого через первый элемент задержки соединен с первым входом схемы сравнения, выходы первой группы элементов И соединены с соответствующими входами записи регистров первой группы, шина данных дополнительного блока подключена к информационным входам регистра и регистров второй группы, шина адреса дополнительного блока соединена с информационными входами регистров первой группы и первыми входами схем сравнения, выходы последних соединены с первыми входами соответствующих элементов И второй группы, первый и второй выходы первой группы регистров соединены соответственно с соответствующими вторыми входами группы схем сравнения, первыми входами одноименной группы дешифраторов и вторыми входами последних, первые и вторые выходы первой группы дешифраторов соответственно соединены с третьей и первой выходной шиной дополнительного блока, вход записи последнего соединен с одноименным входом регистра, выход которого подключен к второму входу схемы сравнения, третий вход последней связан с выходом преобразователя сопротивления, выход схемы сравнения соединен с вторыми входами схем И первой группы и через второй элемент задержки подключен к вторым входам одноименной группы схем И, выходы последних соединены с входами записи соответствующих регистров второй группы регистров, выходы которых через дешифраторы второй группы дешифраторов связаны с второй выходной шиной дополнительного блока, причем пятый и шестой входы дополнительного блока соединены соответственно с первым и вторым входом преобразователя сопротивление - код.

Вышеописанные отличительные признаки предлагаемого устройства способствует повышению надежности за счет самовосстановления работоспособности.

Анализ отличительных признаков аналогов, прототипа, устройств решающих аналогичную цель, показывает, что такой отличительный признак предлагаемого изобретения, как четвертая группа релейных элементов отсутствует у известных устройств. Кроме того, такие отличительные признаки как основные и дополнительные блоки не могут быть применены в предлагаемом изобретении для достижения поставленной цели. Необходимо было такое изменение их структуры и введение новых связей, которое позволило получить качественно новый эффект, отсутствующий у известных устройств.

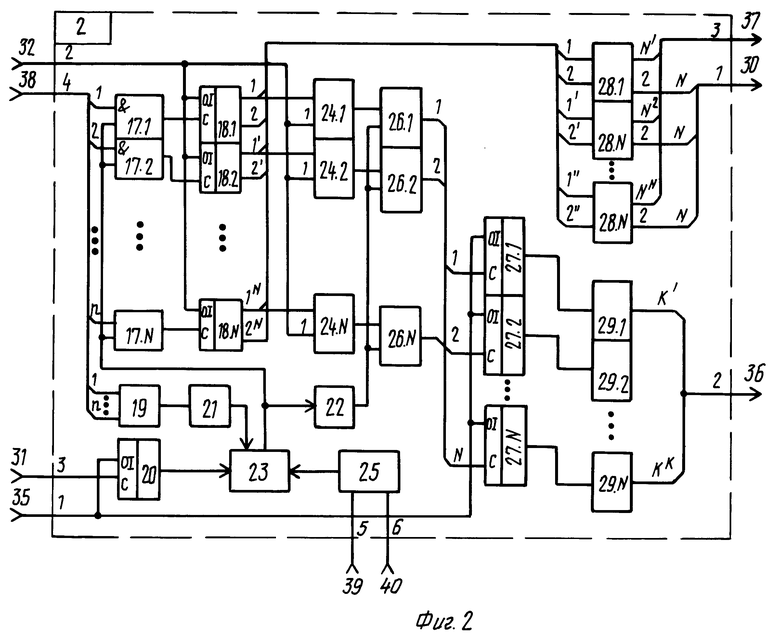

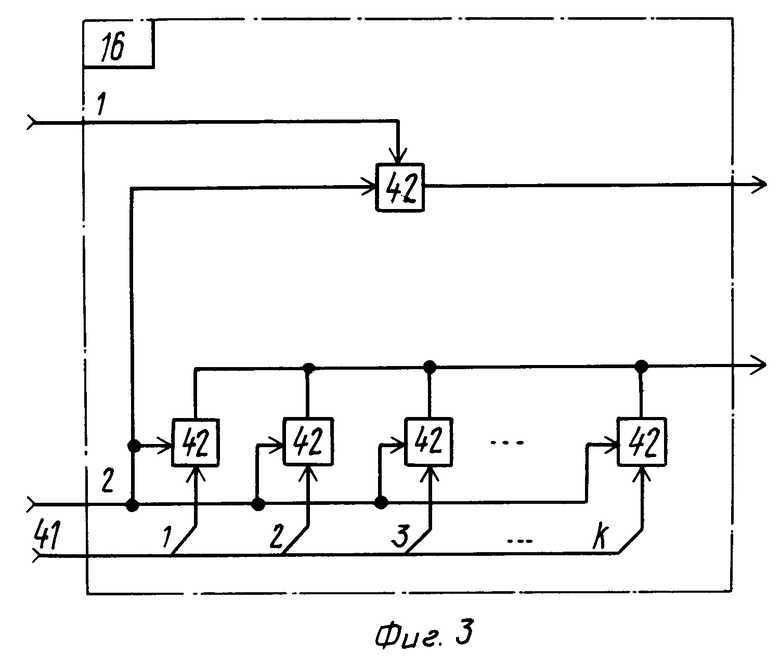

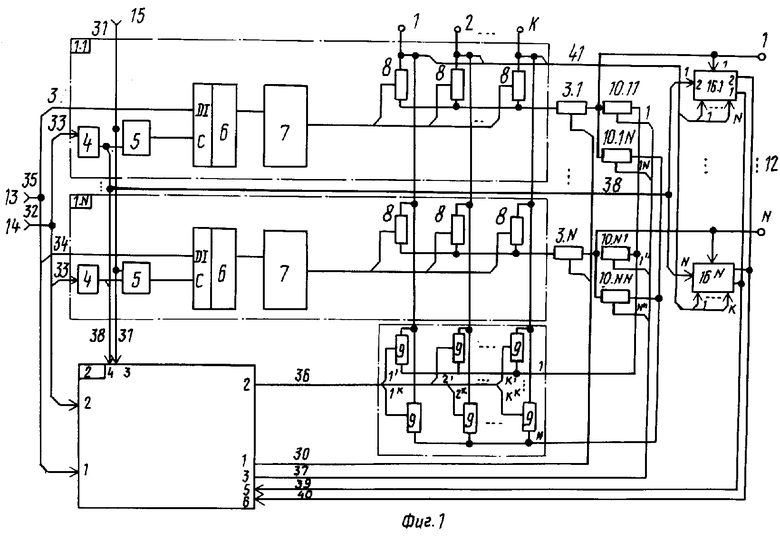

На фиг. 1 представлена функциональная схема многоканального коммутатора; на фиг. 2 - функциональная схема дополнительного блока; на фиг. 3 - функциональная схема четвертой группы релейных элементов.

Многоканальный коммутатор (фиг. 1) содержит N основных блоков 1.1-1.N, дополнительный блок 2, первую группу релейных элементов, содержащую N релейных элементов 3.1-3.N, адресный селектор 4, элемент И 5, регистр 6, дешифратор 7, K релейных элементов 8.1-8.К, вторую группу релейных элементов 9.11-9N.K, содержащую N строк и К столбцов, третью группу релейных элементов 10.11-10.N.N, содержащую N подгрупп из N релейных элементов, входную шину 11, выходную шину 12, шину 13 данных, шину 14 адресов, вход 15 записи, четвертую группу релейных элементов, содержащую N релейных элементов 16.1-16.N.

Дополнительный блок (фиг. 2) содержит первые группы элементов И 17.1-17. N, регистров 18.1-18.N, элемент ИЛИ 19, регистр 20, первый 21 и второй 22 элемент задержки, блок 23 сравнения, группу схем-блоков сравнения 24.1-24. N, преобразователь сопротивление - код 25, вторые группы элементов И 26.1-26. N, регистров 27.1-27.N, первую 28 и вторую 29 группы дешифраторов. Четвертая группа релейных элементов (фиг. 3) содержит (K+1)-релейных элементов 42.

Входы релейных элементов 3.1-3.N соединены с выходом соответствующего основного блока 1.1-1. N, а управляющие входы соединены с первой выходной шиной 30 дополнительного блока 2. Входы 31 записи основных блоков 1.1-1.N соединены с входом 15 записи. Шина 14 адреса соединена с шиной 32 адреса основных 1.1-1.N блоков и шиной 33 адреса дополнительного блока 2. Шина 13 данных соединена с шиной 34 данных основных 1.1-1.N блоков и шиной 35 данных дополнительного блока 2. Входная шина 11 соединена с входными шинами основных блоков 1.1-1. N и с объединенными выходами К-релейных элементов 9.11-9. N. K второй группы релейных элементов. Вход селектора 4 каждого из основных блоков 1.1-1. N соединен с шиной 32 адреса блока, первый вход элемента И 5 соединен с входом 31 записи, выход элемента И 5 соединен с входом записи регистров, выход которого через дешифратор 7 соединен с управляющими входами K релейных элементов 8.1-8.К, входы которых соединены с соответствующими цепями входной шины блока, а выходы объединены и подключены к выходу блока. Выход каждого релейного элемента 3.1-3.N первой группы релейных элементов подключен к соответствующей цепи выходной шины 12 и объединенным выходам релейных элементов 10.11-10.N.N, соответствующей подгруппы третьей группы релейных элементов, входы одноименных релейных элементов 10.11-10. N.N подгруппы третьей группы объединены и подключены к объединенным выходам К-релейных элементов 9.11-9.N.K одноименной строки второй группы релейных элементов, управляющие входы релейных элементов 9.11-9.N.K, 10.11-10. N. N второй и третьей групп релейных элементов подключены соответственно к второй 36 и третьей 37 выходным шинам дополнительного блока 2. Первый и второй входы релейных элементов 16.1-16.N соединены соответственно с одноименными цепями выходной шины 12 и одноименными цепями шины селекции 38 адресных селекторов 4 основных блоков 1.1-1.N, соединенных с шиной селекции дополнительного блока 2, пятый и шестой вход которого соединен соответственно линиями 39-40 с первыми и вторыми выходами N релейных элементов 16.1-16. N.К цепей входной шины 11 шиной 41 соединены с одноименными цепями третьего входа релейных элементов 16.1-16.N. В каждом основном блоке 1.1-1. N его шина 34 данных соединена с информационным входом регистра 6, выход селектора 4 адреса соединен с вторым входом элемента И 5, а выход каждого N селектора 4 адреса соединен с шиной 38 селекции.

Цепи 1-N шины 39 селекции дополнительного блока 2 подключены к первым входам соответствующих элементов И 17.1-17.N первой группы и одноименным входам элемента ИЛИ 19, выход которого через первый элемент 21 задержки соединен с первым входом блока 23 сравнения, выходы 42 первой группы элементов И 17.1-17. N соединены с соответствующими входами записи регистров 18.1-18. N первой группы, шина 35 данных дополнительного блока 2 подключены к информационным входам регистра 20 и регистров 27.1-27.N второй группы, шина 32 адреса дополнительного блока 2 соединена с информационными входами регистров 18.1-18.2 первой группы и первыми входами блоков сравнения 24.1-24.N. Выходы 43 блоков сравнения 24.1-24.N соединены с первыми входами соответствующих элементов И 26.1-26.N второй группы. Первый и второй выходы первой группы регистров 18.1-18.N соединены соответственно с соответствующими вторыми входами группы блоков сравнения 24.1-24.N, первыми входами одноименной группы дешифраторов 28.1-28. N и вторыми входами последних. Первые и вторые выходы первой группы дешифраторов 28.2-28.N соответственно соединены с третьей 37 и первой 30 выходной шиной дополнительного блока 2, вход 31 записи последнего соединен с одноименным входом регистра 20, выход которого подключен к второму входу блока 23 сравнения. Третий вход блока 23 сравнения связан с выходом преобразователя 25 сопротивление-код, выход блока 23 сравнения соединен с вторыми входами схем И 17.1-17.N первой группы и через второй элемент 22 задержки подключен к вторым входам одноименной группы элементов И 26.1-26. N. Выходы элементов И 26.1-26.N соединены с входами записи соответствующих регистров 27.1-27.N второй группы регистров, выходы которых через дешифраторы 29.1-29.N второй группы дешифраторов связаны с второй выходной шиной 36 дополнительного блока 2, причем пятый и шестой входы дополнительного блока 2 линиями 39 и 40 соединены соответственно с первым и вторым входом преобразователя 25 сопротивление-код.

Селектор 4 служит для селекции адреса блока 1.1-1.N, регистр 6 и дешифратор 7 предназначены соответственно для записи двоичного кода и преобразования его в унитарный код, в соответствии с которым срабатывает один из K(1. ..K) релейных элементов 8 (1...N) строки. Дополнительный блок 2 служит для замены вышедших из строя блоков 1.1-1.N. Первая группа релейных 3 элементов предназначена для отключения неисправных (1...N) строк по К(1... К) релейных элементов от (1...N) цепей выхода 12 устройства. Вторая группа релейных 9 элементов предназначена для замены (1...N) строк по К(1...К) элементов матрицы элементов 8. Третья группа релейных 10 элементов предназначена для подключения (1...N) строк матрицы элементов 9 к соответствующим (1...N) цепям выхода 12 устройства. Четвертая группа релейных 16.1-16.N элементов предназначена для формирования сопротивления параллельного соединения К(1...К) релейных элементов одноименной N(1...N) строки.

Группа регистров 18.1-18.N предназначена для записи адресов неисправных блоков 1.1-1.N, регистр 20 служит для записи текущего адреса блока 1.1-1.N, схема 23 сравнения служит для сравнения кодов сопротивления параллельного соединения К релейных элементов N(1...N) строки и эталонного кода сопротивления, записываемого в регистр 20; схемы 24.1-24.N служат для сравнения адресов и формирования сигналов, разрешающих прохождение сигнала записи информации на соответствующие синхровходы регистров 27.1-27.N; преобразователь сопротивление-код предназначен для формирования кода сопротивления параллельного соединения К(1. ..К) релейных элементов 8; группа регистров 27.1-27.N предназначена для записи двоичных кодов управления второй группой релейных элементов 9. Дешифраторы 28.1-28.N служат для формирования двоичных кодов управляющих подключением резервных ключевых элементов 9 к цепям выхода 12 устройства. Дешифраторы 29.1-29.N служат для формирования унитарного кода управления элементами 9.

В начальный момент времени на выходе селекторов 4 находится уровень "0"; на выходе регистров 6, 18.1-18.N, 20, 27.1-27.N - уровень "0" (цепь начальной установки условно не показана); элементы 3.1-3.N находятся в замкнутом состоянии; элементы 10.11-10.N находятся в разомкнутом состоянии; на выходе блока сравнения 23 находится уровень "0".

Блок 23 сравнения, преобразователь 25 сопротивление-код описаны в кн.: Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. - Л.: Энергоатомиздат, 1986.; Алексеенко А.Н., Коломбет Е.А., Стародуб Г. И. Применение прецизионных аналоговых ИС. - M.: Радио и связь. 1981, с. 224.

Многоканальный коммутатор работает следующим образом. На адресную шину 14 устройства подается адрес селектора 4 одного из блоков 1.1-1.N. При совпадении послужившего по шине 14 адреса и записанного в селекторе 4 соответствующего блока 1.1-1.N на выходе селектора 4 появляется уровень "1", который поступает на вход элемента 5 по шине 38 поступает на четвертый вход блока 2 и управляющие входы ключей 16.1-16.N на шину 13 данных, передается двоичный код, соответствующий номеру элемента 8.1-8.К, а на вход 15 записи сигнал записи, который запишет код с шины данных в регистр 6. В соответствии с поступившим двоичным кодом дешифратор 7 формирует унитарный код, который включает соответствующий 8.1-8.К элемент. Далее повторяется вышеописанный алгоритм записи управляющего кода в остальные 1.1-1.N блоки.

В случае неисправности блоков 1.1-1.N, т.е. отказе элемента 5, регистра 6, дешифратора 7, неисправности релейных элементов 8.1-8.К типа "Обрыв", "Залипание" работоспособность коммутатора можно восстановить за счет отключения неисправных блоков 1.1-1.N и подключения взамен резервных элементов блока 2. Процедура контроля работоспособности блоков 1.1-1.N и самовосстановления работоспособности коммутатора выполняется одновременно с описанными выше процедурами его программирования. При этом выполняется следующая последовательность действий.

Находящиеся на шине 32 адресов и шине 35 данных коды поступают соответственно на информационный вход группы регистров 18.1-18.N и информационный вход регистра 20, группы регистров 27.1-27.N блока 2. Сигнал записи с входа записи 15 стробирует код данных в регистр 20, который с его выхода поступает на второй вход блока 23 сравнения. Одновременно с этим сигнал уровня "1" с выхода адресного селектора 4 соответствующего блока 1.1-1.N по шине 38 поступает на управляющий второй вход одноименного релейного элемента 16.1-16.N. В релейном элементе 16.1-16.N (фиг. 3) открываются ключи 42 и на их выходах подается сопротивление последовательного соединения релейных элементов следующей цепи (например, для релейных элементов 16.1): параллельного соединения 8.1-8.К, 3.1. В соответствии со сформированным сопротивлением преобразователь 25 сопротивление-код формирует соответствующий двоичный код, который поступает на третий вход блока 23 сравнения. Одновременно с этим сигнал уровня "1" с выхода адресного селектора 4 соответствующего блока 23 сравнения. Одновременно с этим сигнал уровня "1" с выхода адресного селектора 4 соответствующего блока 1.1-1.N через элемент ИЛИ 19, элемент 21 задержки поступает на первый вход схемы 23 сравнения и разрешает ее работу. Блок 23 сравнивает находящиеся на их вторых и третьих входах коды данных и в случае их несовпадения, что свидетельствует о неисправности одного из блоков 1.1-1.N, на ее выходе появляется перепад 0/1 через соответствующий элемент И 17.1-17.N (на первом входе которого находится уровень "1" с выхода селектора 4 блока 1.1-1.N) стробирует адрес неисправного блока 1.1-1. N в соответствующий регистр 18.1-18.N. Записанный адрес поступает на второй вход соответствующего блока 24.1-14.N сравнения 8, на втором входе которой находится такой же адрес, и на ее выходе устанавливается уровень "1".

В соответствии с записанным в регистр 18.1-18.N адресом на первом выходе соответствующего дешифратора 28.1-28.N устанавливается код, в соответствии с которым размыкаются элементы 3.1-2.N, а на вторых выходах дешифраторов 28.1-28. N устанавливается унитарный код, в соответствии с которым подключаются резервные строки элементов 10.11-10.К.

Одновременно с этим перепад 0/1 с выхода схемы 23 сравнения, через элемент 22 задержки, соответствующий элемент И 26.1-26.N стробирует код данных с шины 35 в соответствующий регистр 27.1-27.N. В соответствии с записанным кодом соответствующий дешифратор 29.1-29.N формирует унитарный код, который включает один из элементов 9.11-9.N.K.

Далее повторяется программирование связей элементов 8.1-8.N.K, последовательность действий которых рассмотрена выше.

В устройстве предусмотрена возможность подключения любой исправной строки элементов 9.11-9.N.K к выходу устройства. Для этого необходимо повторно переписать в регистр 18.1-18. N адрес резервной строки элементов 9.11-9.N.K.

Введение в предлагаемый многоканальный коммутатор четвертой группы релейных элементов, ряда новых связей, изменение конструкции дополнительного блока позволяет заменить отказавшую N(1...N) строку коммутационного поля или его устройство управления исправным устройством. Это производится одновременно с процессом программирования связей коммутатора, что позволяет исключить его отказы, возникающие в процессе его программирования, тем самым повышая надежность устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Многоканальный резервированный коммутатор | 1989 |

|

SU1737723A1 |

| ЭВМ | 1990 |

|

RU2024928C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046396C1 |

| ЦИФРОАНАЛОГОВАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ И ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2022364C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2049347C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения параллельных коммутационных устройств в универсальных системах и структурах высокой производительности. Многоканальный коммутатор содержит N основных блоков (1...N), 1 дополнительный блок /2/, 1 первую группу релейных элементов (3...N), 1 адресный селектор /4/, 1 элемент И /5/, 1 регистр /6/, 1 дешифратор /7/, K релейных элементов /8...K), 1 вторую группу релейных элементов (9...N - K), 1 третью группу релейных элементов (10...N N), 1 входную шину /11/, 1 выходную шину 12, 1 шину данных /13/, 1 шину адресов /14/, 1 четвертую группу релейных элементов (16...N). Введением четвертой группы N релейных элементов и ряда новых связей обусловлено повышение надежности работы многоканального коммутатора. 1 з.п. ф-лы, 1 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР N 1834615 кл.H 03K 17/00. | |||

Авторы

Даты

1995-01-09—Публикация

1991-04-29—Подача