Изобретение относится к средствам автоматизации натурных исследований двумерных сигналов датчиков изображений, в частности радиолокационных отражений, и может быть использовано для регистрации, обработки и воспроизведения радиолокационных эхо-сигналов. Система ориентирована на совместную работу с импульсными некогерентными радиолокационными станциями (РЛС) высокого разрешения (с наносекундными зондирующими импульсами) и обеспечивает возможность получения в темпе эксперимента и представления в удобной форме информации о статистических характеристиках эхо-сигналов различного происхождения. Съем данных радиолокационных измерений производится в стробе в режиме кругового обзора и в режиме остановленной антенны РЛС. Кроме того, система обеспечивает возможность записи радиолокационных изображений в заданной области обзора и последующее отображение на штатных индикаторах РЛС натурных радиолокационных изображений и изображений, сформированных пользователем.

Известны устройства для записи-воспроизведения радиолокационной информации [1, 2] . Однако они имеют низкое разрешение и не обеспечивают возможности реализации современных методов цифровой обработки и хранения видеосигналов с последующим их воспроизведением на аналоговых видеоиндикаторах информации.

Техническим решением, наиболее близким к заявляемому, является цифроаналоговая система для регистрации и статистической обработки информации [3] . Система содержит аналоговый процессор, аналого-цифровой преобразователь (АЦП), блок памяти тарировочных характеристик, блок программной перестройки структуры, блок памяти алгоритмов, блок памяти управляющей информации, микроЭВМ (оперативное запоминающее устройство, арифметико-логическое устройство и блок управления), таймер и блок вывода. Блоки программной перестройки структуры и памяти алгоритмов производят перестройку конфигурации системы программным путем применительно к алгоритмам и типам выполняемых задач. В зависимости от заданного режима работы информация, принимаемая с объекта исследования, может непосредственно либо после предварительной обработки в аналоговом процессоре и дискретизации в АЦП поступать на блок вывода для регистрации и последующего анализа, использоваться в системе для экспресс-анализа.

Известная система не обеспечивает высокого разрешения при сравнительно низком быстродействии канала микроЭВМ, т.е. ее недостатком является невысокий допустимый темп преобразования и регистрации информации, зависимый от временных характеристик микроЭВМ, а также невозможность регистрации двумерного сигнала. В частности, система не позволяет осуществлять согласованное с разрешающей способностью РЛС преобразование радиолокационных эхо-сигналов, их регистрацию и накопление и тем самым не обеспечивает возможности восстановления сигнала с точностью, достаточной для его описания. Кроме того, цифроаналоговая система регистрации и статистической обработки информации не позволяет воспроизводить накопленные данные радиолокационных изображений на штатных средствах отображения информации в РЛС.

Цель изобретения - расширение области применения за счет возможности регистрации и отображения двумерных сигналов с высоким темпом преобразования.

Цель достигается тем, что в цифроаналоговой системе для регистрации и обработки информации, содержащей блок программной перестройки структуры, блок вывода, выход которого является выходом системы и микроЭВМ, блок программной перестройки структуры содержит мультиплексор и демультиплексор, первый выход которого является первым выходом блока программной перестройки структуры, первый и второй информационные входы которого подключены соответственно к первому и второму информационным входам мультиплексора, выход которого является вторым выходом блока программной перестройки структуры, третий выход которого подключен к второму выходу демультиплексора, информационный вход которого является третьим информационным входом блока программной перестройки структуры, управляющий вход которого подключен к управляющим входам мультиплексора и демультиплексора, а в систему введены кодер видеосигнала, блок прямого доступа к памяти, блок программного обмена, формирователь строба, блок адреса и синхронизации, сверхоперативное запоминающее устройство и генератор тактовых импульсов, причем выход кодера видеосигнала подключен к первому информационному входу блока программной перестройки структуры, к второму информационному входу которого подключен информационный выход блока прямого доступа к памяти, первый выход блока программной перестройки структуры подключен к первому информационному входу блока прямого доступа к памяти, к второму информационному входу которого подключен первый информационный выход микроЭВМ, первый управляющий выход которой подключен к первому управляющему входу блока прямого доступа к памяти, второй информационный и второй управляющий выходы микроЭВМ подключены к соответствующим входам блока программного обмена, информационный выход и выход селектора адреса которого подключены к соответствующим входам формирователя строба и блока адреса и синхронизации, управляющий выход блока программного обмена подключен к первому управляющему входу блока адреса и синхронизации, а также к управляющим входам блока программной перестройки структуры и формирователя строба, первый управляющий выход которого подключен к второму управляющему входу блока прямого доступа к памяти, первый и второй управляющие выходы которого подключены соответственно к второму и третьему управляющим входам блока адреса и синхронизации, управляющий выход которого подключен к третьему управляющему входу блока прямого доступа к памяти, прямой тактирующий выход блока адреса и синхронизации подключен к одноименному входу кодера видеосигнала, стробирующий выход которого подключен к одноименному входу сверхоперативного запоминающего устройства, информационный вход которого подключен к второму выходу блока программной перестройки структуры, третий информационный вход которого подключен к выходу сверхоперативного запоминающего устройства, управляющий вход которого подключен к третьему управляющему выходу блока прямого доступа к памяти, адресный вход сверхоперативного запоминающего устройства подключен к адресному выходу блока адреса и синхронизации, синхровход которого подключен к выходу генератора тактовых импульсов, управляющий вход которого подключен к второму управляющему выходу формирователя строба, третий выход блока программной перестройки структуры подключен к информационному входу блока вывода, тактовый вход которого подключен к инверсному тактирующему выходу блока адреса и синхронизации, информационным входом системы является аналоговый вход кодера видеосигнала, а входные сигналы "Курс" и "Запуск" системы подключены к соответствующим входам блока программного обмена, формирователя строба и блока адреса и синхронизации. Кодер видеосигнала содержит АЦП, регистр, элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент задержки, причем аналоговый вход кодера видеосигнала подключен к информационному входу АЦП, разрядные выходы которого подключены соответственно к n разрядам информационного входа регистра, тактовый вход которого подключен к тактовому входу АЦП и является тактовым входом кодера видеосигнала, n-разрядный выход регистра подключен к выходу кодера видеосигнала, стробирующий выход которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого подключен к (n+1)-у разрядному выходу регистра и к входу элемента НЕ, выход которого подключен к (n+1)-у разряду информационного входа регистра и к входу элемента задержки, выход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Формирователь строба содержит первый и второй счетчики, триггер, первый, второй и третий элементы И и элемент ИЛИ, причем информационный вход формирователя строба подключен к информационным входам первого и второго счетчиков, вычитающие входы которых подключены к входу "Запуск" формирователя строба, вход "Курс" которого подключен к входам установки в ноль первого и второго счетчиков и триггера, выход которого подключен к первому входу третьего элемента И и является первым управляющим выходом формирователя строба, второй управляющий выход которого подключен к выходу третьего элемента И, второй вход которого подключен к входу "Запуск" формирователя строба, управляющий вход которого подключен к первым входам первого и второго элементов И, вторые входы которых подключены к входу селектора адреса формирователя строба, выходы первого и второго элементов И подключены соответственно к тактовым входам первого и второго счетчиков, выходы переноса которых подключены к первому и второму входам элемента ИЛИ, выход которого подключен к входу установки в единицу триггера. Блок адреса и синхронизации содержит первый, второй и третий регистры, первый, второй и третий счетчики, триггер, элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ и элемент И-НЕ, причем информационный вход блока адреса и синхронизации подключен к информационным входам первого, второго и третьего регистров, тактовые входы которых подключены к первому управляющему входу блока адреса и синхронизации, вход селектора адреса которого подключен к входам разрешения записи первого, второго и третьего регистров, выходы первого и третьего регистров подключены соответственно к информационным входам первого и второго счетчиков, входы вычитания которых подключены к тактовому входу блока адреса и синхронизации, вход "Запуск" которого подключен к тактовому входу второго счетчика и к входам установки в ноль третьего счетчика и триггера, выход которого подключен к входу установки в ноль первого счетчика, прямой выход переноса которого подключен к собственному тактовому входу,входу сложения третьего счетчика и является прямым тактирующим выходом блока адреса и синхронизации, инверсный тактирующий выход которого подключен к инверсному выходу переноса первого счетчика, второй управляющий вход блока адреса и синхронизации подключен к вычитающему входу третьего счетчика, прямой выход которого является адресным выходом блока адреса и синхронизации и подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу второго регистра, а выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к первому входу элемента ИЛИ и к первому входу элемента И-НЕ, выход которого является управляющим выходом блока адреса и синхронизации, третий управляющий вход которого подключен к входу элемента НЕ, выход которого подключен к второму входу элемента И-НЕ, выход переноса второго счетчика подключен к второму входу элемента ИЛИ, выход которого подключен к входу установки в единицу триггера.

Совокупность отличительных признаков заявляемой системы, а именно наличие взаимосвязанных кодера видеосигнала и сверхоперативного запоминающего устройства, информационными входами и выходами подключенного к микроЭВМ посредством блоков программной перестройки структуры и прямого доступа к памяти, блока программного обмена, связывающего с микроЭВМ формирователь строба и блок адреса и синхронизации, к которым подключены сигналы "Курс" и "Запуск", с одной стороны, в известных ранее устройствах не обнаружена, а с другой стороны, придает заявляемой системе новое качество - возможность регистрации и отображения двумерных сигналов с высоким темпом преобразования в интересующей пользователя области пространства (зоны обзора РЛС), воспроизведения накопленных радиолокационных изображений на штатных средствах отображения информации в РЛС. Этим достигается поставленная цель. Причем сама процедура обработки реализована схемно на простейших узлах цифровой вычислительной техники. Это позволяет заключить, что предложенное техническое решение удовлетворяет критериям существенных отличий.

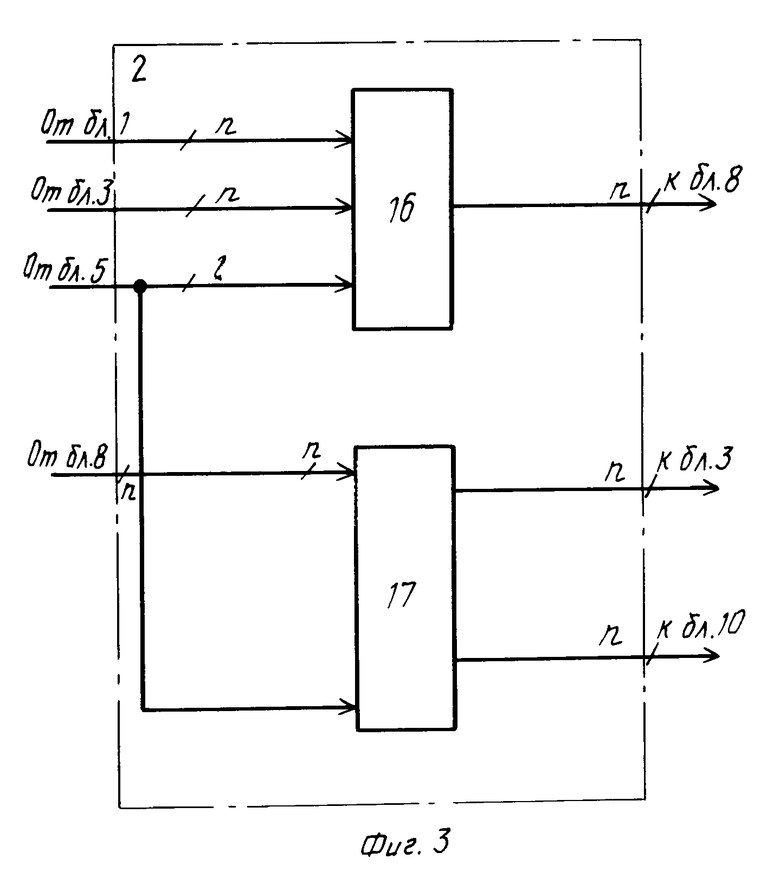

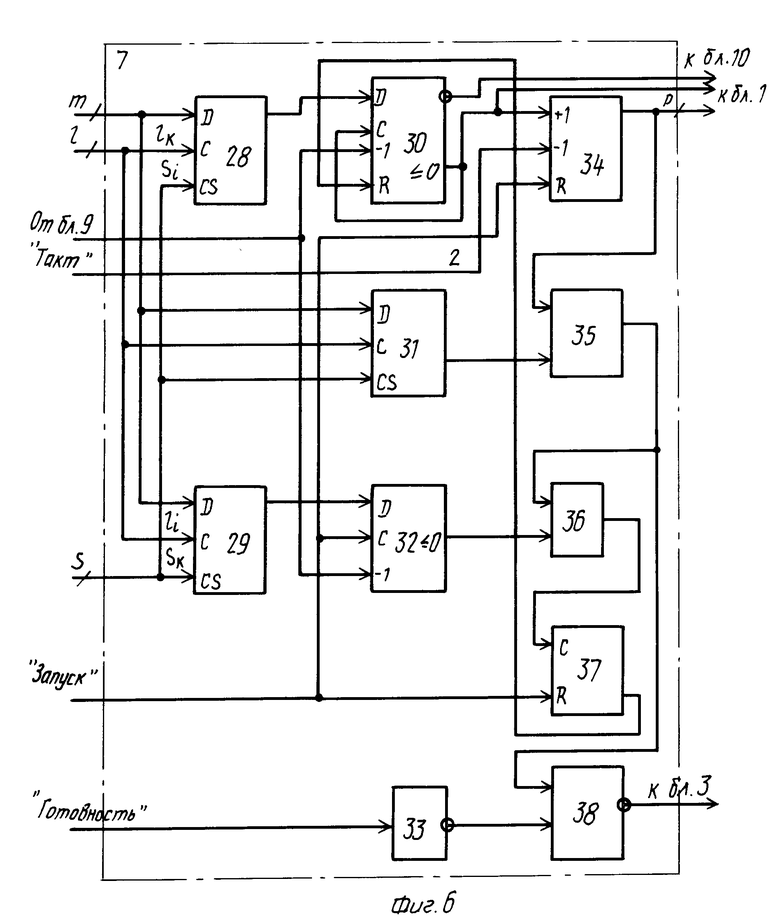

На фиг. 1 представлена блок-схема цифроаналоговой системы для регистрации и обработки информации; на фиг. 2 - схема кодера видеосигнала; на фиг. 3 - схема блока программной перестройки структуры; на фиг. 4 - схема блока программного обмена; на фиг. 5 - схема формирователя строба; на фиг. 6 - схема блока адреса и синхронизации; на фиг. 7 - схема генератора тактовых импульсов.

Система для регистрации и обработки информации содержит кодер 1 видеосигнала, блок 2 программной перестройки структуры, блок 3 прямого доступа к памяти, микроЭВМ 4, блок 5 программного обмена, формирователь 6 строба, блок 7 адреса и синхронизации, сверхоперативное запоминающее устройство 8, генератор 9 тактовых импульсов, блок 10 вывода. Причем n-разрядный выход кодера 1 видеосигнала подключен к первому информационному входу блока 2 программной перестройки структуры, к второму информационному входу которого подключен n-разрядный информационный выход блока 3 прямого доступа к памяти. Первый n-разрядный выход блока 2 программной перестройки структуры подключен к первому информационному входу блока 3 прямого доступа к памяти, к второму информационному входу которого подключен n-разрядный первый информационный выход микроЭВМ 4. К первому управляющему входу блока 3 прямого доступа к памяти подключен k-разрядный первый управляющий выход микроЭВМ 4, m-разрядный второй информационный и l-разрядный второй управляющий выходы которой подключены к соответствующим входам блока 5 программного обмена. m-Разрядный информационный выход и s-разрядный выход селектора адреса блока 5 программного обмена подключены к соответствующим входам формирователя 6 строба и блока 7 адреса и синхронизации, l-разрядный управляющий выход блока 5 программного обмена подключен к первому управляющему входу блока 7 адреса и синхронизации, а также к управляющим входам блока 2 программной перестройки структуры и формирователя 6 строба. Первый управляющий выход формирователя 6 строба подключен к второму управляющему входу блока 3 прямого доступа к памяти, к второму и третьему управляющим входам блока 7 адреса и синхронизации подключены соответственно первый и второй управляющие выходы блока 3 прямого доступа к памяти. Управляющий выход блока 7 адреса и синхронизации подключен к третьему управляющему входу блока 3 прямого доступа к памяти, прямой тактирующий выход блока 7 адреса и синхронизации подключен к одноименному входу кодера 1 видеосигнала. Информационный вход сверхоперативного запоминающего устройства 8 подключен к второму n-разрядному выходу блока 2 программной перестройки структуры, а n-разрядный информационный выход - к третьему информационному входу блока 2 программной перестройки структуры. Управляющий вход сверхоперативного запоминающего устройства 8 подключен к третьему управляющему выходу блока 3 прямого доступа к памяти, адресный вход - к р-разрядному адресному выходу блока 7 адреса и синхронизации, стробирующий вход - к одноименному выходу кодера 1 видеосигнала. Выход генератора 9 тактовых импульсов подключен к синхронизирующему входу блока 7 адреса и синхронизации, управляющий вход - к одноименному второму выходу формирователя 6 строба. Информационный вход блока 10 вывода подключен к одноименному инверсному выходу блока 7 адреса и синхронизации. Информационным входом системы является аналоговый вход кодера 1 видеосигнала, синхронизирующие входные сигналы "Курс" и "Запуск" системы, вырабатываемые РЛС, подключены к соответствующим входам блока 5 программного обмена, формирователя 6 строба и блока 7 адреса и синхронизации, выходом системы и микроЭВМ 4 является аналоговый выход блока 10.

Кодер 1 видеосигнала (фиг. 2) содержит АЦП 11, буферный регистр 12, элемент НЕ 13, элемент 14 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15. Аналоговый вход кодера 1 видеосигнала подключен к информационному входу АЦП 11, n-разрядные выходы которого подключены соответственно к n разрядам информационного входа регистра 12, тактовый вход которого подключен к тактовому входу АЦП 11 и является тактовым входом кодера 1 видеосигнала. n Разрядов выхода регистра 12 подключены к выходу кодера 1 видеосигнала, стробирующий выход которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, первый вход которого подключен к (n+1)-у разрядному выходу регистра 12 и к входу элемента НЕ 13. Выход последнего подключен к (n+1)-у разряду информационного входа регистра 12 и к входу элемента 14 задержки, выход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15.

Блок 2 программной перестройки структуры (фиг. 3) содержит мультиплексор 16 и демультиплексор 17, первый n-разрядный выход которого является первым выходом блока 2. Первый и второй n-разрядные информационные входы блока 2 подключены соответственно к первому и второму информационным входам мультиплексора 16, n-разрядный выход которого является вторым выходом блока 2. Третий выход блока 2 подключен к второму выходу демультиплексора 17, информационный вход которого является третьим информационным входом блока 2, управляющий вход которого подключен к управляющим входам мультиплексора 16 и демультиплексора 17.

Блок 5 программного обмена (фиг. 4) содержит устройство 18 параллельного обмена, регистр 19, дешифратор 20 адреса.

Формирователь 6 строба (фиг. 5) содержит счетчики 21 и 22, элементы И 23 и 24, элемент ИЛИ 25, Т-триггер 26, элемент И 27.

Причем m-разрядный информационный вход формирователя 6 строба подключен к информационным входам счетчиков 21 и 22, вычитающие входы которых подключены к входу "Запуск" формирователя 6 строба. Вход "Курс" формирователя 6 подключен к входам установки в ноль счетчиков 21, 22 и Т-триггера 26, выход которого подключен к первому входу элемента И 27 и является первым управляющим выходом формирователя 6 строба. Второй управляющий выход формирователя 6 подключен к выходу элемента И 27, второй вход которого подключен к входу "Запуск" формирователя 6 строба. l-Разрядный управляющий вход формирователя 6 подключен к первым входам элементов И 23 и 24, вторые входы которых подключены к s-разрядному входу селектора адреса формирователя 6 строба. Выходы элементов И 23 и 24 подключены к тактовым входам счетчиков 22 и 21 соответственно, выходы переноса которых подключены к первому и второму входам элемента ИЛИ 25, выход которого подключен к входу установки в единицу Т-триггера 26.

Блок 7 адреса и синхронизации (фиг. 6) содержит регистры 28 и 29, счетчик 30, регистр 31, счетчик 32, элемент НЕ 33, счетчик 34, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 35, элемент ИЛИ 36, Т-триггер 37, элемент И-НЕ 38. Причем m-разрядный информационный вход блока 7 подключен к информационным входам регистров 28, 29 и 31, тактовые входы которых подключены к первому управляющему l-разрядному входу блока 7. s-Разрядный вход селектора адреса блока 7 подключен к входам разрешения записи регистров 28, 29 и 31, выходы регистров 28 и 29 подключены к информационным входам счетчиков 30 и 32, входы вычитания которых подключены к тактовому входу блока 7. Вход "Запуск" блока 7 подключен к тактовому входу счетчика 32 и к входам установки в ноль счетчика 34 и Т-триггера 37, выход которого подключен к входу установки в ноль счетчика 30. Прямой выход переноса счетчика 30 подключен к собственному тактовому входу, входу сложения счетчика 34 и, кроме того, является прямым тактирующим выходом блока 7, инверсный тактирующий выход которого подключен к инверсному выходу переноса счетчика 30. Второй управляющий вход "Такт" блока 7 подключен к вычитающему входу счетчика 34, р-разрядный прямой выход которого является адресным выходом блока 7 и, кроме того, подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 35, второй вход которого подключен к выходу регистра 31, а выход - к первому входу элемента ИЛИ 36 и к первому входу элемента И-НЕ 38. Выход последнего является управляющим выходом блока 7, третий управляющий вход "Готовность" которого подключен к входу элемента НЕ 33, выход которого соединен с вторым входом элемента И-НЕ 38. Выход переноса счетчика 32 подключен к второму входу элемента ИЛИ 36, выход которого подключен к входу установки в единицу Т-триггера 37.

Генератор 9 тактовых импульсов (фиг. 7) содержит резистор 39, кварцевый резонатор 40, элемент НЕ 41, элемент И-НЕ 42, элемент НЕ 43.

В кодере 1 видеосигнала АЦП 11 может быть выполнен на основе БИС сверхбыстродействующего АЦП типа К 1107ПВ2 или К 1107ПВ5. Элемент 14 задержки может быть выполнена в виде четного числа элементов НЕ. Блок 3 прямого доступа к памяти и устройство 18 параллельного обмена являются стандартными узлами ЭВМ и представляют собой контроллер прямого доступа к оперативной памяти и интерфейс параллельного обмена соответственно. К примеру, в случае использования в качестве микроЭВМ 4 микроЭВМ ряда "Электроника 60" блок 3 может быть представлен устройством прямого доступа к памяти И3 15КС-14-002 (Устройство прямого доступа к памяти И3 ТО и ТЭ И9М3.858.385 ТО), а устройство 18 параллельного обмена блока 5 в этом случае представлено интерфейсом пользователя И5 15КС-16-037 (Интерфейс пользователя И5 15КС-16-037ТО и ИЭ М3.858.396 ТО). Сверхоперативное запоминающее устройство 8 может быть выполнено на БИС статистического быстродействующего ЗУ, к примеру, серии 132. Блок 10 вывода представлен декодером видеосигнала, который может быть выполнен, к примеру, на БИС сверхбыстродействующего ЦАП типа К1118ПА2.

Работа системы. Высокий темп поступления и большой объем радиолокационной информации исключают возможность непосредственного ввода данных в ЭВМ. Необходимы специальные технические решения для обеспечения согласованного с разрешающей способностью РЛС преобразования сигналов и съема данных в интересующей области зоны обзора РЛС - стробе.

В цифроаналоговой системе для регистрации и обработки информации настройка параметров принимаемой с РЛС информации осуществляется путем программирования частоты дискретизации Fд видеосигнала, границ строба по дальности и пеленгу. Специальный алгоритм обмена видеоинформации, позволивший выполнить буферизацию данных на основе сверхоперативного запоминающего устройства (СОЗУ) сравнительно небольшой емкости, основан на структурных свойствах радиолокационного эхо-сигнала: видеоинформация записывается в СОЗУ или читается из него на интервале времени развертки сигнала Тр, существенно меньшем периода Тзи посылки двух зондирующих импульсов, оставшаяся часть времени (Тзи - Тр) используется для обмена с ОЗУ микроЭВМ. Таким образом, необходимая память буферного СОЗУ определяется накапливаемым объемом данных в пределах одной зондирующей посылки.

В систему кроме специальных аппаратных средств и их программных драйверов входят программы диалогового задания режимов функционирования системы на профессионально-естественном языке. Так, в соответствии с данными диалога о протяженности строба по пространству и частоте дискретизации Fд формируется начальный адрес СОЗУ. С учетом этих данных и данных о размерности строба по азимуту настраивается канал прямого доступа к памяти микроЭВМ. Кроме того, значения границ строба по дальности и в азимутальном направлении используются для настройки элементов системы, формирующих пространственно-временные координаты съема данных. В диалоге пользователь также определяет режим работы системы: запись данных радиолокационных измерений, отображение радиолокационной информации на индикаторе кругового обзора РЛС или контроль технических средств системы. При этом выполняется программное изменение конфигурации системы. При отображении на индикаторе кругового обзора РЛС информации, содержащейся в эхо-сигнале, записанном ранее системой на протяжении ряда обзоров, данные о параметрах строба и его местоположении в зоне обзора РЛС считываются из паспорта на кадр информации с внешнего носителя.

Задание режима функционирования системы, т.е. настройка ее специальных аппаратных средств путем занесения соответствующих уставок в регистры, производится посредством программных операций с использованием канала программного обмена. Обращение к регистрам в процессе функционирования системы осуществляется в ответ на требование прерывания (ТП) программы, которое инициируется РЛС при прохождении антенной нулевого отсчета направлений. Программа обслуживания прерывания выполняется во время действия импульса отметки нулевого положения антенны. Таким образом, для каждого нового оборота антенны параметры строба и режим съема данных могут быть перепрограммированы путем изменения уставок для соответствующих регистров.

Обмен видеоданными производится по каналу прямого доступа к памяти ЭВМ.

Функционирование. Перед началом работы в микроЭВМ 4 вводится программа, обеспечивающая пользователю возможность задания пространственно-временных параметров съема и отображения данных, их накопление и экспресс-анализ. Синхронизация работы системы в РЛС осуществляется посредством импульсов "Запуск" и "Курс", вырабатываемых РЛС в момент формирования зондирующих импульсов и при прохождении антенной нулевого отсчета направлений соответственно.

При поступлении сигнала "Курс" в блок 5 программного обмена последний вырабатывает запрос "Требование передачи" (ТП ЭВМ), который транслируется в микроЭВМ 4 по двунаправленной l-разрядной управляющей шине. Реагируя на запрос, микроЭВМ 4 через блок 5 программного обмена задает в виде уставок режим и параметры работы системы: в формирователь 6 строба записывается код пеленга начала строба Пн и код пеленга конца строба Пк (счетчики 21 и 22 соответственно); в блок 7 адреса и синхронизации задаются частота дискретизации Fд видеосигнала по пространственной координате (регистр 28, счетчик 30), дальность начала строба (регистр 29 и счетчик 32) и количество отсчетов в стробе, записываемых в сверхоперативное запоминающее устройство 8 (регистр 31); в блок 2 программной перестройки структуры поступает управляющий сигнал, который определяет направление потока информации - от кодера 1 видеосигнала к сверхоперативному запоминающему устройству 8 и от сверхоперативного запоминающего устройства 8 к блоку 3 прямого доступа к памяти в режиме съема данных радиолокационных измерений или от блока 3 прямого доступа к памяти к сверхоперативному запоминающему устройству 8 и от сверхоперативного запоминающего устройства 8 к блоку 10 вывода в режиме отображения данных радиолокационных измерений.

Программируется также блок 3 прямого доступа к памяти, осуществляющий процесс чтения-записи в сверхоперативное запоминающее устройство 8. Этот блок, в том числе, формирует сигналы "Готовность" и "Такт", которые поступают в блок 7 адреса и синхронизации и определяют цикл обмена данными между сверхоперативным запоминающим устройством 8 и микроЭВМ 4.

Кроме того, во время действия импульса "Курс" осуществляется предустановка формирователя 6 строба: устанавливаются в исходное состояние счетчики 21 и 22 и триггер 26.

В процессе функционирования системы импульсы "Запуск" поступают в формирователь 6 строба на вычитающие входы счетчиков 21 и 22. В моменты времени, когда текущий пеленг равен коду пеленга начала строба и конца строба, содержимое счетчиков 21 и 22 равно нулю. В результате на выходе триггера 26 сформирован сигнал, активный до тех пор, пока выполняется условие - Пн < Пт < Пк, где Пт - текущий пеленг. Этим сигналом разрешается работа генератора 9, сигнал с выхода которого поступает на вычитающий вход счетчика 32, блока 7 адреса и синхронизации, где записано число отсчетов по пространственной координате, соответствующее начальной дальности строба. В момент, когда текущий номер отсчета сравняется с заданным, триггер 37 блока 7 разблокирует счетчик 30, который делит задающую частоту сигнала, поступающего с генератора 9, на значение, занесенное в регистр 28. Этим достигается получение требуемого значения частоты дискретизации видеосигнала по пространственной координате. На выходе счетчика 34 формируется текущий адрес ячейки сверхоперативного запоминающего устройства 8, причем, так как счетчик 34 всякий раз начинает считать с нуля, текущее значение адреса ячейки соответствует текущему значению количества отсчетов. Когда текущее число отсчетов станет равным заданному, записанному в регистре 31, триггер 37 блокирует счетчик 30, а на выходе элемента И 38 формируется управляющий сигнал, поступающий в блок 3 прямого доступа к памяти и означающий окончание процесса обращения к сверхоперативному запоминающему устройству 8. Блок 3 прямого доступа выдает запрос в микроЭВМ 4 в виде требования канала прямого доступа к памяти и при условии разрешения начинает цикл передачи данных.

Режим отображения информации аналогичен режиму записи. Так, при выводе информации из микроЭВМ 4, предварительно считанной с внешнего носителя, формирователь 6 строба вырабатывает управляющий сигнал, поступающий в блок 3 прямого доступа к памяти и инициирующий передачу данных от ЭВМ 4 к сверхоперативному запоминающему устройству 8. Этот сигнал вырабатывается в момент, когда номер текущего пеленга равен пеленгу начала строба. Блок 3 прямого доступа к памяти, реагируя на управляющий сигнал, обеспечивает запись информации в сверхоперативное запоминающее устройство 8 в течение периода между посылками. Вывод записанной информации на индикатор кругового обзора РЛС производится на следующей посылке. По окончании вывода блок 7 адреса и синхронизации вырабатывает сигнал, инициирующий передачу очередного пакета информации, и цикл повторяется. Таким образом, информация, выводимая на индикатор, смещена относительно записанной на одну посылку.

Структура рассмотренной системы по сравнению с известными системами и устройствами такого же рода дает следующие преимущества: возможность регистрировать и воспроизводить двумерные сигналы с высоким темпом преобразования (в реальном масштабе времени развертки видеосигнала); возможность выделения области пространства, в которой требуется регистрировать или выводить информацию; возможность определять пространственно-временные параметры выделенной области пространства на каждый оборот антенны РЛС, что дает возможность задавать траекторию перемещения строба в зоне обзора и тем самым отслеживать, например, движение цели.

Специальное прикладное программное обеспечение системы ориентировано на оперативную оценку по выборкам сравнительно небольшого объема основных статистических характеристик и осуществляет также функции обработки: отображение в любом из направлений двумерного массива данных одномерных реализаций процесса с требуемой степенью детализации, например реализаций процесса по пространственной и временной координатам; построение гистограммы распределения амплитуд эхо-сигнала и аппроксимацию эмпирического распределения, оценку параметров аппроксимирующего распределения; построение корреляционной функции и энергетического спектра; построение и анализ бинарных радиолокационных портретов отражений от различного рода объектов наблюдения.

Все эти факторы предопределяют преимущественную область применения системы-проведение натурных экспериментальных исследований отражений от морских и воздушных радиолокационных целей, радиолокационных отражений от элементов системы океан - атмосфера: от взволнованной морской поверхности, неоднородностей приводного слоя, тропосферы, биологических и других объектов. Результаты исследований могут быть использованы в задачах проектирования и испытаний систем обработки радиолокационных изображений, в частности навигационных систем и др.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭВМ | 1990 |

|

RU2024928C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042188C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046396C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ТРЕХМЕРНЫХ ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ | 1991 |

|

RU2051411C1 |

Изобретение относится к средствам автоматизации натурных исследований двумерных сигналов датчиков изображений и может быть использовано для регистрации, обработки и воспроизведения радиолокационных эхо-сигналов. Цель изобретения - расширение области применения за счет возможности регистрации и отображения двумерных сигналов с высоким темпом преобразования. Цифроаналоговая система для регистрации и обработки информации содержит кодер 1 видеосигнала, блок 2 программной перестройки структуры, блок 3 прямого доступа к памяти, микроЭВМ 4, блок 5 программного обмена, формирователь 6 строба, блок 7 адреса и синхронизации, сверхоперативное запоминающее устройство 8, генератор 9 тактовых импульсов и блок 10 вывода, соединенные между собой функционально. 3 з.п.ф-лы, 7 ил.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифро-аналоговая система для регистрации и статистической обработки информации | 1979 |

|

SU858023A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-10-30—Публикация

1991-01-21—Подача