Изобретение относится к вычислительной технике и может быть использовано при разработке персональных бытовых ЭВМ, игровых автоматов и других средств вычислительной техники, построенных на основе микропроцессоров и осуществляющих индикацию информации на телевизионном мониторе или приемнике.

Известны два основных способа представления в памяти ЭВМ изображений, выводимых на электронно-лучевую трубку: символьный и графический. В первом случае в видеопамяти хранятся коды отображаемых символов или элементов графики в последовательности, определяемой текстом. При стандартном формате экрана (25 строк по 80 символов) объем видеопамяти составляет 2000 байт. При отображении информации коды символов преобразуются в их изображения с помощью знакогенератора. Во втором случае в видеопамяти хранятся все элементы (точки, пикселы), составляющие изображение. При этом изображение может иметь произвольный вид (единственное ограничение - разрешающая способность), но объем видеопамяти резко увеличивается. В частности, для получения того же формата экрана, что и в рассмотренном случае, объем видеопамяти должен составлять не менее 12000 байт (при отображении символа матрицей 6х8 точек).

Известен ряд ПЭВМ, для которых характерно высокое качество изображений, выводимых не видеомонитор, и большая гибкость преобразования этих изображений. В то же время обладают следующими недостатками: большим объемом видеопамяти и высокими требованиями к быстродействию микропроцессора, формирующего изображения в памяти. По этим причинам в большинстве таких ЭВМ видеопамять вынесена из основной памяти (это позволяет видеоконтроллеру функционировать параллельно основному процессору, благодаря чему повышается производительность последнего) и либо используется мощный микропроцессор (как правило 16-разрядный), обладающий командами, обрабатывающими строки данных, либо видеоконтроллер, обладающий способностью автономно осуществлять достаточно простое преобразование информации (например, сдвиг) в видеопамяти.

Недостатком микроЭВМ-прототипа является отсутствие возможности плавного перемещения изображения на экране видеомонитора. Действительно, изображение на экране зависит только от того, какие коды записаны в видеопамяти. Для перемещения изображения, например, вверх на строку следует сдвинуть информацию в видеопамяти вперед на число символов, отображаемых в строке текста на экране. Однако, очевидно, что изображение при этом изменится скачком, сразу сместившись на целую строку символов. Никаких промежуточных стадий не будет.

Целью настоящего изобретения является расширение функциональных возможностей микроЭВМ с символьным способом представления информации в видеопамяти за счет устранения указанного недостатка.

Существенным отличием предлагаемой микроЭВМ, содержащей микропроцессор, контроллер прямого доступа к памяти, контроллер видеотерминала, узел ввода-вывода, блок оперативной памяти, блок постоянной памяти, дешифратор, генератор синхросигналов, запоминающий узел знакогенератора, формирователь видеосигнала, элемент ИЛИ, причем адресные выходы микропроцессора соединены с адресными входами блоков оперативной и постоянной памяти, с информационными входами дешифратора и с адресными входами-выходами контроллера прямого доступа к памяти "группа младших выходов адреса микропроцессора связана с адресными входами контроллера видеотерминала, информационные входы-выходы микропроцессора соединены с информационными входами-выходами контроллеров видеотерминала, прямого доступа к памяти и узла ввода-вывода, с информационными входами блока оперативной памяти и информационными выходами блоков оперативной и постоянной памяти, управляющий выход чтения памяти микропроцессора соединен с одноименным выходом контроллера прямого доступа к памяти и со входом контроллера прямого доступа к памяти и со входом чтения блока постоянной памяти. Управляющий выход записи в память микропроцессора соединен с одноименным выходом контроллера прямого доступа к памяти и с входом записи блока оперативной памяти, управляющие выходы чтения и записи устройств ввода-вывода микропроцессора соединены соответственно с одноименными входами-выходами контроллера прямого доступа к памяти, а также входами узла ввода-вывода и контроллера видеотерминала, выход подтверждения прямого доступа микропроцессора связан с одноименным входом контроллера прямого доступа к памяти, выход запроса прямого доступа которого подключен к одноименному входу микропроцессора, входы начальной установки микропроцессора и контроллера прямого доступа к памяти связаны между собой и подключены к входу начальной установки микроЭВМ, выход разрешения адреса контроллера прямого доступа к памяти соединен с управляющим входом дешифратора, первые четыре выхода которого подключены соответственно к входам обращения контроллеров прямого доступа к памяти и видеотерминала, блоков оперативной и постоянной памяти, а группа выходов связана с группой управляющих входов узла ввода-вывода, выход подтверждения прямого доступа к памяти контроллера прямого доступа к памяти соединен с одноименным входом контроллера видеотерминала, а выход запроса прямого доступа к памяти последнего связан с одноименным входом контроллера прямого доступа к памяти, один из выходов генератора синхросигналов подключен к тактовым входам микропроцессора и контроллера прямого доступа к памяти, второй выход генератора связан с тактовым входом формирователя видеосигнала, выход синхронизации которого соединен со входом символьной синхронизации контроллера видеотерминала, выходы кода символа и номера строки растра контроллера подключены соответственно к группам старших и младших адресных входов запоминающего узла знакогенератора, выходы последнего связаны соответственно с информационными входами формирователя видеосигнала, выход видеосигнала которого подключен к одному из входов элемента ИЛИ, соединенного выходом с выходом видеосигнала микроЭВМ, выход горизонтальной синхронизации контроллера видеотерминала подключен ко второму входу элемента ИЛИ и выходу горизонтальной синхронизации видеотерминала микроЭВМ, является введение регистра, счетчика-регистра, логического узла и трех одновибраторов, причем информационные входы регистра связаны соответственно с упомянутыми информационными входами-выходами микропроцессора, вход записи регистра подключен к пятому выходу дешифратора, а выходы регистра соединены соответственно с информационными входами счетчика-регистра, вход занесения которого связан с выходом вертикальной синхронизации контроллера видеотерминала, выходы подключены к информационным входам логического узла, связанного тактовым входом с выходом горизонтальной синхронизации контроллера видеотерминала, первым выходом подключенного к счетному входу счетчика-регистра, а вторым выходом соединенного со входами первого и второго одновибраторов, выход первого одновибратора через третий одновибратор подключен к третьему входу элемента ИЛИ, а выход второго одновибратора связан с выходом вертикальной синхронизации видеотерминала микроЭВМ.

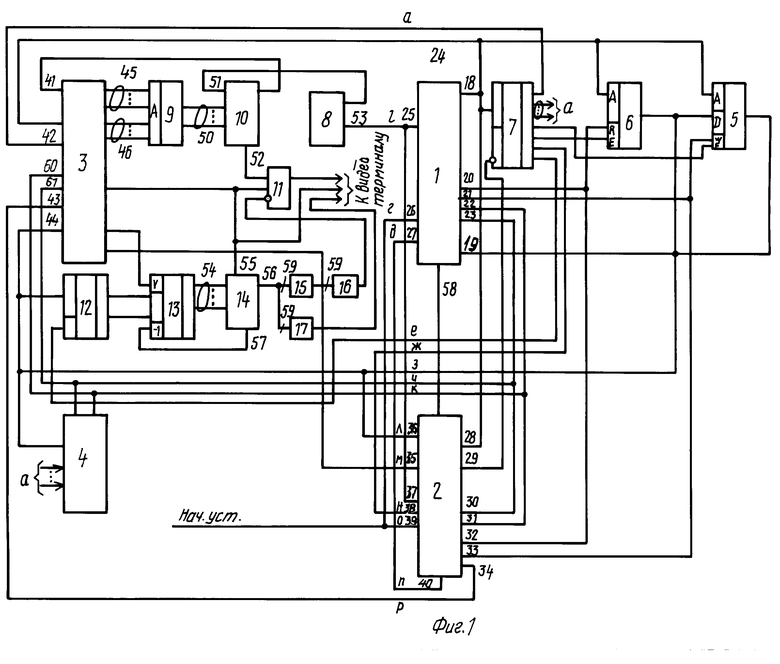

На фиг.1, 2 приведена схема предлагаемой микроЭВМ. Она содержит микропроцессор 1, контроллер 2 прямого доступа к памяти (ПДП), контроллер 3 видеотерминала (ВТ), узел 4 ввода-вывода, блок 5 оперативной памяти, блок 6 постоянной памяти, дешифратор 7, генератор 8 синхросигналов, запоминающий узел (ЗУ) 9 знакогенератора, формирователь 10 видеосигнала, элемент 11 ИЛИ, регистр 12, счетчик 13, логический узел 14, одновибраторы 15, 16, 17, 18 - адресные выходы, 19 - информационные входы-выходы, 20-23 - управляющие выходы чтения памяти, записи в память, чтения устройств ввода-вывода, записи устройств ввода-вывода, 24 - группа младших адресных выходов, 25-27 - входы синхронизации, начальной установки и запроса прямого доступа к памяти микропроцессора 1 соответственно, 28 - адресные входы-выходы, 29 - выход разрешения адреса, 30-33 - управляющие выходы записи в устройства ввода-вывода, чтения устройств ввода-вывода, чтения памяти, записи в память, 34, 35 - выход подтверждения и вход запроса прямого доступа к памяти, 36 - информационные входы-выходы, 37-39 - тактовый вход, входы обращения и начальной установки, 40 - выход запроса прямого доступа к памяти контроллера ПДП 2 соответственно, 41-43 - входы символьной синхронизации, обращения, подтверждения прямого доступа к памяти, 44 - информационные входы-выходы, 45, 46 - выходы кода символа и номера строки растра, 47-49 - выходы горизонтальной, вертикальной синхронизации и запроса прямого доступа к памяти контроллера ВТ 3 соответственно, 50, 51 - информационные и тактовый входы, 52 - выход видеосигнала формирователя 10 соответственно, 53 - один из выходов генератора синхросигналов, 54 - информационные входы, 55 - тактовый вход, 56, 57 - выходы логического узла 14, 58 - выход подтверждения прямого доступа к памяти микропроцессора 1, 59 - входы запуска одновибраторов, 60, 61 - входы чтения и записи устройств ввода-вывода контроллера 3 ВТ соответственно.

Адресные выходы 18 микропроцессора 1 соединены с адресными входами блоков оперативной 5 и постоянной 6 памяти, с информационными входами дешифратора 7 и с адресными входами-выходами 28 контроллера 2 ПДП. Группа 24 младших выходов адреса микропроцессора 1 соединена также с адресными входами контроллера 3 ВТ.

Информационные входы-выходы 19 микропроцессора 1 соединены с информационными входами-выходами 44 контроллера 3 ВТ, 36 контроллера 2 ПДП и узла ввода-вывода 4, с информационными входами блока 5 оперативной памяти, информационными выходами блоков 5 и 6 оперативной и постоянной памяти, а также информационными входами регистра 12.

Управляющий выход 20 чтения памяти микропроцессора 1 соединен с одноименным выходом 32 контроллера 2 ПДП и со входом чтения блока 6 постоянной памяти. Управляющий выход 21 записи в память микропроцессора 1 соединен с одноименным выходом 33 контроллера 2 ПДП и с входом записи блока 5 оперативной памяти.

Управляющие выходы 22 чтения устройств ввода-вывода 23 записи в устройства ввода-вывода микропроцессора 1 соединены соответственно с одноименными входами-выходами 31 и 30 контроллера 2 ПДП, а также входами узла ввода-вывода 4 и 60, 61 контроллера 3 ВТ.

Выход подтверждения прямого доступа 58 микропроцессора 1 связан с одноименным входом контроллера 2 ПДП, выход запроса прямого доступа 40 которого подключен к одноименному входу 27 микропроцессора 1. Входы 26 и 39 начальной установки микропроцессора 1 и контроллера 2 ПДП связаны между собой и подключены к входу начальной установки микроЭВМ.

Выход разрешения адреса 29 контроллера 2 ПДП соединен с управляющим входом дешифратора 7, первые пять выходов которого подключены соответственно ко входам обращения контроллеров 2 ПДП и 3 ВТ, блоков 5 оперативной и 6 постоянной памяти, а также входу занесения регистра 12, а оставшиеся выходы связаны с группой управляющих входов узла ввода-вывода. Выход 34 подтверждения прямого доступа к памяти контроллера 2 ПДП соединен с одноименным входом 43 контроллера 3 ВТ, а выход 49 запроса прямого доступа к памяти последнего связан с одноименным входом 35 контроллера 2 ПДП.

Один из выходов генератора синхросигналов 8 подключен к тактовым входам 25 микропроцессора 1 и 37 контроллера 2 ПДП. Второй выход генератора 8 связан с тактовым входом 51 формирователя видеосигнала 10, выход синхронизации которого соединен со входом 41 символьной синхронизации контроллера 3 ВТ, выходы кода символа 45 и номера строки растра 46 контроллера 3 подключены соответственно к группам старших и младших адресных входов запоминающего узла знакогенератора 9. Выходы последнего связаны соответственно с информационными входами 50 формирователя 10 видеосигнала. Выход видеосигнала 52 формирователя 10 подключен к одному из входов элемента ИЛИ 11, выход которого соединен с выходом видеосигнала микроЭВМ, выход горизонтальной синхронизации 47 контроллера 3 ВТ подключен ко второму входу элемента ИЛИ 11, тактовому входу 55 логического узла 14 и выходу горизонтальной синхронизации видеотерминала микроЭВМ. Выход 48 вертикальной синхронизации контроллера 3 ВТ связан со входом занесения счетчика-регистра 13, информационные входы которого соединены с выходами регистра 12, выходы подключены к информационным входам 54 логического узла 14, связанного выходом 57 со счетным входом счетчика-регистра 12, а выходом 56 соединенного со входами одновибраторов 15 и 17. Выход одновибратора 15 через одновибратор 16 подключен к третьему входу элемента ИЛИ 11, а выход одновибратора 17 связан с выходом вертикальной синхронизации видеотерминала микроЭВМ.

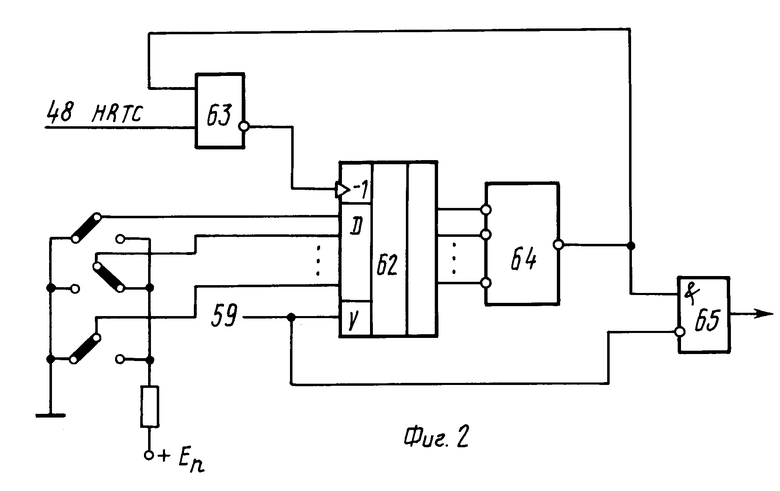

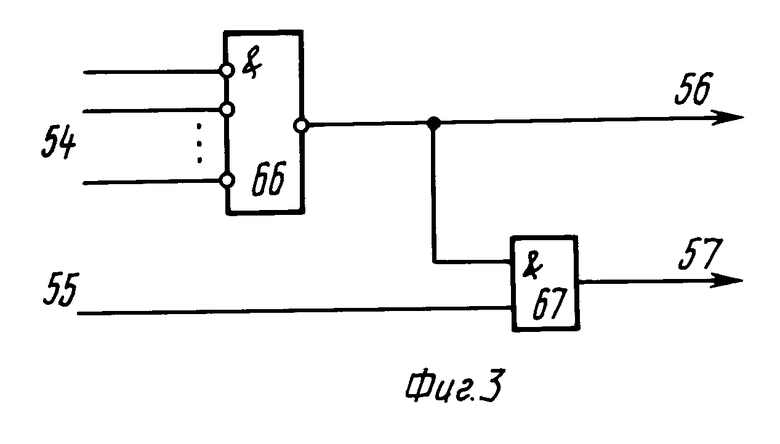

Каждый из одновибраторов включает счетчик, вход занесения которого подключен к управляющему входу одновибратора, а счетный вход соединен с выходом первого элемента И, один из входов которого соединен с выходом строчной синхронизации контроллера видеотерминала, а второй вход подключен к выходу второго элемента И, входы которого связаны с выходами счетчика, вход занесения которого связан с инверсным входом третьего элемента И, соединенного прямым входом с выходом второго элемента И, а выход подключен к выходу одновибратора, информационные входы счетчика подключены к шинам нулевого и единичного потенциалов в соответствии с кодом, заносимым в счетчик. Логический узел включает первый элемент И, входы которого подключены к информационным входам узла, а выход соединен со вторым выходом узла и одним из входов второго элемента И, второй вход которого связан с тактовым входом узла, а выход подключен к первому выходу узла.

На фиг.2 представлен вариант организации одновибраторов 15-17. Одновибратор включает счетчик 62, вход занесения которого подключен к управляющему входу 59 одновибратора, а счетный вход соединен с выходом элемента И63, один из входов которого соединен с выходом 48 строчной синхронизации контроллера ВТ, а второй вход подключен к выходу элемента И64, входы которого связаны с выходами счетчика. Вход занесения счетчика связан с инверсным входом элемента И65, прямой вход которого соединен с выходом элемента И64, а выход подключен к выходу одновибратора. Информационные входы счетчика 62 подключены к шинам нулевого и единичного потенциалов в соответствии с кодом, заносимым в счетчик.

На фиг.3 представлен вариант реализации логического узла 14. Узел включает элемент И66, входы которого подключены ко входам 54 узла, а выход соединен с выходом 56 узла и одним из входов элемента И67, второй вход которого связан со входом 55 узла, а выход подключен к выходу 57 узла.

Работает микроЭВМ следующим образом. Сигнал уровня лог. "1", поступающий на вход начальной установки ЭВМ после включения питающего напряжения, осуществляет начальную установку микропроцессора 1 и контроллера ПДП 2. После окончания действия этого сигнала контроллер ПДП оказывается в пассивном состоянии, а микропроцессор на своих адресных выходах 18 устанавливает стартовый адрес, сопровождаемый активным уровнем на его управляющем выходе чтения памяти 20.

Дешифратор 7 управляет обращениями к программно доступным узлам ЭВМ. Код адреса, поступающий на информационные входы дешифратора, при наличии разрешающего (нулевого уровня) на управляющем входе (связанном с выходом 29 контроллера ПДП) вызывает появление сигнала уровня логической единицы на соответствующем этому коду выходе дешифратора.

Стартовый адрес микропроцессора соответствует блоку постоянной памяти 6, из-за чего сигнал уровня лог."1" появляется на выходе, связанном со входом включения блока постоянной памяти, и микропроцессор начинает отработку программы монитора, содержащейся в блоке постоянной памяти.

В соответствии с этой программой микропроцессор программирует контроллеры ПДП и ВТ, устанавливая на своих адресных выходах последовательность адресов, соответствующих внутренним узлам контроллеров, на информационных входах-выходах - последовательность кодов данных, сопровождаемых сигналами записи в устройства ввода-вывода на выходе 23. Коды адресов внутренних блоков контроллеров вызывают активизацию выходов дешифратора 7, связанных со входами обращения контроллеров.

Для обращения к блоку оперативной памяти 5 микропроцессор 1 или контроллер ПДП 2 устанавливают на своих адресных выходах соответствующие коды адреса, а на управляющих выходах сигналы чтения или записи в память в зависимости от типа выполняемого обращения. Дешифратор 7 активизирует вход обращения блока 5, а логический уровень сигнала на его входе записи определяет режим работы блока. Аналогичным образом микропроцессор производит запись информации в регистр 12.

После программирования и инициализации контроллеров микропроцессор, в соответствии с программой монитора, переходит к циклическому опросу узла ввода-вывода 4 с целью получения команды с консоли. Обращения к узлу ввода-вывода производятся микропроцессором аналогично обращениям к контроллерам ПДП и ВТ, с той разницей, что при этом устанавливаются коды адреса, соответствующие активизации конкретных выходов группы выходов дешифратора 7. Последние вызывают обращения к тем или иным устройствам узла ввода-вывода 4, включая соответствующие группы вентилей.

Символы на экране видеомонитора формируются путем засветки отдельных точек телевизионного растра и располагаются в фиксированных позициях - знакоместах. Часть ячеек блока оперативной памяти 5 используется в качестве экранной области для хранения кодов отображаемых на экране символов. Каждому знакоместу на экране соответствует определенная ячейка экранной области, поэтому для вывода символа на определенном знакоместе микропроцессор должен записать его код в соответствующую ячейку этой области. Для того, чтобы изображение присутствовало на экране, контроллер ВТ должен циклически (синхронно с перемещением электронного луча по экрану ЭЛТ) с периодом, равным периоду кадровой синхронизации видеомонитора, получать из экранной области блока оперативной памяти 5 коды всех отображаемых на экране символов. Это процесс называется регенерацией изображения.

Регенерация изображения производится контроллерами ВТ и ПДП в режиме прямого доступа к памяти. Для получения кода очередного символа контроллер ВТ 3 активизирует выход 49 запроса прямого доступа. По этому сигналу контроллер ПДП 2 в свою очередь активизирует выход 40 запроса прямого доступа, связанный с одноименным входом 27 микропроцессора 1. Микропроцессор, закончив очередное обращение к памяти или порту ввода-вывода, переводит свои выходы, управляющие каналом, в высокоимпедансное состояние и сообщает об этом контроллеру ПДП, активизируя свой выход 59 подтверждения прямого доступа. Получив этот сигнал, контроллер ПДП 2 активизирует сигнал разрешения адреса на своем выходе 29, блокируя тем самым дешифратор 7, который запрещает появление активных уровней на всех своих выходах, кроме управляющего блоком оперативной памяти 5. Затем контроллер ПДП инициирует передачу данных из блока 5 в внутренние буферы контроллера ВТ3, формируя последовательность кодов адресов ячеек экранной области памяти и сопровождая каждый код вложенными друг в друга во времени сигналами на следующих своих управляющих выходах: подтверждения прямого доступа к памяти, чтение памяти, запись в устройство ввода-вывода. Первый из этих управляющих сигналов готовит контроллер ВТ к приему кода символа, второй вызывает чтение кода из блока оперативной памяти, третий стробирует занесение кода в контроллер ВТ.

Формирование символов на экране производится контроллером ВТ с помощью запоминающего узла знакогенератора 9, хранящего информацию о графическом представлении каждого символа. Символ кодируется в знакогенераторе матрицей m x n, где m - число строк телевизионного растpа в пределах знакоместа, а n - число точек, которые могут быть засвечены в строке в пределах знакоместа. Выбор матрицы в знакоместе определяется кодом отображаемого символа, устанавливаемого на выходах 45 контроллера ВТ, и поступающего на старшие разряды запоминающего узла знакогенератора 9. На младшие адресные входы узла 9 с выходов номеров строк растра 46 контроллера ВТ 3 поступает код, определяющий, какая строка матрицы символа должна быть прочитана в формирователь видеосигнала. Параллельный код строки символа в формирователе видеосигнала 10 преобразуется в последовательный сдвиговым регистром. Частота сдвигов задается генератором синхронизирующих сигналов 8. Изменение кодов отображаемых символов производится по сигналам, поступающим на вход символьной синхронизации контроллера ВТ из формирователя видеосигнала после окончания вывода на экран строки матрицы очередного символа.

Сигнал с выхода 47 горизонтальной синхронизации контроллера ВТ 3 осуществляет синхронизацию горизонтальной развертки видеотерминала и блокирует пропускание видеосигнала через элемент ИЛИ 11 во время обратного хода луча по горизонтали.

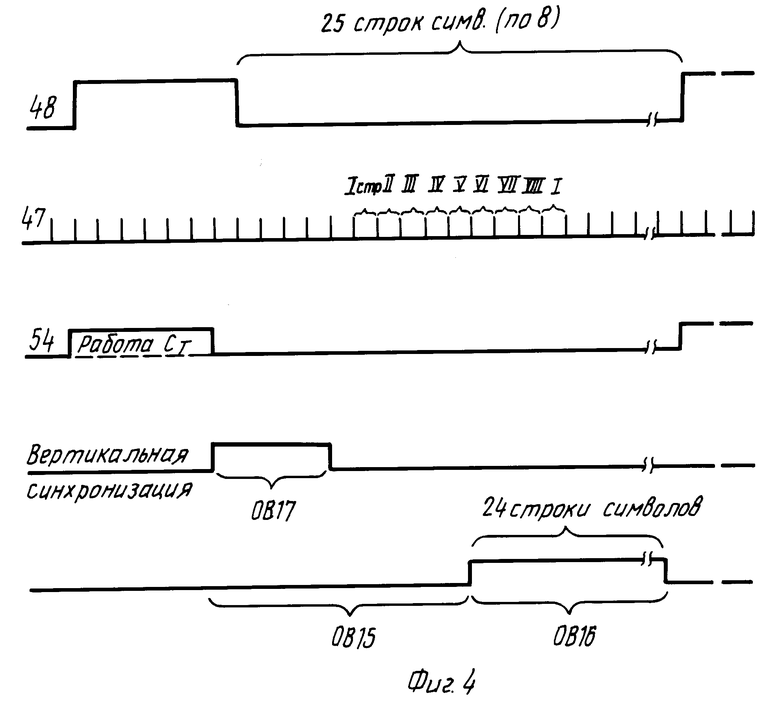

Функционирование узлов микроЭВМ, осуществляющих синхронизацию вертикальной развертки видеотерминала, описывается временной диаграммой, приведенной на фиг.4. Сигнал с выхода 48 вертикальной синхронизации контроллера ВТ передним фронтом переписывает информацию из регистра 12 в счетчик 13. Если в счетчике оказывается код, отличный от "0", на выходе элемента И 66 логического узла 14 устанавливается уровень лог."1", который пропускает через элемент И 67 сигналы, поступающие с выхода 47 горизонтальной синхронизации контроллера ВТ. Каждый из этих сигналов, воздействуя на счетный вход счетчика 13, уменьшает код, хранящийся в счетчике, на единицу. Таким образом, на выходе 57 логического узла 14 вырабатывается импульс положительной полярности длительностью, равной произведению периода горизонтальной синхронизации контроллера ВТ на величину, код которой хранится в регистре 12. Задний фронт импульса, выработанного логическим узлом 14 на выходе 57, запускает одновибраторы 15 и 17. Последний вырабатывает импульс вертикальной синхронизации видеотерминала необходимой для этого длительности. Задний фронт импульса, выработанного одновибратором 15, запускает одновибратор 16, сигнал с выхода которого блокирует пропускание видеосигнала через элемент ИЛИ 11 во время обратного хода луча по вертикали.

Описанный аппаратный механизм позволяет с помощью программы осуществлять плавное перемещение изображения на экране видеотерминала в вертикальном направлении. Пусть в исходном состоянии в регистре 12 записан код "1". Тогда положительная полка сигнала на выходе 57 логического узла будет иметь длительность один период частоты горизонтальной синхронизации. Следовательно, сигнал вертикальной синхронизации, поданный на видеотерминал, окажется смещенным относительно сигнала на одноименном выходе контроллера ВТ на один период горизонтальной синхронизации, а блокировка видеосигнала на элементе ИЛИ 11 окажется снятой при отображении первой строки растра первой символьной строки. Далее микропроцессор записывает в регистр 12 код "2". Теперь положительная полка сигнала на выходе 57 будет обладать длительностью в два периода частоты горизонтальной синхронизации, из-за чего соответствующим образом окажутся отодвинутыми сигналы вертикальной синхронизации и блокировки видеосигнала, вследствие чего отображение информации на экране начнется со второй строки растра первой символьной строки. Следует отметить, что поскольку интервал между импульсом вертикальной синхронизации, поступающим на видеотерминал, и снятием блокировки видеосигнала не изменяются, положение начала изображения на экране электронно-лучевой трубки не изменяется. Записывая в счетчик последовательно коды "3", "4",..."8", микропроцессор будет сдвигать изображение на 2, 3,...7 строк растра. После этого следует записать в регистр 12 код "1", сдвинув информацию в видеопамяти на одну строку символов вверх.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОАНАЛОГОВАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ И ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2022364C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке персональных бытовых ЭВМ, игровых автоматов и других средств вычислительной техники, построенных на основе микропроцессоров и осуществляющих индикацию информации на телевизионном мониторе или приемнике. Цель изобретения - расширение области применения устройства за счет возможности плавного перемещения изображения. ЭВМ содержит микропроцессор, контроллер прямого доступа к памяти, контроллер видеотерминала, узел ввода-вывода, блок оперативной памяти, блок постоянной памяти, дешифратор, генератор синхросигналов, запоминающий узел, формирователь видеосигнала, элемент ИЛИ, регистр, счетчик, логический узел и три одновибратора. 4 ил.

ЭВМ, содержащая микропроцессор, контроллер прямого доступа к памяти, контроллер видеотерминала, узел ввода-вывода, блок оперативной памяти, блок постоянной памяти, дешифратор, генератор синхросигналов, запоминающий узел, формирователь видеосигнала, элемент ИЛИ, причем адресный выход микропроцессора соединен с адресными входами блоков оперативной и постоянной памяти, информационным входом дешифратора, адресными входами-выходами контроллера прямого доступа к памяти, адресным входом контроллера видеотерминала, информационные входы-выходы микропроцессора соединены с информационными входами-выходами контроллеров видеотерминала, прямого доступа к памяти и узла ввода-вывода, с информационным входом блока оперативной памяти и информационными выходами блоков оперативной и постоянной памяти, выход чтения памяти микропроцессора через шину соединен с одноименным выходом контроллера прямого доступа к памяти и входом чтения блока постоянной памяти, выход записи в память микропроцессора через шину соединен с одноименным выходом контроллера прямого доступа к памяти и входом записи блока оперативной памяти, выходы чтения и записи устройства ввода-вывода микропроцессора через шину соединены соответственно с одноименными входами-выходами контроллера прямого доступа к памяти и входами узла ввода-вывода и контроллера видеотерминала, выход подтверждения прямого доступа микропроцессора соединен с одноименным входом контроллера прямого доступа к памяти, выход запроса прямого доступа которого подключен к одноименному входу микропроцессора, входы начальной установки микропроцессора и контроллера прямого доступа к памяти объединены между собой и подключены к входу начальной установки ЭВМ, выход разрешения адреса контроллера прямого доступа к памяти соединен со стробирующим входом дешифратора, первые четыре выхода которого подключены соответственно к входам обращения контроллеров прямого доступа к памяти и видеотерминала, блоков оперативной и постоянной памяти, а группа выходов связана с группой управляющих входов узла ввода-вывода, выход подтверждения прямого доступа к памяти контроллера прямого доступа к памяти соединен с одноименным входом контроллера видеотерминала, выход запроса прямого доступа к памяти которого соединен с одноименным входом контроллера прямого доступа к памяти, первый выход генератора синхросигналов подключен к тактовым входам микропроцессора и контроллера прямого доступа к памяти, второй выход генератора синхросигналов соединен с тактовым входом формирователя видеосигнала, выход синхронизации которого соединен с входом символьной синхронизации контроллера видеотерминала, выходы кода символа и номера строки растра которого подключены соответственно к группам старших и младших разрядов адресного входа запоминающего узла, группа выходов которого соединена с группой информационных входов формирователя видеосигнала, выход видеосигнала которого подключен к первому входу элемента ИЛИ, выход которого является выходом видеосигнала ЭВМ, выход горизонтальной синхронизации контроллера видеотерминала подключен к второму входу элемента ИЛИ и выходу горизонтальной синхронизации видеотерминала одноплатной ЭВМ, отличающаяся тем, что, с целью расширения области применения путем плавного перемещения изображения, она дополнительно содержит регистр, счетчик, логический узел и три одновибратора, причем информационный вход регистра связан с информационными входами-выходами микропроцессора, вход записи регистра подключен к пятому выходу дешифратора, а выход регистра соединен с информационным входом счетчика, вход записи которого связан с выходом вертикальной синхронизации контроллера видеотерминала, выходы счетчика подключены к информационным входам логического узла, связанного тактовым входом с выходом горизонтальной синхронизации контроллера видеотерминала, первый выход логического узла подключен к счетному входу счетчика, а второй выход соединен с первыми входами первого и второго одновибраторов, выход первого одновибратора соединен с первым входом третьего одновибратора, выход которого подключен к третьему входу элемента ИЛИ, выход второго одновибратора связан с выходом вертикальной синхронизации видеотерминала ЭВМ, а каждый из одновибраторов включает счетчик, элементы И, И - НЕ, ИЛИ, причем в одновибраторе вход записи счетчика одновибратора подключен к первому входу одновибратора, а счетный вход соединен с выходом элемента И - НЕ, первый вход которого является вторым входом одновибратора и соединен с выходом строчной синхронизации контроллера видеотерминала, а второй вход подключен к выходу элемента ИЛИ, входы которого связаны с выходами счетчика одновибратора, вход занесения которого связан с инверсным входом элемента И, соединенного прямым входом с выходом элемента ИЛИ, а выход подключен к выходу одновибратора, информационные входы счетчика одновибратора подключены к входам установки выдержки одновибратора, а логический узел включает элементы ИЛИ, И, входы элемента ИЛИ подключены к информационным входам логического узла, а выход соединен с вторым выходом логического узла и первым входом элемента И, второй вход которого связан с тактовым входом логического узла, а выход подключен к первому выходу логического узла.

| Горшков Д | |||

| и др | |||

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

Авторы

Даты

1994-12-15—Публикация

1990-11-26—Подача