Изобретение относится к импульсной технике и может быть использовано в дискретных цифровых системах автоматического контроля и регулирования.

Известны устройства для получения разностной частоты импульсов [1]. Недостатком этих устройств являются ограничения сверху по значению вычитаемых частот, обусловленные наличием в составе устройства тактового генератора и требованием непревышения значения вычитаемых частот частоты тактового генератора.

Известно также устройство для получения разностной частоты импульсов по авт. свид.СССР N 1264093, кл. G 01 R 23/00, 1985. Недостатком этого устройства является то, что его работоспособность обеспечивается только при несовпадении фаз входных сигналов и нарушается при их совпадении. Вторым недостатком является неопределенность длительности выходных импульсов при малой разности фаз входных сигналов.

Известно устройство для получения разностной частоты импульсов [2], содержащее две цепочки, каждая из которых состоит из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и двух синхронных D-триггеров, тактовые входы которых объединены между собой, а прямой выход первого триггера соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а его информационный вход соединен с прямым выходом второго триггера.

Указанное устройство наиболее близко к предлагаемому по техническому решению, оно выбрано за прототип. Недостатком известного устройства является ограниченный диапазон вычитаемых частот. Значения вычитаемых частот должны быть как минимум в два раза ниже частоты тактового генератора. Кроме того, известное устройство достаточно сложно.

Целью предлагаемого изобретения является устранение указанного недостатка - повышение надежности устройства путем его упрощения.

Указанная цель достигается тем, что тактовые входы второго и третьего синхронных D-триггеров подключены соответственно к первой и второй шинам входных частот, а информационный вход второго D-триггера соединен с прямым выходом третьего D-триггера, подключенного информационным входом к инверсному выходу второго D-триггера, прямой выход которого объединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, связанного по выходу с первым входом вновь введенного элемента ИЛИ-НЕ, второй вход которого подключен к тактовому входу первого синхронного D-триггера.

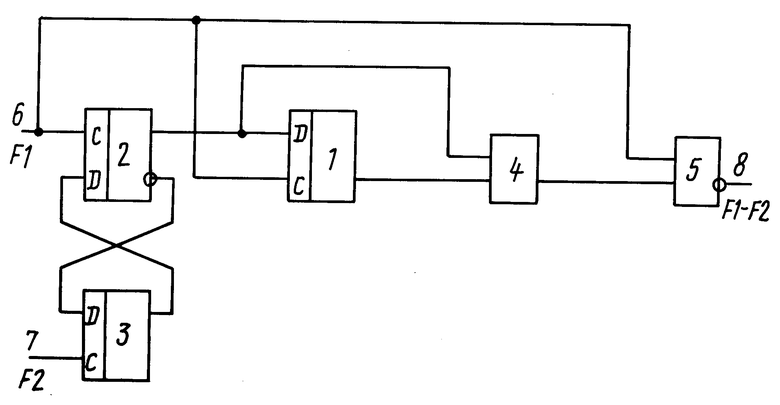

На чертеже приведена предлагаемая схема вычитания частот.

В состав устройства входят три D-триггера 1,2,3, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, вентиль 5, на логическом элементе 2 ИЛИ-НЕ.

Входная шина 6, на которую подается первая частота F1, соединена с входами синхронизации С D-триггеров 1,2 и входом вентиля 5. Входная шина 7, на которую подается вторая частота F2, соединена с синхронизирующим входом С D-триггера 3. Прямой выход D-триггера 2 (прямой или инверсный) соединен с информационным входом D D-триггера 1, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4. Выход этого элемента соединен с управляющим входом вентиля 5. Выход вентиля 5 соединен с выходной шиной устройства 8 F1-F2.

Рассмотрим работу схемы вычитания. Возможны три варианта прихода входных сигналов. Между двумя фронтами импульсов частоты F2, по которым возможно переключение D-триггера 3, приходит один, больше одного и ни одного фронта импульса частоты F1, по которому возможно переключение D-триггеров 1,2. Это соответствует случаям F1 = F2, F1 > F2, F1 < F2.

Рассмотрим первый случай F1 = F2. После прихода фронта импульса частоты F2 состояние D-триггеров 2 и 3 противоположны, поскольку D-вход D-триггера 3 соединен с инверсным выходом D-триггера 2. Следующим приходит фронт импульсов F1. По этому фронту информация из D-триггера 2 переписывается в D-триггер 1, а из D-триггера 3 в D-триггер 2. Поскольку D-триггеры 2 и 3 находились в разном состоянии, то после фронта импульса частоты F1 D-триггеры 1 и 2 будут также находиться в различном состоянии. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 устанавливается сигнал, закрывающий вентиль 5. Теперь D-триггеры 2 и 3 находятся в одинаковом состоянии. Следующий импульс частоты F2 вновь переключает D-триггер 3. По очередному импульсу частоты F1 информация из D-триггера 2 переписывается в D-триггер 1, а из D-триггера 3 в D-триггер 2. Сигнал на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 подтверждает закрытое состояние вентиля 5. Далее процессы повторяются и на выходе 8 устройства импульсы в рассматриваемом случае (F1 = F2) отсутствуют.

Во втором случае F1 > F2 с приходом импульса частоты F2 состояния D-триггеров 2,3 различны. Следующим на схему приходит импульс частоты F1. Поскольку, как и в первом случае, после прихода фронта сигнала частоты F1 D-триггеры 2,1 оказываются в различных состояниях, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 вырабатывает сигнал, закрывающий вентиль 5. D-триггеры 2,3 находятся в одинаковом состоянии. С приходом очередного импульса частоты F1 информация из D-триггера 2 вновь переписывается в D-триггер 1, а из D-триггера 3 в D-триггер 2. Так как состояние D-триггеров 2,3 в рассматриваемом случае одинаково, одинаковым оказывается и состояние D-триггеров 2 и 1. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 вырабатывает сигнал, открывающий вентиль 5, благодаря чему импульс частоты F1 проходит на выходную шину. Состояния D-триггеров 1-3 одинаковы и все последующие импульсы частоты F1 через открытый вентиль 5 проходят на выход схемы 8 до тех пор, пока не придет импульс частоты F2.

В третьем случае F2 < F1 импульс частоты F2 переключает D-триггер 3, устанавливая его в состояние, противоположное состоянию D-триггера 2. Каждый последующий импульс частоты F2 подтверждает состояние D-триггера 3. Поскольку импульс частоты F1 в рассматриваемом случае не поступает, не поступает импульс и на выход 8 устройства.

В качестве примера практической реализации на схеме D-триггеры 1-3 изображены как триггеры, переключающиеся по передним фронтам импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 выполнен в виде полусумматора по модулю 2, вентиль 5 выполнен в виде логической схемы 2 ИЛИ-НЕ. Длительность выходного импульса на шине 8 равна длительности логического нуля импульса частоты F1. Если необходимо получить на выходе 8 импульс логической единицы длительностью, равной длительности логической единицы импульса частоты F1, то D-триггер 2,1 необходимо выполнять с переключением по заднему фронту импульса частоты F1, а вентиль 5 в этом случае может быть выполнен в виде логической схемы 2И с инвертором на выходе, соединенным с элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 4. Работа схемы не нарушится, если D-вход D-триггера 1 соединить не с прямым, а с инверсным выходом D-триггера 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования импульсов разностной частоты | 1990 |

|

SU1764156A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1993 |

|

RU2111609C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 1999 |

|

RU2159988C1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2110146C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРКИ ТАКТОВЫХ СИГНАЛОВ | 1992 |

|

RU2084016C1 |

| Устройство для устранения влияния дребезга сигнала | 1989 |

|

SU1725371A1 |

| Формирователь разностной частоты импульсных последовательностей | 1984 |

|

SU1265985A1 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 2005 |

|

RU2285334C1 |

Изобретение относится к импульсной технике и может быть использовано в дискретных цифровых системах автоматического контроля и регулирования, при этом оно обладает повышенной надежностью за счет достаточной простоты. Устройство содержит три D-триггера 1,2,3 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, вентиль 5 на логическом элементе ИЛИ - НЕ. 1 ил.

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ РАЗНОСТНОЙ ЧАСТОТЫ, содержащее три синхронных D-триггера и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с прямым выходом первого D-триггера, объединенного своими тактовым и информационным входами с тактовым входом и прямым выходом второго D-триггера соответственно, отличающееся тем, что, с целью повышения надежности устройства путем его упрощения, введен элемент ИЛИ - НЕ, при этом тактовые входы второго и третьего синхронных D-триггеров подключены соответственно к первой и второй шинам входных частот, а информационный вход второго D-триггера соединен с прямым выходом третьего D-триггера, подключенного информационным входом к инверсному выходу второго D-триггера, прямой выход которого объединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, связанного по выходу с первым входом элемента ИЛИ - НЕ, второй вход которого подключен к тактовому входу первого синхронного D-триггера.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для формирования сигнала разностной частоты импульсных последовательностей | 1981 |

|

SU1086552A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-02-09—Публикация

1990-04-17—Подача