Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации.

Известен преобразователь фазоманипулированного кода в бинарный код (см. Авторское свидетельство СССР №1774501 от 08.01.90, МКИ: Н 03 М 5/12, "Преобразователь кода", В.Л.Котляров, С.В.Мотыжев, Л.В.Ольшевская, опубликовано 07.11.92, Бюл. №41), выбранный в качестве аналога изобретения и содержащий первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого объединен с входом элемента задержки и является входом преобразователя, выход соединен с С-входом триггера, инверсный выход которого соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является первым выходом преобразователя. Прямой выход триггера является вторым выходом преобразователя. Первый вход и выход мажоритарного элемента подключены соответственно к прямому выходу и D-входу триггера. Первый выход элемента задержки соединен со вторым входом мажоритарного элемента, второй выход - со вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и третьим входом мажоритарного элемента.

Недостатком известного преобразователя является низкая помехоустойчивость, обусловленная пропусканием на информационный выход входного сигнала логического "0" или логической "1" с любой длительностью не менее заданной величины и пропусканием на тактовый выход любых входных сигналов, просуммированных с выходными информационными, что существенно затрудняет выделение полезной информации из потока входных сигналов потребителем информации.

Известен преобразователь фазоманипулированного кода в бинарный код (см. патент РФ №2163418 от 22.06.99, МПК: Н 03 М 5/12, "Преобразователь фазоманипулированного кода в бинарный код", Курочкин А.А., Мартынов А.П., Панкратов С.В., Фомченко В.Н., Шишкин Г.И., опубликован 20.02.2001, Бюл. №5), выбранный в качестве прототипа и содержащий генератор импульсов, блок дифференцирования, синхронизатор, делитель частоты, селектор, регистр, счетчик символов, информационный вход, тактовый выход, информационный выход и вход "Сброс".

Первый вход блока дифференцирования соединен с первым входом синхронизатора, выход которого соединен с тактовым выходом делителя частоты, R-вход делителя частоты соединен с выходом селектора, а выход является тактовым выходом и соединен с тактовым входом регистра. Выход регистра является информационным выходом. Информационный вход блока дифференцирования является информационным входом.

Блок дифференцирования состоит из сдвигающего регистра и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым выходом блока дифференцирования, а первый и второй входы - с соответствующими выходами его сдвигающего регистра. D-вход и С-вход сдвигающего регистра соединены соответственно с информационным и тактовым входами блока дифференцирования. Второй и третий выходы блока дифференцирования соединены соответственно с первым и вторым выходами его сдвигающего регистра. Информационный вход регистра соединен с третьим выходом блока дифференцирования, второй выход которого соединен с информационным входом селектора, выход которого соединен с третьим входом синхронизатора и R-входом регистра. Выход генератора импульсов соединен с тактовыми входами блока дифференцирования и селектора, а также со вторым входом синхронизатора. Вход "Сброс" селектора является входом "Сброс".

Селектор содержит первый, второй, третий, четвертый и пятый элементы ИЛИ-НЕ, первый, второй и третий элементы И-НЕ, инвертор, первый и второй счетчики, интегрирующую RC-цепь. Первые входы первого элемента ИЛИ-НЕ и первого элемента И-НЕ соединены через интегрирующую RC-цепь с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ, а выход - с первым входом третьего элемента ИЛИ-НЕ. Второй вход которого соединен с выходом первого элемента ИЛИ-НЕ, а выход - с первым входом второго элемента И-НЕ, выход которого соединен с R-входом первого счетчика. С-вход первого счетчика соединен с выходом четвертого элемента ИЛИ-НЕ, первый вход которого соединен с выходом первого счетчика, вторым входом первого элемента ИЛИ-НЕ и с первым входом третьего элемента И-НЕ. Второй вход третьего элемента И-НЕ соединен с выходом первого элемента И-НЕ, а выход - с R-входом второго счетчика, С-вход которого соединен с выходом пятого элемента ИЛИ-НЕ. Первый вход пятого элемента ИЛИ-НЕ соединен с выходом второго счетчика и с входом инвертора, выход которого соединен со вторым входом первого элемента И-НЕ и с выходом селектора. Первые входы первого элемента ИЛИ-НЕ и первого элемента И-НЕ соединены с информационным входом селектора. Вторые входы четвертого и пятого элементов ИЛИ-НЕ соединены с тактовым входом селектора. Второй вход второго элемента И-НЕ соединен с входом "Сброс" селектора.

Синхронизатор содержит счетчик и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого являются соответственно первым и третьим входами синхронизатора, а выход соединен с R-входом счетчика. С-вход и выход которого являются соответственно вторым входом и выходом синхронизатора.

С-вход счетчика символов соединен с выходом делителя частоты, R-вход - с выходом селектора, а выход - с выходом "Сброс".

Первым недостатком прототипа является большое время передачи информации.

Вторым недостатком является сложность схемы из-за необходимости формирования синхросигнала.

Задачей, решаемой заявляемым изобретением, является создание преобразователя кода, обладающего уменьшенным временем передачи информации и отличающегося простотой схемной реализации.

Технический результат заключается в уменьшении времени передачи информации и упрощении схемы преобразователя кода.

Это достигается тем, что преобразователь фазоманипулированного кода в бинарный код содержит генератор импульсов, счетный триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй счетчики, элемент И-НЕ, входную и выходную информационные шины, шину выходных тактовых импульсов. Новым является то, что дополнительно введены RS-триггер, элемент И, первый и второй элементы ИЛИ, первый и второй D-триггеры, счетные входы которых объединены и соединены со счетными входами первого и второго счетчика, выходы вторых разрядов которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с выходной информационной шиной, выходы третьих разрядов первого и второго счетчиков соединены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с R-входом RS триггера и с R-входом счетного триггера, вход которого соединен с входной информационной шиной, а выход - с D входом первого D-триггера, выход которого соединен с D-входом второго D-триггера, с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с S-входом RS триггера и прямым выходом второго D-триггера, инверсный выход которого соединен с R-входом первого счетчика и первым входом элемента И-НЕ, второй вход которого соединен с выходом RS триггера и первым входом элемента И, второй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с шиной выходных тактовых импульсов, R-вход второго счетчика соединен с выходом элемента И-НЕ, выход генератора импульсов соединен со счетным входом первого D-триггера.

Указанная совокупность признаков позволяет:

- уменьшить время передачи информации за счет того, что в заявляемом устройстве время передачи логического "0" равно Тт/4, (где Тт - длительность тактового интервала), время передачи логической "1" равно 3Тт/4, а в прототипе время передачи как логического "0", так и логической "1" равно Тт;

- упростить схему преобразователя кода за счет исключения необходимости использования формирователя синхросигнала.

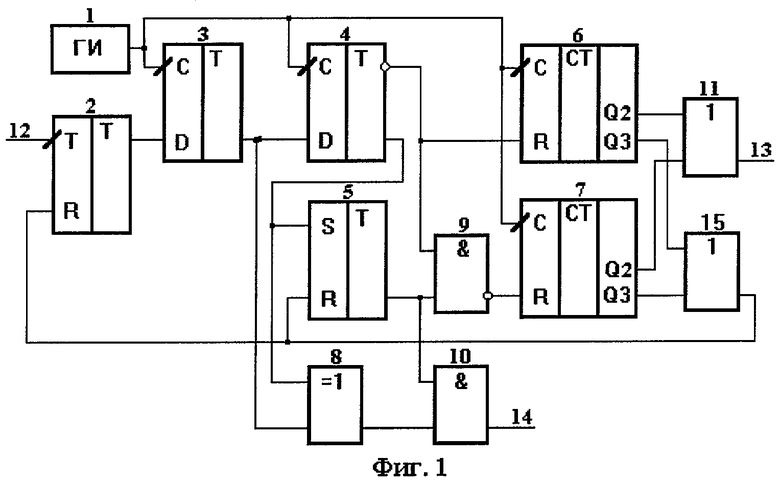

На фиг.1 приведена принципиальная схема преобразователя фазоманипулированного кода в бинарный код, на фиг.2 - диаграммы работы преобразователя.

Преобразователь фазоманипулированного кода в бинарный код содержит (см. фиг.1) генератор 1 импульсов, счетный триггер 2, первый D-триггер 3, второй D-триггер 4, RS-триггер 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, элемент И-НЕ 9, элемент И 10, первый счетчик 6, второй счетчик 7, первый элемент ИЛИ 11, второй элемент ИЛИ 15, входную 12 и выходную 13 информационные шины, шину выходных тактовых импульсов 14.

Счетный вход триггера 2 подключен к входной информационной шине 12, R-вход - к R-входу RS-триггера 5 и выходу второго элемента ИЛИ 15, выход подключен к D-входу первого D-триггера 3, выход которого соединен с D-входом второго D-триггера 4 и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, второй вход которого соединен с прямым выходом второго D-триггера 4 и S-входом RS-триггера 5, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 соединен с первым входом элемента И 10, выход которого соединен с шиной выходных тактовых импульсов 14, а второй вход соединен с выходом RS-триггера 5 и первым входом элемента И-НЕ 9, выход которого соединен с R-входом второго счетчика 7, а второй вход - с инверсным выходом второго D-триггера 4 и R-входом первого счетчика 6, счетный вход первого счетчика 6 соединен с счетным входом второго счетчика 7, счетными входами первого D-триггера 3 и второго D-триггера 4 и выходом генератора импульсов 1, выход второго разряда первого счетчика 6 соединен с первым входом первого элемента ИЛИ 11, выход которого соединен с выходной информационной шиной 13, а второй вход с выходом второго разряда второго счетчика 7, выход третьего разряда которого соединен с первым входом второго элемента ИЛИ 15, второй вход которого соединен с выходом третьего разряда первого счетчика 6.

Генератор 1 импульсов может быть реализован по схеме кварцевого генератора (см. Потемкин И.С. "Функциональные узлы цифровой информатики", М.: Энергоиздат, 1988, с.240, рис.7.9). Частота работы генератора 1 импульсов должна превышать частоту передачи информационных разрядов. В данном варианте преобразователя частота работы генератора 1 импульсов в 8 раз превышает частоту передачи информационных разрядов.

Преобразователь фазоманипулированного кода в бинарный код работает следующим образом.

В режиме ожидания информации на входной информационной шине 12 присутствует уровень логического "0". Генератор импульсов 1 формирует импульсы с периодом повторения Тт/8. Триггеры 2, 3, 4, 5 и счетчики 6, 7 находятся в состоянии логического "0". На тактовом 14 и информационном 13 выходах удерживается уровень логического "0".

При поступлении положительного импульса на D-вход (шина 12) счетный триггер 2 переключается в состояние логической "1". Фронтом импульса генератора в состояние логической "1" переключается триггер 3. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 формируется положительный импульс длительностью Тт/8, прохождение которого на тактовый выход 14 запрещено сигналом логического "0" с выхода триггера 5. С задержкой Тт/8 относительно переключения триггера 3 фронтом импульса генератора переключается в состояние логической "1" триггер 4. При этом на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 устанавливается уровень логического "0", разрешается переключение счетчика 6 и переключается в состояние логической "1" триггер 5, разрешая дальнейшее прохождение импульсов с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 на выход 14 устройства. На выходе элемента И-НЕ 9 сохраняется уровень логической "1", запрещающий переключение счетчика 7.

С приходом следующего положительного импульса на D-вход (шина 12) счетный триггер 2 переключается в состояние логического "0". Фронтом импульса генератора в состояние логического "0" переключается триггер 3. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 формируется положительный импульс длительностью Тт/8, который проходит на тактовый выход 14 и производит опрос информации на выходе 13. Если к моменту опроса триггер второго разряда счетчика 6 переключится в состояние логической "1", что свидетельствует о поступлении на D-вход 12 сигнала логической единицы с длительностью паузы больше Тт/4, на выходе 13 будет присутствовать информация логической "1". В противном случае на выходе 13 сохранится состояние логического "0". С задержкой Тт/8 относительно переключения триггера 3 фронтом импульса генератора переключается в состояние логического "0" триггер 4, обнуляя счетчик 6 и запрещая его переключение. Тактовый импульс на выходе 14 заканчивается. На выходе элемента И-НЕ 9 появляется уровень логического "0", разрешающий переключение счетчика 7. С приходом следующего импульса устройство работает аналогично за исключением того, что длительность паузы между импульсами анализируется по состоянию второго разряда счетчика 7.

По окончании информационной посылки, как только пауза превысит по длительности значение Тт/2, переключается в состояние логической "1" триггер третьего разряда счетчика 6 или 7 (в зависимости от того, на R-вход какого счетчика подан разрешающий сигнал), вызывая переключение триггера 5 в состояние логического "0" и обнуление счетчика. Устройство переходит в режим ожидания входной информации.

В представленном устройстве вместо счетчиков можно использовать сдвигающие регистры.

Таким образом, данный преобразователь кода осуществляет передачу логического "0" сигналом на выходной информационной шине 5 с длительностью Тт/8 и паузой Тт/8, а при передаче логической "1" с длительностью Тт/8 и паузой 5Тт/8. Это позволяет уменьшить время передачи (информационной посылки с равным количеством сигналов логического "0" и логической "1") в два раза по сравнению с прототипом, поскольку в прототипе время передачи сигнала логического "0" и логической "1" равна Тт (где Тт - длительность тактового интервала). Одновременно упрощается схема преобразователя за счет отказа от использования формирователя синхросигнала.

Изготовлен лабораторный макет преобразователя кода, испытания которого подтвердили работоспособность и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 2005 |

|

RU2297096C1 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2005 |

|

RU2282306C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2002 |

|

RU2249911C2 |

| ПРЕОБРАЗОВАТЕЛЬ БИИМПУЛЬСНОГО КОДА В БИНАРНЫЙ КОД | 2004 |

|

RU2258305C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2002 |

|

RU2253944C2 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2258304C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 1999 |

|

RU2159988C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ШИРОТНО-МАНИПУЛИРОВАННЫЙ КОД | 2003 |

|

RU2250562C2 |

| Масштабный преобразователь кодов | 1988 |

|

SU1569994A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации. Техническим результатом является уменьшение времени передачи информации и упрощение схемы преобразователя кода. Устройство содержит генератор импульсов, счетный триггер, D-триггеры, RS-триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, элемент И, счетчики, элементы ИЛИ, входную и выходную информационные шины, шину выходных тактовых импульсов. 2 ил.

Преобразователь фазоманипулированного кода в бинарный код, содержащий генератор импульсов, счетный триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй счетчики, элемент И-НЕ, входную и выходную информационные шины, шину выходных тактовых импульсов, отличающийся тем, что дополнительно введены RS-триггер, элемент И, первый и второй элементы ИЛИ, первый и второй D-триггеры, счетные входы которых объединены и соединены со счетными входами первого и второго счетчиков, выходы вторых разрядов которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с выходной информационной шиной, выходы третьих разрядов первого и второго счетчиков соединены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с R-входом RS триггера и с R-входом счетного триггера, вход которого соединен с входной информационной шиной, а выход - с D входом первого D-триггера, выход которого соединен с D-входом второго D-триггера, с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с S-входом RS триггера и прямым выходом второго D-триггера, инверсный выход которого соединен с R-входом первого счетчика и первым входом элемента И-НЕ, второй вход которого соединен с выходом RS триггера и первым входом элемента И, второй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с шиной выходных тактовых импульсов, R-вход второго счетчика соединен с выходом элемента И-НЕ, выход генератора импульсов соединен со счетным входом первого D-триггера.

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 1999 |

|

RU2159988C1 |

| Преобразователь кода | 1990 |

|

SU1774501A1 |

| Преобразователь биимпульсного кода в бинарный | 1989 |

|

SU1626384A1 |

| JP 5327513, 10.12.1993 | |||

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

2006-10-10—Публикация

2005-03-10—Подача