Изобретение относится к устройствам вычислительной техники и систем управления и может быть использовано в системах передачи данных.

Известен преобразователь бинарного кода в фазоманипулированный код (см. авторское свидетельство СССР N 1332536 от 07.03.86, МКИ H 03 M 5/12, "Преобразователь кода", И.В.Келтуяла, опубл. 23.08.87, Бюл. N 31), содержащий генератор импульсов, первый и второй элементы И, элемент НЕ, выход которого подключен к первому входу второго элемента И, триггер, выход которого является выходом преобразователя. Первый вход первого элемента И и вход элемента НЕ объединены и являются входом преобразователя. D-вход триггера подключен к выходу элемента НЕ. Прямой выход генератора импульсов соединен со вторыми входами первого и второго элементов И, выходы которых и инверсный выход генератора импульсов соединены соответственно с S-, R- и C-входами триггера.

Недостатком известного преобразователя является низкая надежность функционирования, обусловленная тем, что переключающий перепад импульса с инверсного выхода генератора может приходить на C-вход триггера до того, как с S- или R-входа снимается сигнал, поступающий с прямого выхода генератора через элементы И, вследствие задержки сигнала как в самом генераторе, так и в элементах И. В этом случае переключение триггера сигналом по C-входу, а следовательно, и формирование выходных сигналов производиться не будет. Указанный недостаток накладывает определенные ограничения на выбор элементной базы и схемотехнических решений преобразователя.

Кроме того, в режиме ожидания, когда на входе преобразователя присутствует уровень логического "0" и соответствующий сигнал должен присутствовать на его выходе, триггер может переключаться сигналом по C-входу после снятия сигнала с R-входа, формируя на выходе последовательность импульсов, которая затрудняет выделение момента начала поступления полезной информации.

Известен преобразователь бинарного кода в фазоманипулированный код (см. статью В. П.Климова, И.М.Казанова, И.Л.Вишнякова "Кодирующие устройства оптических каналов" в сборнике статей "Электронная техника в автоматике", под ред. Ю. И. Конева, выпуск 16. - М.: Радио и связь, 1985 г., с.262, рис.4), являющийся прототипом и содержащий тактируемый фронтом D-триггер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого является информационным входом преобразователя, второй вход соединен с выходом генератора тактовых импульсов, а выход - с D-входом триггера, выход которого является информационным выходом преобразователя, а C-вход - его тактовым входом, соединенным с шиной тактовых импульсов удвоенной частоты.

Недостатком известного преобразователя является формирование на выходе в режиме ожидания последовательности импульсов, которая затрудняет выделение момента начала поступления полезной информации.

Недостатком является также отсутствие возможности формирования признака начала информационной посылки, обеспечивающего взаимную синхронизацию приемника и передатчика и достоверную передачу сообщений.

К недостаткам прототипа можно отнести также отсутствие возможности неискаженной передачи на выход входного бинарного кода или любого логического состояния.

Задачей, решаемой предлагаемым техническим решением, является создание преобразователя бинарного кода в фазоманипулированный код, обладающего широкими функциональными возможностями.

Технический результат, заключающийся в расширении функциональных возможностей, достигается тем, что в преобразователь бинарного кода в фазоманипулированный код, содержащий входную информационную шину и шину тактовых импульсов удвоенной частоты, соединенную с C-входом тактируемого фронтом D-триггера, D-вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с выходной информационной шиной, введены шина разрешения преобразования, шина запрета синхросигнала, формирователь синхросигнала, коммутатор, элемент ИЛИ-НЕ и счетный триггер, счетный вход которого соединен с шиной тактовых импульсов удвоенной частоты, а инверсный выход - с тактовым входом формирователя синхросигнала и первым входом элемента ИЛИ-НЕ, второй вход которого соединен с шиной разрешения преобразования, а выход - с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом коммутатора, первый вход которого соединен с входной информационной шиной, управляющий вход - с третьим входом элемента ИЛИ-НЕ и с управляющим выходом формирователя синхросигнала, информационный выход которого соединен со вторым входом коммутатора, а управляющий вход - с шиной запрета синхросигнала. Кроме того, формирователь синхросигнала содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, счетный триггер, первый и второй тактируемые фронтом D-триггеры, R-входы которых соединены с R-входом счетного триггера, управляющим входом формирователя синхросигнала и с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с управляющим выходом формирователя синхросигнала, а второй вход - с инверсным выходом второго D-триггера, D-вход которого соединен с прямым выходом первого D-триггера, D-вход которого соединен с шиной питания, а инверсный выход - с информационным выходом формирователя синхросигнала и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с тактовым входом формирователя синхросигнала, а выход - со счетным входом счетного триггера, инверсный выход которого соединен с тактовыми входами первого и второго D-триггеров. Кроме того, формирователь синхросигнала содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и тактируемый фронтом D-триггер, D-вход которого соединен с шиной питания, C-вход - с тактовым входом формирователя синхросигнала, а R-вход - с управляющим входом формирователя синхросигнала и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с управляющим выходом формирователя синхросигнала, а второй вход - с инверсным выходом D-триггера и с информационным выходом формирователя синхросигнала.

Указанная совокупность признаков позволяет расширить функциональные возможности преобразователя бинарного кода в фазоманипулированный код за счет обеспечения возможности:

- неискаженной передачи на выход входной информации в любом коде или любого логического уровня входного сигнала для проверки канала связи или установления статического режима при перерыве в передаче информации;

- одного из двух вариантов признака начала информационной посылки в фазоманипулированном или бинарном коде: при непрерывной передаче сообщений используется первый вариант синхросигнала длительностью в 3 тактовых интервала, в первой половине которого передается уровень логической "1", а во второй половине - логического "0" (указанный синхросигнал отличается по структуре от двоичного кода отсутствием обязательных переходов в первом и третьем тактах); при передаче одиночного сообщения после перерыва используется второй вариант синхросигнала в виде логической "1" в первом (дополнительном) разряде кода.

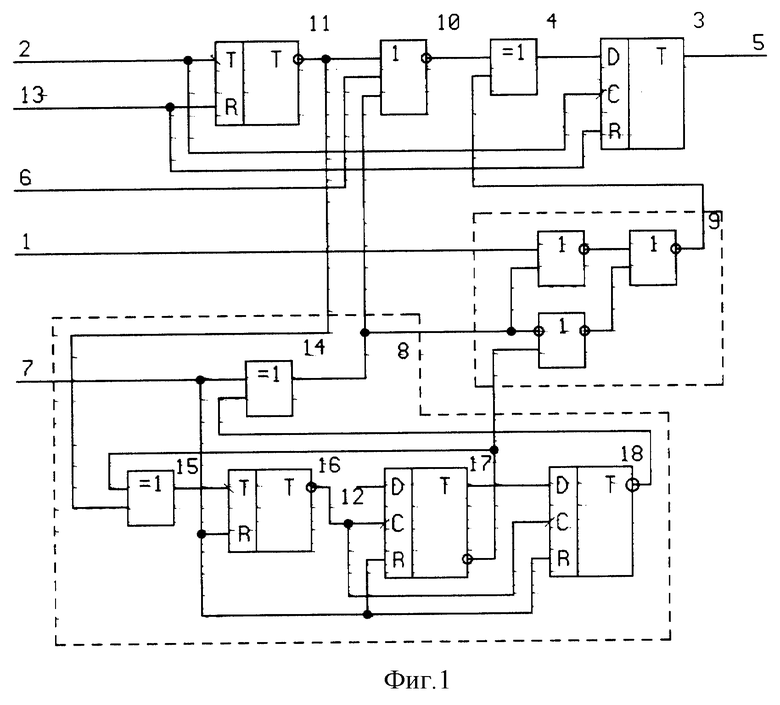

На фигуре 1 приведена принципиальная электрическая схема преобразователя бинарного кода в фазоманипулированный код с формирователем первого варианта синхросигнала, на фигуре 2 - принципиальная электрическая схема формирователя второго варианта синхросигнала, на фигуре 3 - диаграммы работы преобразователя в первом режиме.

Преобразователь содержит (см. фиг. 1) входную информационную шину 1, шину 2 тактовых импульсов удвоенной частоты, тактируемый фронтом D-триггер 3, элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, выходную информационную шину 5, шину 6 разрешения преобразования, шину 7 запрета синхросигнала, формирователь 8 синхросигнала, коммутатор 9, элемент 10 ИЛИ-НЕ, счетный триггер 11, шину 12 питания, шину 13 сброса.

Шина 2 тактовых импульсов удвоенной частоты соединена с C-входом тактируемого фронтом D-триггера 3, D-вход которого соединен с выходом элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с выходной информационной шиной 5. Счетный вход счетного триггера 11 соединен с шиной 2 тактовых импульсов удвоенной частоты, а инверсный выход - с тактовым входом формирователя 8 синхросигнала и первым входом элемента 10 ИЛИ-НЕ, второй вход которого соединен с шиной 6 разрешения преобразования, а выход - с первым входом элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ. Второй вход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом коммутатора 9, первый вход которого соединен с входной информационной шиной 1, управляющий вход - с третьим входом элемента 10 ИЛИ-НЕ и с управляющим выходом формирователя 8 синхросигнала. Информационный выход формирователя 8 синхросигнала соединен со вторым входом коммутатора 9, а управляющий вход - с шиной 7 запрета синхросигнала. R-входы D-триггера 3 и счетного триггера 11 соединены с шиной 13 сброса.

Формирователь 8 синхросигнала (первый вариант) содержит (см. фиг. 1) первый 14 и второй 15 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, счетный триггер 16, первый 17 и второй 18 тактируемые фронтом D-триггеры, R-входы которых соединены с R-входом счетного триггера 16, управляющим входом формирователя 8 синхросигнала и с первым входом первого элемента 14 ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход первого элемента 14 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим выходом формирователя 8 синхросигнала, а второй вход - с инверсным выходом второго D-триггера 18, D-вход которого соединен с прямым выходом первого D-триггера 17. D-вход первого D-триггера 17 соединен с шиной 12 питания, а инверсный выход - с информационным выходом формирователя 8 синхросигнала и с первым входом второго элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с тактовым входом формирователя 8 синхросигнала, а выход - со счетным входом счетного триггера 16. Инверсный выход счетного триггера 16 соединен с тактовыми входами первого D-триггера 17 и второго D- триггера 18.

Формирователь 8 синхросигнала (второй вариант) содержит (см. фиг. 2) элемент 19 ИСКЛЮЧАЮЩЕЕ ИЛИ и тактируемый фронтом D-триггер 20, D-вход которого соединен с шиной 12 питания, C-вход - с тактовым входом формирователя 8 синхросигнала, а R-вход с управляющим входом формирователя 8 синхросигнала и с первым входом элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим выходом формирователя 8 синхросигнала, а второй вход - с инверсным выходом D-триггера 20 и с информационным выходом формирователя 8 синхросигнала.

Коммутатор 9 может быть выполнен на основе мультиплексора (см. книгу: Цифровые интегральные микросхемы: Справочник /П.П.Мальцев и др.-М.: Радио и связь, 1994, с.111, рис.3.42а), на основе элемента И-ИЛИ (см. книгу: Зельдин Е. А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. - Л.: Энергоатомиздат. Ленинградское отд-ние, 1986, с. 97, рис. 7.1б) или на основе элементов ИЛИ-НЕ, как показано на фигуре 1.

Преобразователь работает следующим образом.

Преобразователь может работать в следующих режимах:

1) преобразования бинарного кода в фазоманипулированный код с формированием первого варианта синхросигнала при непрерывной передаче сообщений (используется синхросигнал длительностью в 3 тактовых интервала, в первой половине которой передается уровень логической "1", а во второй половине - логического "0");

2) преобразования бинарного кода в фазоманипулированный код с формированием второго варианта синхросигнала при передаче одиночного сообщения (после перерыва используется синхросигнал в виде логической "1" в первом (дополнительном) разряде кода);

3) неискаженной передачи на выход входной информации в любом коде или любого логического уровня входного сигнала;

4) режиме с формированием первого варианта синхросигнала при непрерывной передаче сообщений;

5) режиме с формированием второго варианта синхросигнала при передаче одиночных сообщений.

Для режимов один, два, четыре, пять с управляющего выхода формирователя 8 синхросигнала можно выдавать сигнал окончания синхросигнала в устройство выдачи информации (на фиг. 1, фиг. 2 не показано) для упрощения схемной реализации последнего.

Для режимов три, четыре, пять можно выдавать потребителю (на фиг. 1, фиг. 2 не показан) тактовые импульсы с выхода счетного триггера 11.

В исходном состоянии на шине 6 разрешения преобразования, шине 7 запрета синхросигнала, шине 13 сброса уровень логической "1", на входной информационной шине 1, шине 2 тактовых импульсов удвоенной частоты, выходной информационной шине 5 уровень логического "0". D-триггер 3, формирователь 8 синхросигнала, коммутатор 9, элемент 10 ИЛИ-НЕ, счетный триггер 11 находятся в состоянии логического "0". На выходе элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ - уровень логической "1".

Рассмотрим работу преобразователя в режиме один. Диаграммы работы преобразователя в первом режиме приведены на фигуре 3. На шину 2 поступают тактовые импульсы удвоенной частоты. На шине 13 и 6 устанавливаются уровни логического "0". На выходной информационной шине 5 - логический "0".

При поступлении на шину 7 уровня логического "0" снимается удерживающий потенциал с R-входов триггеров 16, 17 и 18 формирователя 8. На управляющем выходе формирователя 8 устанавливается логическая "1", которая поступает на третий вход элемента 10 ИЛИ- НЕ, запрещая прохождение тактовых импульсов с выхода счетного триггера 11 на время формирования синхросигнала и на управляющий вход коммутатора 9, разрешая поступление на его выход с информационного выхода формирователя 8 логической "1", которая поступает через элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ на D-вход D-триггера 3. Для синхронизации работы преобразователя и устройства выдачи информации можно выдавать в последний тактовые импульсы с выхода счетного триггера 11.

По фронту импульса, поступающего на шину 2 тактовых импульсов удвоенной частоты, на выходе D-триггера 3 и соответственно на выходной информационной шине 5 преобразователя устанавливается логическая "1", а по срезу импульса происходит переключение счетного триггера 11. На выходе элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ формируется сигнал логической "1", который переключает триггер 16 в состояние логической "1". По срезам двух последующих импульсов, поступающих на шину 2, происходит дальнейшее переключение счетного триггера 11. На выходе элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ формируется фронт, который устанавливает счетный триггер 16 в нулевое состояние. На его выходе формируется фронт, переключающий в единичное состояние D-триггер 17, на инверсном выходе которого устанавливается логический "0", поступающий на вход элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ, который изменяет фазу тактовых импульсов, на тактовый вход счетного триггера 16 и на информационный выход формирователя 8 синхросигнала, а далее через коммутатор 9 и элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ на D-вход D-триггера 3. По фронту следующего импульса, поступающего на шину 2 тактовых импульсов удвоенной частоты, на выходе D-триггера 3 и соответственно на выходной информационной шине 5 преобразователя устанавливается логический "0", а по срезу импульса происходит переключение счетного триггера 11. На выходе элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ формируется фронт, который устанавливает счетный триггер 16 в единичное состояние. По срезам двух последующих импульсов, поступающих на шину 2 тактовых импульсов удвоенной частоты, происходит дальнейшее переключение счетного триггера 11. В итоге он устанавливается в нулевое состояние. На выходе элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ формируется фронт, который устанавливает счетный триггер 16 в нулевое состояние. На его выходе формируется фронт, переключающий в единичное состояние D-триггеры 17, 18, на инверсном выходе последнего устанавливается логический "0", поступающий через элемент 14 ИСКЛЮЧАЮЩЕЕ ИЛИ на управляющий выход формирователя 8 синхросигнала, а далее на третий вход элемента 10 ИЛИ-НЕ, на выходе которого устанавливается логическая "1", и на управляющий вход коммутатора 9, разрешая поступление на второй вход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ логических уровней входной информационной шины 1.

После установления логической "1" на шине 7 запрета синхросигнала формирователь 8 синхросигнала установится в нулевое состояние: на его информационном выходе установится логическая "1", а на управляющем выходе сохранится логический "0", что не приводит к изменению режима работы преобразователя: преобразователь готов к преобразованию бинарного кода в фазоманипулированный код. На входную информационную шину 1 начинает поступать информация в бинарном коде, причем на один бит информации приходятся два импульса на шине 2 удвоенной тактовой частоты. Логический уровень с входной информационной шины 1 через коммутатор 9 и элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ поступает на D-вход D-триггера 3 и по фронту первого импульса, поступающего на шину 2 тактовых импульсов удвоенной частоты, устанавливается на выходной информационной шине 5. По срезу этого импульса счетный триггер 11 переключается в единичное состояние: на его инверсном выходе устанавливается логический "0". На выходе элемента 10 ИЛИ-НЕ устанавливается логическая "1". Логический уровень с входной информационной шины 1 через коммутатор 9 поступает на второй вход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, инвертируется им и поступает далее на D-вход D-триггера 3. По фронту следующего импульса, поступающего на шину 2 тактовых импульсов удвоенной частоты, инверсия логического уровня входной информационной шины 1 устанавливается на выходной информационной шине 5. По срезу этого импульса счетный триггер 11 переключается в нулевое состояние: на его инверсном выходе устанавливается логическая "1". На выходе элемента 10 ИЛИ-НЕ устанавливается логический "0". В последующих тактовых интервалах преобразователь работает аналогично. Таким образом, на выходной информационной шине 5 формируется фазоманипулированный код.

Для передачи последующего сообщения необходимо подать стробирующий импульс (в виде логического "0") на шину 7 запрета синхросигнала и далее информацию на входную информационную шину 1 в бинарном коде.

Для передачи одиночных сообщений во втором режиме можно использовать схему формирователя синхросигнала, приведенную на фигуре 2. В этом случае при поступлении стробирующего импульса в виде логического "0" на шину 7, действующего в интервале времени не менее длительности синхросигнала, снимается удерживающий в нулевом состоянии потенциал с R-входа D-триггера 20 формирователя 8 синхросигнала. На управляющем выходе формирователя 8 синхросигнала устанавливается логическая "1", которая поступает на третий вход элемента 10 ИЛИ-НЕ, устанавливая его в нулевое состояние на время формирования синхросигнала, и на управляющий вход коммутатора 9, разрешая поступление на его выход с информационного выхода формирователя 8 синхросигнала логической "1", которая далее поступает через элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ на D-вход D-триггера 3.

По фронту импульса, поступающего на шину 2 тактовых импульсов удвоенной частоты, на выходе D-триггера 3 и соответственно на выходной информационной шине 5 преобразователя устанавливается логическая "1", а по срезам этого и последующего импульсов происходит переключение счетного триггера 11. Таким образом, последний устанавливается в нулевое состояние. На тактовом входе формирователя 8 синхросигнала формируется фронт, устанавливающий в единичное состояние D-триггер 20, на инверсном выходе которого устанавливается логический "0", поступающий через элемент 19 ИСКЛЮЧАЮЩЕЕ ИЛИ на управляющий выход формирователя 8 синхросигнала, а далее на третий вход элемента 10 ИЛИ-НЕ, на выходе которого устанавливается логическая "1", и на управляющий вход коммутатора 9, разрешая поступление на второй вход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ логических уровней входной информационной шины 1. Далее преобразователь работает аналогично режиму один.

В режиме три на шине 6 разрешения преобразования, шине 7 запрета синхросигнала установлены уровни логической "1". В этом случае на первом входе элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ фиксируется уровень логического "0". Логический уровень с входной информационной шины 1 через коммутатор 9 и элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ поступает на D-вход D-триггера 3 и по фронтам импульсов, поступающих на шину 2 тактовых импульсов удвоенной частоты, устанавливается на выходной информационной шине 5.

Для работы в режиме четыре и пять (в зависимости от реализации схемы формирователя 8 синхросигнала по схеме на фигуре 1 или схеме на фигуре 2) на шине 6 разрешения преобразования необходимо установить уровень логической "1", а на шину 7 запрета синхросигнала подавать строб синхросигнала непосредственно перед передачей информации.

Таким образом, описание работы подтверждает работоспособность заявляемого преобразователя.

Изготовлен лабораторный макет преобразователя фазоманипулированного кода в бинарный код, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

| СДВИГАЮЩИЙ РЕГИСТР | 1995 |

|

RU2105357C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 2005 |

|

RU2297096C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1997 |

|

RU2129332C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1999 |

|

RU2211529C2 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

Изобретение относится к вычислительной технике и может быть использовано в системах управления. Техническим результатом является расширение функциональных возможностей за счет обеспечения выделения момента начала поступления полезной информации. Преобразователь содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, D-триггер, формирователь синхросигнала, коммутатор, элемент ИЛИ-НЕ и счетный триггер. 2 з.п.ф-лы, 3 ил.

| КЛИМОВ В.П | |||

| и др | |||

| Кодирующие устройства оптических каналов | |||

| Сборник статей "Электронная техника в автоматике" /Под ред | |||

| Конева Ю.И | |||

| - М.: Радио и связь, 1985, с | |||

| Автоматический переключатель для пишущих световых вывесок | 1917 |

|

SU262A1 |

| Преобразователь кода | 1986 |

|

SU1332536A1 |

| ДЕКОДЕР | 1993 |

|

RU2088044C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ | 1995 |

|

RU2087072C1 |

| RU 2001520 C1, 15.10.1993 | |||

| US 4862482 A, 29.08.1989 | |||

| US 5801651 A, 01.09.1998 | |||

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

2000-11-27—Публикация

1999-03-16—Подача