Изобретение относится к вычислительной технике, а также к цифровой обработке сигналов, и может быть использовано для фильтрации действительных сигналов в радиотехнических устройствах различного назначения, в частности в радиолокации.

Целью изобретения является повышение быстродействия и упрощение фильтра при обработке действительных сигналов.

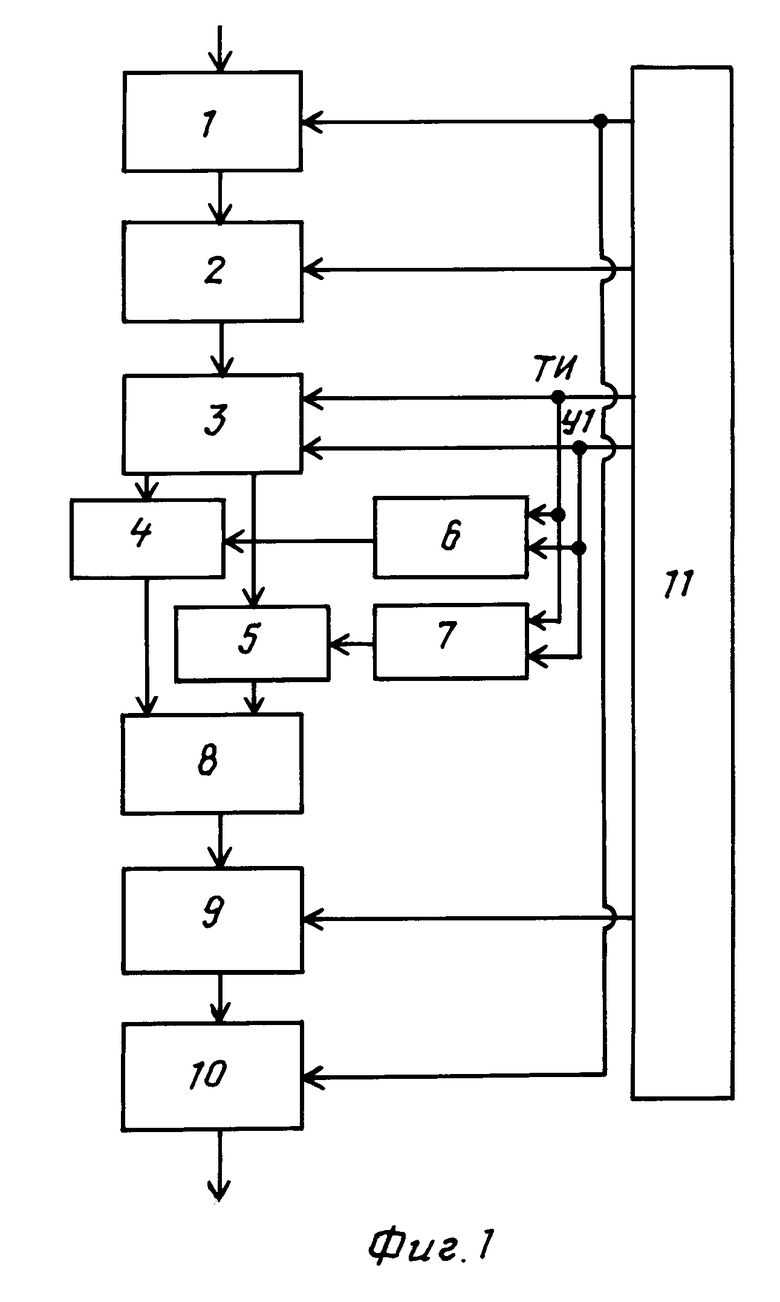

Структурная схема цифрового фильтра приведена на фиг.1.

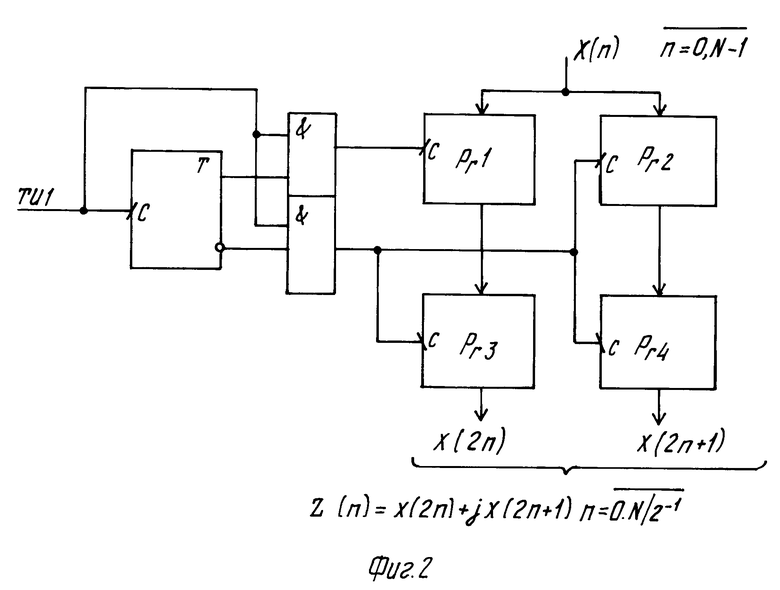

Входом фильтра является вход формирователя 1 комплексной последовательности. Формирователь 1 может быть реализован, например, на четырех регистрах, триггере и двух схемах И. Входы первого и второго регистров подключены к входу формирователя 1, выход первого регистра является входом третьего регистра, а выход второго - входом четвертого. Выходы третьего и четвертого регистров являются выходами формирователя 1, причем с третьего регистра снимается реальная часть числа, а с выхода четвертого - мнимая часть числа.

Схема формирователя 1 комплексной последовательности и временные диаграммы его работы приведены соответственно на фиг.2 и 3. Формирователь содержит триггер со счетным входом, два элемента И и четыре регистра. Триггер и два элемента И предназначены для формирования четной и нечетной последовательности импульсов из импульсов сопровождения данных ТИ1, поступающих из блока 11 синхронизации. Входные данные под управлением четной и нечетной последовательности импульсов по их передним фронтам записываются в первый и второй регистры, причем число х(n) для n=2t(t=0, N/2-1) записываются в первый регистр, а числа х(n) для n=2t+1(t=0, N/2-1) записываются во второй регистр. По задним фронтам нечетной последовательности информация с выходов первого и второго регистров перезаписывается соответственно в третий и четвертый регистры и появляется на выходе формирователя 1 в виде комплексной последовательности

Z1(n)=x(2n)+jx(2n+1), n=0, N/2-1. (1)

Регистры могут быть выполнены на микросхемах 533ТМ9, триггер - 533ТМ2, элементы И - 533ЛИ3.

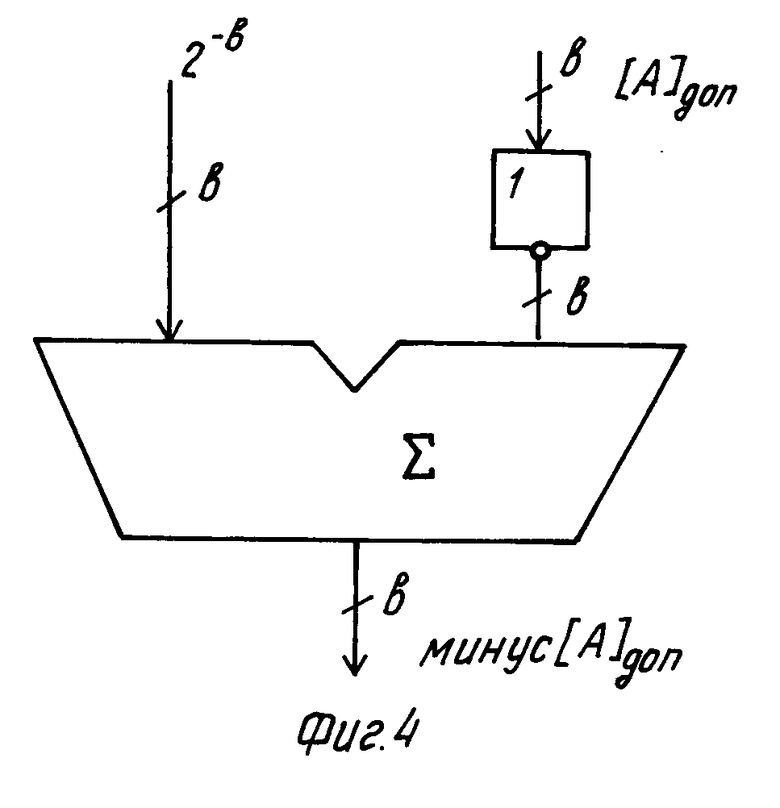

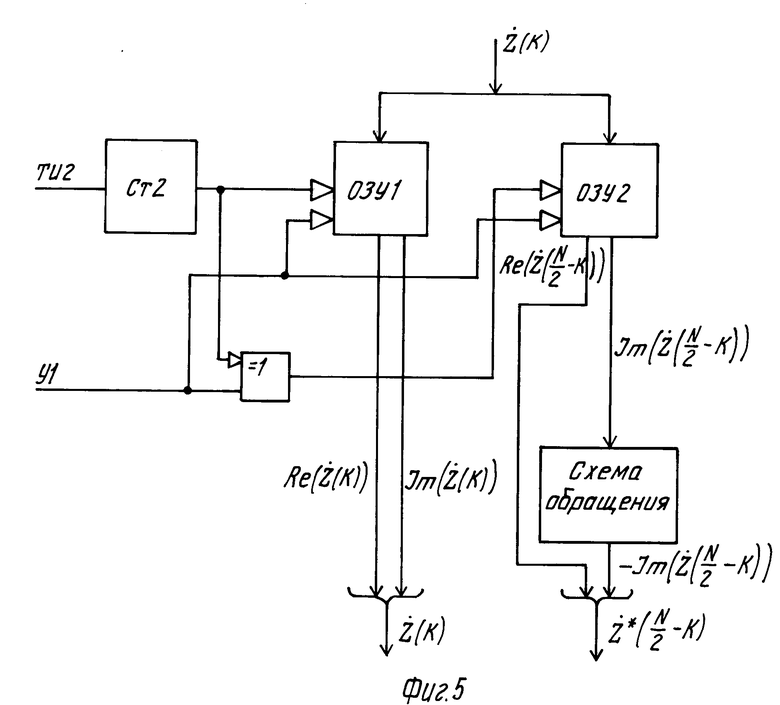

Выход формирователя 1 является входом процессора БПФ2 (Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов. Пер. с англ. М.: Мир, 1978). Выход процессора БПФ является входом формирователя 3 комплексно-сопряженной последовательности. Формирователь 30, схема которого приведена на фиг.5, может быть реализован, например, на счетчике адреса, группе управляемых инверторов, двух оперативных ЗУ-ОЗУ1 и ОЗУ2 и схемы обращения знака числа. Входы ОЗУ1 и ОЗУ2 подключены к входу формирователя 3. Вход последовательности тактовых импульсов ТИ2, поступающий из блока 11, подключен к входу счетчика адреса, выход которого подключен к адресному входу ОЗУ1 и к входу группы управляемых инверторов. К второму входу группы управляемых инверторов подключен управляющий сигнал У1, поступающий из блока 11. Управляющий сигнал У1 подается также на ОЗУ1 и ОЗУ2 в качестве сигнала записи-чтения. Выход группы управляемых инверторов подключен к адресному входу ОЗУ2. Выход ОЗУ1 является первым комплексным выходом формирователя 3. Выход ОЗУ2 является входом схемы обращения знака. Обращение знака производится только для мнимой части комплексных чисел, поступающих из ОЗУ2. Выход схемы обращения знака для мнимой части числа и выход ОЗУ2 для реальной части числа являются вторым комплексным выходом формирователя 3. Счетчик адреса содержит log2N/2 разрядов, где N - размер фильтруемого массива. Группа управляемых инверторов содержит log2N/2 двухвходовых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (например, 533ЛП5), на один из входов каждого из которых заведен управляющий сигнал У1, на другой - соответствующий разряд адреса. При У1=0 группа управляемых инверторов пропускает адрес без изменения, при У1= 1 адрес инвертируется. ОЗУ1 и ОЗУ2 одинаковы и предназначены для хранения N/2 чисел разрядности 2b каждый, причем b разрядов предназначены для хранения реальной части комплексного числа, а следующие b разрядов - для хранения мнимой части комплексного числа. Схема обращения предназначена для изменения на противоположный знак мнимой части числа, считываемого из ОЗУ2 и представленного в дополнительном коде. Как известно, для того, чтобы изменить знак числа, представленного в дополнительном коде, нужно проинвертировать все разряды этого числа и прибавить единицу в младший разряд. Поэтому схема обращения может быть построена на базе группы из b инверторов и b-разрядного параллельного сумматора. Схема этого устройства приведена на фиг.4.

Формирователь 3 комплексно-сопряженной последовательности работает следующим образом.

Запись чисел в ОЗУ1 и ОЗУ2 происходит одновременно, режим записи устанавливается сигналом У1=0. Во время записи управляющий сигнал У1 равен "0", а следовательно, группа управляемых инверторов не инвертирует адрес. Счетчик адреса в исходном состоянии установлен в "0".

На каждый тактовый импульс ТИ2 счетчик изменяет свое содержание на единицу, генерируя поток адресов 0,1,2,3...N/2-1. Таким образом, в оба ОЗУ по одним и тем же адресам записываются одинаковые числа массива комплексных чисел. В результате в оба ОЗУ записан массив Z(k), k=0, N/2-1.

Считывание чисел из ОЗУ1 и ОЗУ2 происходит также одновременно. Режим считывания устанавливается сигналом У1 ≠ 1. В этом случае на ОЗУ2 приходят инверсные значения адресов, генерируемых счетчиком: на ОЗУ1 поступают адреса 0,1,2,3...N/2-1, a на ОЗУ2 - N/2-1,N/2-2...2,1,0. Поэтому из ОЗУ1 считывается массив Z(k) и одновременно из ОЗУ2 - массив Z(N/2-k), где k=0,1,2. ..N/2-1.

Кроме этого, у мнимой части массива Z(N/2-k), считываемого из ОЗУ2, схема обращения меняет знак на противоположный, а это означает, что получается массив Z*(N/2-k), комплексно-сопряженный массиву Z(N/2-k).

Таким образом, на выходе формирователя 3 получаются два массива Z(k) и Z*(N/2-k).

ОЗУ1 и ОЗУ2 могут выполняться, например, на микросхемах 537РУ9, счетчик адреса - 533ИЕ7, группа управляемых инверторов - 533ЛП5. Построение схемы обращения знака для дополнительных кодов описано в работе Папернов А.А. Логические основы ЦВТ. М.: Сов.радио, 1972.

Первый комплексный выход формирователя 3 является одним из входов комплексного умножителя 4, второй вход умножителя 4 подключен к выходу блока 6 памяти. Второй комплексный выход формирователя 3 является одним из входов комплексного умножителя 5, второй вход умножителя 5 подключен к выходу блока 7 памяти.

Блоки 6 и 7 памяти предназначены для хранения и выдачи коэффициентов фильтра и представляет собой постоянные запоминающие устройства, работающие только в режиме считывания. Блоки 6 и 7 имеют одинаковую структуру (фиг.6). Рассмотрим структуру одного из них подробнее. Блок 6 (7) памяти содержит счетчик адреса, аналогичный счетчику адреса в формирователе комплексно-сопряженной последовательности, и ПЗУ. В исходном состоянии счетчик адреса сброшен в состояние "0" управляющим сигналом У1=0. При включении сигнала У1= 1 происходит разблокировка счетчика адреса, и он на каждый тактовый импульс ТИ2 изменяет свое состояние на единицу, генерируя поток адресов 0,1,2...N/2-1. Одновременно сигнал У1=1 разрешает выдачу информации из ПЗУ. В ПЗУ блока 6 записаны коэффициенты массива С1(k), а в ПЗУ блока 7 памяти - коэффициенты массива С2(k). Коэффициенты С1(k) и C2(k) рассчитываются заранее и записываются в соответствующие ПЗУ. Они могут выполняться, например, на микросхемах 556РТ7. Выходы блоков 6 и 7 памяти являются входами комплексных умножителей 4 и 5.

Выходы комплексных умножителей 4 и 5 являются входами комплексного сумматора 8. Его выход является входом процессора обратного БПФ 9. Структуры комплексного умножителя, комплексного сумматора и процессора обратного БПФ описаны в работе Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов. Пер. с англ. М.: Мир, 1978.

Выход процессора обратного БПФ 9 является входом формирователя 10 действительной последовательности. Формирователь 10, схема которого и временные диаграммы его работы приведены соответственно на фиг. 7 и 8, может быть реализован, например, на двух регистрах, мультиплексоре, триггере и двух схемах И. Вход первого регистра соединен с реальной частью входа, а вход второго - с мнимой частью входа формирователя 10. Выход первого регистра соединен с первым входом мультиплексора, выход второго регистра - с вторым входом мультиплексора. Выход мультиплексора является выходом формирователя 10. Триггер и схемы И предназначены для формирования последовательности нечетных импульсов из последовательности ТИ1, поступающей из блока 11.

Реальная часть массива Z2(n) подается на вход первого регистра, мнимая - на вход второго регистра. По переднему фронту нечетного импульса ТИ1, получаемого на триггере и схеме И, информация записывается в первый и второй регистры и не меняется в течение двух периодов следования ТИ1. В это время мультиплексор под управлением сигнала, снимаемого с прямого выхода триггера, выдает попеременно на выход формирователя 10 реальную и мнимую части комплексного массива Z2(n). Таким образом, на выходе формирователя 10 получается действительная последовательность чисел y(n), n=0, N-1, причем y(n)=Re(Z2(n), n=0,2...N-2; y(n)=Im(Z2(n)) для n=1,3,5...N-1. Регистры могут быть выполнены на микросхемах 533ТМ9, триггер - 533ТМ2, схема И - 533ЛИ3, мультиплексор - 533КП11.

Цифровой фильтр работает следующим образом.

Входной действительный массив данных х(n), n=0,...N-1, поступает в формирователь 1, где преобразуется в комплексный массив Z1(n), n=0,1...N/2-1, согласно формулам (1). Каждое число последовательности х(n) сопровождается импульсом сопровождения, образует тактовую серию ТИ1 блока 11 управления. В первый регистр записываются все четные числа последовательности х(n), во второй регистр - все нечетные числа той же последовательности. Запись происходит по переднему фронту импульсов сопровождения. По заднему фронту нечетного импульса сопровождения - информация из первого и второго регистров переписывается соответственно в третий и четвертый регистры. Таким образом, в третьем и четвертом регистрах формируются реальные и мнимые части комплексных элементов массива Z1(n), n=0,1...N/2-1. Частота выдачи элементов массива Z1(n) из формирователя 1 в два раза ниже, чем прием входного массива х(n). Массив Z1(n) передается в процессор БПФ2, на выходе которого получается спектр Z1(k), k=0,1...N/2-1. Спектр Z1(k) передается в формирователь 3, в котором образуются два массива Z1(k), k=0,1...N/2-1 и Z1*(N/2-k), k=0,1...N/2-1.

Приходящий на вход формирователя 3 массив Z1(k) записывается в ОЗУ1 и ОЗУ2. Адреса для записи информации формируются счетчиком адреса. Переключение счетчика происходит по тактовым импульсам сопровождения элементов массива Z1(k) ТИ2. Адреса для считывания формирует тот же счетчик, который формировал адреса для записи по импульсам ТИ2. Это возможно, так как запись и считывание информации разнесены по времени. Считывание информации из ОЗУ1 и ОЗУ2 происходит одновременно. Однако при считывании на ОЗУ2 подается инверсный адрес. Инверсия адреса производится под действием управляющего сигнала У1, который также управляет режимом записи-чтения в ОЗУ1 и ОЗУ2. В результате того, что на ОЗУ1 подается обычный, а на ОЗУ2 - инверсный адрес, на их выходах формируются массивы Z1(k) и Z1(N/2-k), k=0...N/2-1. Для формирования комплексно-сопряженного массива Z1*(N/2-k) мнимая часть массива Z1(N/2-k), считываемого из ОЗУ2, пропускается через схему обращения знака. В результате на выходе формирователя 3 под действием ТИ2 и У1 формируются два массива:

Z1(k) и Z1*(N/2-k).

В умножителях 4 и 5 происходит поэлементное умножение массивов Z1(k) и Z1*(N/2-k) на массивы С1(k) и С2(k), k=0,1...N/2-1 соответственно. Коэффициенты C1(k) и C2(k), предварительно рассчитанные, поступают из блоков 6 и 7 памяти. В сумматоре 8 происходит поэлементное суммирование результатов умножения массивов, получаемых в умножителях 4 и 5. Результатом суммирования является массив Z2(k), k=0...N/2-1. Массив Z2(k) преобразуется в процессоре обратного БПФ9 в массив Z2(n), n=0,1...N/2-1. Формирователь 10 преобразует комплексный массив Z2(n) в выходной действительный массив y(n), n= 0,1...N-1. По переднему фронту каждого четного импульса ТИ1 в формирователе 10 в первый регистр записывается реальная часть, а во второй - мнимая часть всех элементов массива. Мультиплексор работает таким образом, что в течение периода следования четных импульсов ТИ1 он попеременно подключает к своему выходу то первый, то второй вход. Таким образом, на каждый такт записи информации в регистры первые полпериода считывается реальная часть, а вторые полпериода - мнимая часть каждого элемента массива Z2(n), n=0,1...N/2-1.

В результате этого формируется массив y(n), n=0,1...N-1.

Блок 11 синхронизации формирует требуемые тактовые серии ТИ1, ТИ2 и управляющие сигналы У1, "Пуск 1", "Пуск 2" для синхронизации и правильной работы фильтра.

Тактовые импульсы ТИ1 используются для организации приема и выдачи информации в формирователях 1 и 10. ТИ1 поступает непрерывно в течение всего времени работы предлагаемого фильтра. Тактовые импульсы ТИ2 подаются в моменты приема и выдачи информации в формирователь 3. Сигналы "Пуск 1" и "Пуск 2" запускают в работу процессоры БПФ2 и обратного БПФ9 после того, как они приняли для обработки массивы Z1(n) и Z2(n). Управляющий сигнал У1 принимает значение логической "1" только в момент выдачи информации из формирователя 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАРНО-РАЗНОСТНЫЙ УГЛОВОЙ ДИСКРИМИНАТОР | 1991 |

|

RU2012015C1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1282156A1 |

| Устройство для контроля программно-логических матриц | 1987 |

|

SU1469504A1 |

| УСТРОЙСТВО СОРТИРОВКИ СИМВОЛОВ | 1992 |

|

RU2067317C1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных гиперкубических циклических системах | 2019 |

|

RU2718166C1 |

| КОСМИЧЕСКИЙ РАДИОЛОКАТОР С СИНТЕЗИРОВАННОЙ АПЕРТУРОЙ, ФОРМИРУЮЩИЙ ИЗОБРАЖЕНИЕ В РЕАЛЬНОМ ВРЕМЕНИ | 1999 |

|

RU2158008C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1987 |

|

SU1425708A1 |

Изобретение относится к цифровой обработке сигналов и может быть использовано для фильтрации действительных сигналов в радиотехнических устройствах различного назначения, в частности в радиолокации. Целью изобретения является повышение быстродействия и упрощение фильтра. Цифровой фильтр содержит формирователь 1 комплексной последовательности, процессор 2 быстрого преобразования Фурье, формирователь 3 комплексно-сопряженной последовательности, умножители 4, 5, блоки 6, 7 постоянной памяти коэффициентов, сумматор 8, процессор 9 обратного преобразователя Фурье, формирователь 10 действительной последовательности. 8 ил.

ЦИФРОВОЙ ФИЛЬТР, содержащий два умножителя, сумматор, блок синхронизации, первый блок постоянной памяти коэффициентов, первый выход которого соединен с первым информационным входом первого умножителя, выход которого соединен с первым информационным входом сумматора, отличающийся тем, что фильтр дополнительно содержит формирователь комплексной последовательности, процессор быстрого преобразования Фурье, формирователь комплексно-сопряженной последовательности, второй блок постоянной памяти коэффициентов, процессор обратного преобразования Фурье, формирователь действительной последовательности, выход которого является выходом фильтра, информационный вход фильтра соединен с информационным входом формирователя комплексной последовательности, выход которого соединен с информационным входом процессора быстрого преобразования Фурье, выход которого соединен с информационным входом формирователя комплексно-сопряженной последовательности, первый и второй выходы которого соединены с вторым и первым информационными входами первого и второго умножителей соответственно, выход второго блока постоянной памяти коэффициентов соединен с вторым информационным входом второго умножителя, выход которого соединен с вторым информационным входом сумматора, выход которого соединен с информационным входом процессора обратного преобразования Фурье, выход которого соединен с информационным входом формирователя действительной последовательности, первый выход блока синхронизации соединен с синхровходами формирователя комплексной последовательности и формирователя действительной последовательности, второй выход блока синхронизации соединен с синхровходом процессора быстрого преобразования Фурье, третий выход - с синхровходами формирователя комплексно-сопряженной последовательности и первого и второго блоков постоянной памяти коэффициентов, входы разрешения считывания которых соединены с управляющим входом формирователя комплексно-сопряженной последовательности и четвертым выходом блока синхронизации соответственно, пятый выход которого соединен с синхровходом процессора обратного преобразования Фурье.

| Рекурсивный цифровой фильтр | 1989 |

|

SU1640711A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-02-20—Публикация

1991-07-30—Подача