Изобретение относится к технике радиолокации и может быть использовано в радиолокационных системах для обнаружения и сопровождения по координатам подвижных целей.

Известен фазовый суммарно-разностный моноимпульсный угломер (Леонов А. И. , Фомичев К. И. Моноимпульсная радиолокация. М. : Радио и связь, 1984). Устройство содержит моноимпульсный антенный датчик, суммарно-разностный волноводный мост, смесители суммарного и разностного сигналов, гетеродин, фазовращатель на π/2, усилитель промежуточной частоты суммарного сигнала и усилитель промежуточной частоты разностного сигнала, а также блок автоматической регулировки усиления и фазовый детектор (ФД).

Недостатком такого угломера является то, что напряжение на выходе ФД пропорционально не только направлению на цель, но и косинусу разности набега фаз в суммарном и разностном каналах, что ведет к существенной ошибке в определении направления на объект.

Известно также угломерное устройство, свободное от этого недостатка. Устройство содержит моноимпульсный антенный датчик, смеситель, гетеродин, два предварительных усилителя промежуточной частоты, ключевую схему, устройство стробирования, сравнивающее устройство.

Однако такое устройство обладает повышенной чувствительностью к неидентичности приемных каналов до их объединения и пониженной разрешающей способностью по дальности, кроме того, аппаратурная реализация устройства достаточно сложна.

Наиболее близким по технической сущности к предложенному устройству является оптимальное решающее устройство моноимпульсного пеленгатора (Свиридов Э. Ф. Сравнительная эффективность моноимпульсных радиолокационных систем пеленгования. - М. : Судостроение, 1964, с. 71, рис. 16а). При выполнении в цифровом виде это устройство будет содержать последовательно соединенные первый аналого-цифровой преобразователь (АЦП) и первый цифровой оптимальный фильтр, выход которого подключен к первому входу делителя; последовательно соединенные второй АЦП и второй цифровой оптимальный фильтр, выход которого подключен к второму входу делителя, и постоянное запоминающее устройство (ПЗУ), в котором записаны предварительно рассчитанные значения функции y = arctg x.

Работа устройства заключается в следующем. После оптимальной фильтрации в суммарном и разностном каналах производится вычисление пеленгационной характеристики S(θ) в делителе путем деления сигнала на выходе оптимального фильтра разностного канала на сигнал на выходе оптимального фильтра суммарного канала. С помощью ПЗУ определяются величины, пропорциональные arctg S(θ). Выход ПЗУ является выходом устройства.

Недостатком этого угломера является то, что определение направления на объект θ производится с существенной ошибкой. Это обусловлено тем, что пеленгационная характеристика оказывается пропорциональна не только тангенсу направления на объект, но и косинусу разности набега фаз в суммарном и разностном каналах.

Целью изобретения является повышение точности измерения угловой координаты.

Это достигается тем, что в известное устройство, содержащее последовательно соединенные первый АЦП и первый процессор дискретного преобразования Фурье (ДПФ), выходы действительных и мнимых частей которого подключены соответственно к первому входу действительных чисел и первому входу мнимых чисел первого делителя, последовательно соединенные второй АЦП и второй процессор ДПФ, выходы действительных и мнимых чисел которого подключены соответственно к второму входу действительных чисел и второму входу мнимых чисел первого делителя, и ПЗУ, введены второй делитель и формирователь модуля знака, причем первый и второй входы действительных чисел первого делителя соединены соответственно с первым и вторым входами действительных чисел второго делителя, первый и второй входы мнимых чисел первого делителя подключены соответственно к первому и второму входам мнимых чисел второго делителя, выход которого соединен с первым входом формирователя модуля и знака, второй вход которого подключен к выходу первого делителя, а выход формирователя модуля и знака соединен с входом ПЗУ, выход которого является выходом устройства.

Проведенный сопоставительный анализ прототипа и предложенного устройства позволил выявить новые отличительные признаки у заявляемого технического решения: второй делитель, формирователь модуля и знака с соответствующими связями, что указывает на наличие критерия "новизна".

Предложенное устройство соответствует также критерию "существенные отличия", поскольку не обнаружено решений с признаками, отличающими его от прототипа.

Сущность изобретения заключается в следующем.

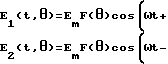

Пусть сигналы E1(t, θ ) и E2(t, θ) на выходах соответственно первой и второй антенн моноимпульсного датчика описываются соотношениями:

(1) где F(Q) - коэффициент усиления антенны;

(1) где F(Q) - коэффициент усиления антенны;

Em - амплитуда;

ω - частота поля;

Δϕ - фазовый сдвиг из-за разности путей прохождения сигнала от цели до антенны, определяемый равенством (Леонов А. И. , Фомичев К. И. Моноимпульсная радиолокация. - М. : 1984, с. 7).

Δϕ =  =

=  , где λ- длина волны;

, где λ- длина волны;

l - расстояние между фазовыми центрами антенн;

θ - азимут цели относительно равносигнального направления;

θ0,5 - ширина диаграммы направленности антенны по уровню половинной мощности.

После преобразования по частоте и усиления в своем УПЧ суммарный сигнал Uc( ωo, t, θ) поступает на вход АЦП1 (см. фиг. 1). Этот сигнал можно описывать соотношением

Uc(ωo, t, θ) = KcEmF(θ) cos

cos t+

t+  +

+  +cos

+cos t-

t-  +

+  =

=

= M1cos(ωot+γc), где M1= 2KcEmF(θ)cos  ;

;

ωo - частота сигнала после преобразования;

γc и Kc - соответственно фазовый набег и коэффициент усиления сигнала в суммарном канале.

После преобразования по частоте и усиления в своем УПЧ разностный сигнал Up( ωo, t, θ) можно описать соотношением:

Up(ωo, t, θ) = KpEmF(θ) cos

cos t+

t+  +

+  -cos

-cos t-

t-  +

+  =

=

= M2cos(ωot+γp), где M2= -2KpEmF(θ)sin  ;

;

γp и Kp - соответственно фазовый набег и коэффициент усиления сигнала в разностном канале.

Для использования в качестве оптимальных фильтров - цифровых согласованных фильтров, аналоговые сигналы суммарного и разностного каналов в АЦП1 и АЦП2 преобразуются в цифровую форму. В цифровой форме суммарный и разностный сигналы могут быть описаны соотношениями:

Uc(ko, n, θ) = M1cos kon+

kon+ ,

,

Up(ko, n, θ) = M2cos kon+

kon+ , где ko - номер спектрального коэффициента, соответствующего частоте входного сигнала;

, где ko - номер спектрального коэффициента, соответствующего частоте входного сигнала;

n - дискретная переменная по времени.

Известно (Кузьмин С. З. "Основы проектирования цифровой обработки радиолокационной информации". М. - 1986, с. 103), что для радиоимпульсов с прямоугольной огибающей операция дискретного преобразования Фурье является операцией согласованной (оптимальной) фильтрации.

Процессор ДПФ суммарного канала осуществляет преобразование Фурье суммарного сигнала в соответствии с соотношением (k)= M

(k)= M cos

cos kon+

kon+ e

e =

=

=

e

e

+

+  e

e

e

e

=

=

=  e

e

e

e

+ e

+ e

e

e

=

=

=

e

e (I1+jI2)+e

(I1+jI2)+e (I3+γI4)

(I3+γI4) , (2) где

, (2) где  (k) - сигнал на выходе процессора ДПФ суммарного канала;

(k) - сигнал на выходе процессора ДПФ суммарного канала;

I1=  cos

cos  (k-ko)n, I2=

(k-ko)n, I2=  sin

sin  (k-ko)n,

(k-ko)n,

I3=  cos

cos  (k+ko)n, I4=

(k+ko)n, I4=  sin

sin  (k+ko)n,

(k+ko)n,

k - дискретная переменная по частоте.

Нетрудно заметить, что /

/

(3)

(3)

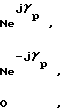

В результате для Sc(k) окончательно получим (k)=

(k)=

Процессор ДПФ разностного канала осуществляет преобразование Фурье разностного сигнала в соответствии с соотношением

Sp(k)= M cos

cos  kon+

kon+ e

e

. (4)

. (4)

Проделав те же выкладки, что и для суммарного сигнала, можно убедиться, что на выходе процессора ДПФ разностного сигнала формируется сигнал  (k), который можно описать соотношением

(k), который можно описать соотношением =

=

(5)

(5)

Зададимся значением k = ko, т. е. выберем спектральные коэффициенты на выходах ДПФ1 и ДПФ2, соответствующие частоте входного сигнала, и определим величины А и В на выходах делителей.

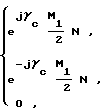

Перепишем соотношения для Sp(ko) и Sc(ko) в алгебраической форме: (ko)= a+jb;

(ko)= a+jb;  (ko)= c+jd, (6) где a=

(ko)= c+jd, (6) где a=  Ncosγp - соответствует выходу действительных чисел процессора ДПФ 3;

Ncosγp - соответствует выходу действительных чисел процессора ДПФ 3;

b=  Nsinγp - соответствует выходу мнимых чисел процессора ДПФ 3;

Nsinγp - соответствует выходу мнимых чисел процессора ДПФ 3;

c=  Ncosγc - соответствует выходу действительных чисел процессора ДПФ 4;

Ncosγc - соответствует выходу действительных чисел процессора ДПФ 4;

d=  Nsinγc - соответствует выходу мнимых чисел процессора ДПФ 4.

Nsinγc - соответствует выходу мнимых чисел процессора ДПФ 4.

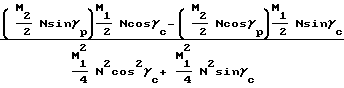

В делителе 5 вычисляется число A, определяемое соотношением

A=  = ReUg. (7)

= ReUg. (7)

В делителе 6 вычисляется число В, определяемое соотношением

B= =

= . (8)

. (8)

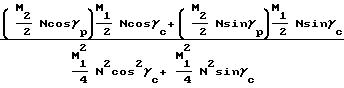

Из соотношений (6), (7), (8), предполагая, что Kp = Kc получим

A=  =

=

=

cosγpcosγc+sinγpsin

cosγpcosγc+sinγpsin =

=  -tg

-tg

cos

cos -

- , (9)

, (9)

B=  =

=

=  -tg

-tg

sin

sin  -

- . (10)

. (10)

Далее число A поступает на 1-й вход (Вх1) формирователя модуля и знака (ФМЗ), а число В - на 2-й вход (Вх2) ФМЗ.

В ФМЗ выполняются стандартные операции извлечения корня квадратного из суммы квадратов чисел A и В. Результату этих действий присваивается знак числа, поступающего на первый вход (Вх1) ФМЗ.

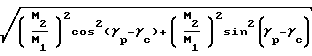

В результате на выходе ФМЗ определяется число Z1, для которого справедливо соотношение

Z1= (signA) = _

= _

= -  = -tg

= -tg  . (11) Далее Z1 поступает в ПЗУ 8, где записано число Z2, заранее вычисленное в соответствии с соотношением

. (11) Далее Z1 поступает в ПЗУ 8, где записано число Z2, заранее вычисленное в соответствии с соотношением

Ζ2= -  arctg Z1= -

arctg Z1= -  arctg

arctg -tg

-tg

= θ. (12)

= θ. (12)

Таким образом, если в устройстве выполнить описанные операции, то на выходе устройства получим величину, которая прямо пропорциональна направлению на цель и не зависит от неидентичности фазовых характеристик суммарного и разностного каналов.

Анализ соотношений (9) и (11) показывает, что соотношение (9) для A совпадает с описанием пеленгационной характеристики S( θ) прототипа. Соотношение (11) описывает пеленгационную характеристику S(θ) предлагаемого устройства.

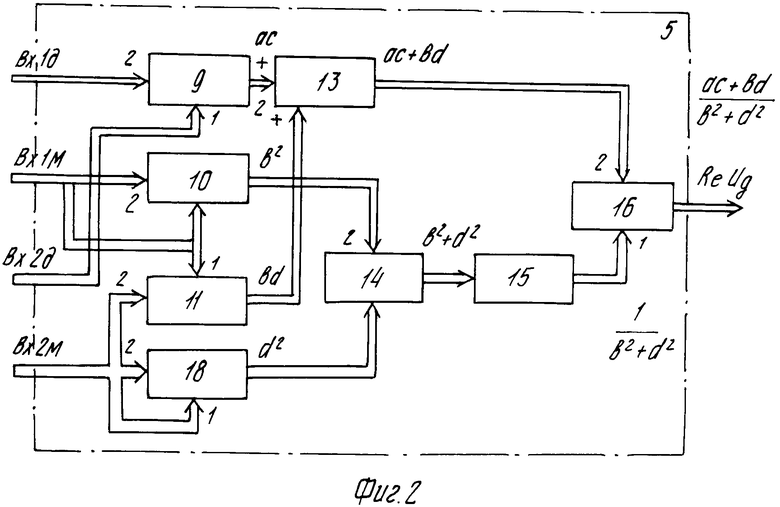

На фиг. 1 изображена структурная схема устройства, работающего по описанному алгоритму.

Устройство содержит последовательно соединенные первый АЦП 1 и первый процессор ДПФ 3, последовательно соединенные второй АЦП 2 и второй процессор ДПФ 4, а также первый делитель 5 и второй делитель 6, формирователь модуля и знака 7, ПЗУ 8. Выход действительных чисел "a" первого процессора ДПФ 3 одновременно подключен к первому входу Вх. 1д действительных чисел первого делителя 5 и первому входу Вх. 1д действительных чисел второго делителя 6. Выходы действительных чисел "с" второго процессора ДПФ второго процессора ДПФ 4 одновременно подключен к второму входу Вх. 2д действительных чисел первого делителя 5 и ко второму входу Вх. 2д действительных чисел второго делителя 6.

Выход мнимых чисел b первого процессора ДПФ 3 одновременно соединен с первым входом Вх. 1м мнимых чисел первого делителя 5 и первым входом Вх. 1м мнимых чисел второго делителя 6. Выход мнимых чисел d второго ДПФ 4 одновременно соединен с вторым входом Вх. 2м мнимых чисел первого делителя 5 и вторым входом Вх. 2м мнимых чисел второго делителя 6.

Выход первого делителя 5 соединен с первым входом Вх1 формирователя модуля и знака 7. Выход второго делителя 6 подключен к второму входу Вх2 формирователя модуля и знака. Выход формирователя модуля и знака 7 подключен к входу ПЗУ 8, выход которого является выходом устройства.

Устройство, реализующее суммарно-разностный дискриминатор, может быть выполнено в виде специализированного процессора цифровой обработки сигналов. В этом процессора АЦП может быть использован стандартный, например, типа К1107ПВ4. Процессоры ДПФ могут быть выполнены на базе серийных микросхем 1815ВФ3. Л. Рабинер и Б. Голд. Теория и применение цифровой обработки сигналов, с. 422, фиг. 6.16.

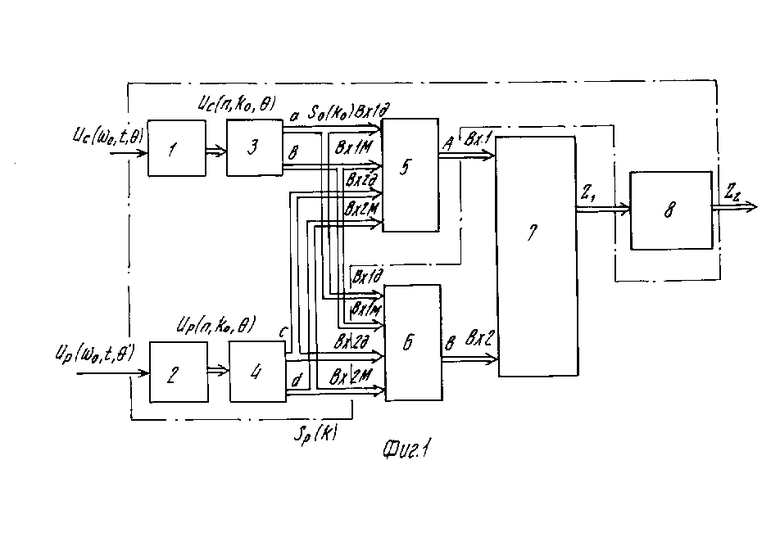

Делители 5 и 6 реализуют стандартную операцию деления двух комплексных чисел. Пример возможной реализации делителя 5 представлен на фиг. 2.

Делитель 5 содержит пять умножителей 9, 10, 11, 12, 16, два сумматора 13 и 14, а также ПЗУ 15.

Первый вход действительных чисел Вх1д делителя 5 соединен с вторым входом умножителя 9, выход которого соединен с вторым входом сумматора 13. Выход сумматора 13 соединен с вторым входом умножителя 16, выход которого является выходом делителя 5. Первый вход сумматора 13 соединен с выходом умножителя 11, второй вход которого одновременно соединен с первым и вторым входами умножителя 12 и вторым входом Вх. 2м мнимых чисел делителя 5. Выход умножителя 12 соединен с первым входом сумматора 14, выход которого соединен с входом ПЗУ 15. Выход ПЗУ 15 соединен с первым входом умножителя 16. Второй вход Вх. 2д действительных чисел делителя 5 соединен с первым входом умножителя 9. Первый вход Вх. 1м мнимых чисел делителя 5 одновременно соединен с вторым входом умножителя 10 и первыми входами умножителя 10 и 11, а выход умножителя 10 соединен с вторым входом сумматора 14. Умножители могут быть реализованы на стандартных микросхемах, например, типа 1802 ВР5, сумматор может быть - на стандартных микросхемах типа К1802 ИМ1, ПЗУ - например, на микросхеме 556 РТ7.

Пример возможной реализации делителя 6 представлен на фиг. 3. Делитель содержит 5 умножителей 17, 18, 19, 20, 24, два сумматора 21, 22, а также ПЗУ 23.

Первый вход Вх. 1д действительных чисел делителя 6 соединен с первым входом умножителя 19, второй вход которого одновременно соединен с вторым входом мнимых чисел Вх. 2м и первым и вторым входами умножителя 20, выход которого соединен с вторым входом сумматора 22. Первый вход сумматора 22 соединен с выходом умножителя 18. Выход сумматора 22 соединен с входом ПЗУ 22, выход которого соединен с первым входом умножителя 24, выход которого является выходом делителя 6. Первый вход Вх. 1м мнимых чисел делителя 6 соединен с вторым входом умножителя 17, выход которого соединен с вторым входом сумматора 21. Выход сумматора 21 соединен с вторым входом умножителя 24. Первый вход сумматора 21 соединен с выходом умножителя 19. Второй вход Вх. 2д действительных чисел делителя 6 одновременно соединен с вторым входом умножителя 18 и первыми входами умножителей 17 и 18. Делитель 6 может быть реализован на такой же элементной базе, как и делитель 5.

Формирователь модуля и знака реализует стандартную операцию взятия модуля комплексного числа, причем выходным значениям присваивается знак действительной части комплексного числа.

Пример возможной реализации формирователя модуля и знака представлен на фиг. 4. Формирователь модуля и знака содержит два умножителя 25 и 26, сумматор 27, ПЗУ 28 и регистр 29.

Первый вход Вх1 формирователя одновременно соединен с первым и вторым входами умножителя 25, выход которого соединен с вторым входом сумматора 27. Второй вход Вх2 формирователя одновременно соединен с вторым и первым входами умножителя 26, выход которого соединен с первым входом сумматора 27. Выход сумматора 27 соединен с входом ПЗУ 28, выход которого соединен с входом Вх4 регистра 29, выход которого является выходом формирователя. Знаковая шина первого входа Вх1 формирователя соединена с входом знака Вх. зн регистра 29.

Формирователь модуля и знака может быть реализован на стандартных микросхемах. Например, умножители 25 и 26 могут быть реализованы на микросхемах типа 1802ВР5. Сумматор может быть реализован на микросхеме 1802 ИМ1, регистр 29 - на микросхеме К 1802 ИР1.

Работа суммарно-разностного углового дискриминатора в соответствии со структурной схемой может быть описана следующим образом.

Аналоговый сигнал Uc( ωo , t, θ ) суммарного канала поступает на вход АЦП 1 и преобразуется в цифровую форму Uc(n, ko, θ). В процессоре ДПФ 3 определяется комплексный спектральный коэффициент сигнала суммарного канала. Далее действительная часть "a" этого спектрального коэффициента одновременно подается на первый вход Вх. 1д действительных чисел делителя 5 и 1-й вход Вх. 1д действительных чисел делителя 6. Мнимая же часть b комплексного спектрального коэффициента сигнала суммарного канала одновременно подается на первый вход Вх. 1м мнимых чисел делителя 5 и первый вход Вх. 1м мнимых чисел делителя 6.

Аналоговый сигнал Up(ωo , t, θ ) разностного канала поступает на вход АЦП 2 и преобразуется в цифровую форму Up(n, ko, θ). В процессоре ДПФ 4 определяется комплексный спектральный коэффициент Sp(ko) сигнала разностного канала. Далее действительная часть "с" этого спектрального коэффициента одновременно подается на второй вход Вх. 2д действительных чисел делителя 5 и 2-й вход Вх. 2д действительных чисел делителя 6. Мнимая же часть d комплексного спектрального коэффициента сигнала разностного канала одновременно подается на второй вход Вх2м мнимых чисел делителя 5 и второй вход Вх. 2м мнимых чисел делителя 6.

В результате в делителе 5 вычисляется действительная часть ReUд, а в делитель 6 - мнимая часть ImUд результата деления комплексного спектрального коэффициента разностного канала на комплексный спектральный коэффициент суммарного канала.

Далее сигнал с выхода делителя 5 поступает на первый вход Вх1 формирователя модуля и знака, а сигнал с выхода делителя 6 поступает на его второй вход Вх2.

В формирователе модуля и знака 7 вычисляют значения пеленгационной характеристики предлагаемого устройства, совпадающие по знаку с сигналами на первом входе формирователя. Сигналы с выхода формиpователя модуля и знака поступают в ПЗУ 8. В ПЗУ 8 записаны предварительно рассчитанные значения функции arctg Z2. Когда поступают на адресный вход ПЗУ значения Z2, они являются адресами ячеек, в которых записаны значения arctg Z2, и которые и выдаются на выход ПЗУ 8. В результате на выходе ПЗУ 8, а значит и всего устройства формируются величины, пропорциональные направлению на объект.

Делитель 5 работает следующим образом. С первого входа Вх. 1д действительных чисел на 2-й вход умножителя 9 поступает действительная часть "a" спектрального коэффициента суммарного канала. На 1-й вход умножителя 9 с второго входа Вх. 2д действительных чисел поступает часть "с" специального коэффициента разностного канала. С выхода умножителя 9 результат умножения "a" на "с" поступает на 2-й вход сумматора 13.

С первого входа Вх. 1м мнимых чисел на 2-й и 1-й входы умножителя 10 и 1-й вход умножителя 11 поступает мнимая часть b спектрального коэффициента суммарного канала. Одновременно с 2-го Вх. 2м мнимых чисел поступает мнимая часть d комплексного отчета разностного сигнала на второй вход умножителя 11, 2-й и 1-й входы умножителя 12. В результате на выходе умножителя 11 формируется произведение b на d, которое поступает на 1-й вход сумматора 13. На выходе умножителя 12 формируется квадрат числа d, который поступает на 1-й вход сумматора 14. На выходе умножителя 10 формируется квадрат числа b, который поступает на 2-й вход сумматора 14.

В результате на выходе сумматора 13 формируется число, соответствующее ac + bd, которое поступает на 2-й вход умножителя 16. На выходе сумматора 14 формируется число, соответствующее b2 + d2, которое поступает на адресный вход ПЗУ 15. На выход ПЗУ 15 считываются заранее вычисленные значения, равные 1/b2 + 1/d2, которые поступают на 1-й вход умножителя 16. В результате на выходе умножителя 16, т. е. на выходе делителя 5 формируется число  , равное действительной части ReUдрезультата деления комплексных спектральных коэффициентов разностного и суммарного каналов.

, равное действительной части ReUдрезультата деления комплексных спектральных коэффициентов разностного и суммарного каналов.

Делитель 6 работает аналогично. В результате на выходе делителя формируется число  , равное мнимой части ImUд результата деления спектральных коэффициентов разностного и суммарного каналов.

, равное мнимой части ImUд результата деления спектральных коэффициентов разностного и суммарного каналов.

Формирователь модуля и знака 7 работает следующим образом. С первого входа Вх1 формирователя на 1-й и 2-й входы умножителя 25 поступает число ReUд, равное действительной части результата деления спектральных коэффициентов. На выходе умножителя 25 формируется число, равное квадрату входной величины, т. е. (ReUд)2, которое поступает на 2-й вход сумматора 27.

С второго входа Вх2 формирователя на 1-й и 2-й входы умножителя 26 поступает число ImUд, равное мнимой части результата деления спектральных коэффициентов. На входе умножителя 26 формируется число, равное квадрату входной величины, т. е. (ImUд)2, которое поступает на 1-й вход сумматора 27. С выхода сумматора 27 сумма (ReUд)2 + (ImUд)2поступает на адресный вход ПЗУ 28. На выход ПЗУ 28 считываются заранее вычисленные числа, равные корню квадратному из подкоренного выражения. Далее значащие числа выхода ПЗУ 28 поступают на вход регистра 28. Кроме того, одновременно со знаковой шины первого входа Вх1 в знаковую часть регистра записывается знак числа, поступающего на 1-й вход формирователя.

В результате в регистре формируется число, соответствующее координате объекта.

Была проведена оценка эффективности предлагаемого устройства. В качестве базового варианта был выбран прототип. Оценка θn угловой координаты в прототипе в соответствии с алгоритмом его работы и формулами (9)

θп= +  arctg

arctg tg

tg

cos

cos -

- (13)

(13)

Оценка θy угловой координаты в предлагаемом устройстве определяется в соответствии с соотношением (12)

θy= θ. (14)

Относительная погрешность вычислений δ определялась в соответствии с известным соотношением

δ =  · 100% (15)

· 100% (15)

Практические исследования показали, что разность набега фаз ( γp-γc) достигает 30о. По соотношениям (13), (14), (15) в качестве примера для значений θ0,5= 6о, θ= 1о, γp-γc = 30о было определено, что θy = 1о, θn= 0,88о, а δ ≃ 12% .

Таким образом, предлагаемое устройство позволяет существенно повысить точность измеpения угловой координаты.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| СПОСОБ РАДИОПЕЛЕНГОВАНИЯ И РАДИОПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2015 |

|

RU2598648C1 |

| СПОСОБ РАДИОПЕЛЕНГОВАНИЯ И РАДИОПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2303274C1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДОПЛЕРОВСКОЙ ОБРАБОТКИ КВАДРАТУРНЫХ ИМПУЛЬСНЫХ ВИДЕОСИГНАЛОВ | 1997 |

|

RU2155970C2 |

| Устройство для измерения относительной задержки импульсных сигналов | 1982 |

|

SU1068886A1 |

| СПОСОБ ПЕЛЕНГАЦИИ РАДИОСИГНАЛОВ И ПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2201599C1 |

| УСТРОЙСТВО ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ В ИМПУЛЬСНО-ДОПЛЕРОВСКОЙ РЛС С КОМПЕНСАЦИЕЙ ЧМ ДОПЛЕРОВСКИХ СИГНАЛОВ | 2017 |

|

RU2657462C1 |

| СПОСОБ ОБНАРУЖЕНИЯ ИСТОЧНИКОВ ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ В ПРЕДЕЛАХ КОНТРОЛИРУЕМОЙ ЗОНЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2206101C1 |

| УСТРОЙСТВО ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ В ИМПУЛЬСНО-ДОПЛЕРОВСКОЙ РЛС С КОМПЕНСАЦИЕЙ ЧМ ДОПЛЕРОВСКИХ СИГНАЛОВ ЗА ОДИН ПЕРИОД ИЗЛУЧЕНИЯ И ПРИЕМА ПАЧКИ РАДИОИМПУЛЬСОВ | 2021 |

|

RU2782574C1 |

Сущность изобретения: суммарно-разностный угловой дискриминатор содержит два аналого-цифровых преобразователя 1, 2, два процессора дискретного преобразования Фурье 3, 4, два делителя 5, 6, один формирователь модуля и знака 7 и один постоянный запоминающий блок. 1-3-5-7-8, 2-4-6-8, 3-6, 4-5. 4 ил.

СУММАРНО-РАЗНОСТНЫЙ УГЛОВОЙ ДИСКРИМИНАТОР, содержащий последовательно соединенные первый аналого-цифровой преобразователь и первый процессор дискретного преобразования Фурье (ДПФ), выходы сигналов действительных и мнимых чисел которого подключены соответственно к первому входу сигналов действительных чисел и к первому входу сигналов мнимых чисел первого делителя, последовательно соединенные второй аналого-цифровой преобразователь и второй процессор ДПФ, выходы сигналов действительных и мнимых чисел которого подключены соответственно к второму входу сигналов действительных чисел и второму входу сигналов мнимых чисел первого делителя, постоянный запоминающий блок, отличающийся тем, что введены второй делитель и формирователь модуля и знака, первый и второй входы сигналов действительных чисел первого делителя соединены соответственно с первым и вторым входами сигналов действительных чисел второго делителя, первый и второй входы сигналов мнимых чисел первого делителя подключены соответственно к первому и второму входам сигналов мнимых чисел второго делителя, выходы первого и второго делителей соединены с входами формирователя модуля и знака, выход которого соединен с входом постоянного запоминающего блока, выход которого является выходом углового дискриминатора.

Авторы

Даты

1994-04-30—Публикация

1991-07-11—Подача