арифметического блока, вход управления вычитанием которого подключен выходу первого элемента НЕ, вход «6торого соединен с шестым выходом блока управления, седьмой и восьмой выходы которого соединены соответственно с вторыми и третьими входами третьего и четвертого элементов 2 ИИЛИ, четвертые входы которых подключены к выходам мнимых частей соответственно первого и второго операндов арифметического блока, девятый и десятый выходы блока управления подключены к вторым входам соответственно первого и BTOpo.ro сумматоров по модулю 2, одиннадцатый выход блока управления соединен с управляющим входом первого блока памяти и входом второго элемента НЕ, выход которого подключен к управляющему входу второго блока памяти, двенадцатый и тринадцатый выходы блока управления соединены с входами задания адреса соответственно второго и третьего формирователей адреса, выходы переполнения которых .подключены соответственно к первому и второму входам блока управления, четырнадцатьп выход которого подключен к входу задания приращения адреса первого и второго формирователей адреса, пятнадцатый выход блока управления является выходом информации выдачи проц сора, а третий и четвертый входы блока управления, являются соответственно тактовым входом и входом синхронизации приема процессора.

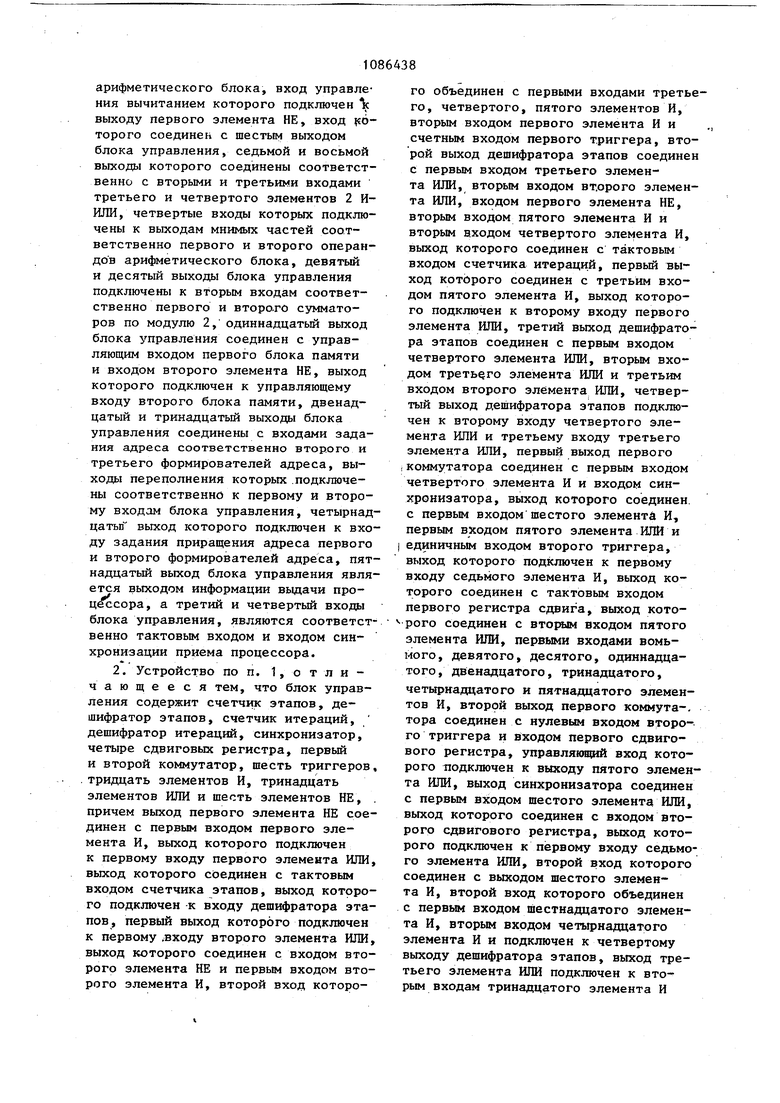

2. Устройство по п. 1, о т л и чающееся тем, что блок управления содержит счетчик этапов, дешифратор этапов, счетчик итераций, дешифратор итераций, синхронизатор, четыре сдвиговых регистра, первый и второй коммутатор, шесть триггеров, тридцать элементов И, тринадцать элементов ИЛИ и шесть элементов НЕ, . причем выход первого элемента НЕ соеинен с первым входом первого элеента И, выход которого подключен к первому входу первого элемента ИЛИ, ыход которого соединен с тактовым ходом счетчика этапов, выход которого подключен к входу дешифратора этаов, первый выход которого подключен первому .входу второго элемента ИЛИ, ыход которого соединен с входом второго элемента НЕ и первым входом второго элемента И, второй вход которого объединен с первыми входами третьего, четвертого, пятого элементов И, вторым входом первого элемента И и счетным входом первого триггера, второй выход дешифратора этапов соединен с первым входом третьего элемента ИЛИ, вторым входом второго элемента ИЛИ, входом первого элемента НЕ, вторым входом пятого элемента И и вторым входом четвертого элемента И, выход которого соединен с тактовым входом счетчика итераций, первый выход которого соединен с третьим входом пятого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, третий выход дешифратора этапов соединен с первым входом четвертого элемента ИЛИ, вторым входом третьего элемента ИЛИ и третьим входом второго элемента ИЛИ, четвертый выход дешифратора этапов подключен к второму входу четвертого элемента ИЛИ и третьему входу третьего элемента ИЛИ, первый выход первого

коммутатора соединен с первым входом четвертого элемента И и входом синхронизатора, выход которого соединен, с первым входом шестого элемента И, первым входом пятого элемента ИЛИ и

единичным входом второго триггера, выход которого подключен к первому входу седьмого элемента И, выход которого соединен с тактовым входом первого регистра сдвига, выход которого соединен с вторым входом пятого элемента ИЛИ, первыми входами вомьмого, девятого, десятого, одиннадцатого, двенадцатого, тринадцатого,

четырнадцатого и пятнадцатого элементов И, второй выход первого коммута-. тора соединен с нулевым входом второго триггера и входом первого сдвигового регистра, управляющий вход которого подключен к выходу пятого элемента ИЛИ, выход синхронизатора соединен с первым входом шестого элемента ИЛИ, выход которого соединен с входом второго сдвигового регистра, выход которого подключен к первому входу седьмого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, второй вход которого объединен с первым входом шестнадцатого элемента И, вторым входом четырнадцатого элемента И и подключен к четвертому выходу дешифратора этапов, выход третьего элемента ИЛИ подключен к вторым входам тринадцатого элемента И

и восьмого элемента И, выход которого соединен со счетным входом третьего триггера, единичный выход которого подключен к первым входам семнадцато го, восемнадцатого элементов И, вторым входом десятого, одиннадцатого, пятнадцатого, шестнадцатого элементов И и третьему входу четырнадцатого элемента И, выходы второго и третьего элементов И соединены соответственно с, единичным и нулевым входами третьего триггера, нулевой выход которого подключен к второму входу девятого элементами и третьему входу тринадцатого элемента И, выход которого соединен с первьм входом восьмого элемента ИЛИ, второй вход которого является четвертым входом блока управления, второй выход дешифратора этапов соединен с вторьм входом восемнадцатого элемента И и третьим входом девятого элемента И, выход которого подключен к первому входу девятого элемента ИЛИ, второй вход которого соединен с выходом десятого элемента И, третий вход которого соединен с вторым входом семнадцатого элемента И, первым входом первого коммутатора и подключен к выходу четвертого элемента ИЛИ, пятый выход дешифратора этапов соединен с вторым входом двенадцатого элемента И, йыход которого соединен с третьим входом девятого элемента ИЛИ и является пятнадцатым выходом блока управления, выходы семнадцатого, восемнадцатого элементов И и девятого элемента ИЛИ соединены соответственно с первым, вторым и третьим входами второго коммутатора, первый и второй выходы которого являются соответственно двенадцатым и тринадцатым выходами блока управления, первьй выход дешифратора этапов является третьим выходом блока управления и подключен к входу третьего элемента НЕ, выход которого соединен с первым входом девятнадцатого элемента И, второй вход которого подключен к выходу четвертого элемента НЕ, вход которого соединен с выходом шестнадцатого элемента И, выход которого является вторым выходом блока управления, а выход девятнадцатого элемента И является первым выходом блока управления, третий выход первого коммутатора соединен с единичным входом четвертого триггера, единичный выход которого подключен к третьему входу пятнадцатого элемента И, выход которого соединен с нулевым входом четвертого триггера и вторым входом шестого элемента ИЛИ, третий вход которого соединен с выходом четырнадцатого элемента И, управляющие входы синхронизатора, второго сдвигового регистра и второй вход седьмого элемента И объед1Й1ены и являются третьим входом блока управления, выход восьмого элемента ИЛИ соединен с вторым входом первого коммутатора и входом третьего сдвигового регистра, выход которого подключен к первому входу десятого элемента ИЛ и единичному входу пятого триггера, единичньй выход которого соединен с первым входом двадцатого элемента И, выход которого подключен к тактовому входу четвертого сдвигового регистра выход которого подключен к третьему входу первого коммутатора и первым входом двадцать первого, двадцать второго, двадцать третьего и двадцат четвертого элементов И, первый выход первого коммутатора соединен с нулевым входом пятого триггера и управЛЯЮ1ДИМ входом четвертого сдвигового регистра, вход которого подключен к выходу десятого элемента ИЛИ, второй вход которого объединен с первыми входами двадцать пятого, двадцать шестого, двадцать седьмого, двадцать восьмого, двадцать девятого элементов И, вторым входом двадцать третьего элемента И и подключен к единичному вьпсоду шестого триггера и обраэует восьмой выход блока управления, нулевбй выход шестого триггера подключен к первому входу тридцатого элемента И, впх;рому входу двадцать второго элемента И и является седьмым выходом блока управления, выход третьего элемента ИЛИ соединен с вторым входом двадцать четвертого элемента И, выход которого подключен к счетному входу шестого триггера, единичный и нулевой входы которого соединены с выходами соответственно второго и третьего элементов И, второй выход дешифратора этапов соединен с вторыми входами двадцать пятого, тридцатого и двадцать шестого элементов И, первый выход дешифратора итераций соединен с третьим входом двадцать пятого и тридцатого элемеп- .тов И, входом пятого элемента НЕ, выход которого подключен к третьему входу двадцать шестого элемента И, выход которого соединен с первым входом одиннадцатого элемента ИЛИ, второй вход которого объединен с первым входом двенадцатого элемента ИЛИ и подключен к выходу двадцать пятого элемента И, выход тридцатого элемента И, соединен с вторым входом двенадцатого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к второму входу двадцать седьмого элемента И, третьему входу двадцать третьего элемента И и входу шестого элемента НЕ, выход которого подключен к третьему входу двадцать второго элемента И, выход которого подключен к первому входу тринадцатрго элемента ИЛИ, второй вход которого соединен с выходом двадцать третьего элемента И, третий выход дешифратора итераций является шестым выходом блока управления и соединен с вторым входом двадцать восьмого элемента И, выход которого является девятым выходом блока управления, четвертый выход дешифратора этапов подключен к второму входу двадцать девятого элемента И, выход которого является десятым выходом блока управления, выходы одиннадцатого, двенадцатого

и тринадцатого элементов ИЛИ и выход двадцать седьмого элемента И соединены соответственно с четвертым, пятым, шестым и седьмым входом второго коммутатора, второй выход двадцатого элемента И и тактовый вход третьего сдвигового регистра объединены и об разуют третий вход блока управления, первый, второй, третий и четвертый выходы дешифратора итерации являются четырнадцатым выходом блока управления, выход первого триггера соединен с четнертЬм входом первого коммутатора и восьмым входом второго коммутатора и является одиннадцатым выходом блока управления, первый выход дешифратора этапов является третьим выхо, дом блока зшравления, выхода четвертого и седьмого элементов ИЛИ являют;ся четвертым выходом блока управления выход одиннадцатого элемента И, выходы второго и третьего сдвиговых регистров и выход восьмого элемента ИЙИ образуют пятьШ выход блока управления а пятый и шестой входы первого коммутатора являются соответственно первым и вторым входами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1987 |

|

SU1411777A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для вычисления скользящего спектра | 1981 |

|

SU1027733A1 |

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

1. ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНР1Я .ФУРЬЕ, содержащий арифметический блок, первый и второй локи памяти, блок постоянной Памяти,блок управления, три формирователя адреса, два элемента И и два элемента PfflH, причем выходы первого и второго элементов И соединены с первыми входами соответственно первого и второго элементов ИЛИ, выходы которых подключены соответственно к первому и второму-входу операндов арифметического блока, входы действительной и мнимой части коэффициентов которого соединены соответственно с первым и вторым выходами блока постоянной памяти, вход которого соединен с выходом первого формирователя адреса, выходы второго и третьего формирователей адреса соединены с адресными входами соответственно первого и второго блоков памяти, первые и вторые выходы которых соответственно объединены и являются соответственно первым и вторым информационными выходами процессора, а первые входы первого и второго элементов И являются соответственно первым и вторым информационными входами процессора, отличающийся тем, что, с целью повышения быстродействия процессора, он содержит первый, второй, третий и четвертый элементы 2 И-ИЛИ, первый и второй сумматоры по модулю 2, первый и второй элементы НЕ, причём первый выход блока управления соединен с первыми входами первого и второго элементов 2 И-ИЛИ, выходы которых подключены к вторым входам соответственно первого и второго элементов ИШ, второй выход блока управления подключен к вторым входам первого и второго Элементов 2 И-ИЛИ, третьи и четвер(Л тые входы которых подключены соответственно к первому и второму выходам первого блока памяти, третий выход блока управления соединен с вторыми входами первого и второго элементов И, четвертый выход блока уп- равления подключен к входу первого 00 формирователя адреса, пятый выход блока управления соединен с входом 4 управления приемом информации арифметического блока, выходы действиСО тельной части первого и третьего 00 операндов которого соединены с первыми входами соо ветственно третьего и четвертого элементов 2 И-ИЛИ, выхо ды которых подключены к первым входам соответственно первого и второго сумматоров по модулю 2, выходы которых подключены соответственно к первым и вторым информационным входам первого и второго блоков памяти, шестой выход блока управления соединен с входом управления суммированием

Изобретение относится к области вычислительной техники и может быть использовано для решения задач цифровой обработки сигналов.

Известно устройство для вычислеНИН коэффициентов Фурье, в котором быстродействие повьш1ается эа счет совмещения вычислений. Устройство содержит блоки умножения, суммирующие блоки, регистры действительной и мнимой частей весового коэффициента С11.

Несмотря на применение четырех множительных блоков и одновременное выполнение операций умножеиия, сложения и вычитания, устройство отличается сравнительно небольшим быстродейст вием, так как результаты вычислений оказываются записанными в те же ре-, гистры, куда записываются исходные данные. Поэтому вычислительное устройство не может начать обработку следующих операндов до тех пор, пок4

ранее вычисленные результаты не будут переписаны в ОЗУ.

Наиболее близким техническим решением к изобретению является устройство для вычисления коэффициентов Фурье, содержащее блоки умножения, суммирующие блоки, регистры действительной и мнимой частей входных операндов, регистры действительной и мнимой частей весового коэффициента, регистры действительной и мнимой частей выходных операндов, а также промежуточные регистры, обеспечиванщие повышение быстродействия вычислений за счет совмещения работы блоков умножения и суммирующих блоков С2.

К недостаткам данного устройства следует отнести относительно небольшое быстродействие при вычислении коэффициентов Фурье от действительной последовательности входных данных; кроме того, реализуемая в нем орга- низация вычислений коэффициентов Фурье от действительной последовательности требует значительных объемов опйративной памяти. Цель изобретения - повышение быст родействия и упрощение устройства. Поставленная цель достигается тем, что в процессор, содержащий арифметический блок, первый и второй блоки памяти, блок постоянной памяти блок управления, три формирователя адреса, два элемента И и два элемента ИЛИ, причем выходы первого и второго элементов И соединены с первыми входами соответственно первого и вто рого элементов ИЛИ, выходы которых подключены соответственно к первому и второму входу операндов арифметического блока, входы действительной и мнимой части коэффициентов котарого соединены соответственно с первым и вторым выходами блока постоянной памяти, вход которого соединен с выходом первого формирователя адреса, выходы второго и третьего формирователей адреса соединены с адресными входами соответственно первого ;и ;вто рого блоков памяти, первые и вторые выходы которых соответственно объеди нены и являются соответственно первым и вторым информационными выходами процессора, а первые входал первого и второго элементов И являются соответственно первым и вторым инфор мационными входами процессора, содер жит первый, второй, третий и четвертый элементы 2 И-ИЛИ, первый и второ сумматоры по модулю 2, первый и второй элементы НЕ, причем первый выход блока управления соединен с первыми входами первого и второго элементов 2 И-ИЛИ, выходы которых подключены к вторым входам соответственно первого и второго элементов ИЛИ, вто рой выход блока управления подключен к вторьт входам первого и второго элементов 2 И-ШШ, третьи и четверты входы которых подключены соответственно к .первому и второму выходам перового блока памяти, третий выход блока управления соединен с вторыми входами первого и второго элементов И, четвертый выход блока управле ния подключен к входу первого формирователя адреса, пятьй выход блока управления соединен с входом управления приемом информации арифметичес кого блока, выходы действительной части первого и третьего операндов которого соединены с первыми входами соответственно третьего и четвертого элементов 2 И-ИЛИ, выходы которых подключены к первым входам соответст-. венно первого и второго сумматоров по модулю 2, выходы которых подключены соответственно к первым и вторым информационным входам первого и второго блоков памяти, шестой выход блока управления соединен с входом управления суммированием арифметического блока, вход управления вычитанием которого подключен к выходу первого элемента НЕ, вход которого соединен с шестым выходом блока управления, седьмой и восьмой выходы которого соединены соответственно с вторыми и третьими входами третьего и четвертого элементов 2 И-ИЛИ, четвертые входы которых подключены к выходам мнимых частей соответственно первого и второго операндов арифметического блока, девятый и десятый выходы блока управления подключены к вторым входам соответственно первого и второго сумматоров по модулю 2, одиннадцатый выход блока управления соединен с управляющим входом первого блока памяти и входом второго элемента НЕ, выход которого подключен к управляющему входу второго блока памяти, двенадцатый и тринадцатый выходы блока управления соединены с входами задания адреса соответственно второго и третьего формирователей адреса, выходы переполнения которых подключены соответственно к первому и второму входам блока управления, четырнадцатый выход которого подключен к входу заданий приращения адреса первого и второго формирователей адреса, пятнадцатьй выход блока управления является выходом информации выдачи процессора, а третий и четвертый входы блока управления, являются соответственно тактовым входом и входом синхронизации приема процессора. Блок управления соДержит счетчик этапов, дешифратор этапов, счетчик итераций, дешифратор итераций, синхронизатор, четыре сдвиговых регистра, первый и второй коммутаторы, шесть триггеров, тридцать элементов И, тринадцать элементов ИЛИ и шесть элементов НЕ, причем выход первого элемента НЕ соединен с первым входом первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход которого соединен с тактовым входом счетчика этапов, выход которого подключен к входу дешифратора этапов, первый выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с входом второго элемента НЕ и первым и входом второго элемента И второй вход которого объединен с первыми входами третьего, четвертого, пятого элементов И, вторым входом первого элемента И и счетным входом первого триггера, второй выход дешифратора этапов соединен с первым входом третьего элемента ИЛИ, вторым входом второго элемента ЩИ, входом первого элемента НЕ, вторым входом пятого элемента И и вторым входом четвертого элемента И, выход которого соединен с тактовым входом счетчика итераций, выход которого соединен с третьим входом пятого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, третий выход дешифратора этапов соединен с пёрвь м входом четвертого элемента ИЛИ, вторьм входом третьего элементА ИЛИ и третьим входом рторото элемента ИЛИ, четвертьй выход дешифратора этапов подключен к второму входу четвертого элемента ИЛИ и третьему входу третьего элемента ИЛИ, первый выход первого коммутатора соединен с первым входом четвертого элемента И и входом синхронизатора, выход которого соединен с перв1 1м входом шестого элемента И первым входом пятого элемента ИЛИ и единичным входом второго триггера, выход которого подключен к первому входу седьмого элемента И, выход которого соединен с тактовым входом первого регистра сдвига, выход которого соединен с вторым входом пятого элемента РШИ, первыми входами восьмого, девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого и пятнадцатого элементов Ивторой выход первого коммутатора соединен с нулевым входом второго триггера и входом первого сдвигового регистра, управляющий вход которого подключен к выходу Пятого элемента ИЛИ, выход синхронизатора соединен с первым входом шестого элемента ИЛИ, выход которого соединен с входом второго сдвигового регистра, выход которого подключен к первому входу седьмого элемента ИЛИ, второй вход которого соединен с выходом

шестого элемента И, второй вход которого объединен с первым входом шестнадцатого элемента И, вторым входом четырнадцатого элемента И и подключен к четвертому выходу дешифратора этапов, выход третьего элемента ИЛИ подключен к вторым входам тринадцатого элемента И и восьмого элемента И, выход которого соединен со счетным входом третьего триггера, единичный выход которого подключен к первым входам семнадцатого, восемнадцатого элементов И, вторым входом десятого, одиннадцатого, пятнадцатого, шестнадцатого элементов И и третьему входу четырнадцатого элемента И, выходы второго и третьего элементов И соединены соответственно с единичным и нулевым входами третьего триггера, нулевой выход которого подключен к второму входу девятого элемента И и к третьему входу тринадцатого элемента И, выход которого соединен с первым входом восьмого элемента ИЛИ, второй вход которого является четвертым входом блока управления, второй выход дешифратора этапов соединен с втором входом восемнадцатого элемента И и третьим входом девятого элемента И, выход которого подключен к первому входу девятого элемента ИЛИ, второй вход которого соединен с выходом десятого элемента И, третий вход которого объединен с вторым входом семнадцатого элемента И, первым входом первого коммутатора и подключен к выходу четвертого элемента И1Ш, пятый вьпсод дешифратора этапов соединен с вторам входом двенадцатого элемента И, выход которого соединен с третьим входом девятого элемента ИЛИ и является пятнадцатым выходом блока управления, выходы семнадцатого, восемнадцатого элементов И и девятого элемента ШШ соединены соответственно с первым, вторым и третьим входами второго коммутатора, первый и второй выходы которого являются соответственно двенадцатым и тринадцатым выходами блока управления, первый выход дешифратора этапов является третьим выходом блока управления и подключён к входу третьего элемента НЕ, выход которого соединен с первым входом девятнадцатого элемента И,, второй вход которого подключен к выходу четвертого элеменха И, второй вход которого подключен к выходу четвертого элемента НЕ, вход которюго соединен с выходом шестнадцатого элемента И, выход которого является вторым выходом блока управления, а выход девятнадцатого элемента И является первым выходом блока управления, третий выход первого коммутатора соединен с единичным входом четвертого триггера, единичный выход которого подключен к третьему входу пятнадцатого элемента И, выход которого соединен с нулевым входом четвертого триггера и вторым входом шестого элемента ИЛИ, третий вход которого соединен с выходом четырнадцатого элемента И,управляющие входы синхронизатора, второго сдвигового регистра и второй вход седьмого элемента И объединены и являются третьим входом блока управления, вьлсод восьмого элемента ИЛИ соединен с вто1ЯФ1 входом первого коммутатора и входом третьего сдвигового регистра, выход которого подключен к первому входу десятого элемента ИЛИ и единичному входу пятого триггера, единичный выход которого соединен с первым входо двадцатого элемента И, выход которого подключен к тактовому входу четвертого сдвигового регистра, выход которого подключен к третьему входу первого коммутатора и первым входом двадцать первого, двадцать второго, двадцать третьего и двадцать четвертого элементов И, первый выход пер-вого коммутатора соединен с нулевым входом пятого триггера и управляющим входом четвертого сдвигового регистра, вход которого подключен к выходу десятого элемента ИЛИ, второй вход которого соединен с первыми BJto дами двадцать пятого, двадцать шесто го, двадцать седьмого, двадцать вось мого, двадцать девятого элементов И, вторым входом двадцать третьего элемента И и подключен к единичному выходу шестого триггера и образует восьмой выход блока управления, нуле

вой вьщод шестого триггера подключен к первому входу тридцатого элемента И, второму входу двадцать второго элемента И и является седьмым выходом блока управления, выход третьего элемента ИЛИ соединен с вторым входом двадцать четвертого элемента И, выход которого подключен к счетному входу шестого триггера, единичный и нулевой входы которого соединены с выходами соответственно второго и третьего элементов И, второй выход дешифратора этапов соединен с вторыт 10

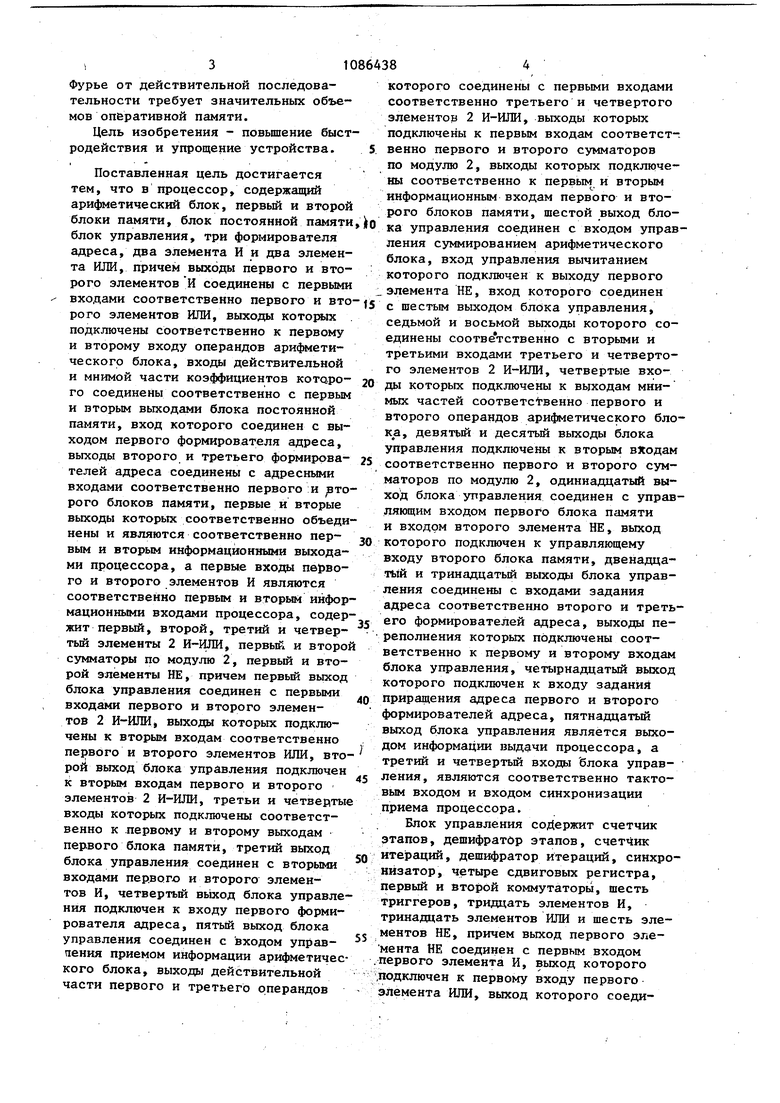

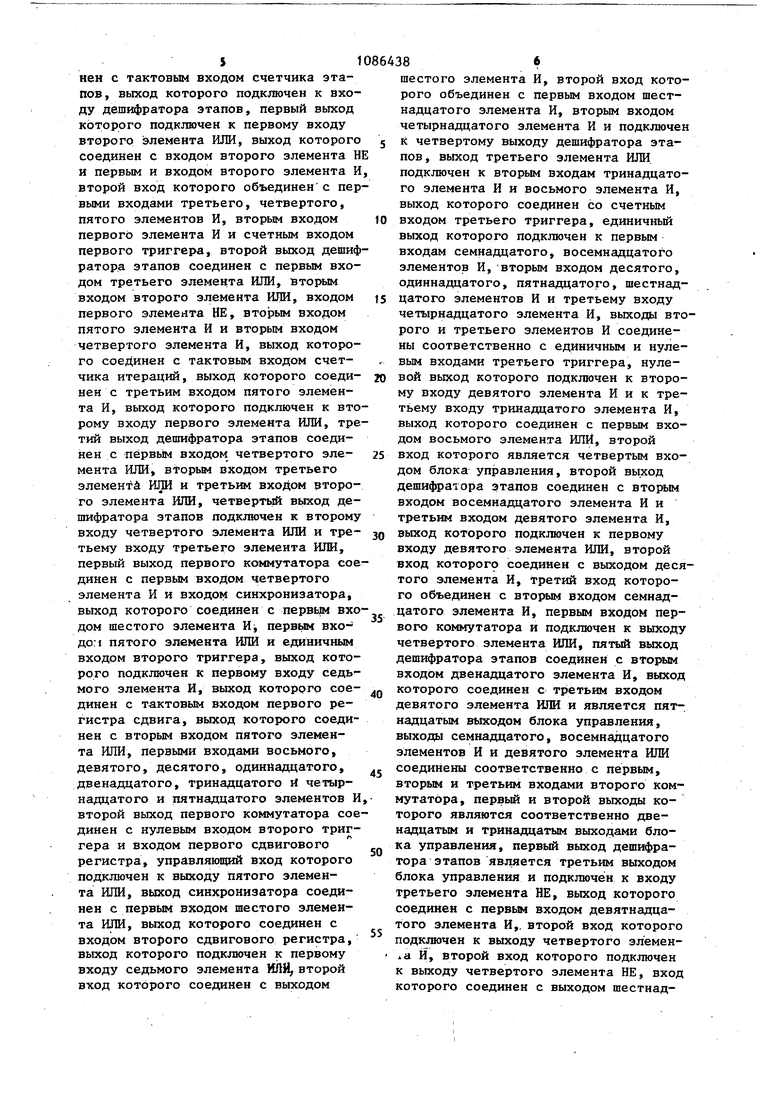

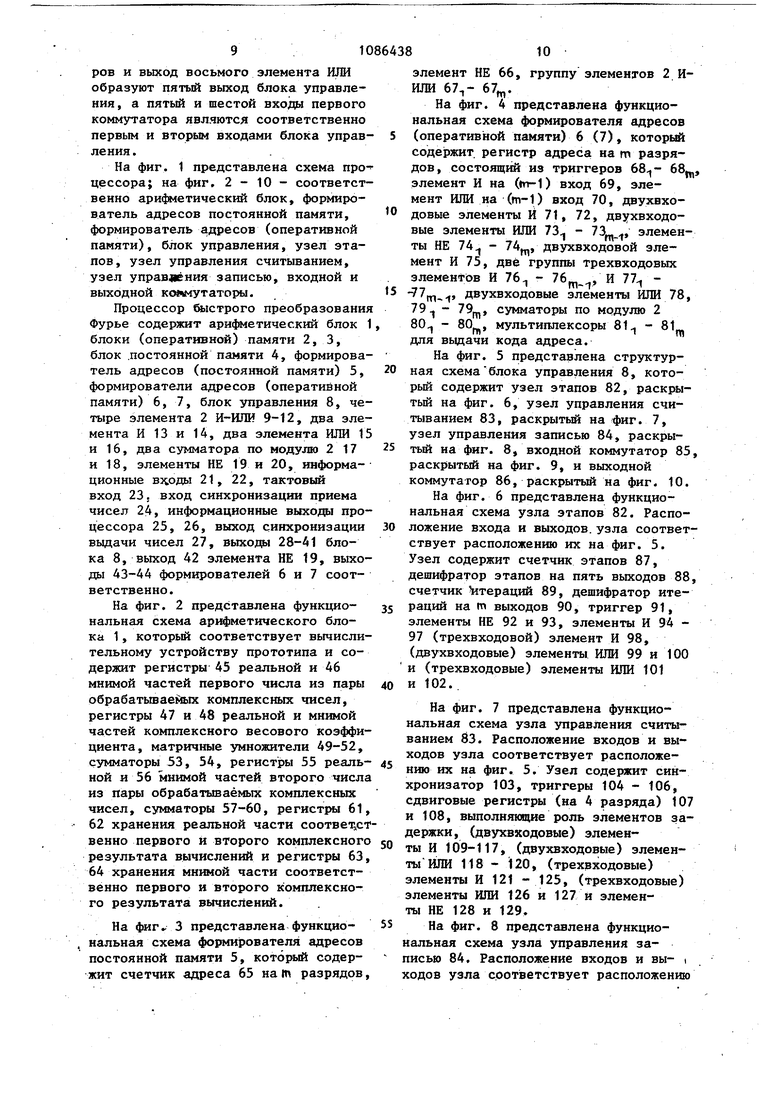

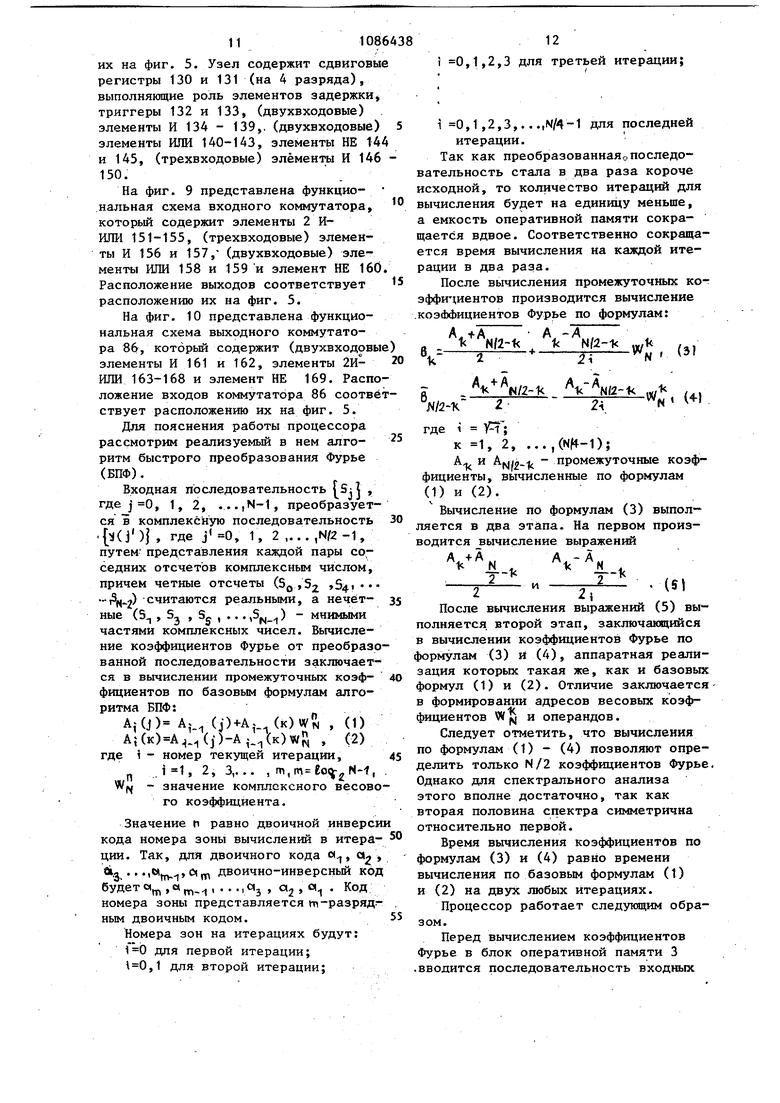

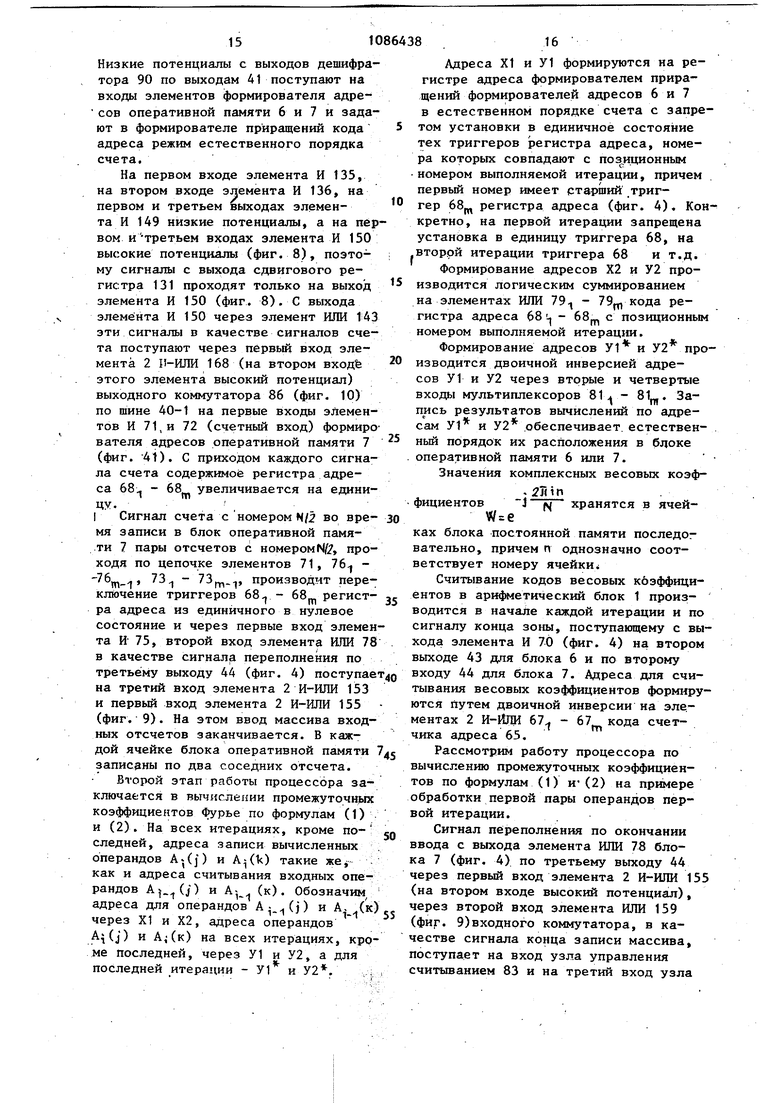

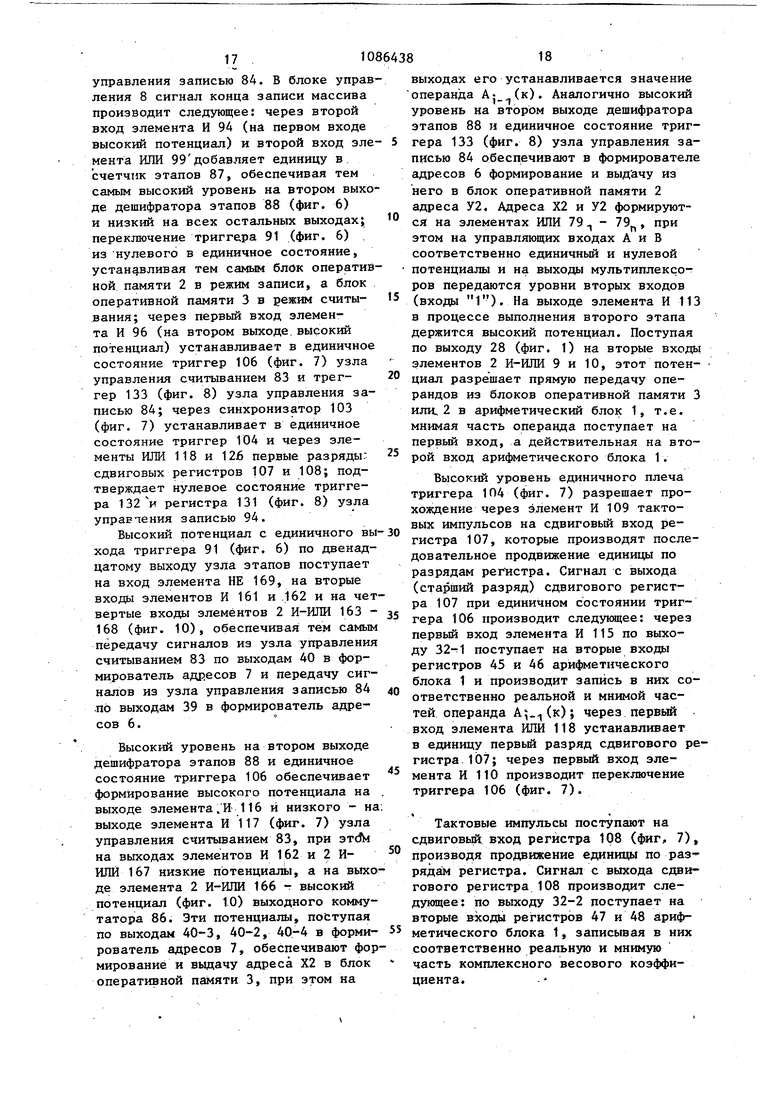

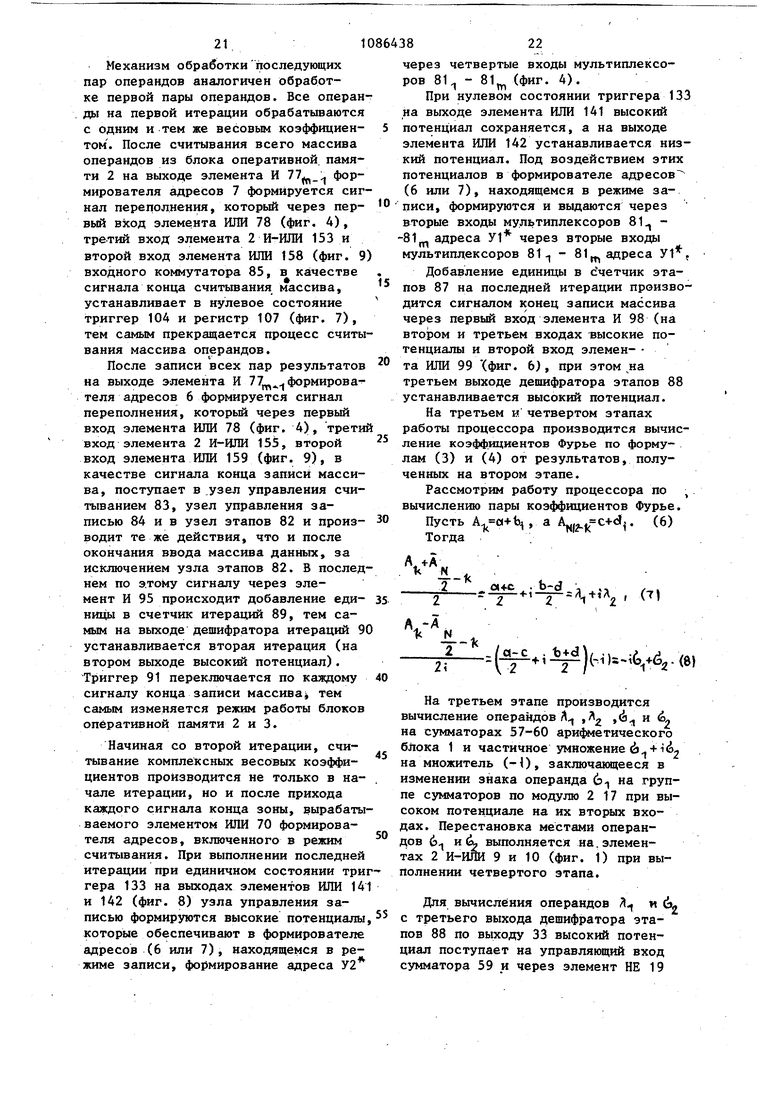

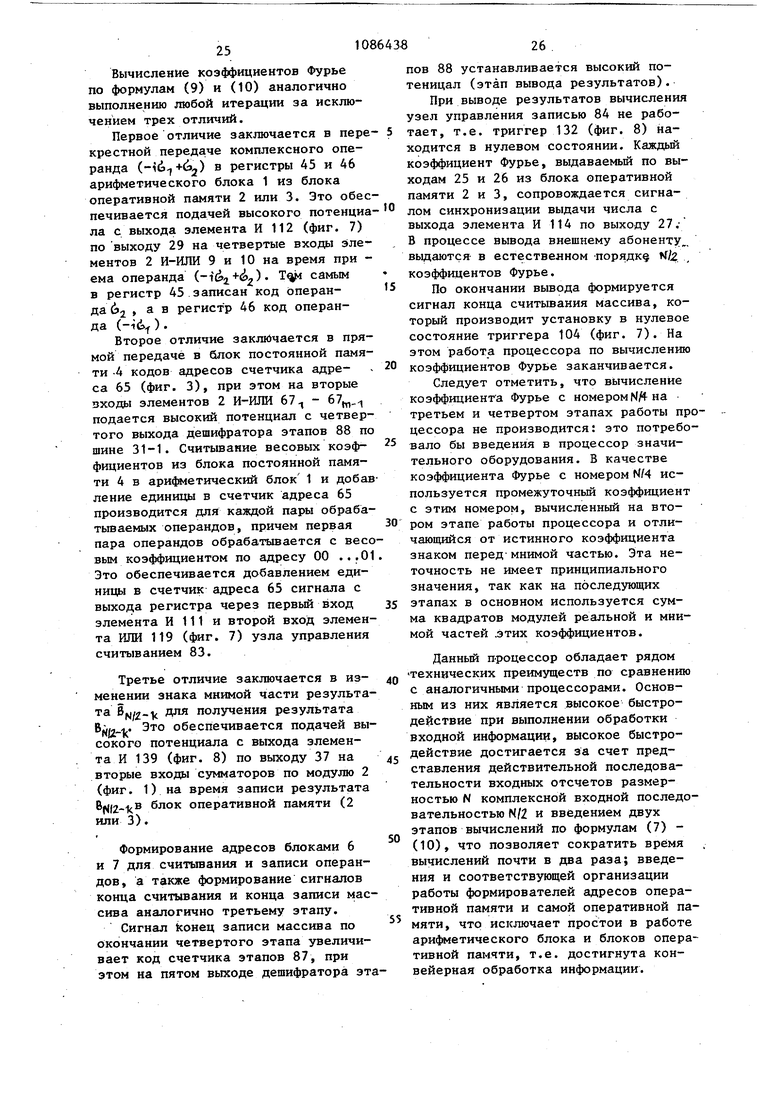

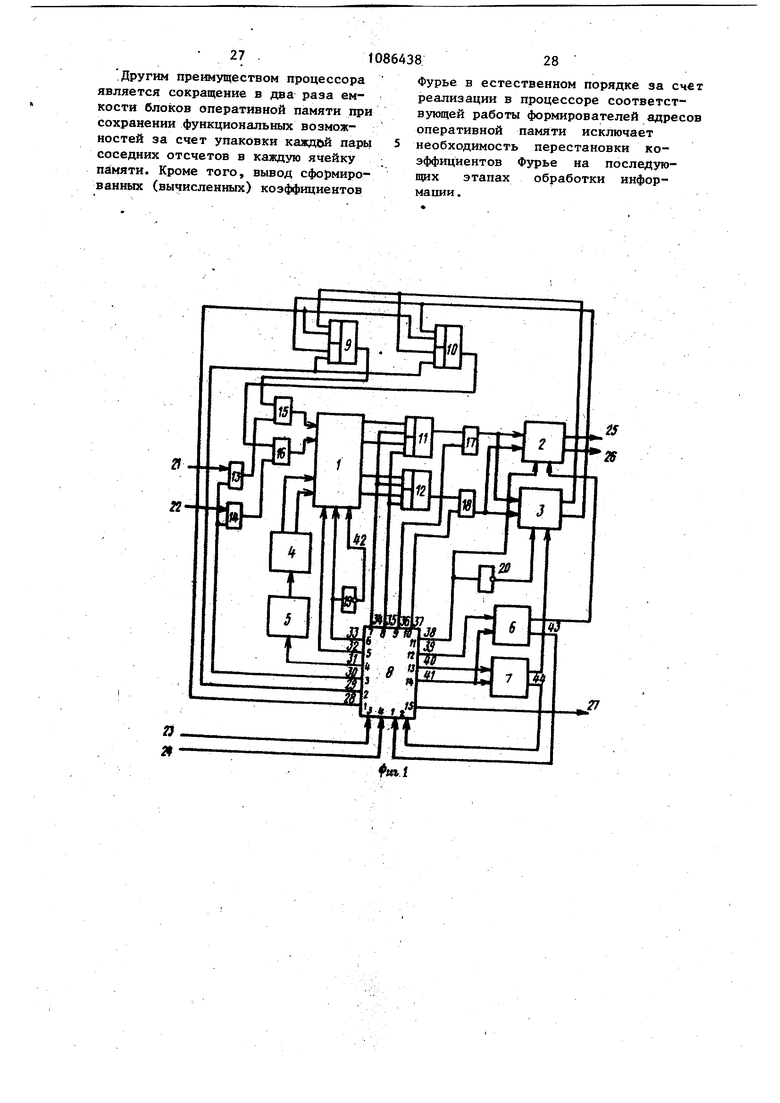

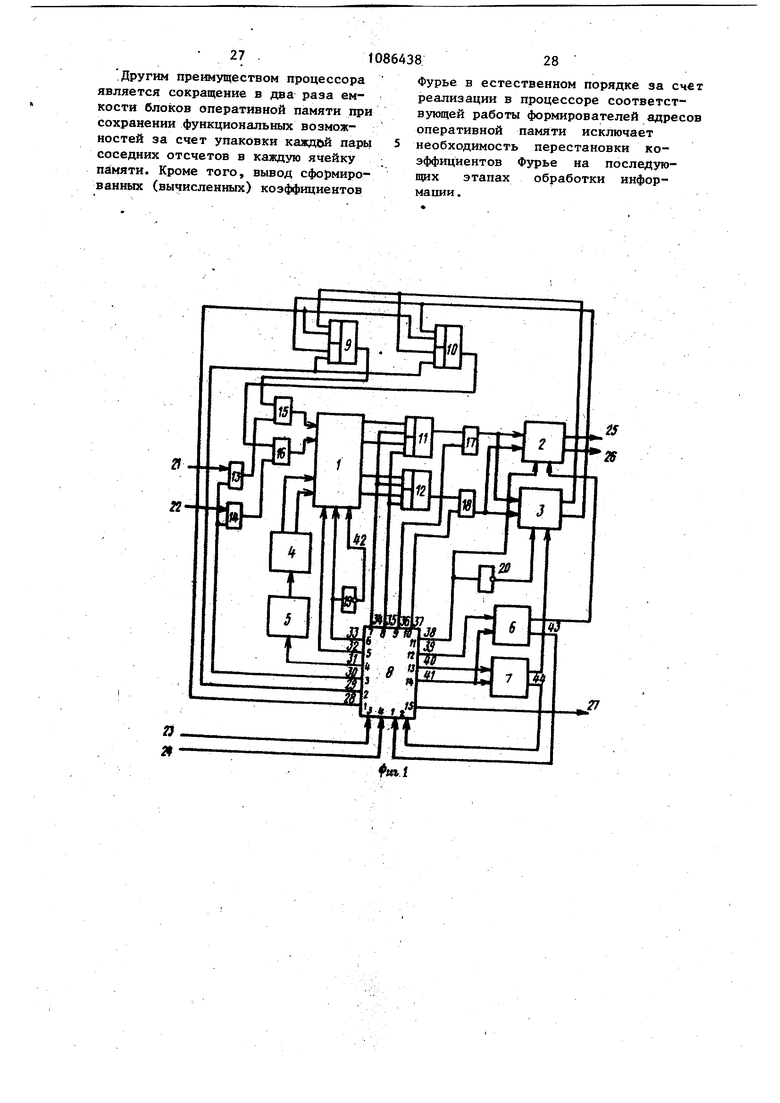

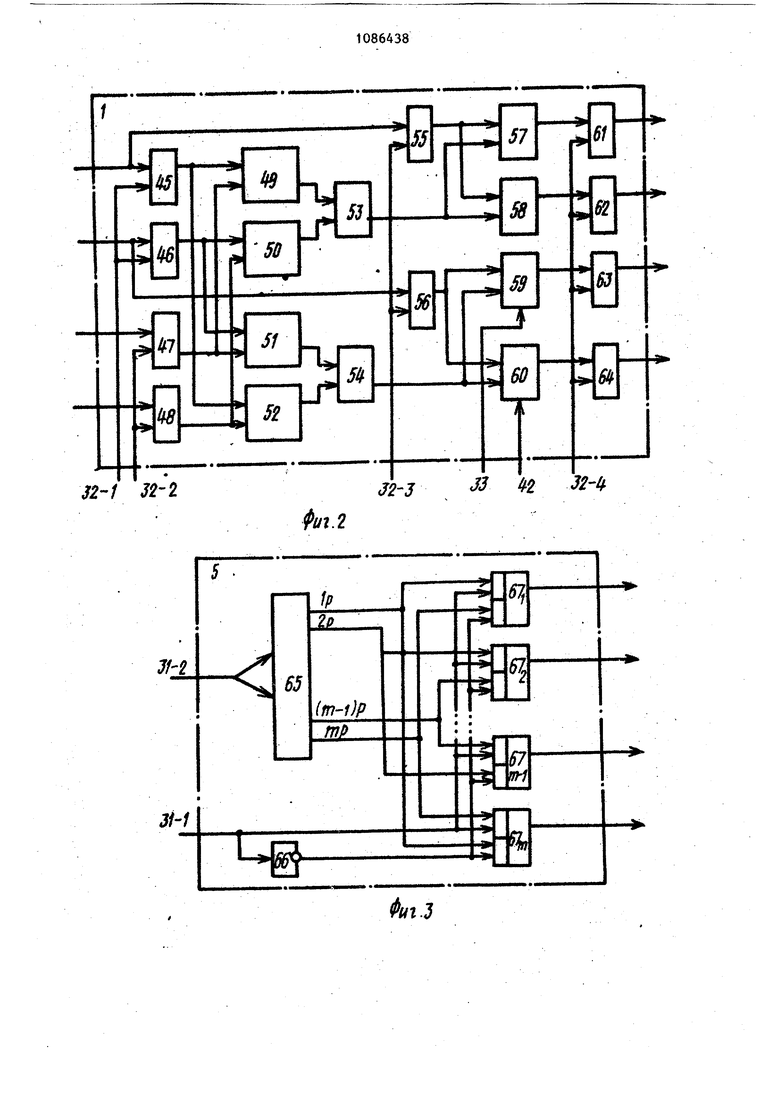

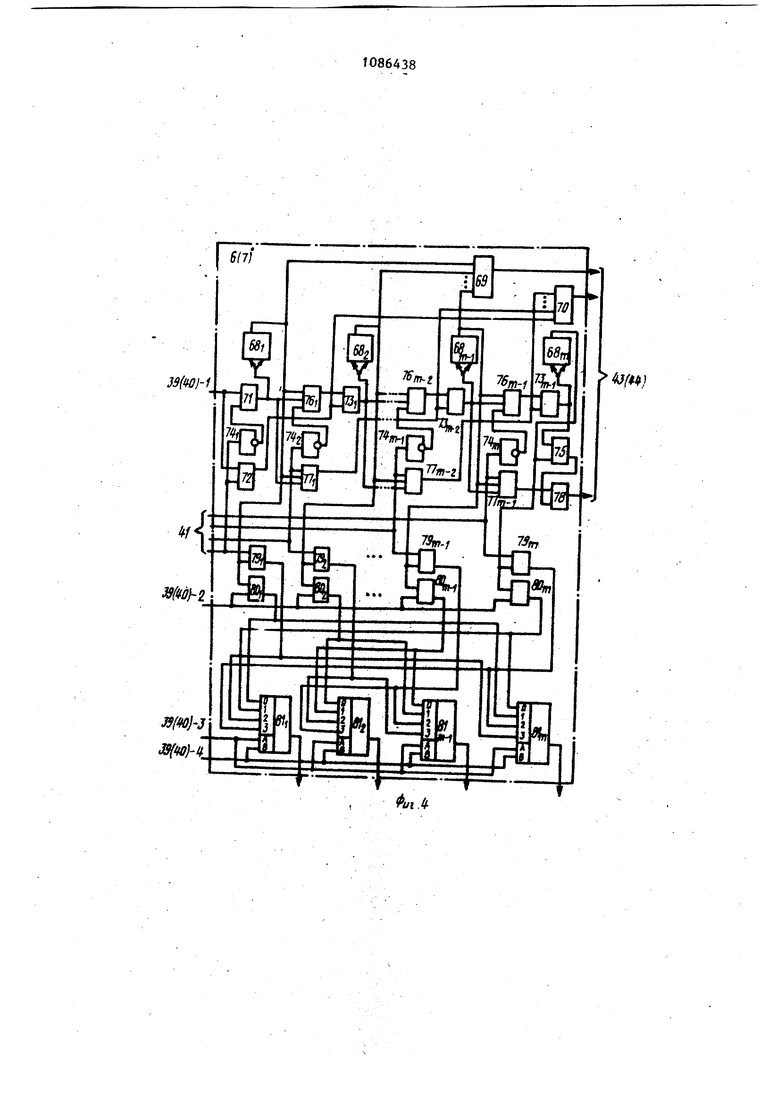

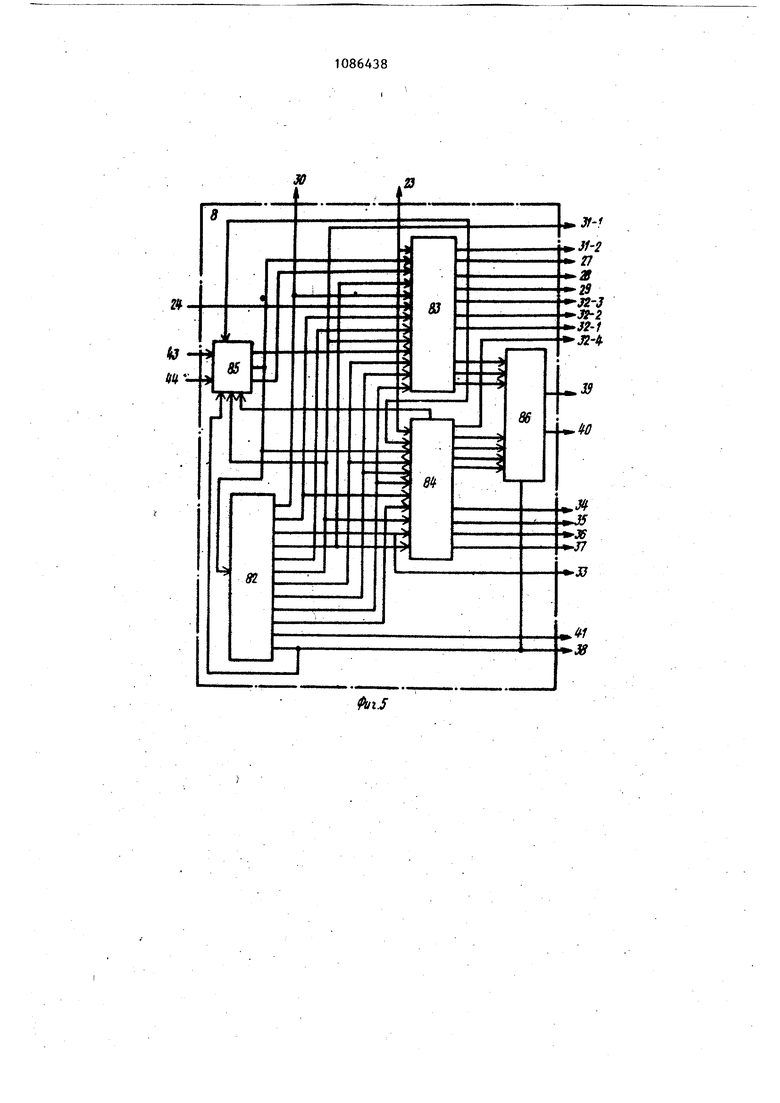

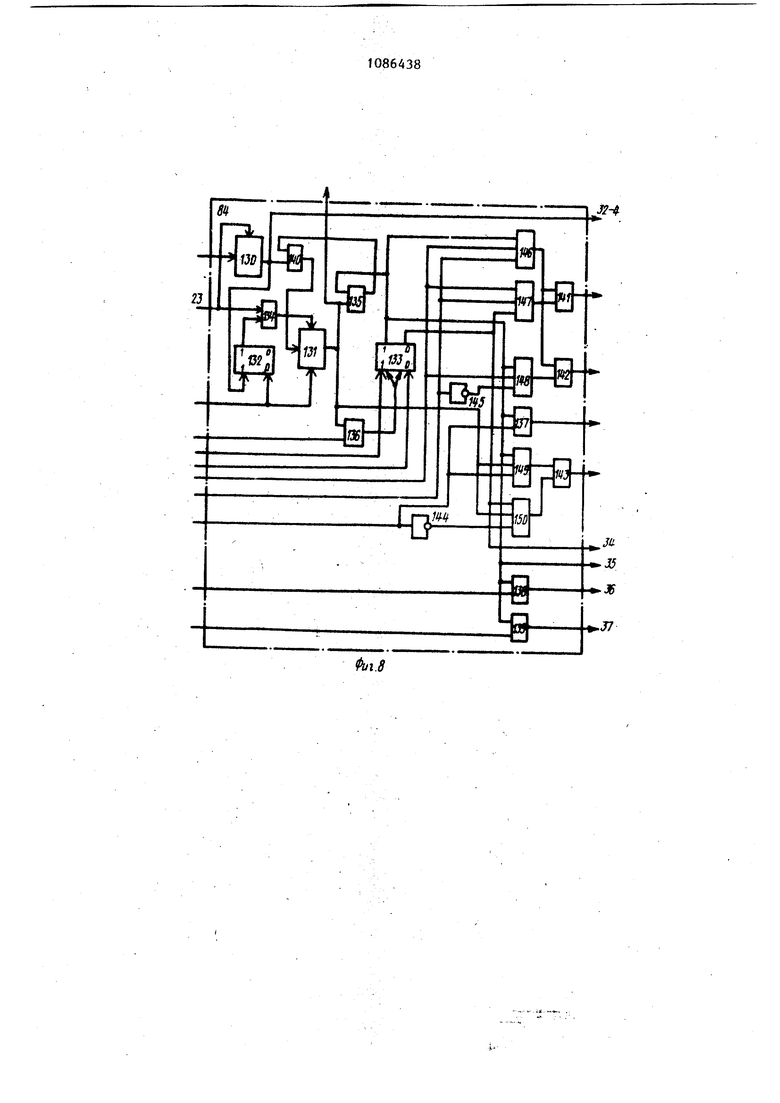

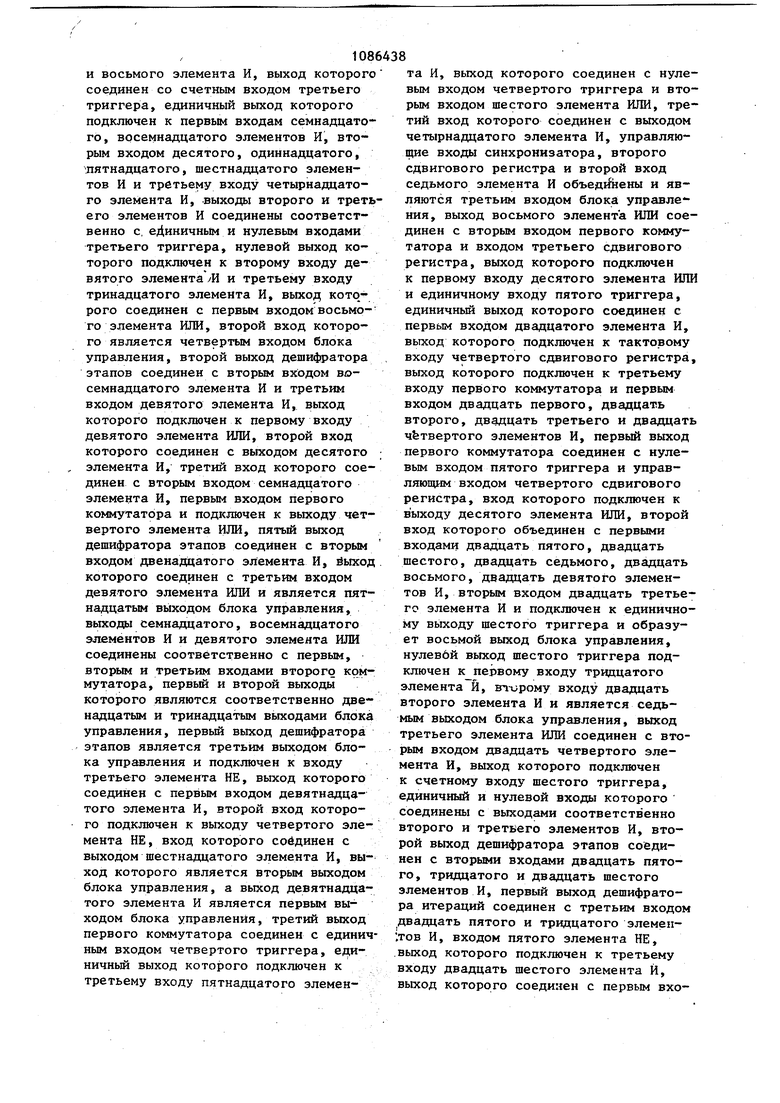

ра итерации являются четырнадцатым выходом блока управления, выход первого триггера соединен с четвертым . входом первого коммутатора и восьмым входом второго коммутатора и является одиннадцатым выходом блока управления, первый выход дешифратора этапов является третьим выходом блока управления, выходы четвертого и седь5 мого элементов ИЛИ являются четвертым выходом блока управления, выход одиннадцатого элемента И, выходы второго и третьего сдвиговых регист- 388 МИ входами двадцать пятого, тридцатого и двадцать шестого элементов И, первый выход дешифратора итераций соединён с третьим входом двадцать пятого и тридцатого элементов И и входом пятого элемента НЕ, выход которого подключен к третьему входу двадцать шестого элемента , выход которого соединен с первым входом одиннадцатого элемента ИЛИ, второй вход которого объединен с первым входом двенадцатого элемента ИЛИ и подключен к выходу двадцать пятого элемента И, выход тридцатого элемента И соединен с вторым входом двенадцатого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к второму входу двадцать седьмого элемента И, третьему входу двадцать третьего элемента И и входу шестого элемента НЕ, выход которого подключен к третьему входу двадцать второго элемента И, выход которого подключен к первому входу тринадцатого элемента ИЛИ, второй вход которого соединен с выходом двадцать третьего элемента И, третий выход дешифратора итераций является шесть&1 выходом блока управления и соединен с вторым входом двадцать восьмого элемента И, выход которого является девятым выходом блока управления, четверплй выход дешифратора этапов подключен к второму входу двадцать девятого элемента И, вырсод которого является десятым выходом блока управления, выходы одиннадцатого, двенадцатого и тринадцатого элементов ИЛИ и выход двадцать седьмого элемента И соединены соответственно с четвертым, пятым, шестым и седьмым входом второго коммутатора, второй выход двадцатого элемента И и тактовый вход третьего сдвигового регистра объединены и образ5 т третий вход блока управления, первый, второй. третий и четвертый выхода дешифраторов и выход ВОСЬМОГО элемента ИЛИ образуют пятый выход блока управления, а пятый и шестой входы первого коммутатора являются соответственно первым и вторым входами блока управления. На фиг, 1 представлена схема процессора; на фиг, 2 - 10 - соответственно арифметический блок, формирователь адресов постоянной памяти, формирователь адресов (оперативной памяти), блок управления, узел этапов, узел управления считыванием, узел управдеяия записью, входной и выходной ксмчмутаторы. Процессор быстрого преобразования Фурье содержит арифметический блок блоки (оперативной) памяти 2,3, блок .постоянной памяти 4, формирователь адресов (постоянной памяти) 5, формирователи адресов (оперативной памяти) 6, 7, блок управления 8, четыре элемента 2 И-ИЛИ 9-12, два элемента И 13 и 14, два элемента ИЛИ 15 и 16, два сумматора по модулю 2 17 и 18, элементы НЕ 19 и 20, информационные вкодь 21, 22, тактовый вход 23. вход синхронизации приема чисел 24, информационные выходы процессора 25, 26, выход синхронизации выдачи чисел 27, выходы 28-41 блока 8, выход 42 элемента НЕ 19, выходы 43-44 формирователей 6 и 7 соответственно. На фиг. 2 представлена функциональная схема арифметического блока 1 , который соответствует вычислительному устройству прототипа и содержит регистры 45 реальной и 46 мнимой частей первого числа из пары обрабатываейых комплексных чисел, регистры 47 и 48 реальной и мнимой частей комплексного весового коэффициента, матричные умножители 49-52, сумматоры 53, 54, регистры 55 реальной и 56 мнимой частей второго числа из пары обрабатываемых комплексных чисел, сумматоры 57-60, регистры 61, 62 хранения реальной части соотвеТаСТ венно первого и второго комплексного результата вычислений и регистры 63 64 хранения мнимой части соответственно первого и второго комплексного результата вычислений. На фиг.. 3 представлена функциональная схема формирователя адресов постоянной памяти 5, который содержит счетчик адреса 65 наш разрядов 10 10 элемент НЕ 66, группу элементов 2 ИИЛИ 67т- 67. На фиг. 4 представлена функциональная схема формирователя адресов (оперативной памяти) 6 (7), которьА содержит, регистр адреса на m разрядов, состоящий из триггеров 68, элемент И на (in-1) вход 69, элемент ИЛИ на (т-1) вход 70, двухвходовые элементы И 71, 72, двухвходовые элементы ИЛИ 73 - 73, элементы НЕ 74 - 74, двухвходовой элемент И 75, две группы трехвходовых элементов И 76 - 76, , И 77 -77, двухвходовые элементы ИЛИ 78, 79.., - 79j, сумматоры по модулю 2 80 - 80, мультиплексоры 8 Ц - 81 для вьщачи кода адреса. На фиг. 5 представлена структурная схемаблока управления 8, который содержит узел этапов 82, раскрытьй на фиг. 6, узел управления считыванием 83, раскрытый на фиг. 7, узел управления записью 84, раскрытый на фиг. 8, входной коммутатор 85, раскрытый на фиг. 9, и выходной коммутатор 86, раскрытый на фиг. 10. На фиг. 6 представлена функциональная схема узла этапов 82. Расположение входа и выходов, узла соответствует расположению их на фиг. 5. Узел содержит счетчик этапов 87, дешифратор этапов на пять выходов 88, счетчик итераций 89, дешифратор итераций на m выходов 90, триггер 91, элементы НЕ 92 и 93, элементы И 94 97 (трехвходовой) элемент И 98, (двухвходовые) элементы ИЛИ 99 и 100 и (трехвходовые) элементы ИЛИ 101 и 102. На фиг. 7 представлена функциональная схема узла управления считыванием 83. Расположение входов и выходов узла соответствует расположению их на фиг. 5. Узел содержит синхронизатор 103, триггеры 104 - 106, сдвиговые регистры (на 4 разряда) 107 и 108, выполняющие роль элементов задержки, (двухвходовые) элементы И 109-117, (двухвходовые) элементы ИЛИ 118 - 120, (трехвходовые) элементы И 121 - 125, (трехвходовые) элементы ИЛИ 126 и 127 и элементы НЕ 128 и 129. На фиг. 8 представлена функциоальная схема узла управления заисью 84. Расположение входов и вы- i одов узла соответствует расположению их на фиг. 5, Узел содержит сдвиговы регистры 130 и 131 (на 4 разряда), выполняющие роль элементов задержки триггеры 132 и 133, (двухвходовые) элементы И 134 - 139,, (двухвходовые) элементы ИЛИ 140-143, элементы НЕ 14 и 145, (трехвходовые) элементы И 146 150. На фиг. 9 представлена функциональная схема входного коммутатора, который содержит элементы 2 ИИЛИ 151-155, (трехвходовые) элементы И 156 и 157, (двухвходовые) элементы ИЛИ 158 и 159 и элемент НЕ 160 Расположение выходов соответствует расположению их на фиг. 5. На фиг. 10 представлена функциональная схема выходного коммутатора 86, которьй содержит (двухвходовы элементы И 161 и 162, элементы 2ИИЛИ 163-168 и элемент НЕ 169. Распо ложение входов коммутатора 86 соотве ствует расположению их на фиг. 5. Для пояснения работы процессора рассмотрим реализуемьй в нем алгоритм быстрого преобразования Фурье (БПФ). Входная последовательность S: , где , 1, 2, ...,N-1, преобразуется в комплексную последовательность .{(j)j, где , 1, 2,...,N/2-1, путем- представления каждой пары со седних отсчетов комплексным числом, причем четные отсчеты (5 ,57 54i считаются реальными, а нечетные (5 ,5, , Sg. , ... ,Sj) - мнимыми частями комплексных чисел. Вычисление коэффициентов Фурье от преобразо ванной последовательности заключается в вычислении промежуточных коэффициентов по базовым формулам алгоритма БПФ: Ai(j) А,. (j)+A (K)wi;i , (О A{(K)A.(J)-A..(K)W (2) где - номер текущей итерации, ., 2, 3,... , m., Wf - значение комплексного весово го коэффициента. Значение п равно двоичной инверси кода номера зоны вычислений в итера ции. Так, для двоичного кода «-,, 012 , Лд .. .,«., О двоично-инверсный коД будете,, а ,,...,с,з номера зоны представляется m-разряд:ным двоичным кодом. Номера зон на итерациях будут: для первой итерации; ,1 для второй итерации; 108 12 i 0,1,2,3 для третьей итерации; 0,1,2,3,. ..,N/4-1 для последней итерации. Так как преобразованнаяопоследовательность стала в два раза короче исходной, то количество итераций для вычисления будет на единицу меньше, а емкость оперативной памяти сокращается вдвое. Соответственно сокращается время вычисления на каждой итерации в два раза. После вычисления промежуточных коэффициентов производится вычисление .коэффициентов Фурье по формулам: А tA.., , А, -А где t к 1, 2, ...,(); А и - промежуточные коэффициенты, вычисленные по формулам (1) и (2). Вычисление по формулам (3) выполляется в два этапа. На первом производится вычисление выражений ..... После вычисления выражений (5) выполняется, второй этап, заключающийся в вычислении коэффициентов Фурье по формулам (3) и (4), аппаратная реализация которых такая же, как и базовых формул (1) и (2). Отличие заключается в формировании адресов весовых коэффициентов w и операндов. Следует отметить, что вычисления по формулам (1) - (4) позволяют определить только N/2 коэффициентов Фурье, Однако для спектрального анализа этого вполне достаточно, так как вторая половина спектра симметрична относительно первой. Время вычисления коэффициентов по формулам (3) и (4) равно времени вычисления по базовым формулам (1) и (2) на двух любых итерациях. Процессор работает следукяцим образом. Перед вычислением коэффициентов Фурье в блок оперативной памяти 3 вводится последовательность входных отсчетовfS; I . Каждая пара соседних отсчетов поступает на информационные входы процессора 21 и 22 одновремени сопровождается сигналом синхрониза ции приема числа по входу 24. Четные отсчеты (Sjj ,$21 ... iS(sj-2 поступают на информационные входы регистра 55 арифметического блока 1 через первые входы элементов И 13 и элементов ИЛИ 15, а нечетные (5, 5 , -5uJ на информационные входы ре1ис ра 56 арифметического блока 1 через первые входы элементов И 14 и элементов ИЛИ 16. Во время врода счетчик этапов 87 (фиг. 6) блока управления 8 находится в нулевом состоянии, при этом с первого выхода дешифратора этапов 88 блока управления 8 на вторые входы групп элементов И 13 и 14 по шине (выходу) 30 поступает разрешающий потенциал. Сигнал синхронизации приема чисел через первый вход элемента ИЛИ 120 (фиг 7)блока упрйвлекия 8проступае на последовательный вход сдвигового регистра 130 (фиг. 8) блока управления 8 и на входы записи регистров 55 и 56 nj входу 32-3 (фиг. 2). Тактовые импульсы по входу 23 поступают на сдвиговый вход регистра 130 и обеспечивают последователь ное продвижение сигнала синхронизации по его разрядам. Сигнал с выхода сдвигового регист ра 130 производит запись в регистры 61-64 арифметического блока 1 вхо ных отсчетов, постуцакщих на их информационные входы с выходов регистров 55 и 56 через сумматоры 57-60 арифметического блока 1, на вторые входы которых поступает нулевая информация, заданная при установке исходного состояния процессора. Одновременно этот же сигнал устанавливае в единичное состояние триггер 132 и через элемент ИЛИ 140 поступает на последовательный вход сдвигового ре гистра 131 (фиг. 8) блока управления 8. Сдвиговые регистры 130 и 131 служат в качестве схем задержки. Сдв говый регистр 130 обеспечивает задержку сигнала записи в регистры 6164 относительно сигнала записи в регистры 56 и 55 на время вычисления в сумматорах 57-60. Сдвиговый регистр 131 обеспечивает задержку изме нения кода адреса и информации на входах блоков оперативной памяти на время их цикла записи. Триггер 133 (фиг. 8) блока управления во время ввода находится в нулевом состоянии и разрешающий потенциал с его нулевого плеча по входу 34 поступает на вторые входы элементов 2 И-ИЛИ 12 и 11, тем самым к информационным входам блоков оперативной памяти будут подключены выходы регистров 61 и 63. Иэменение знаков входных отсчетов на элементах 17 и 18 не производится, так как на вторые их входы поступают нулевые потенциалы с выходов элементов И 138 и 139 (фиг. 6) блока управления 8. Триггер 91 (фиг. 6) блока управления 8 находится в нулевом состоянии. Нулевой потенциал с единичного выхода этого триггера по,входу 38 поступает, на третьи входы (входы управления записью и считыванием) первого и через элемент НЕ 20 второго блоков оперативной памяти 2 и 3. Высокий уровень на третьем входе блока оперативной памяти задает режим записи, а низкий - режим считывания. Поэтому входные отсчеты записываются в блок оперативной памяти 3. Кроме того, нулевой потенциал триггера 91 поступает на элементы выходного коммутатора 86 (фиг. 10) блока управления 8 и обеспечивает подключение выходов элементов ШШ 141-143 и элемента И 137 (фиг. 8) блока управления 8 по шинам 40 на входы формирователя адресов и оперативной памяти 7 (фиг. 4). Во время ввода всей последовательности входных отсчетов на выходах элементов ШШ 141-143 находится низкий потенциал. Низкие потенциалы с выходов элементов ИЛИ 141-143 поступают соответственно через элементы И 162, 2 И-ИЛИ 166 и 167 выходного коммутатора 86 (фиг. 10) на управлякхцие входы мультиплексоров 81 - 81j и вторые входы элементов сумматоров по модулю 2 80- - 80 по входам 40-4, 40-3 и 40-2, обеспечивая тем самым передачу кода регистра адреса 68 - 68 через мультиплексоры 81 - 81 (фиг. 4) на (адресный) вход блока оперативной памяти 3. Во время ввода в счетчике итераций 89 (фиг. 6) блока управления 8 нулевой код, при этом на всех выходах дешифратора 90 низкий потенциал. Низкие потенциалы с выходов дешифратора 90 по выходам 41 поступают на входы элементов формирователя адре сов оперативной памяти 6 и 7 и задают в формирователе приращений кода адреса режим естественного порядка счета. На первом входе элемента И 135, на втором входе элемента И 136, на первом и третьем выходах элемента И 149 низкие потенциалы, а на пер вом итретьем входах элемента И 150 высокие потенциалы (фиг. 8), поэтому сигналы с выхода сдвигового регистра 131 проходят только на выход элемента И 150 (фиг. 8). С выхода элемента И 150 через элемент ИЛИ 143 эти сигналы в качестве сигналов счета поступают через первый вход элемента 2 И-ИЛИ 168 (на втором входе этого элемента высокий потенциал) выходного коммутатора 86 (фиг. 10) по шине 40-1 на первые входы элементов И 71,и 72 (счетный вход) формиро вателя адресов оперативной памяти 7 (фиг. 41). С приходом каждого сигнала счета содержимое регистра адреса 68; - 68 увеличивается на единиЦУ- , , I Сигнал счета с номером N/2 во время записи в блок оперативной памяти 7 пары отсчетов с номеромМ/Д проходя по цепочке элементов 71, 73 - 73., производит переключение триггеров 68 - 68 регистра адреса из единичного в нулевое состояние и через первые вход элемен та И 75, второй вход элемента ИЛИ 78 в качестве сигнал; переполнения по третьему выходу 44 (фиг. 4) поступае на третий вход элемента 2 И-ИЛИ 153 и первый вход элемента 2 И-ИЛИ 155 (фиг. 9). На этом ввод массива входных отсчетов заканчивается. В каждой ячейке блока оперативной памяти записаны по два соседних отсчета. Второй этап работы процессора заключается в вычислении промежуточной коэффициентов Фурье по формулам (1) и (2). На всех итерациях, кроме последней, адреса записи вычисленных операндов A-(j) и A;j(1) такие жej как и адреса считывания входных операндов Aj(j) и А- (к). Обозначим адреса для операндов A-.(j) и А, .(к через XI и Х2, адреса операндов A(j) и А;(к) на всех итерациях, кро ме последней, через У1 и У2, а для последней итерации - У1 и У2. ., Адреса XI и У1 формируются на регистре адреса формирователем приращений формирователей адресов 6 и 7 в естественном порядке счета с запретом установки в единичное состояние тех триггеров регистра адреса, номера которых совпадают с поздаионным номером выполняемой итерации, причем первый номер имеет старший триггер 68р, регистра адреса (фиг. 4). Конкретно, на первой итерации запрещена установка в единицу триггера 68, на ,второй итерации триггера 68 и т.д. Формирование адресов Х2 и У2 производится логическим суммированием на элементах ИЛИ 79 - 79 кода регистра адреса 68 и - 68 с позиционным номером выполняемой итерации. Формирование адресов У1 и У2 производится двоичной инверсией адресов У1 и У2 через вторые и четвертые входы мультиплексоров 81 - 81|. Запись результатов вычислений по адресам У1 и У2 обеспечивает, естественный порядок их расположения в блоке оперативной памяти 6 или 7. Значения комплексных весовых коэф. 2Г( i п фициентов J (и хранятся в ячейках блока постоянной памяти последог вательно, причем п однозначно соответствует номеру ячейки Считывание кодов весовых коэффициентов в арифметический блок 1 производится в начале каждой итерации и по сигналу конца зоны, поступающему с выхода элемента И 70 (фиг. 4) на втором выходе 43 Д.Г1Я блока 6 и по второму входу 44 для блока 7. Адреса для считывания весовых коэффициентов формируются путем двоичной инверсии на элементах 2 И-ЙЛИ 67 - 67 кода счетчика адреса 65. Рассмотрим работу процессора по вычислению промежуточных коэффициентов по формулам (1) и-(2) на примере обработки первой пары операндов первой итерации. Сигнал пе1реполнения по окончании ввода с выхода элемента ИЛИ 78 блока 7 (фиг. 4) по третьему выходу 44 через первый вход элемента 2 И-ИЛИ 155 (на втором входе высокий потенциал), через второй вход элемента ИЛИ 159 (фир. 9)входного коммутатора, в качестве сигнала конца записи массива, поступает на вход узла управления считыванием 83 и на третий вход узла управления записью 84. В блоке управ ления 8 сигнал конца записи массива производит следующее: через второй вход элемента И 94 (на первом входе высокий потенциал) и второй вход эле мента ИЛИ 99добавляет единицу в. счетчик этапов 87, обеспечивая тем самым высокий уровень на втором выхо де дешифратора этапов 88 (фиг. 6) и низкий на всех остальных выходах; переключение триггера 91 (фиг. 6) из нулевого в единичное состояние, устанавливая тем самым блок оператив ной памяти 2 в режим записи, а блок оперативной памяти 3 в режим считывания; через первый вход элемента И 96 (на втором выходе высокий потенциал) устанавливает в единичное состояние триггер 106 (фиг. 7) узла управления считыванием 83 и треггер 133 (фиг. 8) узла управления записью 84; через синхронизатор 103 (фиг. 7) устанавливает в единичное состояние триггер 104 и через элементы ИЛИ 118 и 126 первые разряды: сдвиговых регистров 107 и 108; подтверждает нулевое состояние триггера 132V регистра 131 (фиг. 8) узла управпения записью 94. Высокий потенциал с единичного вы хода триггера 91 (фиг. 6) по двенадцатому выходу узла этапов поступает на вход элемента НЕ 169, на вторые входы элементов И 161 и .162 и на чет вертые входы элементов 2 И-ШТИ 163 168 (фиг. 10), обеспечивая тем самым передачу сигналов из узла управления считыванием 83 по выходам 40 в формирователь адресов 7 и передачу сигналов из узла управления записью 84 -ПО выходам 39 в формирователь адресов 6. Высокий уровень на втором выходе дешифратора этапов 88 и единичное состояние триггера 106 обеспечивает формирование высокого потенциала на выходе элемента .И 116 и низкого - на выходе элемента И 117 (фиг. 7) узла управления считыванием 83, при этЛ на выходах элементов И 162 и 2 ИШШ 167 низкие потенциальг, а на выхо де элемента 2 И-ИЛИ 166 - высокий потенциал (фиг. 10) выходного коммутатора 86. Эти потенциалы, поступая по выходам 40-3, 40-2, 40-4 в формирователь адресов 7, обеспечивают фор мирование и вьздачу адреса Х2 в блок оперативной памяти 3, при этом на 10 818 выходах его устанавливается значение операнда А- (к). Аналогично высокий уровень на втором выходе дешифратора этапов 88 н единичное состояние триггера 133 (фиг. 8) узла управления записью 84 обеспечивают в формирователе адресов 6 формирование и выдачу из него в блок оперативной памяти 2 адреса У2. Адреса Х2 и У2 формируются на элементах ИЛИ 79 -, - 79, при этом на управляющих входах А и В соответственно единичный и нулевой потенциалы и на выходы мультиплексоров передаются уровни вторых входов (входы 1). На выходе элемента И 113 в процессе выполнения второго этапа держится высокий потенциал. Поступая по выходу 28 (фиг. 1) на вторые входь элементов 2 И-ШШ 9 и 10, этот потенциал разрешает прямую передачу операндов из блоков оперативной памяти 3 или, 2 в арифметический блок 1, т.е. мнимая часть операнда поступает на первый вход, а действительная на второй вход арифметического блока 1. Высокий уровень единичного плеча триггера 104 (фиг. 7) разрешает прохождение через элемент И 109 тактовых импульсов на сдвиговый вход регистра 107, которые производят последовательное продвижение единицы по разрядам perticTpa. Сигнал с выхода (старший разряд) сдвигового регистра 107 при единичном состоянии триггера 106 производит следукнцее: через первый вход элемента И 115 по выходу поступает на вторые входы регистров 45 и 46 арифметического блока 1 и производит запись в них соответственно реальной и мнимой частей операнда А.(к); через первый вход элемента ИЛИ 118 устанавливает в единицу первьй разряд сдвигового регистра. 107; через первый вход элемента И 110 производит переключение триггера 106 (фиг. 7). Тактовые импульсы поступают на сдвиговый: вход регистра 108 (фиг, 7), производя продвижение единицы по разряда м регистра. Сигнал с выхода сдвигового регистра 108 производит следующее : по выходу 32-2 поступает на вторые входы регистров 47 и 48 арифметического блока 1, записывая в них соответственно реальную и мнимую часть комплексного весового коэффициента. При нулевом состоянии триггера 106 (фиг, 7) на выходе элементов И 116 и 117 низкие потенциалы, которые через первые входы элементов 2 И-ИЖ 16 и 167 по выходам 40-4 и 40-2 поступают в формирователь адресов 7 и совместно с низким.потенциалом с выхода элемента И 162, поступающим пд выходу 40-3 также в формирователь адресов 7, обеспечивают вьщачу в блок оперативной памяти 3 кода адреса XI, при этом на информационных выходах этого блока устанавливается значение операнда А.,-.(/), который аналогично операнду Аj(к) поступает на первый и второй входы apH(J ieтического блока 1. При нулевом состоянии триггера 106 (фиг. 7) сигнал с выхода сдвигового регистра 107 производит следующее: через третий вход элемента И 121 и вт.орой вход элемента ИЛИ 120 устанавливает в единицу первый разряд регистра 130 (фиг. 8) и по выходу 32-3 поступает на вторые (управляющие) входы регистров 55 и 56, записьшая в них соответственно реальную и мнимзпо часть операнда A(j); через третий вход элемента И 124, второй вход элемента ИЛИ 127 узла управления считьг ванием 83 (фиг. 7) и третий вход элемента 2 И-ИЛИ 168 выходного коммутатора 86 (фиг. 10) по выходу 40-1 поступает на первые входы элементов И 71 и 72 (счетный вход) формирователя адресов 7, увеличивая содержимое регистра адреса 68 -) - 68,„. При выполнении всех этапов обработки сумматоры 53 и 57 выполняют операцию сложения входных операндов, сумматоры 54 и 58 выполняют операцио вычитания, причем вычитаемым являются операнды, поступающие на вторые входы этих сумматоров. Низкий потенциал с третьеговыхода дешифратора этапов 88 (фиг. 6) по выходу 33 поступает на управляющий вход сумматора 59 (фиг. 2) и через элемент НЕ 19 по выходу 42 (фиг. 1) на управлякиций вход сумматора 60, обеспечивая тем самым операцию сло.жения на суммато-; ре 59 и операцию вычитания на сумматоре 60. На информационные входы регистров 61 и 63 поступают реальная и мнимая части результата A,-(j), а на информационные входы регистров 62 и 64 поступают соответственно реальная и мнимая части результата (к). Сигнал с выхода сдвигового регистра 130 (фиг. 8), задержанный по отношению к входному сигналу на время задержки сумматоров 57-60, производит следукяцее: по выходу 32-4 записывает результаты A.(j) и А-(к) в регистры 61-64 арифметического блока 1; устанавливает первьй разряд сдвигового регистра 131 через второй вход злемента ИЛИ 140 (фиг, 8) в единичное состояние; устанавливает в единичное состояние триггер 132, разрешая прохождение тактовых импульсов через элемент И 134 на сдвиговый вход регистра 131. Единичное состояние триггера 133 (фиг. 8) обеспечивает подключение выходов регистров 62 и 64 на инфо1 1ационные входы блоков оперативной памяти 2 и 3, при этом из формирователя адресов 6 в блок оперативной памяти 2 поступает адрес У2. К моменту появления сигнала на выходе -регистра 131 в блоке оперативной памяти 2 происходит запись результата А(к). Сигнал с выхода регистра 131 производит следзпмцее: через второй вход злемента И 136 (на первом входе этого элемента разрешакш1ий потенциал, образованный сборкой по ИЛИ второго, третьего и четвертого выходов дешифратора этапов 88, фиг. 6, на элементе ИЛИ 101) переключает в нулевое состояние триггер 133 (фиг. 8), при этом на выходе формирователя адресов 6 формируется адрес У1; через второй вход элемента И 135 и первый вход элемента ИЛИ 140 записьшает единицу в первый разряд регистра 131. При нулевом состоянии триггера 133 к блокам оперативной памяти 2 и 3 подключены регистры 61 и 62. К моменту появления сигнала на выходе регистра 131 в блоке оперативной памяти 2 происходит запись результата A(j) по адресу У1. При нулевом состоянии триггера 133 сигнал с выхода регистра 131 через второй вход элемента И 150, второй вход элемента ИЛИ 143, третий вход элемента 2 И-ИПИ 165 выходного комутатора 86 (фиг. 10) по выходу 39-1 поступает на счетный вход формирователя адресов 6 и увеличивает код регистра адреса 68 - 68. 211 Механизм обработкипоследующих пар операндов аналогичен обработке первой пары операндов. Все операн ды на первой итерации обрабатываются с одним и тем же весовым коэффициентом. После считывания всего массива операндов из блока оперативной, памяти 2 на выходе элемента И формирователя адресов 7 формируется сиг нал переполнения, который через первый вход элемента ИЛИ 78 (фиг. 4), третий вход элемента 2 И-ИЛИ 153 и второй вход элемента ИЛИ 158 (фиг. 9 входного коммутатора 85, в качестве сигнала конца считывания массива, устанавливает в нулевое состояние триггер 104 и регистр 107 (фиг. 7), тем самым прекршцается процесс считы вания массива операндов. После записи всех пар результатов на выходе элемента И 77 формирова теля адресов 6 формируется сигнал переполнения, который через первый вход элемента ИЛИ 78 (фиг. 4), трети вход элемента 2 И-ИЛИ 155, второй вход элемента ИЛИ 159 (фиг. 9), в качестве сигнала конца записи массива, поступает в ,узел управления считыванием 83, узел управления записью 84 и в узел этапов 82 и производит те же действия, что и после окончания ввода массива данных, за исключением узла этапов 82. В послед нем по этому сигналу через элемент И 95 происходит добавление единицы в счетчик итераций 89, тем самым на выходе дешифратора итераций 9 устанавливается вторая итерация (на втором выходе высокий потенциал). Триггер 91 переключается по каждому сигналу конца записи массива тем самым изменяется режим работы блоков оперативной памяти 2 и 3. Начиная со второй итерации, считывание комплексных весовых коэффициентов производится не только в начале итерации, но и после прихода каждого сигнала конца зоны, вырабаты ваемого элементом ИЛИ 70 формирователя адресов, включенного в режим считывания. При выполнении последней итерации при единичном состоянии три гера 133 на выходах элементов ИЛИ 14 и 142 (фиг. 8) узла управления записью формируются высокие потенциалы которые обеспечивают в формирователе адресов (6 или 7), находящемся в режиме записи, фо1)мирование адреса У2 8 через четвертые входы мультиплексоров 81 - 81 (фиг. 4). При нулевом состоянии триггера 133 на выходе элемента ИЛИ 141 высокий потенциал сохраняется, а на выходе элемента ИЛИ 142 устанавливается низкий потенциал. Под воздействием этих потенциалов в формирователе адресов (6 или 7), находящемся в режиме записи, формируются и выдаются через вторые входы мультиплексоров 81 81, адреса У1 через вторые входы мультиплексоров 8Ц - 81 адреса У. Добавление единицы в счетчик этапов 87 на последней итерации производится сигналом конец записи массива через первый вход элемента И 98 (на втором и третьем входах высокие потенциалы и второй вход элемен- та ИЖ 99 (фиг. 6) , при этом ,на третьем выходе дешифратора этапов 88 устанавливается высокий потенциал. На третьем и четвертом этапах работы процессора производится вычисление коэффициентов Фурье по формулам (3) и (4) от результатов, полученных на втором этапе. Рассмотрим работу процессора по , вычислению пары коэффициентов Фурье. Пусть , а c+d,.. (6) , (7) V% , г ./q-c . . .. V j г На третьем этапе производится вычисление операндов Л ,2 ,6,, и ей на сумматорах 57-60 арифметического блока 1 и частичное умножение 6 + на множитель (-1), заключающееся в изменении знака операнда 6 на группе сумматоров по модулю 2 17 при высоком потенциале на их вторых входах. Перестановка местами операндов 6 и выполняется на.элементах 2 И-ИЛИ 9 и 10 (фиг. 1) при выполнении четвертого этапа. Для вычисления операндов Я и 6 с третьего выхода дешифратора этапов 88 по выходу 33 высокий потенциал поступает на управляющий вход сумматора 59 и через элемент НЕ 19 на управлякнций вход сумматора 60 арифметического блока 1. . Организация считывания операндов А и регистры 55, 56 и 45, 46 такая же, как и для операнДОН Aj (j), А (к) при выполнении второго этапа. Для обеспечения подачи реальной части с с регистра 45 на вторые входы сумматоров 57, 58 и мнимой час ти d с регистра 46 на вторые входы сумматоров 59, 60 в регистры 47 и 48 в начале этапа лооизвопится считывание по нулевому адресу из блока постоянной памяти весового коэббициента, у КОТОРОГО реальная часть равна единице, а мнимая нулю. В результа1те считывания в регистре 47 все разряды установлены в единичное состояние, а в регистре 48 - нулевое состояние на протяжении всего этапа выполнения Адресом на считывание операнда А является прямой код, а операнда A 2обратной код регистра адреса 68| -68fr, формирователя адресов (6 или 7) включенного в режим считывания. Адреса на запись результатов те же, что и адреса считывания входных операндов, причем запись Д +1Д производится по прямому коду адреса, по обратному коду адреса формирователя адресов, включенного в режим записи. Формирование обратного кода адреса производится при высоком потенциа /ле па вторых входах сумматоров по мо дулю 2 80;, - Spj, высокий потенциал формируется на: элементе И 117 при единичном состоянии триггера 106 узл управления считыванием 83 (фиг. 7) и на выходе элемента И 137 при единичноМ состоянии триггера 133 узла упра ления записью 84 (фиг. 8). Адреса для считывания и записи операндов передаются в блоки операти ной памяти 2 и 3 через первые входы мультиплексоров 81 - 81„ (фиг. 4) путем подачи на управляющие входы А и В низких потенциалов с выходов эле ментов И 161, 2 И-РШИ 163 для блока 6, И 162, 2 И-ИЛИ 166 (фиг. 10) для блока 7. Добавление единицы к со S держимому регистра 68 - 68, .вателя адресов (6 или 7), включенного в режим считьгоания, производится через первый вход элемента И 125 и третий вход элемента ИЛИ 127 (фиг. 7 Добавление единицы к содержимому ре 10 824 гистра адреса 68 - 68 формирователя адресов (6 или 7), включенного в режим записи, производится через второй вход элемента И 149 и первый вход элемента ИЛИ 143 (фиг. 8). Сигналы конца считьшания и записи массива на третьем и четвертом этапах формируются при единичном состоянии триггеров 68 - 68j, при .этом на выходе элемента И 69 (фиг. 4) устанавливается высокий потенциал. Пусть для определенности триггер 91 находится в единичном состоянии. Тогда высокий потенциал с единичного выхода этого триггера поступает на вход элемента НЕ 160 и на четвертые входы элементов 2 И-ИЛИ 151155. Формирователь адресов 7 включен в режим считывания, а фop иpoвaтель адресов 6 - в режим записи. Высокий потенциал с выхода элемента И 69 формирователя адресов 7 по выходу 44 через третий вход элемента 2 И-ИЛИ 151 поступает на второй вход элемента И 156 (на третьем входе высокий потенциал). При поступлении импульсного сигнала с выхода элемента ИЛИ 120 (фиг. 7) на первый вход элемента И 156 (фиг. 9) на его выходе формируется сигнал конца считывания массива, который устанавливает в нулевое состояние триггер 132, прекращая процесс считывания. Высокий потенциал с выхода элемента И 69 формирователя адресов 6 по выходу 43 через третий вход элемента 2 И-ШШ 154 поступает на первый вход элемента И 157 (на втором входе высокий потенциал). При поступлении импульсного сигнала с выхода элемента 131 (фиг. В) на третий вход элемента И 157 на его выходе формируется сигнал конца записи массива, который производит действия, аналогичные действиям на предьшуших этапах. К счетчику этапов 87 добавляется единица, а на дешифраторе этапов устанавливается высокий потенциал на четвертом выходе.. При выполнении четвертого этапа вычисление коэффициентов Фурье производится по формулам (2)( I .(VЛ)) ,...,(g-i); wjj-.e 1, 2, 3 Вычисление коэффициентов Фурье по формулам (9) и (10) аналогично выполнению любой итерации за исключением трех отличий. Первое отличие заключается в пер крестной передаче комплексного операнда () в регистры 45 и 46 арифметического блока 1 из блока оперативной памяти 2 или 3. Это обе печивается подачей высокого потенци ла с выхода элемента И 112 (фиг. 7) по выходу 29 на четвертые входы эле ментов 2 И-ИЛИ 9 и 10 на время при еыа операнда ( самым в регистр 45 записан код операнда 62 а в регистр 46 код операнда (-i(; ) . Второе отличие заключается в пря мой передаче в блок постоянной памя ти -4 кодов адресов счетчика адреса 65 (фиг. 3), при этом на вторые входы элементов 2 И-ИЛИ 67 - 67 подается высокий потенциал с четвер того выхода дешифратора этапов 88 п шине 31-1. Считывание весовых коэффициентов из блока постоянной памяти 4 в арифметический блок 1 и доба ление единицы в счетчик адреса 65 производится для каждой пары обраба тьшаемых операндов, причем первая пара операндов обрабатывается с вес вым коэффициентом по адресу 00 ...0 Это обеспечивается добавлением единицы в счетчик адреса 65 сигнала с выxojq;a регистра через первый вход элемента И 111 и второй вход элемен та ИЛИ 119 (фиг. 7) узла управления считыванием 83. Третье отличие заключается в изменении знака мнимой части результа та §N/2-1 . для получения результата Это обеспечивается подачей вы Nfil-V сокого потенциала с выхода элемента И 139 (фиг. 8) по выходу 37 на вторые входы сумматоров по модулю 2 (фиг. 1) на время записи результата В|Ц( блок оперативной памяти (2 или 3). Формирование адресов блоками 6 и 7 для считывания и записи операндов, а также формирование сигналов конца считывания и конца записи мас сива аналогично третьему этапу. Сигнал Конец записи массива по окончании четвертого этапа увеличивает код счетчика этапов 87, при этом на пятом выходе дешифратора эт пов 88 устанавливается высокий потеницал (этап вывода результатов). При выводе результатов вычисления узел управления записью 84 не работает, т.е. триггер 132 (фиг. 8) находится в нулевом состоянии. Каждый коэффициент Фурье, выдаваемый по выходам 25 и 26 из блока оперативной памяти 2 и 3, сопровождается сигналом синхронизации выдачи числа с выхода элемента И 114 по выходу 27; В процессе вывода внешнему абоненту,, выдаются в естественном порядк§ Iz . коэффицентов Фурье. По окончании вывода формируется сигнал конца считывания массива, который производит установку в нулевое состояние триггера 104 (фиг. 7). На этом работа процессора по вычислению коэффициентов Фурье заканчивается. Следует отметить, что вычисление коэффициента Фурье с номером МЯ на третьем и четвертом этапах работы процессора не производится: это потребовало бы введения в процессор значительного оборудования. В качестве коэффициента Фурье с номером К/4 используется промежуточный коэффициент с этим номером, вычисленный на втором этапе работы процессора и отличающийся от истинного коэффициента знаком перед-мнимой частью. Эта неточность не имеет принципиального значения, так как на последующих этапах в основном используется сумма квадратов модулей реальной и мнимой частей .этих коэффициентов. Данный п-роцессор обладает рядом технических преимуществ по сравнению с аналогичными процессорами. Основным из них является высокое быстродействие при выполнении обработки входной информации, высокое быстродействие достигается за счет представления действительной последовательности входных отсчетов размерностью N комплексной входной последовательностью N/2 и введением двух этапов вычислений по формулам (7) (10), что позволяет сократить время вычислений почти в два раза; введения и соответствующей организации работы формирователей адресов оперативной памяти и самой оперативной памяти, что исключает простои в работе арифметического блока и блоков оперативной памяти, т.е. достигнута конвейерная обработка информации. Другим преимуществом процессора является сокращение в два раза емкости блоков оперативной памяти при сохранении функциональных возможностей за счет упаковки каждой пары соседних отсчетов в каждую ячейку памяти. Кроме того, вывод сформированных (вычисленных) коэффициентов 10 2 Фурье в естественном порядке за счет реализации в процессоре соответствующей работы формирователей адресов оперативной памяти исключает необходимость перестановки коэффициентов Фурье на последуюпрх этапах обработки информации .

32-1 Л-2

фиг.2

«/ 42 2-1

Фиг.З

39{WI-1

Щ

Фиг Л

ил7

1

ш

Ж

т

-155

р-1/5/7 J

фиг.9

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 1971 |

|

SU421994A1 | |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления коэффициентов фурье | 1977 |

|

SU736112A1 |

Авторы

Даты

1984-04-15—Публикация

1982-05-24—Подача