1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для айтоматичес - кой проверки функционирования программируемых логических матриц (ПЛМ).

Цель изобретения - повышение быстродействия.

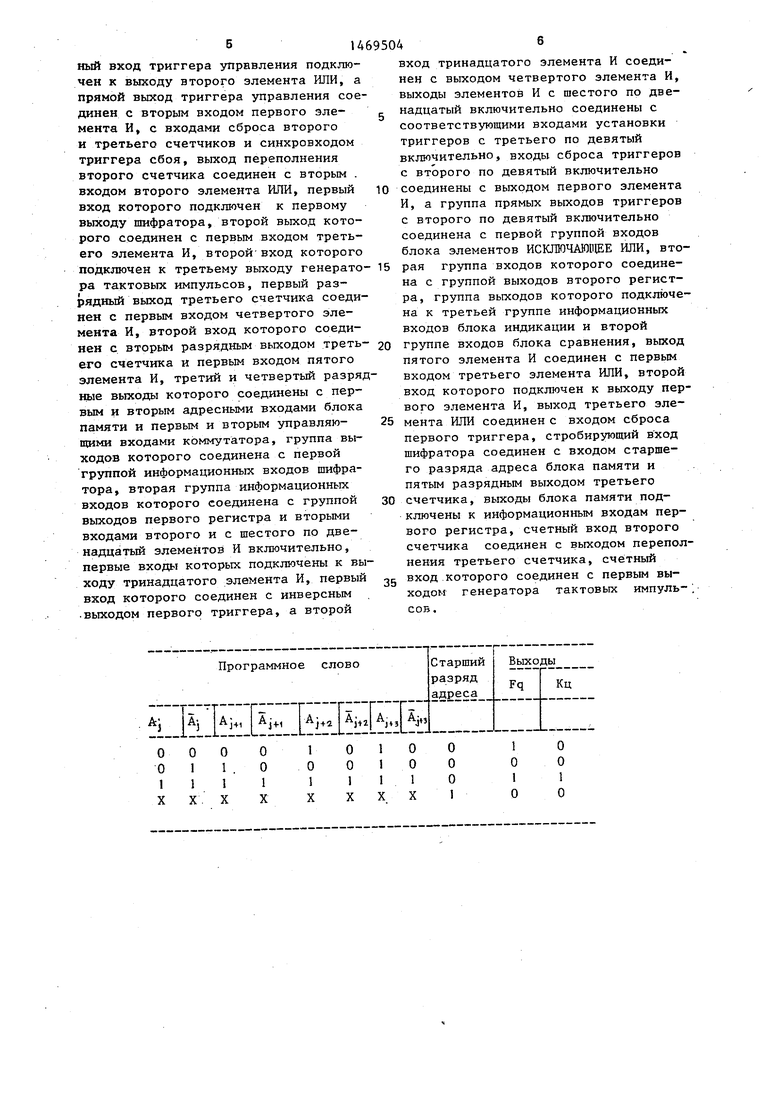

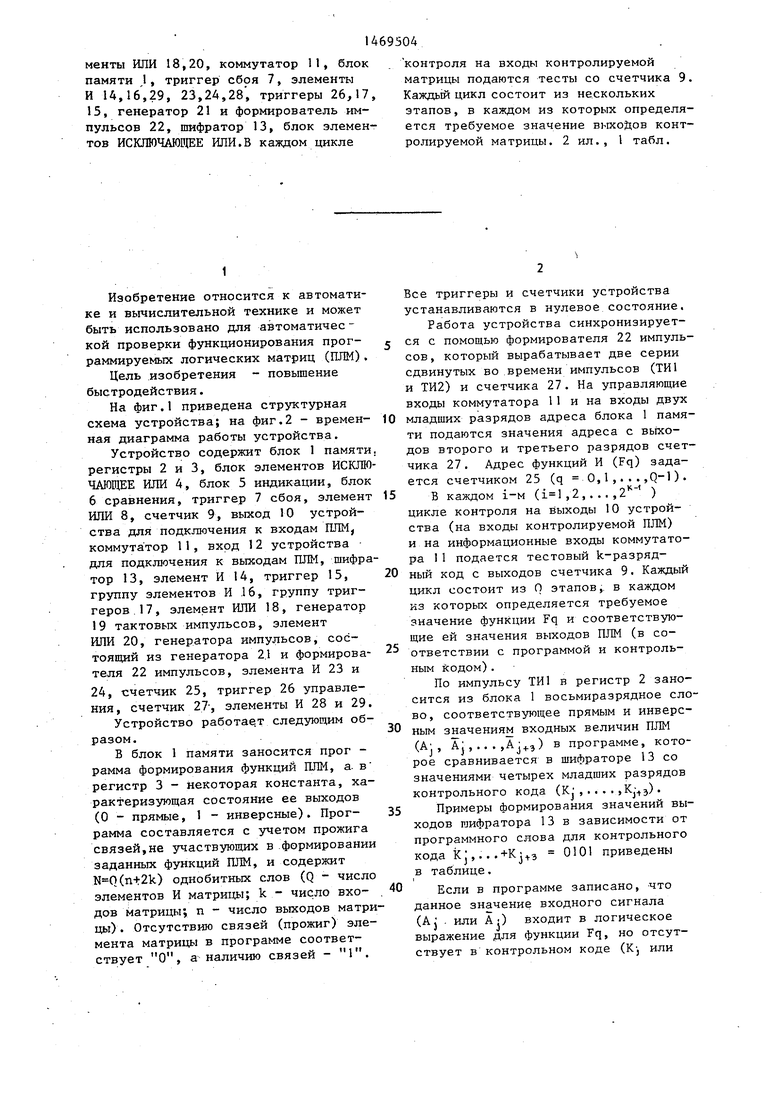

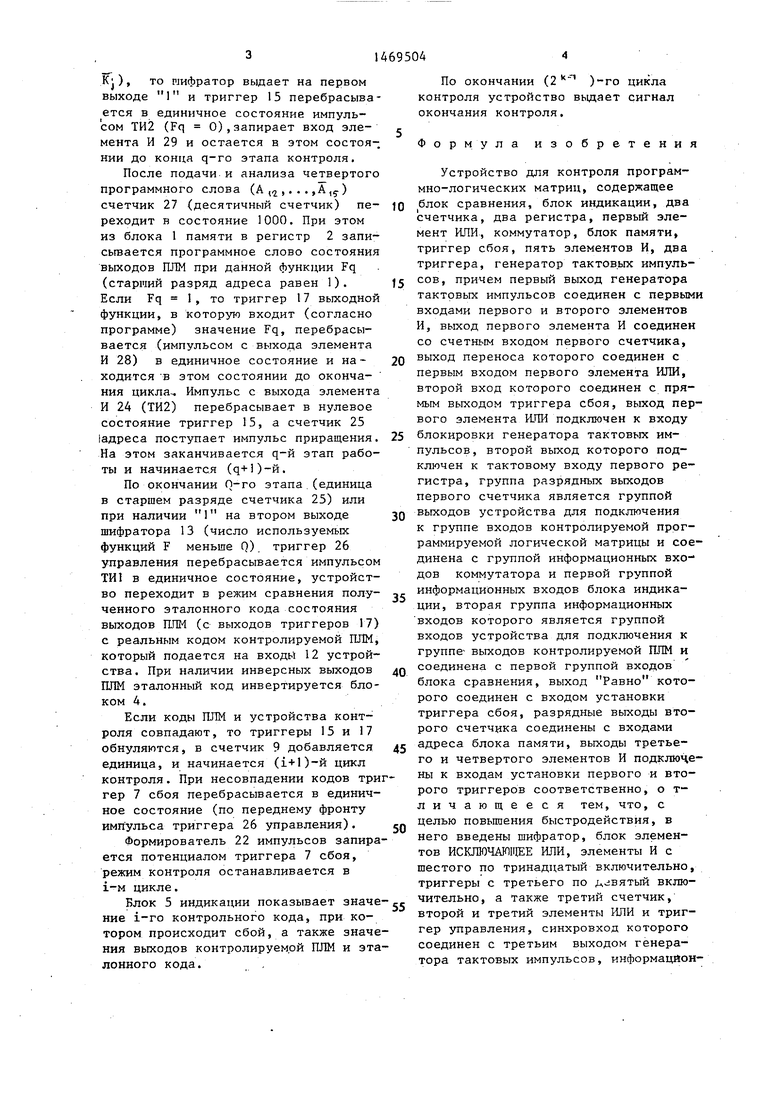

На фиг.1 приведена структурная схема устройства; на фиг.2 - временная диаграмма работы устройства.

Устройство содержит блок 1 памяти регистры 2 и 3, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4, блок 5 индикации, блок 6 сравнения, триггер 7 сбоя, элемент ИЛИ 8, счетчик 9, выход Ю устройства для подключения к входам ПЛМ, коммутатор 11, вход 12 устройства для подключения к выходам ПЛМ, шифратор 13, элемент И 14, триггер 15, группу элементов И .16, группу триггеров. 17, элемент ИЛИ 18, генератор 19 тактовых импульсов, элемент ИЛИ 20, генератора импульсов, состоящий из генератора 2.1 и формирователя 22 импульсов, элемента И 23 и 24, счетчик 25, триггер 26 управления, счетчик 27-, элементы И 28 и 29. Устройство работае;т следующим образом.

В блок 1 памяти заносится прог - рамма формирования функций ПЛМ, а в регистр 3 - некоторая константа, характеризующая состояние ее выходов (О - прямые, 1 - инверсные). Программа составляется с учетом прожига связей,не з аствующих в формировании заданных функций ПЛМ, и содержит (nH:2k) однобитных слов (Q - число элементов И матрицы; k - число входов матрицы; п - число выходов матрицы) . Отсутствию связей (прожиг) элемента матрицы в программе соответствует О, а наличию связей - 1.

се триггеры и счетчики устройства устанавливаются в нулевое состояние. Работа устройства синхронизирует- ся с помощью формирователя 22 импульсов, который вырабатывает две серии сдвинутых во времени импульсов (ТИ1 и ТИ2) и счетчика 27. На управляющие входы коммутатора 11 и на входы двух младших разрядов адреса блока 1 памяти подаются значения адреса с вьгхо- дов второго и третьего разрядов счетчика 27. Адрес функций И (Fq) задается счетчиком 25 (q 0,1 ,. .. ,) В каждом i-M (,2,...,2 ) цикле контроля на выходы 10 устройства (на входы контролируемой ПЛМ) и на информационные входы коммутатора 11 подается тестовый k-разряд- ный код с выходов счетчика 9. Каждый цикл состоит из О этапов, в каждом КЗ которых определяется требуемое значение функции Fq и соответствующие ей значения выходов ПЛМ (в со- ответствии с программой и контрольным кодом).

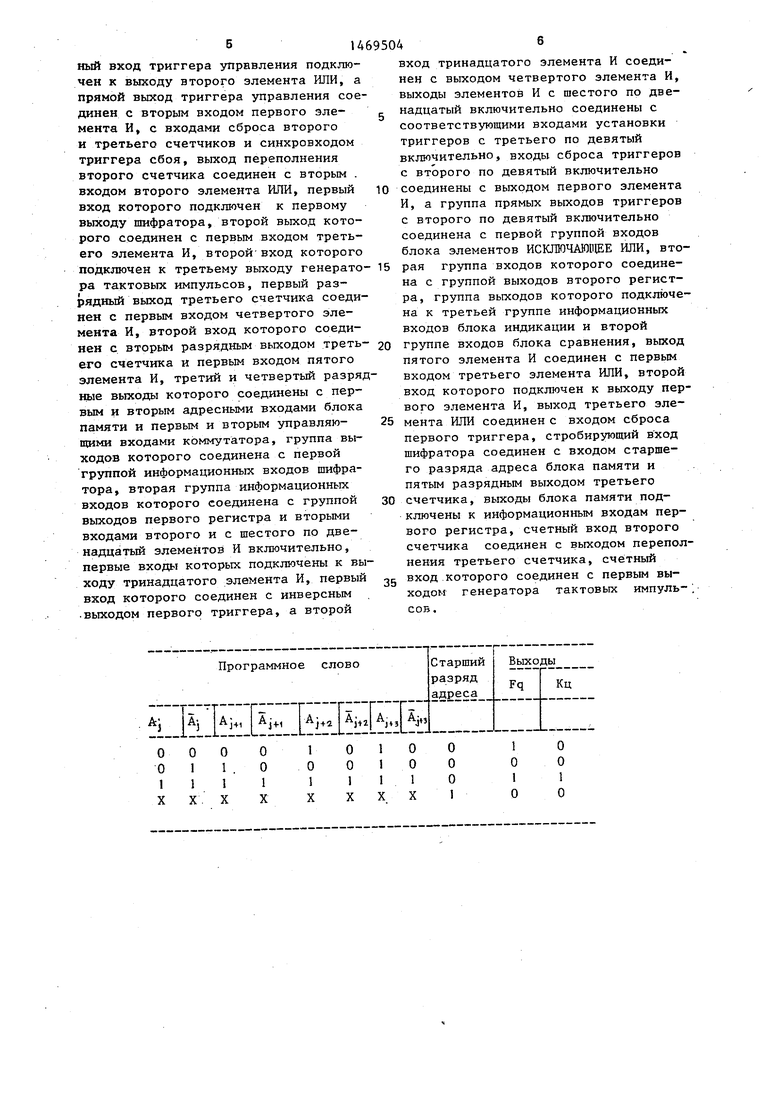

По импульсу ТИ1 в регистр 2 заносится из блока 1 восьмиразрядное слово, соответствующее прямым и инверс- ным значениям входных величин ПЛМ (Aj, Aj,.. .,Aj.,) в программе, которое сравнивается в шифраторе 13 со значениями четырех младших разрядов контрольного кода (Kj , .. . . ,) Примеры формирования значений выходов шифратора 13 в зависимости от программного слова для контрольного кода k;,... 0101 приведены в таблице.

Если в программе записано, -что данное значение входного сигнала (Aj . или А:) входит в логическое выражение для функции Fq, но отсутствует в контрольном коде (Kj или

Kj), то шифратор выдает на первом выходе 1 и триггер 15 перебрасыва- ется в единичное состояние импульсом ТИ2 (Fq О),запирает вход эле- мента И 29 и остается в этом состоя-. НИИ до конца q-ro этапа контроля.

После подачи и анализа четвертого

программного слова (А А,5-)

счетчик 27 (десятичный счетчик) пе- реходит в состояние 1000. При этом из блока 1 памяти в регистр 2 запи- сьгоается программное слово состояния выходов ПЛМ при данной Fq (старший разряд адреса равен 1). Если Fq 1, то триггер 17 выходной функции, в которую входит (согласно программе) значение Fq, перебрасывается (импульсом с выхода элемента И 28) в единичное состояние и на - ходится В этом состоянии до окончания цикла-. Импульс с выхода элемента И 24 (ТИ2) перебрасывает в нулевое состояние триггер 15, а счетчик 25 1адреса поступает импульс приращения. На этом заканчивается q-й этап работы и начинается (q+i)-й.

По окончании 0-го этапа (единица в старшем разряде счетчика 25) или

при наличии 1 на втором выходе

шифратора 13 (число используемых функций F меньше Q) триггер 26 управления перебрасывается импульсом ТИ1 в единичное состояние, устройство переходит в режим сравнения полу- ченного эталонного кода состояния выходов nJH-l (с выходов триггеров 17) с реальным кодом контролируемой ПЛМ, который подается на входы 12 устройства. При наличии инверсных выходов Ш1М эталонный код инвертируется блоком 4.

Если коды ПЛМ и устройства контроля совпадают, то триггеры 15 и 17 обнуляются, в счетчик 9 добавляется единица, и начинается (1+1)-й цикл контроля. При несовпадении кодов триг гер 7 сбоя перебрасывается в единичное состояние (по переднему фронту импульса триггера 26 управления).

Формирователь 22 импульсов запирается потенциалом триггера 7 сбоя, режим контроля останавливается в i-M цикле,

Блок 5 индикации показывает значение i-ro контрольного кода, при котором происходит сбой, а также значения выходов контролируемой ПЛМ и эталонного кода.

5 0 5

0

5 О

5 Q

По окончании ( )-го цикла контроля устройство выдает сигнал окончания контроля.

Формула изобретения

Устройство для контроля программно-логических матриц, содержащее блок сравнения, блок индикации, два счетчика, два регистра, первый элемент ИЛИ, коммутатор, блок памяти, триггер сбоя, пять элементов И, два триггера, генератор тактов.ых импульсов, причем первый выход генератора тактовых импульсов соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен со счетным входом первого счетчика, выход переноса которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с прямым выходом триггера сбоя, выход первого элемента ИЛИ подключен к входу блокировки генератора тактовых импульсов, второй выход которого подключен к тактовому входу первого регистра, группа разрядных выходов первого счетчика является группой выходов устройства для подключения к группе входов контролируемой программируемой логической матрицы и соединена с группой информационных входов коммутатора и первой группой информационных входов блока индикации, вторая группа информационных входов которого является группой входов устройства для подключения к группе- выходов контролируемой ПЛМ и соединена с первой группой входов блока сравнения, выход Равно которого соединен с входом установки триггера сбоя, разрядные выходы второго счетчика соединены с входами адреса блока памяти, выходы третьего и четвертого элементов И подклк)че- ны к входам установки первого и второго триггеров соответственно, о т- личающееся тем, что, с целью повышения быстродействия, в него введены шифратор, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И с шестого по тринадцатый включительно, триггеры с третьего по девятый включительно, а также третий счетчик, второй и третий элементы ИЛИ и триггер управления, синхровход которого соединен с третьим выходом генератора тактовых импульсов, информацйонный вход триггера управления подключен к выходу второго элемента ИЛИ, а прямой вькод триггера управления соединен с BTOpbiM входом первого элемента И, с входами сброса второго и третьего счетчиков и синхровходом триггера сбоя, выход переполнения второго счетчика соединен с вторым . входом второго элемента ИЛИ, первый вход которого подключен к первому выходу шифратора, второй выход которого соединен с первым входом третьего элемента И, второй-вход которого

10

вход тринадцатого элемента И соединен с выходом четвертого элемента И, выходы элементов И с шестого по двенадцатый включительно соединены с соответствующими входами установки триггеров с третьего по девятый включительно, входы сброса триггеров с второго по девятый включительно соединены с выходом первого элемента И, а группа прямых выходов триггеров с второго по девятый включительно соединена с первой группой входов блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, втоподключен к третьему выходу генерато- 15 рая группа входов которого соединера тактовых импульсов, первый разрядный выход третьего счетчика соединен с первым входом четвертого элемента И, второй вход которого соедина с группой выходов второго регистра, группа выходов которого подключена к третьей группе информационных входов блока индикации и второй

иен с вторым разрядным выходом треть- 20 группе входов блока сравнения, вьпсод

его счетчика и первым входом пятого элемента И, третий и четвертый разряд- m,je выходы которого соединены с первым и вторым адресными входами блока памяти и первьм и вторым управляющими входами коммутатора, группа выходов которого соединена с первой группой информационных входов шифратора, вторая группа информационных входов которого соединена с группой выходов первого регистра и вторыми входами второго и с шестого по двенадцатый элементов И включительно, первые входы которых подключены к выходу тринадцатого элемента И, первый вход которого соединен с инверсным выходом первого триггера, а второй

пятого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу пер вого элемента И, выход третьего эле- 25 мента ИЛИ соединен с входом сброса первого триггера, стробирующий вход шифратора соединен с входом старшего разряда адреса блока памяти и пятым разрядньм выходом третьего счетчика, выходы блока памяти подключены к информационным входам первого регистра, счетный вход второго счетчика соединен с выходом перепол нения третьего счетчика, счётный вход которого соединен с первым выходом генератора тактовых импульсов.

3D

35

вход тринадцатого элемента И соединен с выходом четвертого элемента И, выходы элементов И с шестого по двенадцатый включительно соединены с соответствующими входами установки триггеров с третьего по девятый включительно, входы сброса триггеров с второго по девятый включительно соединены с выходом первого элемента И, а группа прямых выходов триггеров с второго по девятый включительно соединена с первой группой входов блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторая группа входов которого соединена с группой выходов второго регистра, группа выходов которого подключена к третьей группе информационных входов блока индикации и второй

группе входов блока сравнения, вьпсод

пятого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу первого элемента И, выход третьего эле- мента ИЛИ соединен с входом сброса первого триггера, стробирующий вход шифратора соединен с входом старшего разряда адреса блока памяти и пятым разрядньм выходом третьего счетчика, выходы блока памяти подключены к информационным входам первого регистра, счетный вход второго счетчика соединен с выходом переполнения третьего счетчика, счётный вход которого соединен с первым выходом генератора тактовых импуль; сов.

тио ГlЛJlПЛЛШШJlШlПJLПJШЛШlrl rULJUUUULJlJlJlJUL rm JlJT JTJLnJlJlJU

c75coг J Jг JГ su I,,ГiГ(

cncii | I 1 1 L-л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1983 |

|

SU1160414A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| Устройство для имитации отказов и сбоев ЭВМ | 1987 |

|

SU1564628A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для автоматической проверки функционирования программируемых логических матриц. Цель - увеличение быстродействия, для достижения которой устройство содержит блок сравнения 6, блок индикации 5, три счетчика 9,25,27, регистры 2,3, эле

Фив.I

| Устройство для обнаружения неисправностей цифровых систем | 1973 |

|

SU561965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1160414A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-30—Публикация

1987-08-24—Подача