Изобретение относится к вычислительной технике и может быть использовано в специализированных системах обработки сигналов изображений высокой производительности.

Известен систолический процессор дискретного преобразования Фурье - ДПФ (авт.св. СССР N 1363343, кл. G 06 F 15/332, 30.12.87), выбранный в качестве прототипа и содержащий информационные входы, входной регистр, первую (систолическую) матрицу, операционные блоки первой матрицы, вторую (систолическую) матрицу, операционные блоки второй матрицы, сумматор, каналы, информационные выходы, блок синхронизации.

Недостатком данного устpойства является невысокая отказоустойчивость.

Техническим результатом изобретения является повышение отказоустойчивости процессора за счет изменения его структуры.

Сущность изобретения заключается в следующем. Процессор выполняет двумерное преобразование Фурье. Для выполнения ДПФ необходимо производить два действия - сложение и умножение. Непозиционная система счисления, в частности система остаточных классов (СОК), позволяет выполнять рациональные операции (сложение, умножение), причем с большой скоростью. Данная система счисления обладает основным достоинством - независимостью образования разрядов числа, в силу чего каждый разряд несет информацию обо всем исходном числе. Отсюда вытекает возможность их независимой параллельной обработки.

Введение двух дополнительных контрольных оснований (при условии, что pn-1˙ pn < pn+1˙ pn+2, где pi - основания СОК; n - количество рабочих оснований; pn+1 и pn+2 - контрольные основания) позволяет обнаруживать ошибки в цифрах не только по двум любым основаниям, но даже и по трем. Введение блока преобразования двоичного кода в код СОК обеспечивает преобразование значений входных данных Х(к)по n+2 основаниям СОК ( (K ∈  ) ). Введение двух блоков преобразования двоичного кода весовых множителей (W(d), d ∈

) ). Введение двух блоков преобразования двоичного кода весовых множителей (W(d), d ∈  ) в код СОК обеспечивает преобразование значений весовых множителей по n+2 основаниям СОК. Введение n+1 систолических матриц преобразования Фурье по первой координате обеспечивает получение значений одномерного ДПФ по основаниям СОК. Введение n+1 дополнительных сумматоров обеспечивает получение сумм по основаниям СОК. Введение n+1 входных регистров обеспечивает запись значений Х(к) по основаниям СОК. Введение n+1 систолических матриц преобразования Фурье по второй координате обеспечивает получение значения двумерного преобразования Фурье по основаниям СОК. Введение n+1 блоков сдвиговых регистров обеспечивает хранение промежуточных значений. Введение бока преобразования кода СОК в двоичный код обеспечивает преобразование значений двумерного преобразования Фурье, представленного в СОК, в двоичный код. Введение блока обнаружения ошибки обеспечивает обнаружение ошибки по основаниям СОК. Введение блока переключений обеспечивает необходимые переключения при обнаружении ошибки. Таким образом, предлагаемое техническое решение обладает существенными отличиями.

) в код СОК обеспечивает преобразование значений весовых множителей по n+2 основаниям СОК. Введение n+1 систолических матриц преобразования Фурье по первой координате обеспечивает получение значений одномерного ДПФ по основаниям СОК. Введение n+1 дополнительных сумматоров обеспечивает получение сумм по основаниям СОК. Введение n+1 входных регистров обеспечивает запись значений Х(к) по основаниям СОК. Введение n+1 систолических матриц преобразования Фурье по второй координате обеспечивает получение значения двумерного преобразования Фурье по основаниям СОК. Введение n+1 блоков сдвиговых регистров обеспечивает хранение промежуточных значений. Введение бока преобразования кода СОК в двоичный код обеспечивает преобразование значений двумерного преобразования Фурье, представленного в СОК, в двоичный код. Введение блока обнаружения ошибки обеспечивает обнаружение ошибки по основаниям СОК. Введение блока переключений обеспечивает необходимые переключения при обнаружении ошибки. Таким образом, предлагаемое техническое решение обладает существенными отличиями.

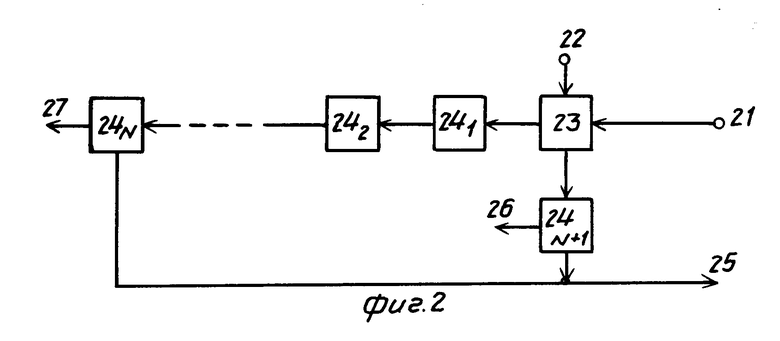

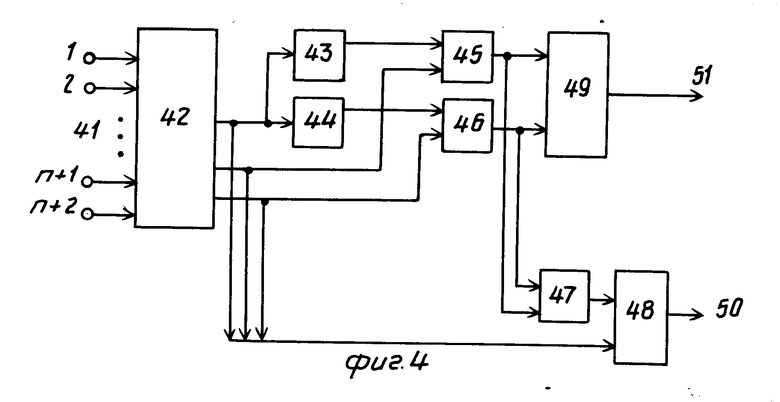

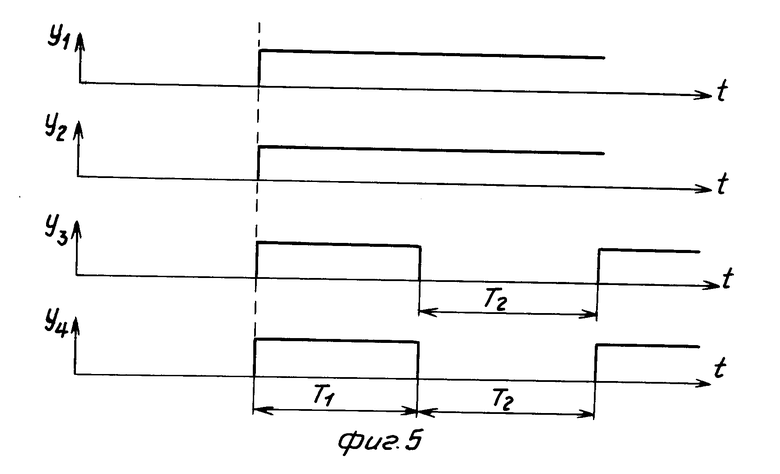

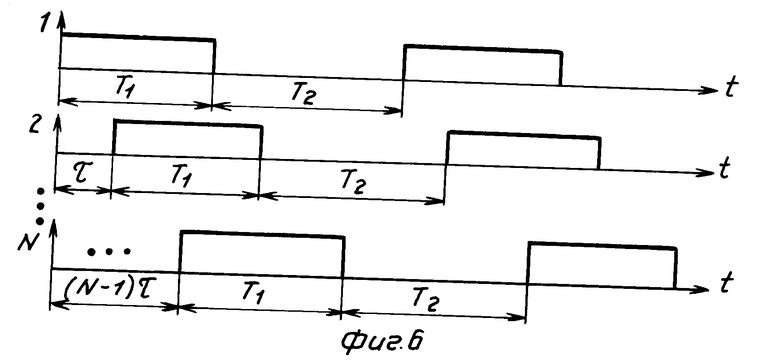

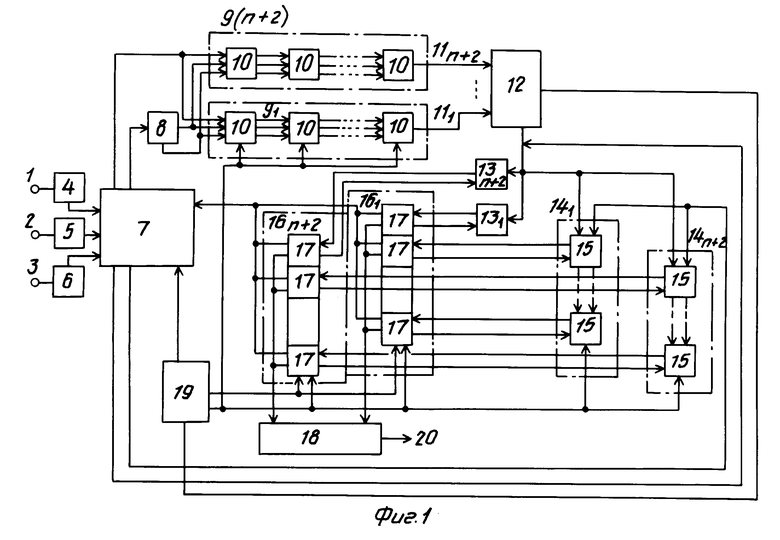

На фиг.1 представлена функциональная схема систолического отказоустойчивого процессора ДПФ; на фиг. 2 - функциональная схема канала блока сдвиговых регистров; на фиг. 3 - функциональная схема блока переключений; на фиг. 4 - функциональная схема блока обнаружения ошибки; на фиг. 5 показаны временные диаграммы соотношения управляющих сигналов У1...У4 при обнаружении ошибки; на фиг. 6 - временные диаграммы поступления управляющего сигала У5 на входы каналов.

Систолический отказоустойчивый процессор ДПФ (фиг.1) содержит информационные входы 1, 2, 3, два блока 4 и 6 преобразования двоичного кода весовых множителей в код СОК, блок 5 преобразования двоичного кода в код СОК, блок 7 переключений, блок 8 входных регистров, n+2 систолических матриц 9 преобразования Фурье по первой координате, операционные блоки 10 систолических матриц преобразования Фурье по первой координате, выходы 11 первых (систолических) матриц, блок 12 обнаружения ошибки, n+2 сумматоров 13, n+2 систолических матриц 14 преобразования Фурье по второй координате, операционные блоки 15 систолических матриц преобразования Фурье по второй координате, n+2 блоков 16 сдвиговых регистров по N каналов 17 в каждом, блок 18 преобразования кода СОК в двоичный код, блок 19 синхронизации, выход 20.

Входы 1, 2, 3 процессора соответственно подключены к входам блоков 4, 5, 6 преобразования двоичного кода в код СОК, выходы которых подключены к информационным входам блока 7 переключений. Первый выход блока 7 подключен к первым входам систолических матриц 9 преобразования Фурье по первой координате, а второй выход - к входам блока 8 входных регистров, выходы которого подсоединены к вторым и третьим входам систолических матриц 9. Выходы 11 матриц 9 подключены к входам блока 12 обнаружения ошибки, первый информационный выход которого объединен с третьим выходом блока 7 переключений и подключен к входам n+2 сумматоров 13 и к первым входам систолических матриц 14 преобразования Фурье по второй координате, на вторые входы которых подключен четвертый выход блока 7 переключений. Второй выход блока 12 обнаружения ошибки подсоединен к входу управления блока 19 синхронизации, первый выход которого подключен к управляющему входу блока 7 переключений. Тактовые входы операционных блоков первых и вторых матриц, блоков сдвиговых регистров объединены и подключены к тактовому выходу блока 19 синхронизации. Выходы n+2 сумматоров 13 подключены к первым информационным входам n+2 блоков 16 сдвиговых регистров, первые выходы которых подключены к вторым входам сумматоров 13. Третьи выходы j-х операционных блоков 15 систолических матриц 14 подключены соответственно к (j+1)-м информационным входам блоков 16 сдвиговых регистров, а (j+1)-е выходы блоков 16 подсоединены к третьим входам j-х операционных блоков 15 систолических матриц преобразования Фурье по второй координате. Вторые выходы блоков 16 сдвиговых регистров подключены к четвертому информационному входу блока 7 переключений. Входы управления блоков 16 сдвиговых регистров объединены и подключены к третьему выходу блока 19 синхронизации. Третьи выходы блоков 16 сдвиговых регистров подключены к входу блока 18 преобразования кода СОК в двоичный код, выход которого является информационным выходом 20 процессора.

Блок 16 сдвиговых регистров содержит N каналов 17, каждый из которых включает в себя (фиг.2) информационный вход 21, вход 22 управления, коммутатор 23, регистры 24, информационные выходы 25, 26, 27. Причем информационный вход 21 подключен к входу коммутатора 23, управляющий вход которого подключен к входу 22 управления. Первый и второй выходы коммутатора 23 подключены к регистрам 24. Первый выход регистра 24, подключенного к второму выходу коммутатора, является выходом 26 блока, а второй выход подключен к выходу 25. Регистры 24 подсоединены между собой последовательно. Выходы N-го регистра являются выходами 25 и 27 блока сдвиговых регистров.

Блок 7 переключений (фиг.3) содержит информационные входы 28, 29, 30, 31, вход 32 управления, n+2 коммутаторов 33, n+2 коммутаторов 34, n+2 мультиплексоров 35, n+2 мультиплексоров 36, информационные выходы 37, 38, 39, 40. Информационные входы 28 и 29 соответственно подключены к входам n+2 коммутаторов 34 и n+2 коммутаторов 33, первые выходы которых подключены соответственно к выходам 38 и 37 блока. Вторые выходы коммутаторов 33 подключены к вторым входам мультиплексоров 35, первые входы которых подключены к информационному входу 31. Вторые выходы n+2 коммутаторов 34 подключены к вторым входам n+2 мультиплексоров 36, первые входы которых подключены к информационному входу 30. Выходы мультиплексоров 35 и 3 подключены соответственно к выходам 39 и 40 блока. Управляющие входы коммутаторов 33, 34 мультиплексоров 35, 36 подключены к входу 32 управления блока.

Блок 12 обнаружения ошибки (фиг.4) содержит информационные входы 41, регистр 42, блоки 43 и 44 модульной свертки, сумматоры 45 и 46, элемент ИЛИ-НЕ 47, блок 48 элементов И, элемент ИЛИ 49, информационный выход 50, выход 51 управления. Информационные входы 41 подключены к входам регистра 42, предназначенного для хранения числа, блоки 43 и 44, предназначенные для вычисления остатков числа по контрольным основаниям, подключены к первому выходу регистра 42. Входы сумматора 45 подключены к выходу блока 43 модульной свертки и к второму выходу регистра 42. Входы сумматора 46 подключены к выходу блока 44 модульной свертки и третьему выходу регистра 42. Выходы сумматоров 45 и 46 подключены к входам элементов ИЛИ-НЕ 47 и ИЛИ 49. Выход элемента ИЛИ-НЕ 47 подключен к первым входам элементов И блока 48, вторые входы которых подсоединены соответственно к выходам регистра 42. Выходы блока 48 и элемента ИЛИ 49 являются соответственно выходами 50 и 51 блока.

Процессор работает следующим образом.

Исходные данные (Х(к)) и весовые множители W1, W2 поступают на входы 1, 2, 3 процессора. Так как на вход управления блока 19 синхронизации с выхода блока 12 обнаружения ошибки управляющих сигналов не поступало, то на первом выходе блока 19 появляется совокупность управляющих сигналов У1, У2, У3, У4 (причем У1 = 0, У2 = 0, У3 = 0, У4 = 0), которая поступает на входы коммутаторов 33, 34, мультиплексоров 35, 36, а с третьего выхода блока 19 поступает сигнал У5 = 0 на входы коммутаторов 23. Исходные данные Х и W1 преобразуются в код СОК в блоках 5 и 4 и через коммутаторы 33 и 34 блока 7 переключений поступают соответственно на первые входы систолических матриц 9 преобразования Фурье по первой координате (значения Wk-1) и на входы блока 8 входных регистров, а через них на вторые и третьи входы первых (систолических) матриц 9 (значения Хk). После загрузки строки данных Хk размером N и поступления весовых множителей Wk-1 систолические матрицы 9 преобразования Фурье по первой координате выполняют одновременное преобразование Фурье по основаниям СОК вида

С1 = x1 + W0(x2 + W0(x3 + W0(x4 + ... + W0xN)));

C2 = x1 + W1(x2 + W1(x3 + W1(x4 + ... + W1xN)));

CN = x1 + WN-1(x2 + WN-1(x3 + WN-1(x4 + ... + WN-1xN))), где W = exp(-j2 π/N).

Отсчеты Сk (k =  ) одномерного ДПФ по строке данных поступают на входы блока 12 обнаружения ошибки. Суть его работы заключается в следующем.

) одномерного ДПФ по строке данных поступают на входы блока 12 обнаружения ошибки. Суть его работы заключается в следующем.

Пусть на его вход поступает число Cj = ( α1, α2, ..., α n+1, α n+2), где α i - остаток числа по модулю pi (i =  ). Основания pn+1 и pn+2 - контрольные. На входы блоков 43 и 44 (фиг.4) с первого выхода регистра 42 подается число Cj = ( α1, α2,..., α n) без остатков αn+1 и α n+2 с образованием на их выходах сигналов, соответствующих величинам

). Основания pn+1 и pn+2 - контрольные. На входы блоков 43 и 44 (фиг.4) с первого выхода регистра 42 подается число Cj = ( α1, α2,..., α n) без остатков αn+1 и α n+2 с образованием на их выходах сигналов, соответствующих величинам

αn+11 ≡ λ1(1) α1+ λ 2(1) α2+ ... + λ n(1) αn(mod pn+1);

αn+21 ≡ λ1(2) α1+ λ2(2) α2+ ... + λn(2)αn(mod pn+2), где λi(1) и λ i(2) - константы системы счислены. Остаток αn+1 числа Cjпо контрольному основанию αn+1 с второго входа регистра 42 и величина αn+1 с выхода блока 43 модульной свертки подаются на входы первого сумматора 45 с образованием на его выходе синдрома ошибки, равного

δ1 = αn+1 - α n+11(mod pn+1 ).

Остаток αn+2 числа Cj с третьего выхода регистра 42 и величина αn+21 с выхода блока 44 модульной свертки подаются на входы сумматора 46 с образованием на его выходе синдрома ошибки, равного

δ2 ≡ αn+2 - α n+21(mod pn+2).

Если число С не содержит ошибки, то величины δ1 и δ2 равны нулю. Данные значения поступают на входы элемента ИЛИ-НЕ 47 и элемента ИЛИ 49, с выхода которого не поступает сигнал на вход управления блока 19 синхронизации. С выхода элемента ИЛИ-НЕ 47 сигнал подается на входы элементов И блока 48 и значения числа Сj через блок 48 поступают на выход 50 блока 12 обнаружения ошибки. Затем значения Ck (k =  ) поступают на входы сумматоров 13 и на первые входы систолических матриц 14 преобразования Фурье по второй координате, на вторые входы которых подаются значения Wm-1, представленные в СОК, поступающие с входа 3 процессора через блок 6 преобразования кода весовых множителей в код СОК и мультиплексор 36 блока 7 переключений. При этом вторые матрицы 14 и сумматоры 13 и связанные с ними блоки 16 сдвиговых регистров выполняют преобразование Фурье матрицы данных по второй координате. После обработки N строк данных по N отсчетам сформирована матрица результатов двумерного преобразования Фуре по основаниям СОК:

) поступают на входы сумматоров 13 и на первые входы систолических матриц 14 преобразования Фурье по второй координате, на вторые входы которых подаются значения Wm-1, представленные в СОК, поступающие с входа 3 процессора через блок 6 преобразования кода весовых множителей в код СОК и мультиплексор 36 блока 7 переключений. При этом вторые матрицы 14 и сумматоры 13 и связанные с ними блоки 16 сдвиговых регистров выполняют преобразование Фурье матрицы данных по второй координате. После обработки N строк данных по N отсчетам сформирована матрица результатов двумерного преобразования Фуре по основаниям СОК:

IK1 = C1K + W0(C2K + W0(C3K + W0(C4K + ... + W0CNK)));

IK2 = C1K + W1(C2K + W1(C3K + W1(C4K + ... + W1CNK)));

.

.

.

IKN =C1K + WN-1(C2K + WN-1(C3K + +WN-1(C4K + ... + WN-1CKN))). где W = exp(-j2 π/N).

Отсчеты двумерного ДПФ, представленные в коде СОК, поступают на вход блока 18 преобразования кода СОК в двоичный код, выход которого является выходом 20 процессора.

При обнаружении ошибки ( δ1 или δ2 не равны нулю) с выхода блока 12 обнаружения ошибки поступает сигнал на вход управления блока 19 синхронизации, на первом выходе которого появляется следующая совокупность управляющих сигналов: У1 = 1, У2 = 1, У3 = 1, У4 = 1. При поступлении на управляющие входы коммутаторов 33 управлюящего сигнала У1= 1 вход 29 (по которому поступают Хk) блока 7 подключается к вторым входам мультиплексоров 35. При поступлении на управляющие входы коммутаторов 34 управляющего сигнала У2 = 1 вход 28 (по которому поступают Wk-1) блока 7 подключается к вторым входам мультиплексоров 36. При поступлении на управляющие входы мультиплексоров 35 управляющего сигнала У3 = 1 вторые входы подключаются к выходам и значения Хk, представленные по основаниям СОК, поступают на входы сумматоров 13 и первые входы вторых (систолических) матриц 14. При поступлении на управляющие входы мультиплексоров 36 управляющего сигнала У4 = 1 значения Wk-1 с вторых входов коммутаторов поступают на вторые входы вторых (систолических) матриц 14. Одновременно с этим с третьего выхода блока 19 синхронизации подается сигнал У5 = 1, который поступает на управляющие входы коммутаторов 23, которые подключают (фиг.2) информационные входы 21 через регистр 24 к первым выходам 25. При этом вторые матрицы 14, сумматоры 13, блоки 16 сдвиговых регистров выполняют одномерное преобразование Фурье по строке данных. По окончании выполнения одномерного ДПФ с выходов блока 19 синхронизации поступает следующая последовательность управляющих сигналов: У1 = 1, У2 = 2, У3 = 0, У4 = 0 (фиг.5). По этим командам через мультиплексоры 35 и 36 на входы сумматоров 13 и входы вторых (систолических) матриц 14 поступают значения Сk и Wm-1 (с входа 30 блока 7). При поступлении управляющего сигнала У5 = 0 (временные диаграммы представлены на фиг.6) коммутаторы 23 подключат N регистров 24 и сумматоры 13, вторые (систолические) матрицы 14, блоки 16 сдвиговых регистров выполняют преобразования Фурье по второй координате. Следовательно, при обнаружении ошибки процессор работает по схеме: одномерное ДПФ == двумерное ДПФ. Время выполнения одномерного ДПФ текущей строки составляет Т1 = 2(N-1)τ, где τ - время выполнения базовой операции операционным блоком. Под базовой операцией операционного блока понимаются операции умножения, сложения и передачи операндов, реализуемые отдельным блоком. Время выполнения двумерного ДПФ строки Т2 = 2N τ .

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ С КОРРЕКЦИЕЙ ОШИБКИ | 1992 |

|

RU2018950C1 |

| СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДЛЯ ВЫЧИСЛЕНИЯ ПОЛИНОМИАЛЬНЫХ ФУНКЦИЙ | 1991 |

|

RU2015549C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММ ПАРНЫХ ПРОИЗВЕДЕНИЙ | 1992 |

|

RU2012041C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ ОШИБОК В ИЗБЫТОЧНОМ МОДУЛЯТОРНОМ КОДЕ | 1991 |

|

RU2022472C1 |

| Систолический процессор цифровой обработки сигналов | 1987 |

|

SU1471200A1 |

| Многоканальный систолический процессор для вычисления полиномиальных функций | 2020 |

|

RU2737236C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД С ПЕРЕСЧЕТОМ ОРТОГОНАЛЬНЫХ БАЗИСОВ | 2005 |

|

RU2298873C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ ОШИБОК В ИЗБЫТОЧНОМ МОДУЛЯРНОМ КОДЕ | 1991 |

|

RU2015620C1 |

| УСТРОЙСТВО СПЕКТРАЛЬНОГО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОШИБОК В КОДАХ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ | 2005 |

|

RU2301441C2 |

| Устройство коррекции ошибок в модулярном коде на основе расширения системы оснований | 2017 |

|

RU2652446C1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных системах обработки сигналов изображений высокой производительности в системе остаточных классов. Систолический отказоустойчивый процессор дискретного преобразования Фурье содержит два блока 4, 6 преобразования двоичного кода весовых множителей в код СОК, блок 5 преобразования двоичного кода в код СОК, блок 7 переключений, блок 8 входных регистров, n + 2 систолических матриц 9 преобразования Фурье по первой координате с операционными блоками 10, блок 12 обнаружения ошибки n + 2 сумматоров 13, n + 2 систолических матриц 14 преобразователя Фурье по второй координате с операционными блоками 15, n + 2 блоков 16 сдвиговых регистров по N каналов 17 в каждом, блок 18 преобразования кода СОК в двоичный код и блок 19 синхронизации, соединенные между собой функционально. 3 з.п.ф-лы, 6 ил.

операционного блока первых систолических матриц преобразования Фурье по первой и второй координатам соединены соответственно с входом (i + 1)-го операционного блока соответственно тех же матриц, отличающийся тем, что в него введены блок преобразования двоичного кода в код системы остаточных классов, первый и второй блоки преобразования кода весовых множителей в код системы остаточных классов, блок переключений, n + 1 входных регистров, где n - число рабочих оснований в системе остаточных классов, n + 1 систолических матриц преобразования Фурье по первой координате, блок обнаружения ошибки, n + 1 систолических матриц преобразования Фурье по второй координате, n + 1 сумматоров, n + 1 блоков сдвиговых регистров и блок преобразования кода системы остаточных классов в двоичный код, причем входы блоков преобразования двоичного кода и кодов весовых множителей в коды системы остаточных классов являются информационными входами процессора, информационный выход которого соединен с выходом преобразователя кода системы остаточных классов в двоичный код, выходы блоков преобразования двоичного кода и кодов весовых множителей в коды системы остаточных классов соединены соответственно с первым, вторым и третьим информационными входами блока переключений, первый выход которого соединен с первыми информационными входами n + 2 систолических матриц преобразования Фурье по первой координате, вторые и третьи информационные входы которых соединены соответственно с первыми и вторыми выходами n + 2 входных регистров, входы которых соединены с вторым выходом блока переключений, третий выход которого соединен с информационным выходом блока обнаружения ошибки, входы которого соединены соответственно с выходами n + 2 систолических матриц преобразования Фурье по первой координате, информационный выход блока обнаружения ошибки соединен с первыми информационными входами n + 2 систолических матриц преобразования Фурье по второй координате и с первыми входами n + 2 сумматоров, выходы которых соединены с первыми информационными входами n + 2 блоков сдвиговых регистров, первые выходы которых соединены соответственно с вторыми входами n + 2 сумматоров, четвертый выход блока переключений соединен с вторыми информационными входами n + 2 систолических матриц преобразования Фурье по второй координате, третьи выходы операционных блоков которых соединены соответственно с второго по N-й входами n + 2 сдвиговых регистров, выходы которых соединены соответственно с третьими входами n + 2 систолических матриц преобразования Фурье по второй координате, тактовые входы систолических матриц преобразования Фурье по первой и второй координатам и n + 2 блоков сдвиговых регистров соединены с тактовым выходом блока синхронизации, первый и второй управляющие выходы которого соединены соответственно с входами управления блока переключений и n + 2 блоков сдвиговых регистров, а управляющий вход блока синхронизации соединен с управляющим выходом блока обнаружения ошибки, четвертый информационный вход блока переключений соединен с вторыми выходами n + 2 блоков сдвиговых регистров, третьи выходы которых соединены соответственно с входами блока преобразования кода системы остаточных классов в двоичный код.

операционного блока первых систолических матриц преобразования Фурье по первой и второй координатам соединены соответственно с входом (i + 1)-го операционного блока соответственно тех же матриц, отличающийся тем, что в него введены блок преобразования двоичного кода в код системы остаточных классов, первый и второй блоки преобразования кода весовых множителей в код системы остаточных классов, блок переключений, n + 1 входных регистров, где n - число рабочих оснований в системе остаточных классов, n + 1 систолических матриц преобразования Фурье по первой координате, блок обнаружения ошибки, n + 1 систолических матриц преобразования Фурье по второй координате, n + 1 сумматоров, n + 1 блоков сдвиговых регистров и блок преобразования кода системы остаточных классов в двоичный код, причем входы блоков преобразования двоичного кода и кодов весовых множителей в коды системы остаточных классов являются информационными входами процессора, информационный выход которого соединен с выходом преобразователя кода системы остаточных классов в двоичный код, выходы блоков преобразования двоичного кода и кодов весовых множителей в коды системы остаточных классов соединены соответственно с первым, вторым и третьим информационными входами блока переключений, первый выход которого соединен с первыми информационными входами n + 2 систолических матриц преобразования Фурье по первой координате, вторые и третьи информационные входы которых соединены соответственно с первыми и вторыми выходами n + 2 входных регистров, входы которых соединены с вторым выходом блока переключений, третий выход которого соединен с информационным выходом блока обнаружения ошибки, входы которого соединены соответственно с выходами n + 2 систолических матриц преобразования Фурье по первой координате, информационный выход блока обнаружения ошибки соединен с первыми информационными входами n + 2 систолических матриц преобразования Фурье по второй координате и с первыми входами n + 2 сумматоров, выходы которых соединены с первыми информационными входами n + 2 блоков сдвиговых регистров, первые выходы которых соединены соответственно с вторыми входами n + 2 сумматоров, четвертый выход блока переключений соединен с вторыми информационными входами n + 2 систолических матриц преобразования Фурье по второй координате, третьи выходы операционных блоков которых соединены соответственно с второго по N-й входами n + 2 сдвиговых регистров, выходы которых соединены соответственно с третьими входами n + 2 систолических матриц преобразования Фурье по второй координате, тактовые входы систолических матриц преобразования Фурье по первой и второй координатам и n + 2 блоков сдвиговых регистров соединены с тактовым выходом блока синхронизации, первый и второй управляющие выходы которого соединены соответственно с входами управления блока переключений и n + 2 блоков сдвиговых регистров, а управляющий вход блока синхронизации соединен с управляющим выходом блока обнаружения ошибки, четвертый информационный вход блока переключений соединен с вторыми выходами n + 2 блоков сдвиговых регистров, третьи выходы которых соединены соответственно с входами блока преобразования кода системы остаточных классов в двоичный код.

| Систолический процессор дискретного преобразования Фурье | 1986 |

|

SU1363243A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-02-20—Публикация

1992-06-15—Подача