10

Изобретение относится к вычислительной технике и может быть использвано в специализированньк системах обработки сигналов и и- ображений вы- сокой производительности.

Цель изобретения - расширение области применения за счет выполнения операций цифровой фильтрации.

На фиг. 1 представлена функционал ная схема процессора; на фиг, 2 - функциональная схема блока весовой обработки; на фиг. 3 - схема первого, третьего и четвертого коммутаторов; на фиг. 4 - схема второго комму татора.

Процессор (фиг. 1) содержит первый 1 и второй 2 информационные входы, первый 3, второй 4 и третий 5 входы коэффициентов, блок 6 весовой обработки, первую 7 и вторую 8 матрицы вычислительных блоков, блок 9 сдвиговых регистров, сумматор 10, блок 11 синхронизации, информационны выход 12 процессора.

Блок весовой обработки (фиг. 2) содержит входы 13 и 14 первого и второго операндов, информационные входы 15 и 16, вход 17 коэффициента, первый коммутатор 18, умножитель 19, второй коммутатор 20, элемент НЕ 21, третий коммутатор 22, четвертый коммутатор 23, узел регистров 24, умножитель 25, первый 26 и второй 27 выходы промежуточного результата, информационный выход 28 и вход 29 управления и синхронизации.

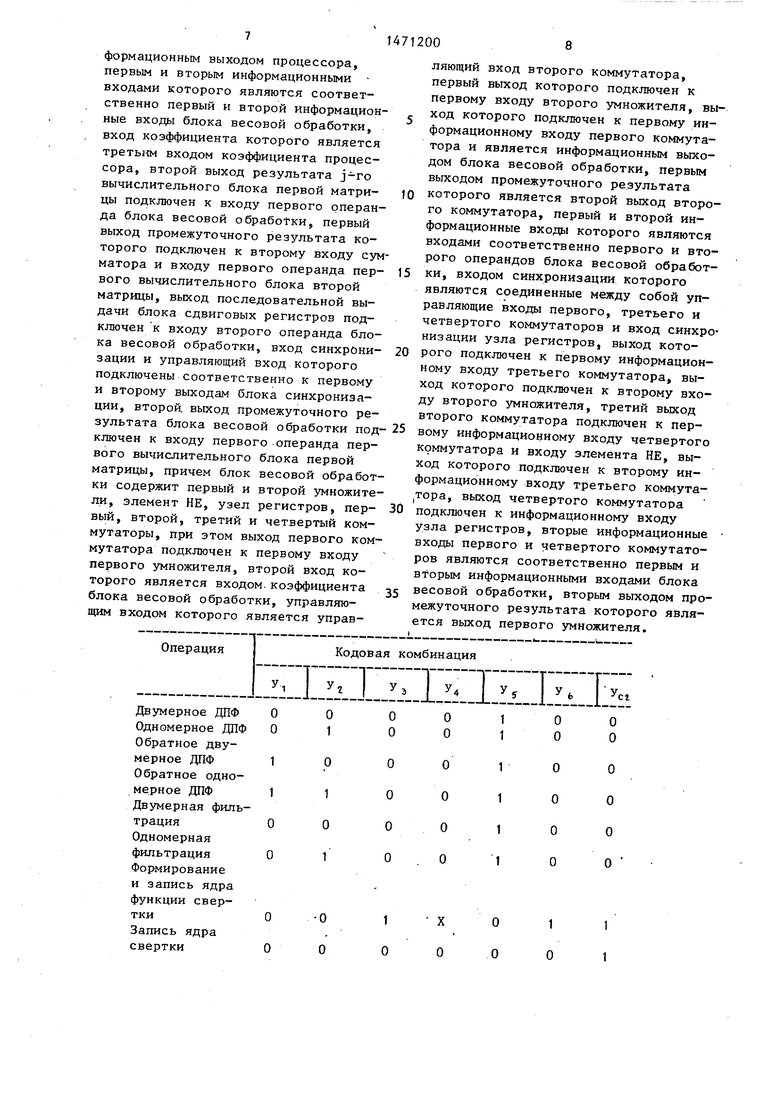

Первый, третий, четвертый ког«1му-- таторы (фиг. 3) содержат первый 30 и второй 31 входы, элементы И 32 и 33, управляющий вход 34, элемент НЕ 35, элемент ИЛИ 36 и выход 37.

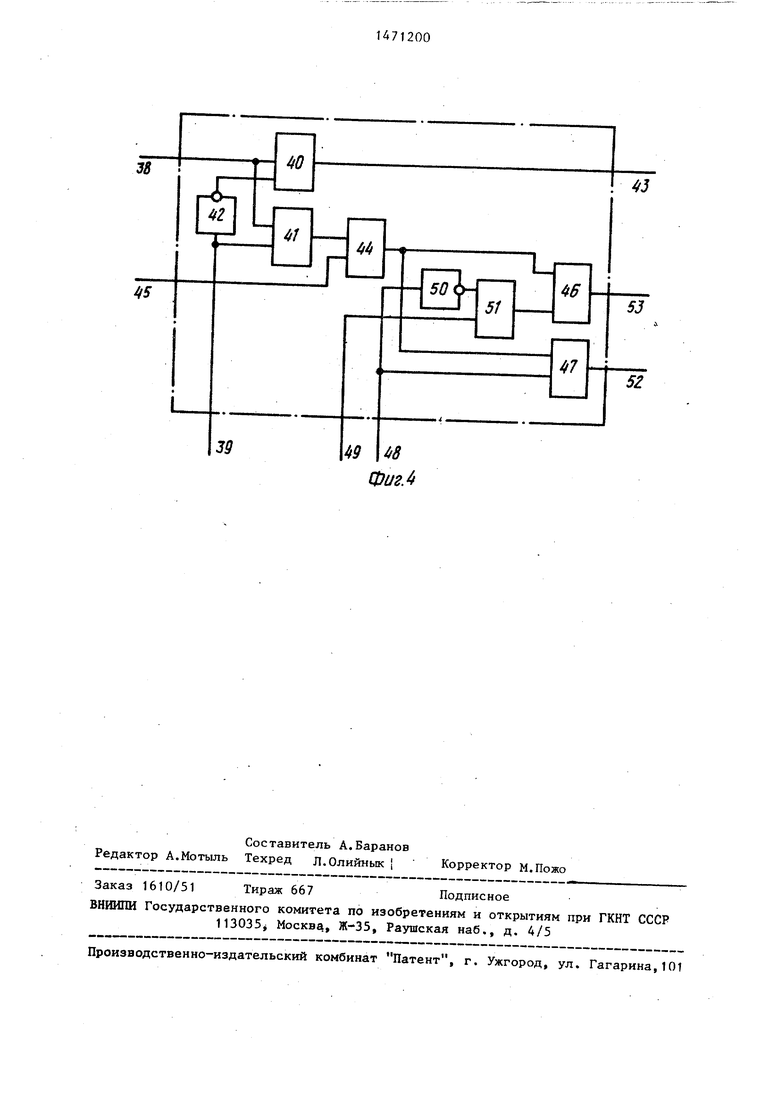

Второй коммутатор (фиг. 4) содержит вход 38, управляющий вход 39, элементы И 40 и 41, элемент НЕ 42, выход 43, элемент ШШ 44, вход 45, элементы И 46 и 47, управляющие входы 48 и 49, элемент НЕ 50, элемент ИЛИ 51, выходы 52 и 53.

Процессор работает следующим об- разом. ,

Пусть, например, вычисляется двумерная функция автокорреляции. При поступлении соответствующей команды на вход управления блока 11 синхро- низации ее код дешифрируется и в виде совокупности управляющих сигналов тУ yf У y t управления поступает на упраяляющие входы коммутаторов 18,

20, 22 и 23 блока 6 весовой обработки.

При поступлении на управляющий вход коммутатора 18 управляющего сигнала у О вход умножителя 19 . подключается к входу 15 блока весово обработки, соединенному с информационным входом 1 процессора. При этом на умножитель 19 поступает текущий отсчет исходных данных (К п 1,N; N - размер отрабатываемой матрицы). На вход умножителя 19 через вход 5 весовых множителей, подключенный к входу 17 блока весовой обработки, поступают симметрирующие весовые множители или весовые множители функции окна

(М-1)(п+К)при нечетном N

W - (n+k) при.четном N;

W при несимметричном спектреj при весовой обработке на входе.

Взвешенные или сфазированные отсчеты входных данных поступают с выхода умножителя 19 на вход систолической матрицы 7, подключенный к вы-, ходу 27 блока 6. После загрузки стро ки данных X размером N и при поступлении на вход систолической матрицы 7 с входа 3 весовых множителей весового множителя W первая систоличес- кая матрица выполняет одномерное преобразование Фурье вида

c,((x3+w4x -...+w x-))) V

;

Ci Cxi+W4x +w4x3+w4x +...+W xN)))

;

CT, X, (x +W - (xj+w (...

X,))) x,+W - (xi+W (x j+W (x,+ ....

+w 4,)))-w - ,

где W exp().

Отсчеты G|(k 1,N) одномерного ДПФ no строке данных поступают с выхода первой систолической матрицы 7 на вход 13 блока 6, к которому подключей вход второго коммутатора 20. При поступлении на управляющий вход коммутатора 20 управляющего сигнала у О выход второго коммутатора 20, соединенный с выходом 26 блока 6, подключается к входу второй систоли - ческой матрицы 8 и входу сумматора 10 При этом на вход весовых множителей поступают весовые множители вида W в темпе поступления данных с выхода 26 блока 6. При этом вторая матрица 8, сумматор 10 и связанный с ними блок 9 сдвиговых регистров выполняют преобразование Фурье матрицы данных по второй координате. После обработки N строк данных по N отсчетов будет сформирована матрица результатов двумерного преобразования Фурье

При поступлении на управляющий вход третьего коммутатора 22 управляющего сигнала О комплексно-сопряженные

отсчеты спектра с выхода элемента НЕ 21 поступают через третий коммутатор 22 на вход умножителя 25. Одновременно с этим при наличии управляющего сигнала у 1 на управляющем

входе коммутатора 20 отсчеты спектра у,с выхода второго коммутатора 20 поступают на вход умножителя 25. С выхода последнего результаты умножения Z XJ , представляющие собой спектральные отсчеты двумерной функции автокорреляции, поступают на выход 28 блока 6 и далее на информационный выход 12 процессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТОЛИЧЕСКИЙ ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1992 |

|

RU2029437C1 |

| Систолический процессор для двумерного дискретного преобразования Фурье | 1988 |

|

SU1608688A1 |

| Систолический процессор дискретного преобразования Фурье | 1986 |

|

SU1363243A1 |

| СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ С КОРРЕКЦИЕЙ ОШИБКИ | 1992 |

|

RU2018950C1 |

| Устройство для трехточечного быстрого преобразования Фурье | 1983 |

|

SU1107132A1 |

| Каскадное устройство для быстрого преобразования Фурье | 1983 |

|

SU1265794A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Устройство для дискретных ортогональных преобразований | 1986 |

|

SU1399764A1 |

| Систолический процессор для вычисления четырехточечного дискретного преобразования Фурье | 1988 |

|

SU1621043A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных системах обработки сигналов и изображений высокой производительности. Цель изобретения - расширение области применения путем выполнения цифровой фильтрации. Поставленная цель достигается благодаря тому, что в состав процессора входят информационные входы 1,2, первый, второй и третий входы 3-5 коэффициентов, блок 6 весовой обработки, матрицы 7,8 вычислительных блоков, блок 9 сдвиговых регистров, сумматор 10, блок 11 синхронизации, информационный выход 12 процессора. 4 ил., 1 табл.

Р

К1

:,,+w (c,+w4cj +w°(c,+...

4+W°C

, .к)));

Укг ik , +W (Сз, +W (С4К +..

+W C,)));

е-1

е-

,K+w (С,,+w ( (С4К + ..

с

NK

)))

Укм

C,,+W

N-1

(c,,+w (c,,+w (c,, + ..

с

NK

))).

где W exp t-j2if/N).

Отсчеты двумерного ДПФ с общего выходе блока 9 сдвиговых регистров поступают на вход 14 блока 6. При наличин на управляющем входе второго коммутатора 20 управляющего сигнала у j 1 результаты двумерного ДПФ через вход коммутатора поступают на выход данного коммутатора и с него на вход элемента НЕ 21 и вход четвертого коммутатора 23. Элементом НЕ 21 выполняется инверсия знака мнимой части операнда, что позволяет сформировать комплексно-сопряженное значет-

вне

У, aKe+Jsign(b,) (b,,).

где а

20 Для выполнения обратного преобразования Фурье, которое необходимо дл получения функции автокорреляции в пространственно-временной области, на вход блока 11 синхронизации посту пает следующая команда, соответствую щая выполнению обратного преобразова ния Фурье, которая также дешифрируется и интерпретируется в виде новой последовательности управляющих сигна лов ,. При поступлении си нала У 1 на управляющий вход первого коммутатора 18 происходит отклю чение входа первого .умножителя 19 от первого информационного входа 1, яв- 35 ляющегося входом 15 блока 6, а вход первого умножителя 19 подключается коммутатором 18 к выходу умножителя 25. При поступлении на вход 3 весовых множителей коэффициентов вида W на вход 4 весовых множителей ко эффициентов вида W- - и на вход 5 весовых множителей коэффициентов вида и сохранении управляющего сигнала у о на управляющем входе второго коммутатора 20 систолические.матрицы 7 и 8 в совокупности с блоком 9 и сумматором выполняют обратное преобразование Фурье над данными, поступающими из блока 6 в первую систолическую матрицу 7. При поступлении управляющего сигнала у j О на управляющий вход второго коммутатора 20 происходит отключение выхода указанного коммутаток

и b , соответственно действи-55 Р от входа элемента НЕ 21, и (незательная и мнимая части комплексного

отсчета выхода элемента НЕ 21

знакового разряда отсчеты посту,пают на вход третьего коммутатора 22.

висимо от управляющего сигнала у на управляющем входе второго коммутатора 20) отсчеты дггнных поступают с выхода коммутатора только на вход

25

0

0 5

20 Для выполнения обратного преобразования Фурье, которое необходимо для получения функции автокорреляции в пространственно-временной области, на вход блока 11 синхронизации поступает следующая команда, соответствующая выполнению обратного преобразования Фурье, которая также дешифрируется и интерпретируется в виде новой последовательности управляющих сигналов ,. При поступлении сигнала У 1 на управляющий вход первого коммутатора 18 происходит отключение входа первого .умножителя 19 от первого информационного входа 1, яв- 5 ляющегося входом 15 блока 6, а вход первого умножителя 19 подключается коммутатором 18 к выходу умножителя 25. При поступлении на вход 3 весовых множителей коэффициентов вида W на вход 4 весовых множителей коэффициентов вида W- - и на вход 5 весовых множителей коэффициентов вида и сохранении управляющего сигнала у о на управляющем входе второго коммутатора 20 систолические.матрицы 7 и 8 в совокупности с блоком 9 и сумматором выполняют обратное преобразование Фурье над данными, поступающими из блока 6 в первую систолическую матрицу 7. При поступлении управляющего сигнала у j О на управляющий вход второго коммутатора 20 происходит отключение выхода указанного коммутатоР от входа элемента НЕ 21, и (независимо от управляющего сигнала у на управляющем входе второго коммутатора 20) отсчеты дггнных поступают с выхода коммутатора только на вход

умножителя 25. При поступлении управляющего сигнала у 1 на управляющий вход третьего коммутатора 22 происходит отключение выхода элемента НЕ 21 от входа умножителя 25 и подключение выхода узла регистров 24 к входу умножителя 25. Одновременно из узла регистров 24 по адресу, указанному в поступившей в блок 11 синхронизации команде выбирается масштабная

выходе умножителя 25 сформирован результат, соответствующий отсчету функции автокорреляции, приведенной к заданному масштабу. С выхода умножителя 25 указанные отсчеты поступают на выход 28 блока 6 и далее на информационный выход 12 процессора.

При выполнении других функций, на пример свертки или при выполнении фильтрации, преобразования Фурье меняются команды, поступающие на вход блока 11 синхронизации. При этом операции свертки, автосвертки, фильтрации, авто- и взаимокорреляции требуют двух команд. Каждой команде соответствует определенный набор управляющих сигналов поступающих на управляющие входы коммутаторов 18, 20, 22 и 23. Кодовые комбинации этих сигналов, соответствующие различным операциям, реализуемым в процессоре, приведены в таблице.

При выполнении операций свертки и фильтрации весовые функции могут быть загружены в узел регистров 24 или через информационный вход 21 процессора, соединенный с входом 16 блока 6, либо через четвертый коммутатор 23 с выхода элемента НЕ 21. В последнем случае весовая функция в спектральной плоскости рассчитываетс через преобразование Фурье от некото

рой эталонной функции, заданной в ко- 45 тельного блока второй матрицы, выход

ординатной плоскости. Переключение каналов загрузки узла регистров 24 осуществляется четвертым коммутатором 23, а переключение режима запись- считывание - по управляющему сигналу , поступающему на управляющий вход узла регистров 24.

Работой процессора управляет стандартный блок 11 синхронизации, в который по входу управления поступает команда на выполнение той или иной операции в процессоре.

Данная команда в блоке 11 дешифрируется и сформированные управляющие

сигналы по выходу шины управления поступают на управляюи1ие входы коммутаторов 18, 20, 22 и 23 и узла регистров 24, куда поступают сигналы записи-считывания .

По выходу шины синхронизации блока 11 сигналы синхронизации, выработанные генератором тактовых импульсов

входы операционных блоков матриц 7 и 8, а также на тактовый вход блока 9 сдвиговых регистров. При поступлении тактового импульса организуется пересылка данных от второй матрицы 8 блоку 9 сдвиговых регистров и обратно и от сумматора 10 к бпоку 9 и наоборот.

рмула изобретения

Ф о

Систолический процессор цифровой . обработки сигналов, содержащий первую и вторую матрицы из N-1 (N - объем входной выборки) вычислительных

блоков, блок сдвиговых регистров, сумматор и блок синхронизации, причем первый выход результата и выход коэффициента i-ro (i 1,N-2) вычислительного, блока первой и второй матриц подключены соответственно к входам первого операнда и -коэффициента (i+ +1)-го вычислительного блока соответственно первой и второй матриц, входы коэффициентов первых вычислительных блоков первой и второй групп являются соответственно первым и вторым входами коэффициента процессора, вто- рой выход результата j-ro (,N-1) вычислительного блока второй матрицы подключен к (j+1)-My информационному входу блока сдвиговые: регистров, )-й выход которого подключен к входу второго операнда j-ro вычислисумматора подключен к первому информационному входу блока сдвиговых регистров, первый выход которого подключен к первому входу сумматора,

первый выход блока синхронизации подключен к тактовому входу блока сдвиговых регистров и входам синхронизации J-X вычислительных, блоков первой и второй матрицj отличающийс я тем, что, с целью расширения области применения за счет выполнения операций цифровой фильтрации, в него введен блок весовой обработки, информационный выход которого является инФормационным выходом процессора, первым и вторым информационными - входами которого являются соответственно первый и второй информационные входы блока весовой обработки, вход коэффициента которого является треть™ входом коэффициента процессора, второй выход результата j-ro вычислительного блока первой матрицы подключен к входу первого операнда блока весовой обработки, первый выход промежуточного результата которого подключен к второму входу сумматора и входу первого операнда первого вычислительного блока второй матрицы, выход последовательной выдачи блока сдвиговых регистров подключен к входу второго операнда блока весовой обработки, вход синхронизации и управляющий вход которого подключены соответственно к первому и второму выходам блока синхронизации, второй, выход промежуточного результата блока весовой обработки под- 25 ключен к входу первого .операнда первого вычислительного блока первой матрицы, причем блок весовой обработки содержит первый и второй умножители, элемент НЕ, узел регистров, пер- 30 выи, второй, третий и четвертый комутаторы, при этом выход первого комутатора подключен к первому входу ервого умножителя, второй вход коорого является входом, коэффициента лока весовой обработки, управляюим входом которого является управ147

20

35

Операция

Кодовая комбинация

Двумерное ДПФ О о Одномерное ДПФ О 1 Обратное двумерное ДПФ 1 о Обратное одномерное ДПФ 1 1 Двумерная фильтрация о о Одномерная

фильтрация О 1 Формирование и запись ядра функции сверткио -О Запись ядра свертки О О

.jAj l3ZlT LTrii

.--я.

о

О

О

о

о о

о

о

1

о

X

о

о о

1 о

8

15

2530

fO

20

35

ляющий вход второго коммутатора первый выход которого подключен к первому входу второго умножителя, выход которого подключен к первому информационному входу первого коммутатора и является информационным выходом блока весовой обработки, первым выходом промежуточного результата которого является второй выход второго коммутатора, первый и второй информационные входы которого являются входами соответственно первого и второго операндов блока весовой обработки, входом синхронизации которого являются соединенные между собой управляющие входы первого, третьего и четвертого коммутаторов и вход синхронизации узла регистров, выход которого подключен к первому информационному входу третьего коммутатора, выход которого подключен к второму вхо- ДУ второго умножителя, третий выход второго коммутатора подключен к первому информационному входу четвертого коммутатора и входу элемента НЕ, выход которого подключен к второму информационному входу третьего коммута- ,тора, выход четвертого коммутатора подключен к информационному входу узла регистров, вторые информационные входы первого и четвертого коммутаторов являются соответственно первым и вторым информационными входами блока весовой обработки, вторым выходом промежуточного результата которого является выход первого умножителя.

--я

О

о

о о

о

о

X

о

о о

о

Г1

J2

J533

ГЪ IP

3it

фиг.З

37

J

Фи2.

Авторы

Даты

1989-04-07—Публикация

1987-06-26—Подача