Изобретение относится к импульсной технике, в частности к технике прямого цифрового синтеза частот и сигналов, и может быть использовано в системах электронной техники, в которых применяются многочастотные сигналы с постоянным или изменяющимся спектральным составом.

Известен цифровой синтезатор частот, содержащий последовательно соединенные накопитель кодов, сумматор, постоянное запоминающее устройство, цифроаналоговый преобразователь (ЦАП) и фильтр нижних частот, выход которого является выходом синтезатора, а также опорный генератор, выход которого подключен к входу синхронизации накопителя кодов, причем первый вход сумматора подключен к шине кода формирования фазоманипулированного сигнала, а информационный вход накопителя кодов - к шине кода установки частоты.

Однако данный синтезатор не обеспечивает формирование многочастотного выходного сигнала с оперативным изменением его спектрального состава.

Наиболее близким к предлагаемому является цифровой синтезатор частот прямого действия, содержащий образцовый генератор, преобразователь кода, ЦАП, фильтр нижних частот, выход которого подключен к шине выходного сигнала синтезатора, N цифровых интеграторов, информационные входы которых соединены с N шинами кодов синтезируемых частот, мультиплексор, N информационных входов которого соединены с выходами соответствующих цифровых интеграторов, а выход - с входом преобразователя кодов, накапливающий сумматор, информационный вход которого соединен с выходом преобразователя кодов, а выход - с информационным входом ЦАП, а также блок синхронизации, вход которого соединен с выходом образцового генератора, первая группа выходов соединена с входом тактирования каждого цифрового интегратора и ЦАП, вторая группа выходов соединена с адресным входом мультиплексора, а третья группа выходов соединена с входами тактирования, мультиплексора и преобразователя кода, а также с входами тактирования и установки нуля накапливающего сумматора.

Данный цифровой синтезатор частот прямого действия обеспечивает получение многочастотного сигнала с оперативным изменением его спектрального состава. При этом в состав выходного сигнала могут включаться моногармоники из диапазона Fmin - Fmax работы синтезатора в любом наборе, частоты отдельных составляющих которых можно менять независимо друг от друга посредством изменения управляющих кодов.

Однако данный цифровой синтезатор частот прямого действия имеет низкую частоту дискретизации fд, которая зависит от времени занесения кода а накапливающий сумматор Δt5, т.е. от быстродействия последнего, а частота дискретизации согласно теореме В. А. Котельникова определяет максимальную синтезируемую частоту синтезатора Fmax ≅ fд/2. Кроме того, частота дискретизации данного синтезатора, как это следует из формулы fд = fo/N+1, где fo - частота следования импульсов на выходе образцового генератора; N - количество частот в выходном сигнале синтезатора, уменьшается с ростом N. Таким образом, недостатком данного синтезатора является ограниченный со стороны высоких частот Fmax диапазон синтезируемых колебаний.

Целью изобретения является расширение диапазона синтезируемых колебаний в сторону высоких частот при обеспечении независимости максимальной синтезируемой частоты синтезатора от количества частот в формируемом многочастотном сигнале.

Цель достигается тем, что в цифровой синтезатор частот, содержащий опорный генератор, N цифровых интеграторов, преобразователь кода, последовательно соединенные ЦАП и фильтр нижних частот, причем тактовый вход ЦАП соединен с тактовыми входами N цифровых интеграторов, информационные входы которых являются кодовыми шинами задания синтезируемых частот, введены N-1 дополнительных преобразователей кода и сумматор кодов с N информационными входами, при этом выход опорного генератора соединен с тактовыми входами ЦАП и сумматора кодов, выход которого соединен с информационным входом ЦАП, выходы преобразователя кодов и N - 1 дополнительных преобразователей кодов подсоединены к соответствующим информационным входам сумматора кодов с N информационными входами, входы преобразователей кодов и N-1 дополнительных преобразователей кодов подключены к выходам соответствующих цифровых интеграторов.

Сумматор кодов с N информационными входами выполнен в виде log2 N суммирующих блоков, каждый из которых выполнен на N/2r сумматорах и N/2r регистрах памяти, где r - номер суммирующего блока, при этом первый и второй входы сумматоров первого суммирующего блока являются соответствующими из N информационных входов сумматора кодов с N информационными входами, выход каждого из сумматоров в каждом из суммирующих блоков подключен к входу соответствущего регистра памяти, выход каждого из регистров памяти с нечетным номером r-го суммирующего блока соединен с первым входом соответствующего сумматора (r+1)-го суммирующего блока, выход каждого из регистров памяти с четным номером r-го суммирующего блока соединен с вторым входом соответствующего сумматора (r+1)-го суммирующего блока, тактовые входы всех регистров памяти всех суммирующих блоков объединены и являются тактовым входом сумматора кодов с N информационными входами, выходом которого является выход регистра памяти (log2 N)-го суммирующего блока.

Кроме того, каждый из N цифровых интеграторов содержит последовательно соединенные умножитель кода, первый сумматор, первый регистр памяти, второй регистр памяти, мультиплексор, блок синхронизации, Р каналов, каждый из которых выполнен в виде последовательно соединенных корректора кода, сумматора и регистра памяти, выход которого подключен к соответствующему информационному входу мультиплексора, при этом входы умножителя кода и корректоров кода Р каналов объединены и являются информационным входом цифрового интегратора, другой вход первого сумматора объединен с другими входами сумматоров Р каналов и подключен к выходу первого регистра памяти, тактовые входы первого и второго регистров памяти и регистров памяти Р каналов объединены и подключены к первому выходу блока синхронизации, второй и третий выходы которого соединены соответственно с первым и вторым управляющими входами мультиплексора, выход которого является выходом цифрового интегратора, а тактовый вход блока синхронизации является входом тактирующего сигнала цифрового интегратора.

Сопоставительный анализ с прототипом показывает, что заявляемый синтезатор отличается наличием новых блоков: N-1 - дополнительных преобразователей кода, сумматора кодов с N информационными входами и их связями с остальными элементами схемы. Таким образом, заявляемый синтезатор соответствует критерию изобретения "новизна".

Сравнение заявляемого решения с другими техническими решениями показывает, что преобразователи кода и сумматоры кодов широко известны. Однако при их введении в указанной связи с остальными элементами схемы в заявляемый цифровой синтезатор частот они проявляют новые свойства, что приводит к расширению диапазона синтезируемых колебаний в сторону высоких частот при обеспечении независимости максимальной синтезируемой частоты синтезатора от количества частот в формируемом многочастотном сигнале. Это позволяет сделать вывод о соответствии технического решения критерию "существенные отличия".

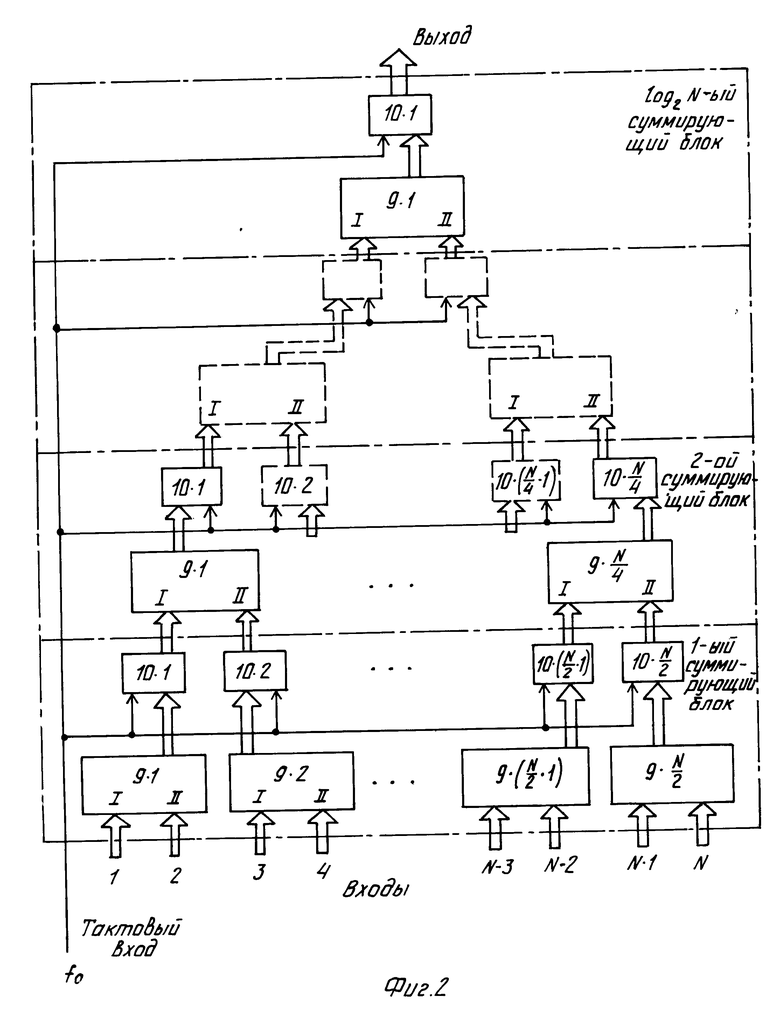

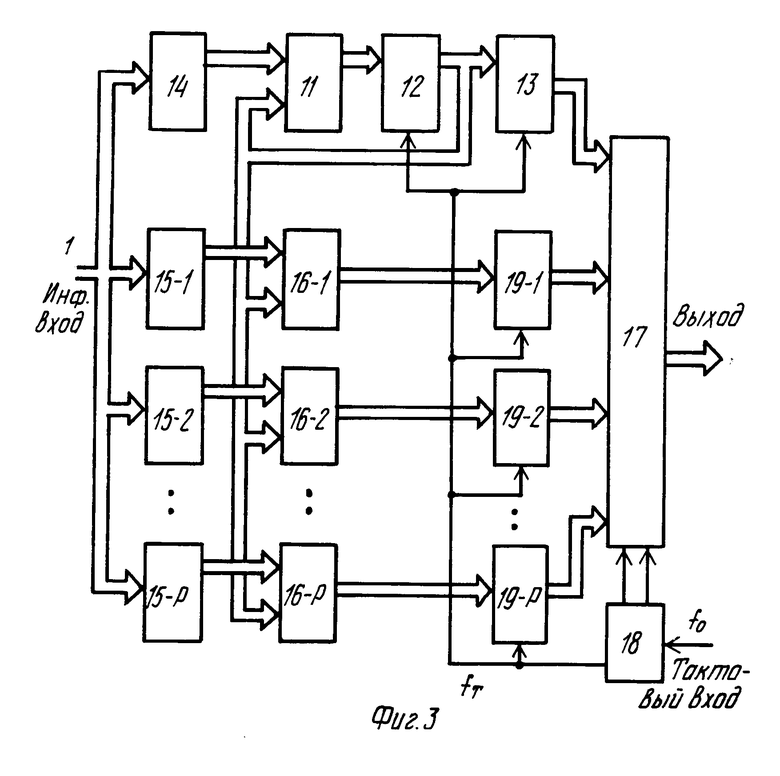

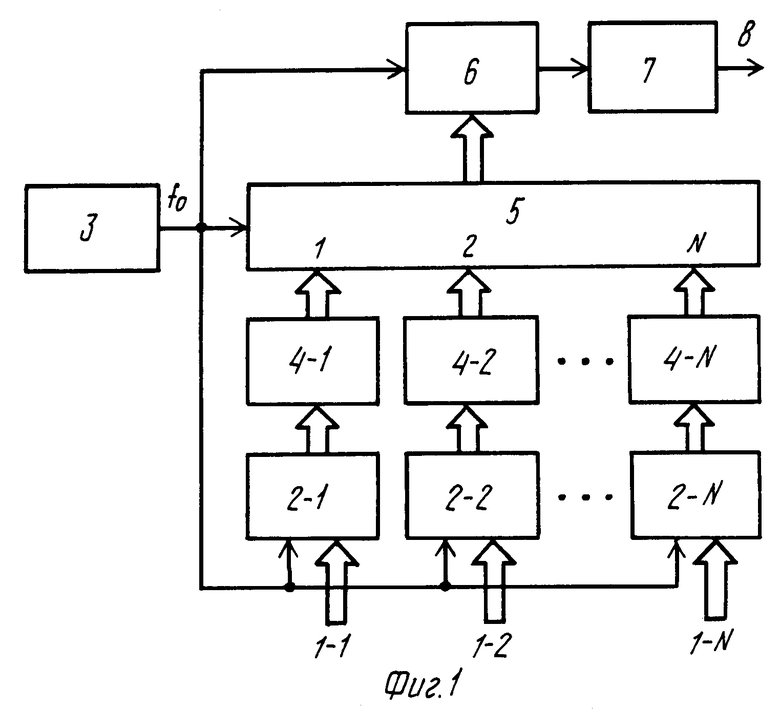

На фиг. 1 представлена структурная электрическая схема цифрового синтезатора частот; на фиг. 2 - структурная электрическая схема сумматора кодов с N информационными входами; на фиг. 3 - структурная электрическая схема цифрового интегратора.

Цифровой синтезатор частот (фиг. 1) содержит шины 1-1, 1-2, ..., 1-N кодов синтезируемых частот, цифровые интеграторы 2-1,2-2,...,2-N, опорный генератор 3, преобразователи 4-1, 4-2, ..., 4-N кода, сумматор 5 кодов с N информационными входами, ЦАП 6, фильтр 7 нижних частот и шину 8 выходного сигнала. Выход опорного генератора 3 соединен с тактовыми входами ЦАП 6, сумматора 5 кодов с N информационными входами и тактовыми входами N цифровых интеграторов 2-1, 2-2, ..., 2-N, информационные входы которых являются кодовыми шинами 1-1, 1-2, ..., 1-N задания синтезируемых частот, а выходы соединены с входами соответствующих преобразователей 4-1, 4-2, ..., 4-N кода. Выходы последних подсоединены к соответствующим информационным входам сумматора 5 кодов с N информационными входами, выход которого соединен с информационным входом ЦАП 6. Выход ЦАП соединен с входом фильтра 7 нижних частот, выход которого является выходной шиной 8 цифрового синтезатора частот.

Сумматор 5 кодов с N информационными входами (фиг. 2) выполнен в виде log2 N суммирующих блоков, каждый из которых выполнен на N/2r сумматорах 9 и N/2r регистрах 10 памяти, где r - номер суммирующего блока. Первый и второй входы сумматоров 9 первого суммирующего блока являются соответствующими из N информационных входов сумматора 5 кодов с N информационными входами, выход каждого из сумматоров 9 в каждом из суммирующих блоков подключен к входу соответствующего регистра 10 памяти. Выход каждого из регистров памяти с нечетным номером r-го суммирующего блока соединен с первым входом соответствующего сумматора 9 (r+1)-го суммирующего блока, выход каждого из регистров памяти с четным номером r-го суммирующего блока соединен с вторым входом соответствующего сумматора 9 (r+1)-го суммирующего блока. Тактовые входы всех регистров 10 памяти всех суммирующих блоков объединены и являются тактовым входом сумматора 5 кодов с N информационными входами, выходом которого является выход регистра памяти (log2 N)-го суммирующего блока.

Каждый из N цифровых интеграторов 2 (фиг. 3) содержит последовательно соединенные умножитель 14 кода, первый сумматор 11, первый регистр 12 памяти, второй регистр 13 памяти и мультиплексор 17, блок 18 синхронизации, Р каналов, каждый из которых выполнен в виде последовательно соединенных корректоров 15 кода, сумматора 16 и регистра 19 памяти, выход которого подключен к соответствующему информационному входу мультиплексора 17. Входы умножителя 14 кода и корректоров 15-1, 15-2, ..., 15-Р кода Р каналов объединены и являются информационным входом цифрового интегратора 2. Другой вход первого сумматора 11 объединен с другими входами сумматоров 16-1, 16-2, ..., 16-Р Р каналов и подключен к выходу первого регистра 12 памяти. Тактовые входы первого 12 и второго 13 регистров памяти и регистров 19-1, 19-2, . .., 19-Р памяти Р каналов объединены и подключены к первому выходу блока 18 синхронизации, второй и третий выходы которого соединены соответственно с первым и вторым управляющими входами мультиплексора 17. Выход мультиплексора является выходом цифрового интегратора 2, а тактовый вход блока 18 синхронизации - входом тактирующего сигнала цифрового интегратора.

Количество цифровых интеграторов 2-1, 2-2, ..., 2-N равно наибольшему числу спектральных линий в синтезируемом многочастотном сигнале.

Принцип действия цифрового синтезатора частот основан на одновременном вычислении кодов выборок N колебаний заданных частот и последующем формировании суммарного многочастотного сигнала.

Синтезатор работает следующим образом.

Сигнал на шине 8 выходного сигнала синтезатора U(t)вых представляет собой сумму гармонических функций, например синусоид единичной амплитуды:

U(t)вых=  Ui(t)i =

Ui(t)i =  sin(2πFi·t+ϕi) (1) где t - текущее время, соответствующее моментам nTo (n = 0, 1, 2, ...);

sin(2πFi·t+ϕi) (1) где t - текущее время, соответствующее моментам nTo (n = 0, 1, 2, ...);

i = i =  - номер функции;

- номер функции;

Fi и ϕi - соответственно синтезируемая частота и начальная фаза i-й функции.

Частоты Fi произвольны, не связаны какими-либо соотношениями и задаются на шинах 1-1, 1-2, ..., 1-N кодов синтезируемых частот F1, F2, ..., FN.

Цифровые интеграторы 2-1, 2-2, ..., 2-N по тактовым импульсам, поступающим от опорного генератора 3 с частотой дискретизации fo, формируют на своих выходах коды, соответствующие текущей фазе синусоидального колебания, в дискретные моменты времени согласно выражению

Φi = 2 πFi. t + ϕi, (2) где Fi = Ki. fo/R, где Ki - код синтезируемой частоты;

R - параметр (емкость) цифрового интегратора.

Пpеобразователи 4-1, 4-2, ..., 4-N кода преобразуют коды текущей фазы Φi(nTo) в коды выборок синусоиды sin[ Φi(nTo)]. Сумматор 5 кодов в каждый тактовый момент времени nTo вычисляет сумму кодов выборок N синусоид и формирует на выходе коды К(nTo), соответствующие выборкам суммарного сигнала в данные моменты времени. Сигнал на выходе ЦAП 6 представляет собой ступенчатопостоянную аппроксимацию функции U(t)вых с периодом дискретизации То. Фильтр 7 нижних частот отделяет побочные компоненты спектра, связанные с дискретизацией.

Для возможности фильтрации значения fo = 1/To и Fmax выбираются в соответствии с теоремой В.А.Котельникова:

fo ≥ 2Fmax , (3) где fo и Fmax - соответственно частота дискретизации и наибольшая частота из диапазона синтезируемых частот.

Сумматор 5 кодов с N информационными входами выполнен по каскадной схеме (фиг. 2) с возможностью хранения промежуточных (частичных) сумм в регистрах 10 памяти. Разрядность сумматоров 9 и регистров 10 памяти определяется разрядностью суммируемых кодов. Линейка сумматоров 9 первого суммирующего блока осуществляет попарное сложение кодов выборок отдельных синусоид в каждый тактовый момент времени nTo, линейка сумматоров 9 второго суммирующего блока осуществляет попарное сложение сумм, полученных в первом суммирующем блоке, который в этот тактовый момент времени формирует частичные суммы для новых значений кодов выборок синусоид, линейка сумматоров 9 третьего суммирующего блока осуществляет попарное сложение сумм, полученных во втором суммирующем блоке и т.д. до получения одного суммарного кода.

В результате такой конструкции сумматора 5 кодов время суммирования (tс) синтезатора определяется временем задержки срабатывания сумматора 9 (ts) и временем записи информации в регистры 10 (tр) любой одной линейки и не зависит от числа суммирующих линеек tc = ts + tр.

Принцип действия цифрового интегратора 2 (фиг. 3) основан на одновременном формировании Р+1 кодов точек отсчета фазы синтезируемого колебания, дискретно сдвинутых относительно друг друга на определенную величину, с последующим выбором кодов данных точек в определенной последовательности для получения требуемой формы выходного колебания.

Цифровой интегратор 2 (фиг. 3) работает следующим образом.

На шине 1 кода синтезируемых частот устанавливается кодированное значение синтезируемой частоты К. Этот код поступает на вход умножителя 14 кода, на выходе которого формируется код числа, равный К(Р+1), где Р - число каналов цифрового интегратора 2. При числе каналов, равном 2х (х = 1, 2, 2, .. .), умножитель 14 кода представляет собой регистр сдвига, который выполняет операции сдвига кода К на х разрядов в сторону увеличения кода. Соединенные в кольцо первый сумматор 11 и первый регистр 12 памяти с тактовой частотой fт = fo/Р+1, где fo - частота тактирования цифрового интегратора 2, осуществляют накопление кода К(Р+1), в результате чего на выходе первого регистра 12 памяти в каждый тактовый момент времени tт = gТт = g/fт, где g = 0, 1, 2, ... - целые числа, формируется код числа, которое пропорционально фазе синтезируемого колебания. Код К установки частоты одновременно поступает на входы Р корректоров 15-1, 15-2, ..., 15-Р кода, которые выполняют операцию умножения кода К установки частоты на постоянный коэффициент, равный Р, в результате чего на их выходах образуются коды чисел, равные по каждому каналу соответственно К, 2К, ..., РК, которые во вторых сумматорах 16-1, 16-2, ..., 16-Р добавляются к выходному коду фазы первого регистра 12 памяти. При этом на выходе вторых сумматоров 16-1, 16-2, ..., 16-Р в тактовые моменты времени tт формируются Р кодов чисел, пропорциональных фазе синтезируемого колебания, но смещенных относительно выходного кода первого регистра 12 памяти соответственно на К, 2К, ..., РК. Выходы первого регистра 12 памяти и выходы Р вторых сумматоров 16-1, 16-2, ..., 16-Р подключены соответственно к информационным входам регистров 13, 19-1, 19-2, ..., 19-Р памяти, которые по тактовым импульсам с частотой fт = fo/Р+1 переписывают информацию с входа на выход и далее на соответствующие информационные входы мультиплексора 17 из Р+1 в один. Мультиплексор 17 с частотой синхронизации fo в последовательности, задаваемой блоком 18 синхронизации, пропускает на выход входные коды таким образом, что за время Тт = (Р+1) . То на его выходе формируется последовательность кодов чисел, соответствующая Р+1 фазовым точкам синтезируемого колебания: 0, К, 2К, ..., РК в первый такт, (Р+1)К, (Р+2)К, (Р+3)К, . .., 2РК во второй такт, (2Р+1)К, (2Р+2)К, (2Р+3)К, ..., 3РК в третий такт работы регистров и т.д, т.е. на выходе мультиплексора 17 в каждый тактовый момент времени to = nTo (n =1, 2, ...) работы цифрового интегратора 2 происходит изменение кода фазы выходного сигнала на величину, равную коду К частоты, в то время как на выходах первого регистра 12 памяти и регистров 13, 19-1, 19-2, ..., 19-Р памяти информация меняется на величину (Р+1)К и только в моменты времени tт =jТт (j = 1, 2,...), Тт = То.(Р+1).

Корректор кода, выполняющий умножение кода частоты на постоянный коэффициент, может быть реализован на регистрах сдвига и сумматорах, причем для первого канала (Р=1) постоянный коэффициент равен единице и корректор кода отсутствует, для второго канала (Р=2) коэффициент равен двум и корректор кода представляет собой регистр сдвига входного кода на один разряд в сторону увеличения, для третьего канала (Р=3) коэффициент равен трем и корректор кода представляет собой двухвходовый К-разрядный сумматор, где К - число двоичных разрядов входного кода К=2k и т.д.

В результате новой конструкции цифрового интегратора удалось уменьшить время срабатывания основного времязадающего узла цифрового синтезатора - цифрового интегратора, так как в предлагаемом интеграторе на частоте fo работает только мультиплексор, а тактовая частота всех остальных элементов схемы в Р+1 раз ниже тактовой частоты синтезатора и равна fo/Р+1, что позволяет дополнительно повысить максимальную синтезируемую частоту предлагаемого синтезатора по сравнению с прототипом.

Эффективность предложенного цифрового синтезатора частот по сравнению с прототипом, состоит в следующем.

В прототипе частота следования импульсов на выходе опорного генератора выбирается из условия

fo = 1/tmax, (4) при этом tmax > Δt5, где Δt5 - время занесения кода в накапливающий сумматор 5 прототипа.

При этом частота дискретизации прототипа определяется выражением

fд = 1/Tд = fo/N+1, (5) где Тд - период дискретизации;

N - количество частот в формируемом сигнале.

Как следует из выражений (4) и (5) частота дискретизации прототипа и максимальная (Fmax) синтезируемая частота предлагаемого синтезатора, которая в соответствии с теоремой Котельникова В.А. равна Fmax ≅ fo/2, во-первых, ограничены временем занесения кода в накапливающий сумматор 5 (Δt5), во-вторых, зависит от количества частот N в формируемом сигнале.

В предложенном синтезаторе, принцип действия которого основан на одновременном формировании кодов выборок всех N колебаний заданных частот и последующем формировании суммарного многочастотного сигнала, накапливающий сумматор 5 отсутствует. Тактовая частота (частота дискректизации) определяется только быстродействием входящих в его состав функциональных узлов, не зависит от количества частот в формируемом сигнале и определяется выражением

fд = fo = 1/tmax, (6) где tmax - наибольшее время срабатывания одного из функциональных узлов синтезатора (например, введенного сумматора 5 кодов с N информационными входами).

Пусть tmax предлагаемого синтезатора равно времени занесения кода Δt5 устройства-прототипа: tmax = Δt5, тогда из выражения (6) следует, что максимальная синтезируемая частота Fmax предлагаемого синтезатора, во-первых, в N+1 раз выше, чем устройства-прототипа, и, во-вторых, не зависит от количества частот в формируемом многочастотном сигнале.

Сумматор 5 кодов с N информационными входами выполнен по каскадной схеме с возможностью хранения промежуточных (частичных) сумм в регистрах памяти. В результате такой конструкции сумматора кодов его время срабатывания (tc) равно сумме времени задержки сумматора (ts) и времени записи информации в регистр памяти (tр) одного суммирующего блока и не зависит от числа суммирующих блоков. Время срабатывания накапливающего сумматора 5 устройства-прототипа, который реализуется, как правило, в виде соединенных в кольцо сумматора и регистра памяти, равно сумме времен задержки срабатываний сумматора и регистра памяти. Так как разрядность сумматоров и регистров сумматора кодов обычно меньше разрядности тех же элементов накапливающего сумматора устройства-прототипа, то время срабатывания (tс) сумматора кодов с N информационными входами предлагаемого синтезатора меньше или равно Δt5 накапливающего сумматора устройства-прототипа (tc < Δt5).

В результате новой конструкции цифрового интегратора удалось уменьшить время срабатывания основного времязадающего узла цифрового синтезатора - цифрового интегратора, так как в предлагаемом интеграторе на частоте fo работает только мультиплексор, а тактовая частота всех остальных элементов схемы в Р+1 раз ниже тактовой частоты синтезатора и равна fo/Р+1.

Предложенный цифровой синтезатор частот имеет существенные отличия от устройства-прототипа как по составу и конструкции блоков, связям, так и по быстродействию, которое возросло в N+1 раз и не зависит от количества частот в формируемом сигнале.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2344541C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1681375A1 |

| ЦИФРОВОЙ МНОГОФАЗНЫЙ ГЕНЕРАТОР | 1992 |

|

RU2066918C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ ДЛЯ МНОГОЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2014 |

|

RU2566961C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ЗАЩИТЫ ИНФОРМАЦИИ В СЕТЯХ СВЯЗИ | 2005 |

|

RU2295195C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1529402A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1998 |

|

RU2153698C2 |

| СИНТЕЗАТОР ЧАСТОТ | 1995 |

|

RU2119238C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ МНОГОЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2013 |

|

RU2536385C1 |

Использование: в импульсной технике, в формирователях многочастотных сигналов с постоянным или изменяющимся спектральным составом. Сущность изобретения: цифровой синтезатор частот содержит шины 1-1, 1-2, ..., 1-N кодов синтезируемых частот, цифровые интеграторы 2-1, 2-2,..., 2-N, опорный генератор 3, преобразователи 4-1, 4-2,..., 4-N кода, сумматор 5 кодов с N информационными входами, цифроаналоговый преобразователь 6, фильтр 7 нижних частот и шину 8 выходного сигнала и позволяет расширить частотный диапазон выходных сигналов в сторону высоких частот при обеспечении независимости максимальной синтезируемой частоты от количества частот в выходном многочастотном сигнале. 2 з.п. ф-лы, 3 ил.

| Цифровой синтезатор частот прямого действия | 1984 |

|

SU1205249A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-02-27—Публикация

1991-02-25—Подача