о

00

U) XI

сл

Изобретение относится к радиотехнике и может быть использовано в приемопередающих устройствах, в системах коротковолновой радиолокации.

Целью изобретения является увеличение числа одновременно формируемых сигналов при упрощении устройства.

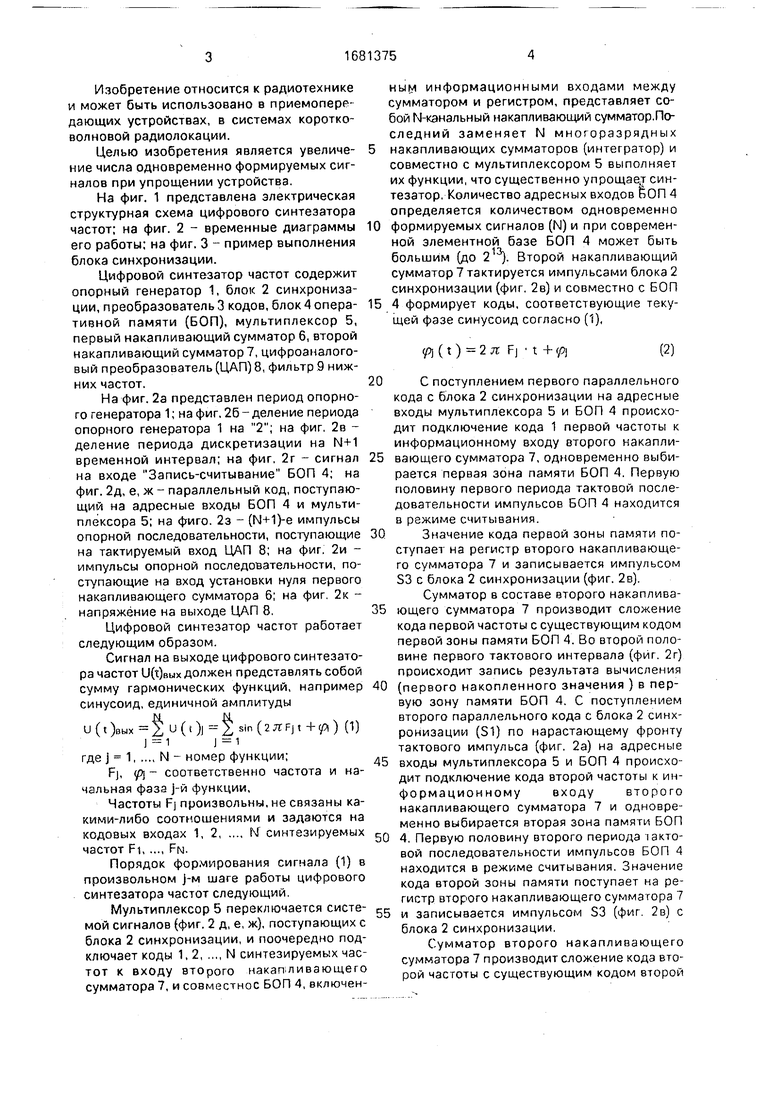

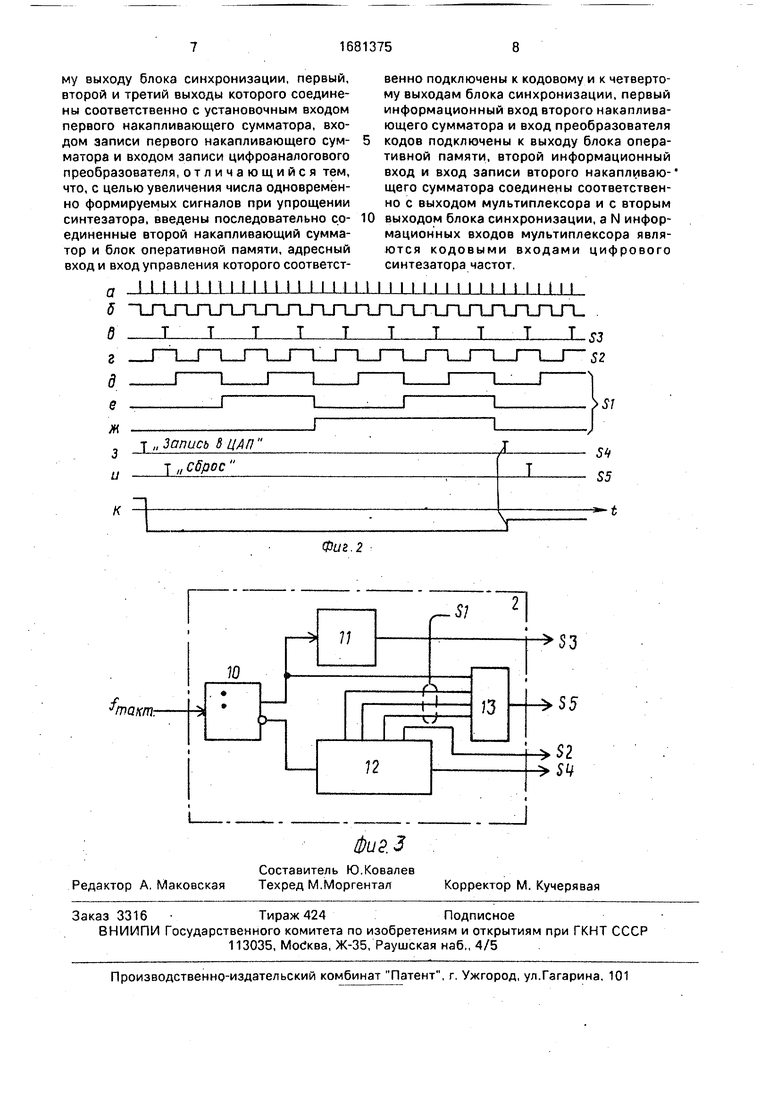

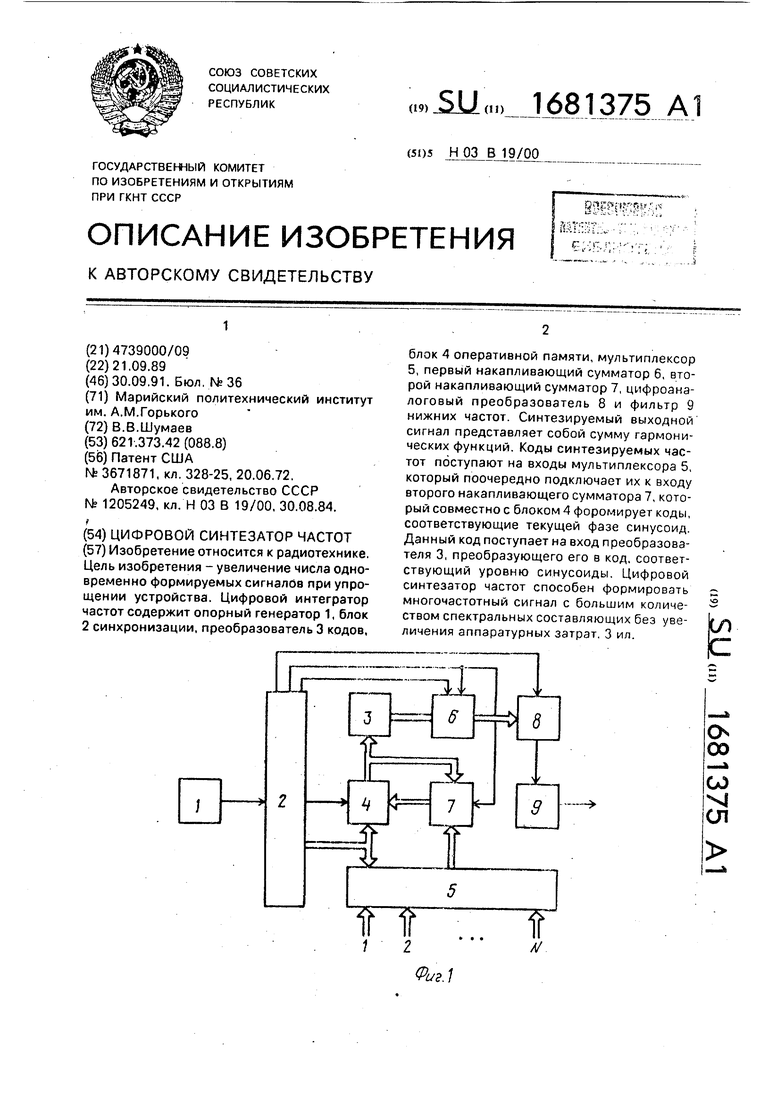

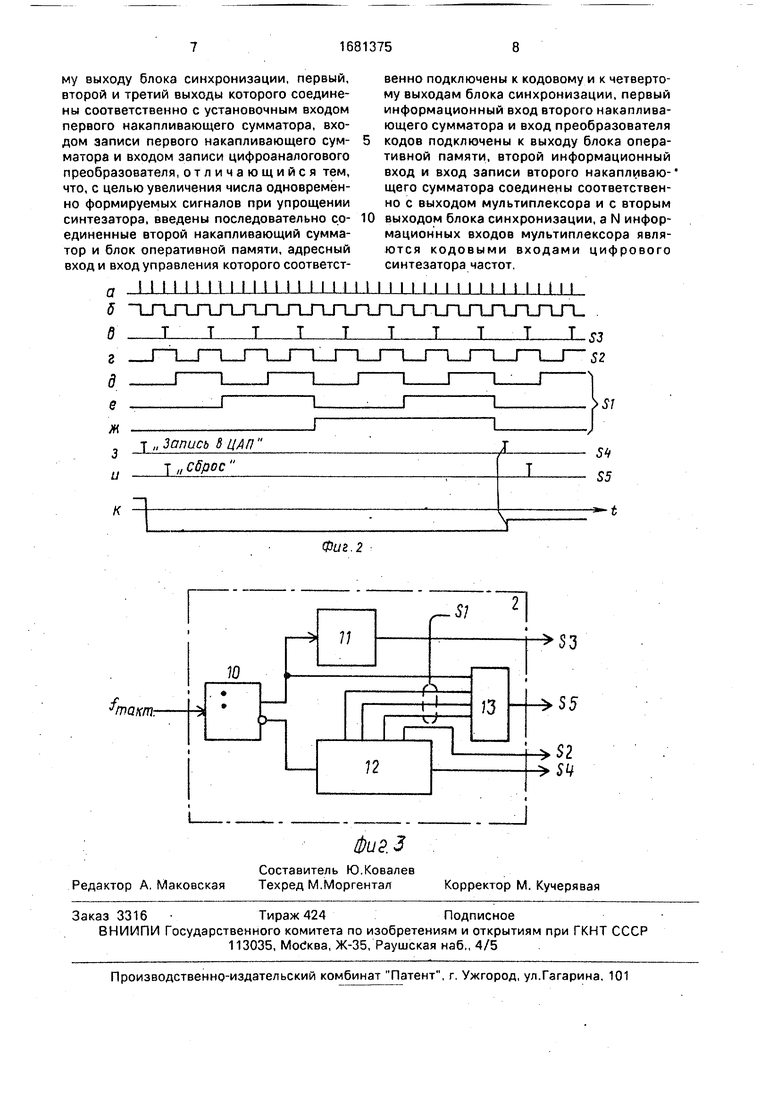

На фиг. 1 представлена электрическая структурная схема цифрового синтезатора частот; на фиг. 2 - временные диаграммы его работы; на фиг. 3 - пример выполнения блока синхронизации.

Цифровой синтезатор частот содержит опорный генератор 1, блок 2 синхронизации, преобразователь 3 кодов, блок 4 оперативной памяти (БОП), мультиплексор 5, первый накапливающий сумматор 6, второй накапливающий сумматор 7, цифроаналого- вый преобразователь (ЦАП) 8, фильтр 9 нижних частот.

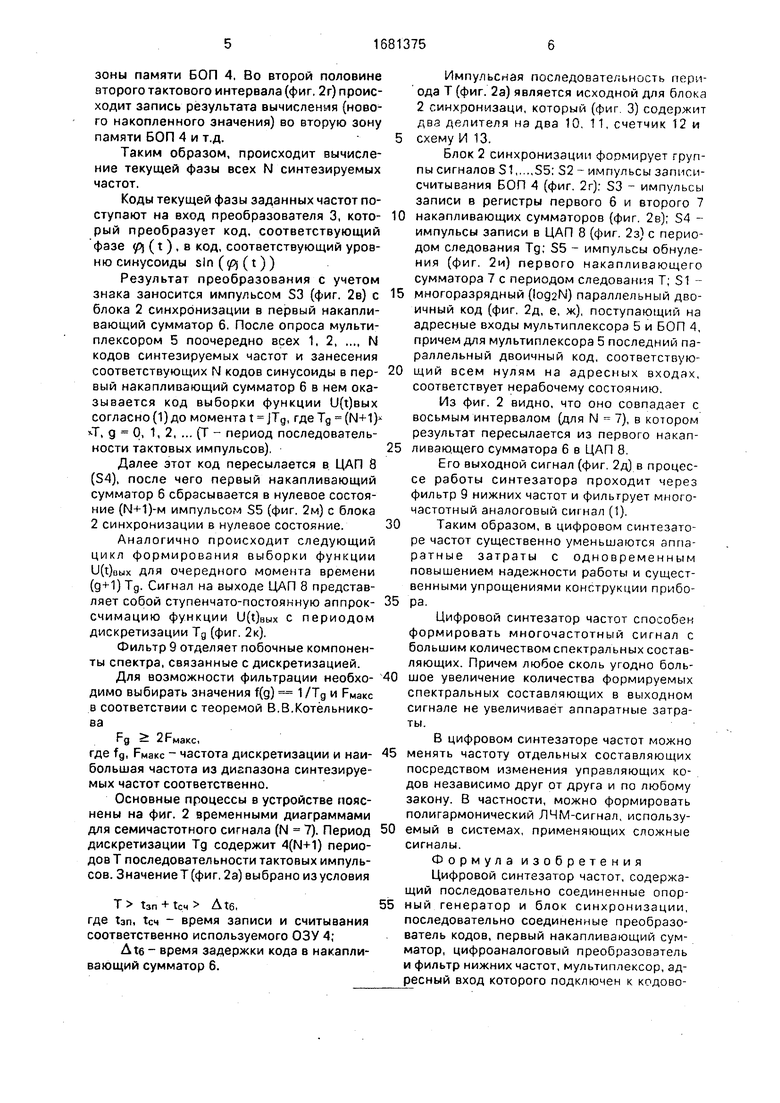

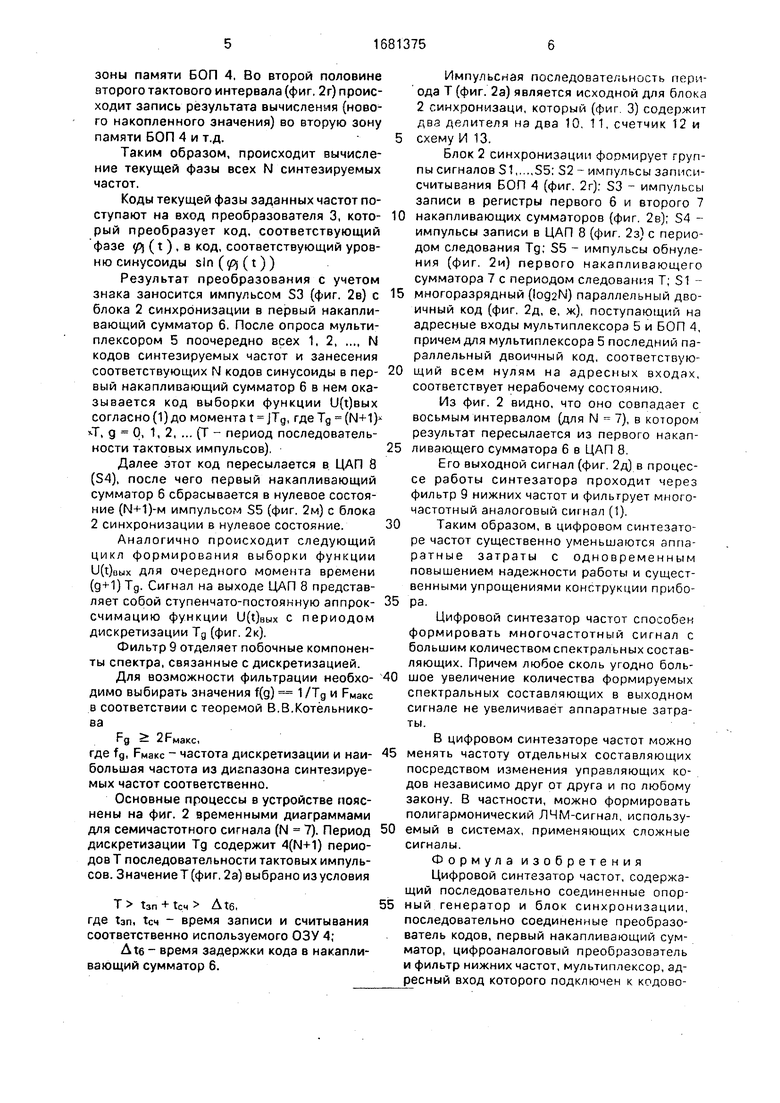

На фиг, 2а представлен период опорного генератора 1; на фиг, 26 - деление периода опорного генератора 1 на на фиг, 2в - деление периода дискретизации на N+1 временной интервал; на фиг, 2г - сигнал на входе Запись-считывание БОП 4; на фиг. 2д, е, ж - параллельный код, поступающий на адресные входы БОП 4 и мультиплексора 5; на фиго. 2з - (N+1)-e импульсы опорной последовательности, поступающие на тактируемый вход ЦАП 8; на фиг. 2и - импульсы опорной последовательности, поступающие на вход установки нуля первого накапливающего сумматора 6; на фиг 2к - напряжение на выходе ЦАП 8.

Цифровой синтезатор частот работает следующим образом.

Сигнал на выходе цифрового синтезатора частот U(t)Bbix должен представлять собой сумму гармонических функций, например синусоид, единичной амплитуды

U ( t )вых 2 U ( )l 5) Sln ( 2 П Fi + ) (1)

J -1 J 1

где j 1, ..., N - номер функции;

Fj, (f - соответственно частота и начальная фаза j-й функции,

Частоты F произвольны, не связаны какими-либо соотношениями и задаются на

кодовых входах 1, 2 Ы синтезируемых

частот FiFN.

Порядок формирования сигнала (1) в произвольном j-м шаге работы цифрового синтезатора частот следующий.

Мультиплексор 5 переключается системой сигналов (фиг. 2 д, е, ж), поступающих с блока 2 синхронизации, и поочередно подключает коды 1,2N синтезируемых частот к входу второго накапливающего сумматора 7, и совместное БОП 4, включенным информационными входами между сумматором и регистром, представляет собой N-канэльный накапливающий сумматор.По- следний заменяет N многоразрядных

накапливающих сумматоров (интегратор) и совместно с мультиплексором 5 выполняет их функции, что существенно упрощает синтезатор, Количество адресных входов БОП 4 определяется количеством одновременно

формируемых сигналов (N) и при современной элементной базе БОП 4 может быть большим (до 2 j. Второй накапливающий сумматор 7 тактируется импульсами блока 2 синхронизации (фиг. 2в) и совместно с БОП

4 формирует коды, соответствующие текущей фазе синусоид согласно (1),

р (t ) 2 л FJ t + pi

(2)

С поступлением первого параллельного

кода с блока 2 синхронизации на адресные входы мультиплексора 5 и БОП 4 происходит подключение кода 1 первой частоты к информационному входу второго накапливающего сумматора 7, одновременно выбирается первая зона памяти БОП 4. Первую половину первого периода тактовой последовательности импульсов БОП 4 находится в режиме считывания.

Значение кода первой зоны памяти поступает на регистр второго накапливающего сумматора 7 и записывается импульсом S3 с блока 2 синхронизации (фиг. 2в).

Сумматор в составе второго накапливающего сумматора 7 производит сложение кода первой частоты с существующим кодом первой зоны памяти БОП 4. Во второй половине первого тактового интервала (фиг. 2г) происходит запись результата вычисления

(первого накопленного значения)в первую зону памяти БОП 4. С поступлением второго параллельного кода с блока 2 синхронизации (S1) по нарастающему фронту тактового импульса (фиг. 2а) на адресные

входы мультиплексора 5 и БОП 4 происходит подключение кода второй частоты к информационному входу второго накапливающего сумматора 7 и одновременно выбирается вторая зона памяти БОП

4. Первую половину второго периода тактовой последовательности импульсов БОП 4 находится в режиме считывания. Значение кода второй зоны памяти поступает на регистр второго накапливающего сумматора 7

и записывается импульсом S3 (фиг 2в) с блока 2 синхронизации.

Сумматор второго накапливающего сумматора 7 производит сложение кода второй частоты с существующим кодом второй

зоны памяти БОП 4. Во второй половине второго тактового интервала (фиг, 2г) происходит запись результата вычисления {нового накопленного значения) во вторую зону памяти БОП 4 и т.д.

Таким образом, происходит вычисление текущей фазы всех N синтезируемых частот.

Коды текущей фазы заданных частот поступают на вход преобразователя 3, кото- рый преобразует код, соответствующий фазе fi (t ) , в код, соответствующий уровню синусоиды sln((t))

Результат преобразования с учетом знака заносится импульсом S3 (фиг. 2в) с блока 2 синхронизации в первый накапливающий сумматор 6. После опроса мультиплексором 5 поочередно всех 1, 2 N

кодов синтезируемых частот и занесения соответствующих N кодов синусоиды в пер- вый накапливающий сумматор 6 в нем оказывается код выборки функции и(г)вых согласно (1) до момента t jTg, гдеТд (N+1)x Т, д 0, 1, 2, ... (Т - период последовательности тактовых импульсов).

Далее этот код пересылается в ЦАП 8 (S4), после чего первый накапливающий сумматор 6 сбрасывается в нулевое состояние (N+1)-M импульсом S5 (фиг. 2м) с блока 2 синхронизации в нулевое состояние.

Аналогично происходит следующий цикл формирования выборки функции и(г)вых для очередного момента времени (д+1) Тд. Сигнал на выходе ЦАП 8 представляет собой ступенчато-постоянную аппрок- счимацию функции U(t)Bux с периодом дискретизации Та (фиг. 2к).

Фильтр 9 отделяет побочные компоненты спектра, связанные с дискретизацией.

Для возможности фильтрации необхо- димо выбирать значения f(g) 1 /Tg и Рмакс в соответствии с теоремой В.В.Котёльнико- ва

Fg г 2РмЭКС1

где fg, Рмакс - частота дискретизации и наи- большая частота из диапазона синтезируемых частот соответственно.

Основные процессы в устройстве пояснены на фиг. 2 временными диаграммами для семичастотного сигнала (N 7). Период дискретизации Тд содержит 4(N+1) периодов Т последовательности тактовых импульсов. ЗначениеТ(фиг. 2а) выбрано из условия

Т tsn + tcH Ate.

где tan, ten время записи и считывания соответственно используемого ОЗУ 4;

Ate - время задержки кода в накапливающий сумматор 6.

Импульсная последовательность периода Т (фиг. 2а) является исходной для блока 2 синхронизаци, который (фиг 3) содержит два делителя на два 10. 11, счетчик 12 и схему И 13.

Блок 2 синхронизации формирует группы сигналов S1,...,S5: 32 - импульсы записи- считывания БОП 4 (фиг. 2г); S3 - импульсы записи в регистры первого 6 и второго 7 накапливающих сумматоров (фиг. 2в); S4 - импульсы записи в ЦАП 8 (фиг. 2з) с периодом следования Tg; S5 - импульсы обнуления (фиг. 2м) первого накапливающего сумматора 7 с периодом следования Т; S1 - многоразрядный (Iog2N) параллельный двоичный код (фиг, 2д, е, ж), поступающий на адресные входы мультиплексора 5 и БОП 4, причем для мультиплексора 5 последний параллельный двоичный код, соответствующий всем нулям на адресных входах, соответствует нерабочему состоянию.

Из фиг. 2 видно, что оно совпадает с восьмым интервалом (для N 7), в котором результат пересылается из первого накапливающего сумматора 6 в ЦАП 8.

Его выходной сигнал (фиг. 2д) в процессе работы синтезатора проходит через фильтр 9 нижних частот и фильтрует многочастотный аналоговый сигнал (1).

Таким образом, в цифровом синтезаторе частот существенно уменьшаются аппаратные затраты с одновременным повышением надежности работы и существенными упрощениями конструкции прибора.

Цифровой синтезатор частот способен формировать многочастотный сигнал с большим количеством спектральных составляющих. Причем любое сколь угодно большое увеличение количества формируемых спектральных составляющих в выходном сигнале не увеличивает аппаратные затраты.

В цифровом синтезаторе частот можно менять частоту отдельных составляющих посредством изменения управляющих кодов независимо друг от друга и по любому закону. В частности, можно формировать полигармонический ЛЧМ-сигнал, используемый в системах, применяющих сложные сигналы.

Формула изобретения Цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор и блок синхронизации, последовательно соединенные преобразователь кодов, первый накапливающий сумматор, цифроаналоговый преобразователь и фильтр нижних частот, мультиплексор, адресный вход которого подключен к кодовому выходу блока синхронизации, первый, второй и третий выходы которого соединены соответственно с установочным входом первого накапливающего сумматора, входом записи первого накапливающего сумматора и входом записи цифроаналогового преобразователя, отличающийся тем, что, с целью увеличения числа одновременно формируемых сигналов при упрощении синтезатора, введены последовательно соединенные второй накапливающий сумматор и блок оперативной памяти, адресный

10 выходом блока синхронизации, а мационных входов мультиплекс ются кодовыми входами ци синтезатора частот,

входи вход управления которого соответст I I И i И I I I I I I I I I I I I I I I I I I I I I I I I I I It i И njnj JOJOJTJTJnJ JlJ J

IIIIIIIIIL.S3

S2

а б

д г д е ж

з и

S

т „ Запись В ЦАП

венно подключены к кодовому и к четвертому выходам блока синхронизации, первый информационный вход второго накапливающего сумматора и вход преобразователя

кодов подключены к выходу блока оперативной памяти, второй информационный вход и вход записи второго накапливаю- щего сумматора соединены соответственно с выходом мультиплексора и с вторым

выходом блока синхронизации, а N информационных входов мультиплексора являются кодовыми входами цифрового синтезатора частот,

S1

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2344541C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Цифровой синтезатор частот прямого действия | 1984 |

|

SU1205249A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1429285A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1995 |

|

RU2119238C1 |

| ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1992 |

|

RU2033685C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ | 2022 |

|

RU2793776C1 |

Изобретение относится к радиотехнике. Цель изобретения - увеличение числа одновременно формируемых сигналов при упрощении устройства. Цифровой интегратор частот содержит опорный генератор 1, блок 2 синхронизации, преобразователь 3 кодов, блок 4 оперативной памяти, мультиплексор 5, первый накапливающий сумматор б, второй накапливающий сумматор 7, цифроана- логовый преобразователь 8 и фильтр 9 нижних частот. Синтезируемый выходной сигнал представляет собой сумму гармонических функций. Коды синтезируемых частот поступают на входы мультиплексора 5, который поочередно подключает их к входу второго накапливающего сумматора 7, который совместно с блоком 4 форомирует коды, соответствующие текущей фазе синусоид. Данный код поступает на вход преобразователя 3, преобразующего его в код. соответствующий уровню синусоиды. Цифровой синтезатор частот способен формировать многочастотный сигнал с большим количеством спектральных составляющих без увеличения аппаратурных затрат. 3 ил. СО С

Л

Редактор А. Маковская

Составитель Ю.Ковалев Техред М.Моргентал

Фиё.З

Корректор М. Кучерявая

| Патент США Nfe 3671871, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Цифровой синтезатор частот прямого действия | 1984 |

|

SU1205249A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-09-30—Публикация

1989-09-21—Подача