Изобретение относится к радиотехнике, в частности к технике цифрового вычислительного синтеза частот, и может быть использовано для формирования сетки частот в радиопередающих и радиоприемных устройствах, а также в устройствах синхронизации различного применения.

Известен цифровой синтезатор частот (Техника средств связи, серия ТРС, выпуск 9, 1983, с. 66 - 71), содержащий последовательно соединенные накопитель кода, информационный вход которого соединен с входной шиной кода установки частоты, тактовый вход - с шиной опорного сигнала, фазосдвигающий сумматор, первый вход которого соединен с выходом накопителя кода, второй вход - с входной шиной кода установки фазы, постоянное запоминающее устройство, вход которого соединен с выходом фазосдвигающего сумматора, цифроаналоговый преобразователь, вход которого соединен с выходом постоянного запоминающего устройства и фильтр низких частот, вход которого соединен с выходом цифроаналогового преобразователя, а выход - с выходной шиной устройства.

Недостатком данного цифрового синтезатора частот является ограниченный со стороны высоких частот диапазон синтезируемых колебаний. В известном синтезаторе частот максимальная выходная частота ограничена быстродействием накопителя кодов, поскольку код на выходе накопителя изменяется с тактовой частотой, равной частоте опорного (тактового) генератора f0.

Наиболее близким к предлагаемому изобретению является цифровой синтезатор частот (патент РФ N 1689937), содержащий накопитель кода, блок памяти амплитуд, цифроаналоговый преобразователь, фильтр низких частот, выходную шину устройства, опорный генератор, блок синхронизации устройства, коммутатор, умножитель, N-1 блоков фазового сдвига, N регистров и N фазосдвигающих сумматоров, где N - число каналов синтезатора, входную шину кода установки частоты и входную шину формирования фазоманипулируемого сигнала, причем входная шина кода установки частоты синтезатора подключена к входам кода установки частоты N-1 блоков фазового сдвига и к входу умножителя, выход которого подключен к входу накопителя кодов, выход которого подключен к информационному входу регистра первого канала и к входам кода фазы N-1 блоков фазового сдвига, выходы N-1 блоков фазового сдвига подключены к соответствующим информационным входам регистров с второго по N-й, выходы регистров с 1-го по N-й подключены к вторым входам соответствующих фазосдвигающих сумматоров, входная шина кода формирования фазоманипулированного сигнала синтезатора подключены к первому входу фазосдвигающих сумматоров, выходы которых подключены к соответствующим информационным входам коммутатора, выход опорного генератора подключен к входу блока синхронизации, первый выход которого подключен к входу синхронизации накопителя кода и входам синхронизации регистров, а группа выходов блока синхронизации подключена к управляющим входам коммутатора, выход которого подключен к входу блока памяти амплитуд, выход которого подключен к выходу синтезатора.

В данном N-канальном синтезаторе удается обеспечить время формирования кодов в каждом канале устройства, равное N•T0 (T0=1/f0), а тактовая частота накопителя кодов понижается в N раз и становится равной f0/N. Следовательно, выходная частота синтезатора может быть увеличена в N раз за счет повышения частоты синхронизации устройства f0 при сохранении тактовой частоты работы накопителя кодов и шага перестройки выходной частоты Δfв= f0/R (R - емкость накопителя кодов, равная 2m, где m - количество двоичных разрядов накопителя кодов).

Однако недостатком данного синтезатора является существенное усложнение схемы ввиду наличия N многоразрядных фазосдвигающик сумматоров и, как следствие, большой объем электрорадиоэлементов для его реализации.

Кроме того, быстродействие данного устройства зависит от быстродействия фазосдвигающих сумматоров, так как время, отводимое фазосдвигающим сумматорам для формирования выходного кода, поступающего на входы коммутатора, неодинаково по каналам и изменяется от T0 для первого фазосдвигающего сумматора до N-T0 для N-го фазосдвигающего сумматора. Таким образом, работоспособность устройства в целом обеспечивается только в том случае, если время суммирования первого фазосдвигающего сумматора будет не более T0.

Изобретением решается задача упрощения устройства при сохранении диапазона синтезируемых частот с одновременным снижением требований к быстродействию фазосдвигающего сумматора.

Для достижения этого технического результата в цифровой синтезатор частот, содержащий накопитель кода, блок памяти амплитуд, цифроаналоговый преобразователь, фильтр низких частот, выходную шину устройства; опорный генератор, блок синхронизации устройства, коммутатор, умножитель, фазосдвигающий сумматор, входную шину кода установки частоты, входную шину кода формирования фазоманипулированного сигнала, N-1 блоков фазового сдвига и N регистров, где N-число каналов синтезатора, причем входная шина кода установки частоты синтезатора подключена к входам кода установки частоты N-1 блоков фазового сдвига и к входу умножителя, выход которого подключен к входу накопителя кода, а выходы N-1 блоков фазового сдвига подключены к соответствующим информационным входам регистров с второго по N-ый, входная шина кода формирования фазоманипулированного сигнала синтезатора подключена к первому входу фазосдвигающего сумматора, выход опорного генератора подключен к входу блока синхронизации, первый выход которого подключен к входу синхронизации накопителя кода и входам синхронизации регистров с первого по N-й, а группа выходов блока синхронизации подключена к управляющим входам коммутатора, выход которого подключен к входу блока памяти амплитуд, выход которого подключен к выходу синтезатора дополнительно введен регистр памяти, вход синхронизации которого подключен к первому выходу блока синхронизации, информационный вход подключен к выходу первого фазосдвигающего сумматора, а выход подключен к входам кода фазы N-1 блоков фазового сдвига и информационному входу первого регистра, при этом второй вход первого фазосдвигающего сумматора подключен к выходу накопителя кода, а выходы регистров с 1-го по N-й включительно подключены к соответствующим информационным входам коммутатора.

Отличительными признаками предлагаемого изобретения от указанного прототипа являются дополнительно введенный в него регистр памяти, выход которого подключен к входам кода фазы N-1 блоков фазового сдвига и информационному входу первого регистра, вход синхронизации подключен к первому выходу блока синхронизации устройства, информационный вход подключен к выходу фазосдвигающего сумматора, второй вход которого подключен к выходу накопителя кода, а выходы регистров с 1-го по N-й подключены к соответствующим информационным входам коммутатора.

Благодаря наличию этих признаков код формирования фазоманипулированного сигнала (код установки фазы) добавляется к коду накопителя в каждом такте его работы, что позволяет исключить из схемы устройства N-1 фазосдвигающих сумматоров, оставив только один фазосдвигающий сумматор, и установив его после накопителя кода. При таком построении устройства время суммирования фазосдвигающего сумматора не должно превышать периода работы накопителя кода, т.е. N•T0.

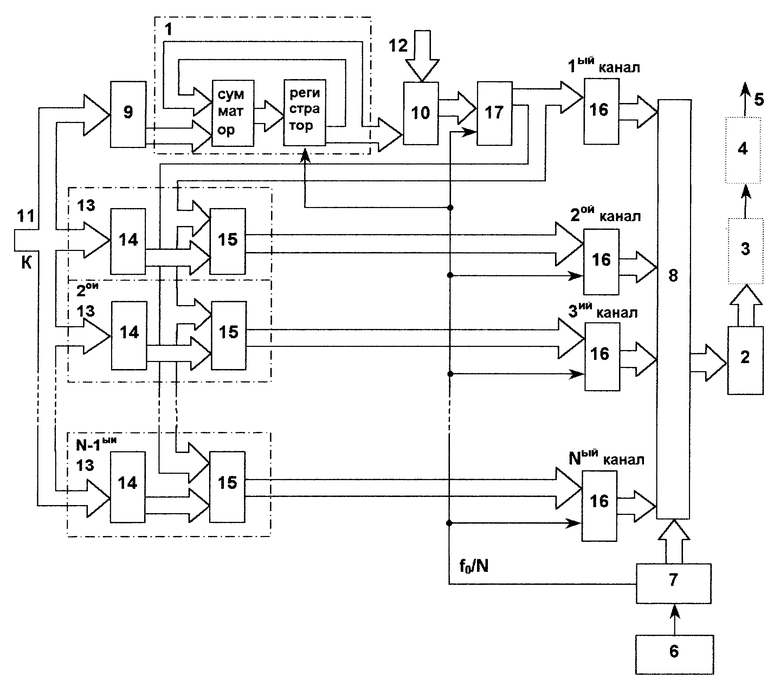

На чертеже представлена структурная схема цифрового синтезатора частот.

Цифровой синтезатор частот содержит накопитель 1 кода, блок 2 памяти амплитуд, цифроаналоговый преобразователь 3, фильтр нижних частот 4, выходную шину 5 устройства, опорный генератор 6, блок синхронизации устройства 7, коммутатор 8, умножитель 9, фазосдвигающий сумматор 10, входную шину 11 кода установки частоты, входную шину 12 кода формирования фазоманипулированного сигнала, N-1 блоков 13 фазового сдвига, каждый из которых содержит формирователь 14 весового коэффициента сдвига и сумматор-вычислитель 15, N регистров 16 и регистр 17 памяти.

Принцип действия предлагаемого цифрового синтезатора частот, как и устройства-прототипа, основан на одновременном формировании кодов N точек отсчета фазы синтезируемого колебания, дискретно сдвинутых друг относительно друга на определенную величину, с последующим выбором кодов данных точек отсчета фазы в определенной последовательности в фиксированные моменты времени для получения требуемой формы выходного синтезируемого колебания.

Синтезатор частот работает следующим образом.

На входной шине 11 кода установки частоты устанавливается кодированное значение синтезируемой частоты K (код установки частоты). Это число поступает на вход умножителя 9, на выходе которого формируется код числа, равный K•N, где N - число каналов устройства. При числе каналов N = 2n (n = 1, 2, 3 ...), умножитель 9 представляет собой регистр сдвига, который выполняет операцию сдвига кода K на n разрядов в сторону увеличения кода. Накопитель 1 кода с тактовой частотой fт = f0/N, где f0 - частота опорного генератора 6, накапливает код К•N, в результате чего на его выходе в каждый тактовый момент времени tт = i•Tт = i/fт, где i = 0, 1, 2, 3 ... - целые числа, формируется код числа, которое пропорционально фазе синтезируемого колебания. С выхода накопителя 1 кода код числа поступает на второй вход фазосдвигающего сумматора 10. На выходе сумматора 10 формируется код числа, соответствующего фазе синтезируемого колебания с учетом сдвига фазы ϕ, заданного кодом формирования фазоманипулируемого сигнала, поступающего на первый вход фазосдвигающего сумматора 10 с входной шины 12 кода формирования фазоманипулируемого сигнала. Выходной код фазосдвигающего сумматора 10 поступает на информационный вход дополнительного регистра 17 памяти и по тактовым импульсам, поступающим на вход синхронизации регистра 17 с первого выхода блока 7 синхронизации устройства, с частотой fт = f0/N переписывается на выход регистра 17. В результате чего на выходе регистра 17 памяти в каждый тактовый момент времени tт формируется код числа, соответствующего фазе синтезируемого колебания с учетом сдвига фазы ϕ.

Код K установки частоты одновременно поступает на входы формирователей 14 весового коэффициента сдвига N-1 блоков 13 фазового сдвига. Формирователь 14 весового коэффициента сдвига выполняет операцию умножения кода K установки частоты на постоянный коэффициент, равный номеру блока фазового сдвига, в результате чего на его выходе образуются коды чисел, равные, по каждому каналу соответственно, K, 2K ... (N-1)К, которые в сумматорах-вычислителях 15 добавляются к выходному коду фазы дополнительного регистра 17 памяти. Таким образом, на выходе блоков 13 фазового сдвига в тактовые моменты времени tт формируются N-1 кодов чисел, пропорциональных фазе синтезируемого колебания с учетом сдвига фазы ϕ, но смещенных относительно выходного кода дополнительного регистра 17 памяти соответственно на K, 2K ... (N-1)K.

Выход дополнительного регистра 17 памяти и выходы N-1 блоков 13 фазового сдвига подключены к информационным входам регистров 16. Регистры 16 по тактовым импульсам с частотой fт = f0/N переписывают информацию с входа на выход, которая далее поступает на соответствующие информационные входы коммутатора 8 из N в один.

Коммутатор 8 с частотой синхронизации f0 в последовательности, задаваемой блоком 7 синхронизации, пропускает на выход входные коды таким образом, что за время Tт=N•T0 (время одного такта работы накопителя 1) на его выходе формируется последовательность кодов чисел, соответствующая фазовым точкам синтезируемого колебания: 0+ϕ, K+ϕ, 2K+ϕ,...(N-1)K+ϕ - в первый такт работы накопителя, NK+ϕ, (N+1)K+ϕ, (N+2)K+ϕ,...(2N-1)K+ϕ - во второй такт, 2NK+ϕ, (2N+1)+ϕ,...(3N-1)+ϕ - в третий такт и т.д., т.е. на выходе коммутатора 8 в каждый тактовый момент времени t0=i•T0, i = 0, 1, 2, 3 ... код фазы выходного синтезируемого колебания изменяется на величину, равную коду частоты K, в то время как на выходах накопителя 1 кода, фазосдвигающего сумматора 10 и блоков 13 фазового сдвига информация меняется на величину N•K и только к моменту времени tт = i•Tт, Tт = T0•N.

Таким образом, тактовая частота работы накопителя 1 кода, блоков фазового сдвига синтезатора предлагаемого устройства и устройства-прототипа одинаковы, а тактовая частота фазосдвигающего сумматора 10 в N раз ниже тактовой частоты фазосдвигающего сумматора первого канала устройства-прототипа.

С выхода коммутатора 8 код числа, пропорциональный фазе синтезируемого колебания, поступает на блок 2 памяти амплитуд. Блок памяти амплитуд представляет собой фазосинусный преобразователь и осуществляет переход от отсчетов кода фазы к отсчетам кода амплитуды синтезируемого колебания, который в цифроаналоговом преобразователе 3 преобразуется в аналоговую величину, т.е. в напряжение, соответствующее входным кодам. Ступенчатый сигнал с выхода ЦАП 3 сглаживается фильтром 4.

В устройстве-прототипе в N раз снижается требование к быстродействию блоков фазового сдвига. При этом быстродействие устройства определяется быстродействием фазосдвигающих сумматоров, потому что время, отводимое фазосдвигающим сумматорам для формирования выходного кода, поступающего на входы коммутатора, неодинаково по каналам и изменяется от Т0 для первого фазосдвигающего сумматора до N•T0 для N-го фазосдвигающего сумматора. В результате этого быстродействие устройства-прототипа ограничено быстродействием фазосдвигающего сумматора первого канала, т.е. его работоспособность обеспечивается только в том случае, если время суммирования первого фазосдвигающего сумматора будет меньше или равно T0.

Введение дополнительного регистра 17 памяти, подключенного к выходу фазосдвигающего сумматора 10, позволяет снизить требование к быстродействию фазосдвигающего сумматора 10 по сравнению с устройством-прототипом в N раз. Фазосдвигающий сумматор 10 в предлагаемом синтезаторе включен между двумя регистрами (регистром накопителя кода и дополнительным регистром 17 памяти), работающими на частоте синхронизации fт = f0/N, поэтому время суммирования фазосдвигающего сумматора 10 становится равным периоду тактовых импульсов накопителя кода Tт = N•T0. В устройстве-прототипе время суммирования фазосдвигающего сумматора первого канала не должно превышать T0 - периода опорного (тактового) сигнала опорного генератора 6.

Подключение последовательно соединенных фазосдвигающего сумматора и дополнительного регистра памяти между выходом накопителя кода и входами кода установки частоты блоков фазового сдвига, позволяет исключить необходимость коррекции кода фазы на сдвиг фазы ϕ в каждом из N каналов, и тем самым сократить число фазосдвигающих сумматоров до одного, т.е. уменьшить в N раз (на N-1) по сравнению с устройством-прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2004 |

|

RU2262190C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2344541C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2002 |

|

RU2223597C1 |

| ЦИФРОВОЙ МНОГОФАЗНЫЙ ГЕНЕРАТОР | 1992 |

|

RU2066918C1 |

| Цифровой синтезатор частот | 1988 |

|

SU1517016A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2012 |

|

RU2490789C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ | 2003 |

|

RU2239281C2 |

Устройство относится к радиотехнике, в частности к технике цифрового вычислительного синтеза частот, и может быть использовано для формирования сетки частот в радиопередающих и радиоприемных устройствах, а также в устройствах синхронизации различного применения. Техническим результатом является упрощение устройства при сохранении диапазона синтезируемых частот с одновременным уменьшением требований к быстродействию фазосдвигающего сумматора. Устройство содержит накопитель 1 кода, блок 2 памяти амплитуд, цифроаналоговый преобразователь 3, фильтр 4 низких частот, выходную шину 5 устройства, опорный генератор 6, блок 7 синхронизации, коммутатор 8, умножитель 9, фазосдвигающий сумматор 10, входную шину 11 кода установки частоты, входную шину 12 кода формирования фазоманипулированного сигнала, N-1 блоков фазового сдвига, N регистров 16 и регистр 17 памяти. 1 ил.

Цифровой синтезатор частот, содержащий накопитель кода, блок памяти амплитуд, выходную шину устройства, опорный генератор, блок синхронизации, коммутатор, умножитель, фазосдвигающий сумматор, входную шину кода установки частоты, входную шину кода формирования фазоманипулированного сигнала, N - 1 блоков фазового сдвига и N регистров, где N - число каналов синтезатора, причем входная шина кода установки частоты синтезатора подключена к входам кода установки частоты N - 1 блоков фазового сдвига и к входу умножителя, выход которого подключен к входу накопителя кода, а выходы N - 1 блоков фазового сдвига - к соответствующим информационным входам регистров с второго по N-й, входная шина кода формирования фазоманипулированного сигнала синтезатора подключена к первому входу фазосдвигающего сумматора, выход опорного генератора - к входу блока синхронизации, первый выход которого подключен к входу синхронизации накопителя кода и входам синхронизации регистров с первого по N-й, а группа выходов блока синхронизации подключена к управляющим входам коммутатора, выход которого подключен к входу блока памяти амплитуд, выход которого подключен к выходу синтезатора, отличающийся тем, что в него дополнительно введен регистр памяти, вход синхронизации которого подключен к первому выходу блока синхронизации, информационный вход - к выходу фазосдвигающего сумматора, а выход - к входам кода фазы N - 1 блоков фазового сдвига и информационному входу первого регистра, при этом второй вход фазосдвигающего сумматора подключен к выходу накопителя кода, а выходы регистров с первого по N-й включительно подключены к соответствующим информационным входам коммутатора.

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1517016A1 |

| US 4933890 A, 12.06.1990 | |||

| US 4958310 A, 18.08.1990. | |||

Авторы

Даты

2000-07-27—Публикация

1998-09-08—Подача