Изобретение относится к электросвязи и может найти применение в автоматизированных системах управления технологическими процессами, в телемеханике и локальных вычислительных системах.

Известны устройства сопряжения ЭВМ с общим каналом связи, в большинстве из которых реализованы стандартные процедуры обмена дискретными сообщениями, отличающиеся лишь способами организации доступа передатчиков информации к общему каналу (моноканалу) связи.

Передача многоадресных сообщений в известных устройствах осуществляется двумя способами. При малом количестве адресов получателей многоадресное сообщение передается поочередно каждому получателю как обычное одноадресное сообщение.

В случае большого количества адресатов получателей сообщение передается всем получателям одновременно. При этом передача подтверждений (квитанций) о приеме сообщения производится поочередно в алгоритме передачи их потребителями как одноадресных сообщений.

Наиболее близким к данному устройству является "Контроллер WD 2840", содержащий ЭВМ потребителя, информационные и командные выходы и входы которой через блоки системного интерфейса соединены соответственно с абонентскими входами и выходами адаптера связи, канальные выходы и входы которого соединены с информационными входами и выходами передающего и приемного накопителей, а управляющие входы и выходы соединены с соответствующими выходами и входами команд и состояний, блока доступа и блока синхронизации, канальный выход кодирующего блока соединен с входом передатчика, выход которого подключен к моноканалу, информационный вход приемного накопителя соединен с выходом декодирующего устройства и входом блока синхронизации, вход декодирующего устройства (блока) соединен с выходом приемника, вход которого подключен к моноканалу, выход приемника соединен с входом блока синхронизации и входом блока обнаружения маркера, выход которого соединен с управляющими входами кодирующего и декодирующего блоков и блока доступа, выходы которого соединены с управляющими входами адаптера связи, регистра команд и состояний, кодирующего и декодирующего блоков, генератор тактовых импульсов, выход которого соединен с входами блока синхронизации и блока опорных частот, выходы тактовых частот которого соединены с управляющими входами приемного и передающего накопителей, кодирующего и декодирующего блоков.

Недостатком известного устройства является большое время передачи многоадресного сообщения.

Целью изобретения является сокращение времени передачи многоадресных сообщений и квитирующих сигналов о доведении этих сообщений до получателей.

Поставленная цель достигается тем, что в устройство, содержащее ЭВМ потребителя, информационные и командные выходы и входы которых через блоки системного интерфейса соединены соответственно с абонентскими входами и выходами адаптера связи, канальные выходы и входы которого соединены с информационными входами и выходами передающего и приемного накопителей, а управляющие входы и выходы соединены с соответствующими выходами и входами регистра команд и состояний, блока доступа и блока синхронизации, канальный выход кодирующего блока соединен с входом передатчика, выход которого подключен к моноканалу, информационный вход приемного накопителя соединен с выходом декодирующего устройства и входом блока синхронизации, вход декодирующего блока соединен с выходом приемника, вход которого подключен к моноканалу, выход приемника соединен с входом блока синхронизации и входом блока обнаружения маркера, выход которого соединен с управляющими входами кодирующего и декодирующего блоков и блока доступа, выходы которого соединены с управляющими входами адаптера связи, регистра команд и состояний, генератор тактовых импульсов, выход которого соединен с входами блока синхронизации и блока опорных частот, выходы тактовых частот которого соединены с управляющими входами приемного и передающего накопителей, кодирующего и декодирующего блоков, включены первый, второй и третий дешифраторы, входы которых соединены с выходами передающего накопителя, четвертый дешифратор, вход которого соединен с выходом декодирующего блока, первый триггер, входы которого соединены с выходами первого и второго дешифраторов, второй триггер, первый вход которого соединен с выходом третьего дешифратора, первый и второй реверсивный счетчики, установочные входы которых соединены с выходом первого дешифратора, первый и второй элементы И, первые входы которых соответственно соединены с выходами первого и второго триггеров, а вторые входы - с выходами блока опорных частот, выходы элементов И соединены с входами прямого и обратного счета первого реверсивного счетчика, пятый и шестой дешифраторы, входы которых соединены соответственно с выходами первого и второго реверсивных счетчиков, вход прямого счета первого реверсивного счетчика соединен с выходом четвертого дешифратора, а вход обратного счета - с выходом первого элемента И, третий, четвертый элементы И и элемент ЗАПРЕТ, выходы которых соединены с входом записи регистра команд и состояний, входы третьего элемента И соединены с выходами второго триггера, четвертого дешифратора и первого реверсивного счетчика, входы четвертого элемента И соединены с выходами пятого и шестого дешифраторов, вход записи элемента ЗАПРЕТ соединен с выходом третьего дешифратора, вход считывания элемента ЗАПРЕТ - с выходом пятого дешифратора, а вход элемента ЗАПРЕТ - с выходом четвертого элемента И.

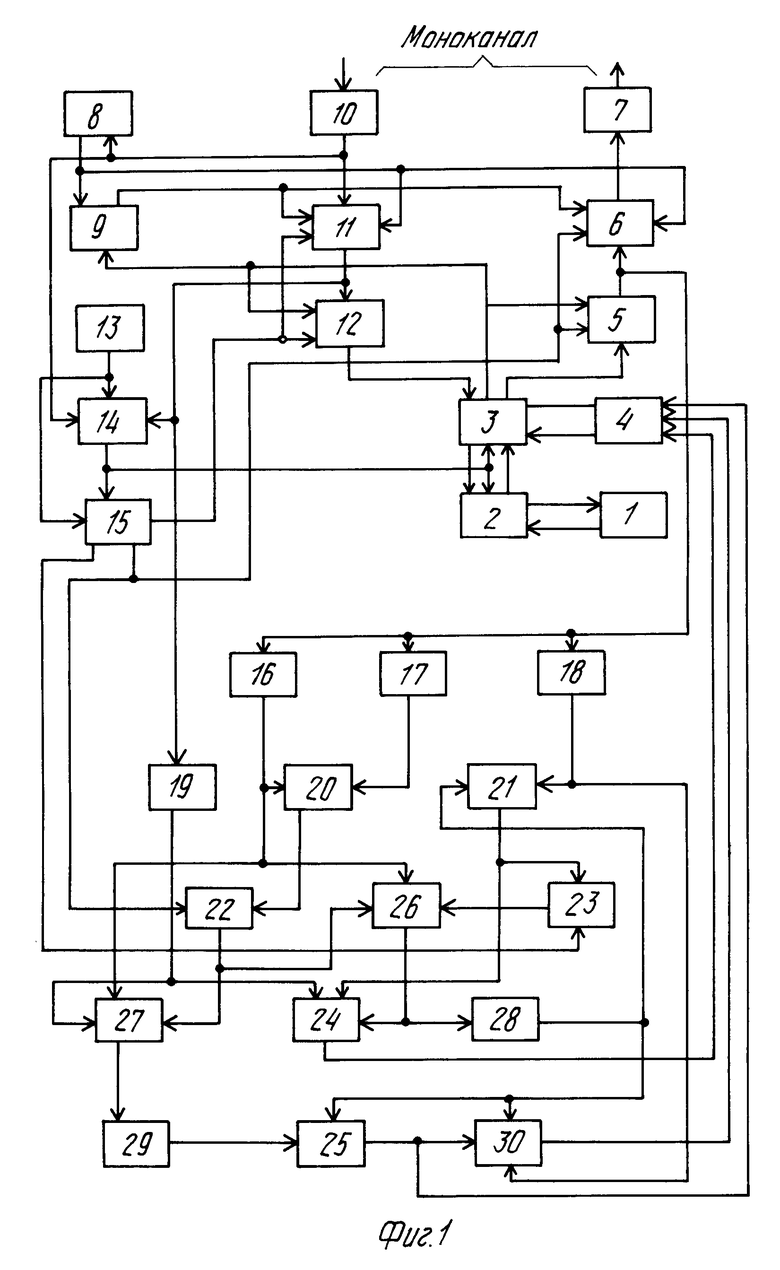

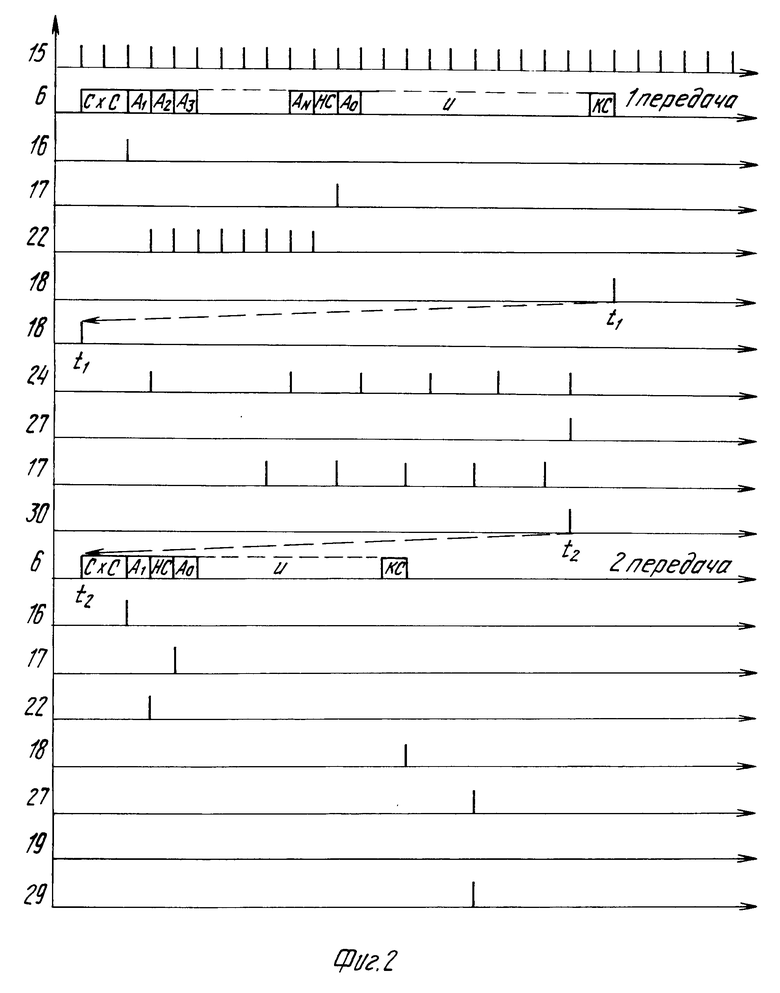

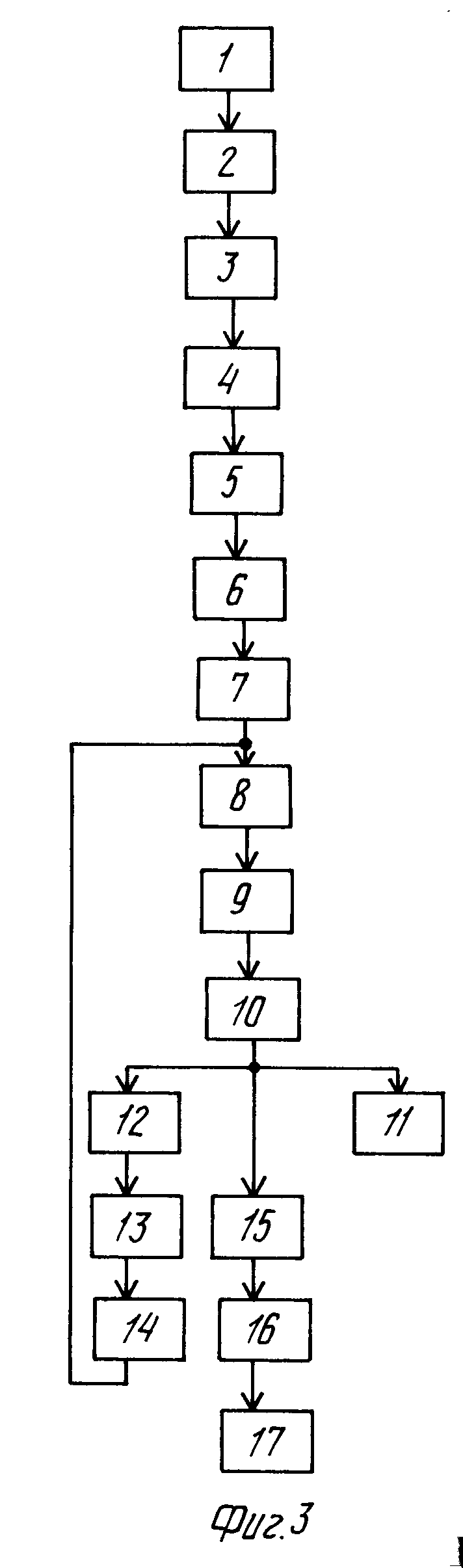

На фиг.1 показана функциональная схема устройства; на фиг.2 - временная диаграмма; на фиг.3 - алгоритм работы устройства: а - начало; б - ретрансляция сообщения из ЭВМ в адаптер связи; в - генерация кадра; г - запись кадра в передающий накопитель; д - ожидание маркера; е - выделение маркера; ж - занятие канала; з - передача кадра; и - переключение контроллера в режим приема квитирующих сигналов; к - запись в регистр команд порядковых номеров получателей кадра, по которым получены квитирующие сигналы (с выхода блока 26 фиг. 1); л - запись формуляров квитанций; м - исключение из заголовка кадра адресов по которым получены квитанции; н - уплотнение заголовка кадра (сдвиг знаков) в накопителе передачи; о - запись команды повторить передачу кадра (с выхода блока 29 фиг.1); п - запись команды конец передачи кадра; р - передача маркера; с - ожидание передачи следующего кадра.

Устройство сопряжения ЭВМ с моноканалом содержит ЭВМ потребителя 1, блоки 2 системного интерфейса, адаптер связи 3, регистр 4 команд и состояний, передающий накопитель 5, кодирующий блок 6, передатчик 7, блок 8 обнаружения маркера, блок 9 доступа, приемник 10, декодирующий блок 11, приемный накопитель 12, генератор 13 тактовых импульсов, блок 14 синхронизации, блок 15 опорных частот, первый 16, второй 17, третий 18, четвертый 19 дешифраторы комбинаций знаков синхросигнала, начала, конца сообщения и квитирующего сигнала, первый 20 и второй 21 триггеры, первый 22, второй 23, третий 24, четвертый 25 элементы И, первый 26, второй 27 реверсивные счетчики, пятый 28, шестой 29 дешифраторы нулевых состояний реверсивных счетчиков, элемент ЗАПРЕТ 30.

ЭВМ потребителя 1 своими информационными и командными выходами и входами с помощью блоков 2 системного интерфейса соединена соответственно с абонентскими входами и выходами адаптера связи 3. Канальные выходы и входы адаптера связи 3 соединены с информационными входами и выходами передающего 5 и приемного 12 накопителей, а управляющие - с соответствующими входами и выходами регистра 4 команд и состояний, блока 9 доступа и блока 14 синхронизации. Выход передающего 5 накопителя соединен с входом кодирующего блока 6, подключенного своим выходом к входу передатчика 7. Выход передатчика 7 и вход приемника 10 подключены к общему каналу (моноканалу) связи. Выход приемника 10 соединен с входами блока 8 обнаружения маркера, блока 14 синхронизации и декодирующего блока 11, выход которого соединен с входами приемного 12 накопителя, блока синхронизации 14, дешифратора 19 квитирующего сигнала.

Выход блока 8 обнаружения маркера соединен с входами кодирующего 6 и декодирующего 11 блоков и блока 9 доступа, выходы которого соединены с управляющими входами кодирующего 6 и декодирующего 11 блоков, адаптера связи 3 и регистра 4 команд и состояний. Выход генератора 13 тактовых импульсов соединен с входами блока 14 синхронизации и блока 15 опорных частот, выходы которых соединены с управляющими входами блоков 2, 3, 5, 6, 11, 12 и входами элементов И 22 и 23. Входы дешифратора 16 знака синхросигнала, дешифратора 17 знака начала сообщения, дешифратора 18 знака конца сообщения соединены с входом декодирующего блока 6. Выход дешифратора 16 соединен с установочными входами первого 26 и второго 27 реверсивных счетчиков и входом первого триггера 20, выход которого соединен с входом первого элемента И 22, выход последнего соединен с входом обратного счета первого реверсивного счетчика 26 и входом прямого счета второго реверсивного счетчика 27. Выход второго дешифратора 17 соединен с вторым входом первого триггера 20. Выход третьего дешифратора 18 соединен с входом второго элемента И 23 и входом записи элемента ЗАПРЕТ 30, выход которого соединен с входом записи регистра 4 команд и состояний. Выход второго элемента И 23 соединен с входом прямого счета первого реверсивного счетчика 26. Выход четвертого дешифратора 4 соединен с входом обратного счета второго реверсивного счетчика 27 и входом третьего 24 элемента И 24, выход которого соединен с входом регистра 4 команд и состояний.

Выход первого 26 реверсивного счетчика соединен с входом пятого дешифратора 28 и входом третьего элемента И 24, выход которого соединен с входом регистра 4 команд и состояний. Выход второго реверсивного счетчика 27 соединен с входом шестого дешифратора 29, выход которого соединен с входом четвертого элемента И 25, выход которого соединен с запрещающим входом элемента ЗАПРЕТ 30. Выход шестого дешифратора 28 соединен с входом считывания элемента ЗАПРЕТ 30, вторым входом элемента И 25 и входом второго триггера 21, выход которого соединен с входом второго 23 и третьего 24 элементов И.

Устройство в случае его использования в составе системы передачи дискретных сообщений с применением корректирующих кодов для обмена кодограммами между рядами приемопередатчиков, подключенных к общему каналу связи, работает следующим образом.

Сформированная с помощью ЭВМ потребителя 1 одноадресная или многоадресная кодограмма с необходимыми служебными знаками, адресами отправителя и получателей в соответствии со структурой, изображенной на фиг.2 (п.6), с помощью блоков 2 системного интерфейса транслируется в адаптер связи 3. Адаптер связи 3 производит генерацию кадра сообщения, запись его в передающий накопитель 5 и по окончании записи кадра переводит блок 9 доступа в режим ожидания маркера. При выделении блоком 8 обнаружения маркера, поступившего из моноканала и принятого приемником 10 сигнала маркера, последний воздействует на кодирующий 6 и декодирующий 7 блоки и блок 9 доступа, выходные сигналы которого поступают на управляющие входы блоков 3, 4, 6, 11 и переводят тракты передачи и приема соответственно в режимы передачи информации и приема квитирующих сигналов о доведении кадра сообщения до получателей.

Этот режим работы реализуется с помощью процедур, указанных на фиг.3 (ж, з,и,) в соответствии с принятыми стандартами обмена информации по локальным вычислительным сетям и применяемой технической базой.

Передача кадра сообщения обеспечивается подачей тактовых импульсов с выхода блока 15 опорных частот и управляющих сигналов с выхода адаптера связи 3 на входы передающего накопителя 5 и кодирующего блока 6. Кодовые комбинации сообщения с информационного выхода передающего накопителя 5 через кодирующий блок 6 с помощью передатчика 7 транслируются в моноканал и далее к приемникам получателей сообщений.

Исходные тактовые импульсы, необходимые для работы устройства, формируются генератором 13 тактовых импульсов, блоком синхронизации 14 и блоком 15 опорных частот.

При поступлении с выхода передающего накопителя 5 кодовой комбинации синхросигнала на вход первого дешифратора 16 его выходной сигнал воздействует на первый вход первого триггера 20, и установочные входы первого 26 и второго 27 реверсивных счетчиков, переводя их в нулевые состояния.

Выходной сигнал триггера 20, подаваемый на первый вход первого элемента И 22, разрешает последнему выдачу на входы прямого счета первого 26 и второго 27 реверсивных счетчиков цикловых импульсов границ адресных комбинаций, поступающих на второй вход элемента И 22 с выхода блока 15 опорных частот. Прекращение подачи этих импульсов на входы прямого счета реверсивных счетчиков 26, 27 происходит при выделении комбинации знака начала сообщения вторым дешифратором 17, выходной сигнал которого, поступающий на второй вход триггера 20, переводит его в состояние, при котором снимается разрешающий сигнал с входа элемента И 22.

Таким образом, обеспечивается счет и запоминание первым 26 и вторым 27 реверсивным счетчиками числа адресов получателей многоадресного сообщения.

При выделении комбинации знака конца сообщения третьим 18 дешифратором его выходной сигнал поступает на вход записи элемента ЗАПРЕТ 30 и на первый вход второго триггера 21. Выходной сигнал триггера 21 является разрешающим для второго 23 и третьего 24 элементов И. Второй элемент И 23 обеспечивает подачу на вход обратного счета первого реверсивного счетчика 26 от блока 15 опорных частот импульсов соответствующих границ временных интервалов, в которые должны поочередно передаваться квитирующие сигналы от получателей сообщений. Третий элемент И 24 обеспечивает передачу параллельным кодом с выхода первого 26 реверсивного счетчика номеров временных интервалов, в которые поступили квитирующие сигналы от получателей сообщений, на вход записи регистра 4 команд и состояний. Это обеспечивается подачей на третий вход элемента И 24 выходных сигналов четвертого дешифратора 19 комбинаций знаков о приеме сообщений, поступающих из моноканала через приемник 10, декодирующий блок 11 на входы приемного накопителя 12 и четвертого 19 дешифратора.

При этом предполагается, что получатели сообщения передают квитирующие сигналы по окончании приема кадра во временные интервалы, сформированные в обратном порядке следования адресных комбинаций между комбинациями знаков синхросигнала и начала сообщения (адресат, получивший сообщение, адрес которого расположен перед знаком начала сообщения, передает квитанцию первым; адресат с комбинацией адреса после синхросигнала передает квитанцию последним).

Структура квитирующего сигнала не содержит адресной информации, поскольку его идентификация отправителем сообщения производится по номеру временного интервала, в который он принимается. Квитирующий сигнал с выхода четвертого дешифратора 19 одновременно подается на вход обратного счета второго реверсивного счетчика 27. При фиксации пятым дешифратором 28 нулевого состояния первого реверсивного счетчика 26, счет временных интервалов ожидания и приема квитанций прекращается подачей выходного сигнала этого дешифратора на второй вход триггера 21. Выходной сигнал дешифратора 28 также поступает на вход считывания элемента ЗАПРЕТ 30 и разрешающий вход четвертого элемента И 25, на второй вход которого поступает сигнал с выхода шестого дешифратора 29, фиксирующего нулевое состояние второго 27 реверсивного счетчика. При этом в случае отсутствия запрещающего сигнала с выхода четвертого элемента И 25 выходной сигнал элемента ЗАПРЕТ 30, поступающий на вход регистра 4 команд и состояний, обеспечивает повторную передачу кадра получателем, не передавшим квитанции по результатам первого приема сообщения.

Необходимые для повторной передачи изменения заголовка сообщения и его уплотнение за счет невключения адресов получателей, от которых получены квитирующие сигналы, осуществляются адаптером связи 3 реализацией процедур и-о, показанных на фиг.3.

Прием квитанций от всех получателей многоадресного сообщения фиксируется выходным сигналом четвертого элемента И 25 при поступлении на его входы сигналов с выходов пятого 28 и шестого 29 дешифраторов нулевых состояний первого 26 и второго 27 реверсивных счетчиков.

Сигналом с выхода четвертого элемента И 25, поступающим на вход регистра 4 команд и состояний, устройство переводится в режим ожидания передачи очередного кадра сообщения.

Временная диаграмма работы устройства при передаче многоадресного сообщения показана на фиг.2.

Вторая передача иллюстрирует работу устройства при повторной передаче сообщения одному из получателей, не принявшему сообщение в первом цикле передачи, и одновременно поясняет работу устройства при передаче одноадресного сообщения.

Алгоритм работы адаптера связи 3, показанный на фиг.3, состоит из известных процедур и не требует никаких изменений в алгоритмах работы блоков 2 системного интерфейса и ЭВМ потребителя 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ОБШИМ КАНАЛОМ СВЯЗИ | 1995 |

|

RU2103730C1 |

| Устройство сопряжения ЭВМ с общим каналом связи | 1988 |

|

SU1668980A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ | 1991 |

|

RU2020595C1 |

| Устройство для приоритетного обслуживания сообщений | 1981 |

|

SU1012257A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| Устройство для приоритетного обслуживания сообщений | 1976 |

|

SU636610A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ ПО ВОКОДЕРНОМУ ТРАКТУ | 1991 |

|

RU2010439C1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ РАДИОТЕЛЕГРАФИСТОВ | 1991 |

|

RU2020538C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ИНДИКАЦИИ ПЛЕНКИ В ЛЕНТОПРОТЯЖНОМ ТРАКТЕ ФОТОАППАРАТА | 1997 |

|

RU2158950C2 |

Изобретение относится к области телемеханики и локальных вычислительных систем. Цель изобретения - сокращение времени передачи многоадресных сообщений. Общий канал связи, по которому производится обмен сообщениями, соединен с контроллером, содержащим блоки обнаружения маркера и доступа, приемник, передатчик, кодирующий и декодирующий блоки, приемный и передающий накопители, генератор тактовых импульсов, блоки синхронизации и опорных частот, адаптер связи и регистр команд и состояний, блоки системного интерфейса и ЭВМ потребителя. К информационным трактам контроллера подключены дешифраторы комбинаций знаков синхросигнала, начала, конца сообщения, квитирующего сигнала, дешифраторы нулевых состояний реверсивных счетчиков, управляющие работой первого и второго реверсивных счетчиков, выходы которых через элементы И и элемент запрет соединены с входами регистра команд первой и второй триггеры. 3 ил.

УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ, содержащее блоки системного интерфейса, информационные и командные выходы и входы которых являются одноименными входами и выходами устройства для подключения к ЭВМ и соединены соответственно с абонентскими входами и выходами адаптера связи, канальные выходы и входы которого соединены с информационными входами и выходами передающего и приемного накопителей, а управляющие входы и выходы соединены с соответствующими выходами и входами регистра команд и состояний, блока доступа и блока синхронизации, канальный выход кодирующего блока соединен с входом передатчика, выход которого является выходом устройства для подключения к многоканалу, информационный вход приемного накопителя соединен с выходом декодирующего блока и входом блока синхронизации, вход декодирующего блока соединен с выходом приемника, вход которого является входом устройства для подключения к многоканалу, выход приемника соединен с входом блока синхронизации и входом блока обнаружения маркера, выход которого соединен с управляющими входами кодирующего и декодирующего блоков и блока доступа, выходы которого соединены с управляющими входами адаптера связи, регистра команд и состояний, кодирующего и декодирующего блоков, генератор тактовых импульсов, выход которого соединен с входами блока синхронизации и блока опорных частот, выходы тактовых частот которого соединены с управляющими входами приемного и передающего накопителей, кодирующего и декодирующего блоков, отличающееся тем, что, с целью сокращения времени передачи многоадресных сообщений и квитирующих сигналов о доведении этих сообщений до получателей, в него введены первый, второй и третий дешифраторы, входы которых соединены с выходом передающего накопителя, четвертый дешифратор, вход которого соединен с выходом декодирующего блока, первый триггер, входы которого соединены с выходами первого и второго дешифраторов, второй триггер, первый вход которого соединен с выходом третьего дешифратора, первый и второй реверсивные счетчики, установочные входы которых соединены с выходом первого дешифратора, первый и второй элементы И, первые входы которых соответственно соединены с выходами первого и второго триггеров, а вторые входы-с выходами блока опорных частот, выходы первого и второго элементов И соединены с входами прямого и обратного счета реверсивного счетчика, пятый и шестой дешифраторы, входы которых соединены соответственно с выходами первого и второго реверсивных счетчиков, вход прямого счета первого реверсивного счетчика соединен с выходом четвертого дешифратора, а вход обратного счета - с выходом первого элемента И, третий, четвертый элементы И и элемент ЗАПРЕТ, выходы которых соединены с входом записи регистра команд и состояний, входы третьего элемента И соединены с выходами второго триггера, четвертого дешифратора и первого реверсивного счетчика, входы четвертого элемента И соединены с выходами пятого и шестого дешифратора, вход записи элемента ЗАПРЕТ соединен с выходом третьего дешифратора, вход считывания элемента ЗАПРЕТ - с выходом пятого дешифратора, а вход элемента ЗАПРЕТ - с выходом четвертого элемента И.

| Бойченко Е.В | |||

| Методы схемотехнического проектирования распределенных информационно-вычислительных микропроцессорных систем | |||

| М.: Энергоатомиздат, 1988, с.67, рис.2.16. |

Авторы

Даты

1995-03-27—Публикация

1991-01-29—Подача