Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением.

Известно устройство для цикловой синхронизации [1], содержащее опознаватель синхросигнала, анализатор совпадения синхросигнала, вход устройства, блок выделения тактовой частоты, распределитель импульсов, выход устройства, триггер, первый, второй и третий элементы И, элемент ИЛИ, регистр, соединенные определенным образом.

Данное устройство сокращает время вхождения в синхронизм за счет дополнительного регистра. Однако это устройство имеет ряд недостатков:

- увеличение времени поиска синхронизма, особенно при последовательном поиске, при искажениях символов синхрокомбинации;

- достаточно большие аппаратные затраты за счет применения входных регистров, так как длина цикла может достигать нескольких тысяч бит, происходит неоправданное увеличение разрядности входного регистра до этой величины;

- неустойчивая работа анализатора совпадения, так как при изменении атмосферных условий (температура, влажность) параметры конденсатора, резистора и диода могут изменяться в широких пределах, а также различные промежутки между позициями синхрокомбинации в цифровых системах передачи информации требуют для каждого случая подбора параметров емкости и резисторов.

Наиболее близким по технической сущности к заявленному изобретению является выбранный в качестве прототипа приемник синхросигнала [2], содержащий опознаватель, состоящий из регистра сдвига и дешифратора, устройство удержания синхронизма, состоящее из накопителя по выходу из синхронизма, устройства формирования весовых коэффициентов К1, сумматора, порогового устройства, генераторного оборудования, элементов И1, И3, НЕТ1, ИЛИ1, устройство поиска синхронизма, состоящее из накопителя по входу в синхронизм, устройства формирования весовых коэффициентов К2, делителя частоты, триггера и элементов И2, И4, НЕТ2, ИЛИ2, блок выделения тактовой частоты и канальный распределитель, соединенные определенным образом.

Недостатками данного устройства являются:

- невозможность одним и тем же приемником осуществить цикловую синхронизацию широкого класса цифровых передач информации;

- увеличение времени поиска синхронизма при искажениях синхрокомбинации, связанного с искажениями символов в линейном тракте;

- увеличение аппаратных затрат за счет использования регистра сдвига с большим числом разрядов при цикловой синхронизации различных передач информации;

- усложнение устройства за счет применения для фазирования двух достаточно сложных устройств поиска и удержания синхронизма, что также приводит к увеличению оборудования.

При последовательном поиске искажение синхрокомбинации на начальной стадии поиска синхронизма приводит к увеличению в два раза времени обнаружения первой синхрокомбинации, а при искажении N-раз подряд синхрокомбинации время ее обнаружения увеличивается в (N+l)-paз. Среднее время обнаружения при последовательном поиске первой синхрокомбинации в случае отсутствия ее искажения равно:

t•(n/2)2,

где t - длительность цикла передачи информации;

n - количество позиций в цикле.

Технической задачей изобретения является расширение функциональных возможностей, позволяющих осуществить синхронизацию различных передач информации с асинхронным объединением цифровых потоков, уменьшение времени поиска синхронизма и сокращение оборудования.

Указанная задача решается тем, что в устройство для цикловой синхронизации, содержащее дешифратор, опознаватель, фазирующее устройство (ФУ) и генераторное оборудование (ГО), причем тактовый вход устройства для цикловой синхронизации (ЦС) соединен с соответствующими входами дешифратора, опознавателя и ГО, а информационный вход устройства для ЦС соединен с соответствующим входом дешифратора, выход отклика опознавателя соединен с соответствующим входом ФУ, выход нулевого состояния которого соединен с соответствующим входом ГО, выход наличия синхронизации ФУ является выходом устройства для ЦС, адресные 1 - N выходы ГО являются соответствующими выходами устройства для ЦС, введены запоминающее устройство (ЗУ), распределитель, задающее устройство, первое и второе устройство совпадения, первый, второй и третий триггеры, инвертор, первый, второй, третий, четвертый и пятый элементы И, первый, второй и третий элементы ИЛИ, причем адресные 1 - N входы ЗУ соединены с соответствующими выходами ГО, выход позиции конца цикла ЗУ соединен с соответствующим входом ГО и является выходом устройства для ЦС, выходы значения синхрокомбинации и позиции синхрокомбинации ЗУ соединены с соответствующими входами дешифратора, выход позиции конца синхрокомбинации ЗУ соединен с соответствующим входом распределителя, тактовый вход которого соединен с тактовым входом устройства для ЦС, тактовые входы второго и третьего триггеров соединены с тактовым входом устройства для ЦС, выход дешифратора соединен с вторым входом первого элемента ИЛИ, вторыми входами первого, второго и третьего элементов И, а также с четвертыми входами четвертого и пятого элементов И, вход разрешения опознавателя соединен с выходом третьего элемента ИЛИ, первый выход и третий выход распределителя соединены с соответствующими входами опознавателя, второй выход распределителя соединен с соответствующими входами опознавателя, ГО и ФУ, а также со входом установки в ноль второго и третьего триггеров, вход установки в максимальное состояние ФУ соединен с выходом первого устройства совпадения, вход установки в ноль ФУ соединен с выходом второго устройства совпадения, выходы 1 - m разрядов ФУ соединены с соответствующими входами первого и второго устройств совпадения, выходы параметров критериев входа в синхронизм 1 - 1,..., L - 1 задающего устройства соединены с соответствующими входами первого устройства совпадения, а выходы параметров критериев выхода из синхронизма 1 - 2,..., К - 2 задающего устройства соединены с соответствующими входами второго устройства совпадения, информационный вход первого триггера соединен с шиной питания, тактовый вход первого триггера соединен с выходом нулевого состояния ФУ, вход установки в ноль первого триггера соединен с выходом второго состояния ФУ, выход первого триггера соединен с входом инвертора и вторыми входами четвертого и пятого элементов И, выход инвертора соединен с первым входом первого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, первый вход второго элемента И соединен с выходом установки режима 0 задающего устройства, выход второго элемента И соединен с вторым входом третьего элемента ИЛИ, выход второго триггера соединен с первым входом первого элемента ИЛИ, с первым входом третьего элемента И и с третьим входом четвертого элемента И, первый вход четвертого элемента И соединен с выходом установки режима 1 задающего устройства, выход четвертого элемента И соединен с третьим входом третьего элемента ИЛИ, выход первого элемента ИЛИ соединен с информационным входом второго триггера, выход третьего элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с информационным входом третьего триггера, выход которого соединен с первым входом второго элемента ИЛИ и третьим входом пятого элемента И, первый вход пятого элемента И соединен с выходом установки режима 2 задающего устройства, выход пятого элемента И соединен с четвертым входом третьего элемента ИЛИ.

Новизна технического решения заключается в наличии в заявленном устройстве новых схемных элементов: запоминающего устройства, распределителя, задающего устройства, первого и второго устройств совпадения, первого, второго и третьего триггеров, инвертора, первого, второго, третьего, четвертого и пятого элементов И, первого второго и третьего элементов ИЛИ.

Таким образом, изобретение соответствует критерию "новизна".

Анализ известных технических решений в исследуемой и смежной областях позволяет сделать вывод, что введенные функциональные узлы известны. Однако введение их в устройство для цикловой синхронизации с указанными связями придает ему новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют расширить его функциональные возможности, уменьшить время поиска синхронизма при сокращении оборудования.

Таким образом, изобретение соответствует критерию "Изобретательский уровень", так как оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передачи высших порядков с асинхронным объединением цифровых потоков.

Таким образом, изобретение соответствует критерию "Промышленная применимость".

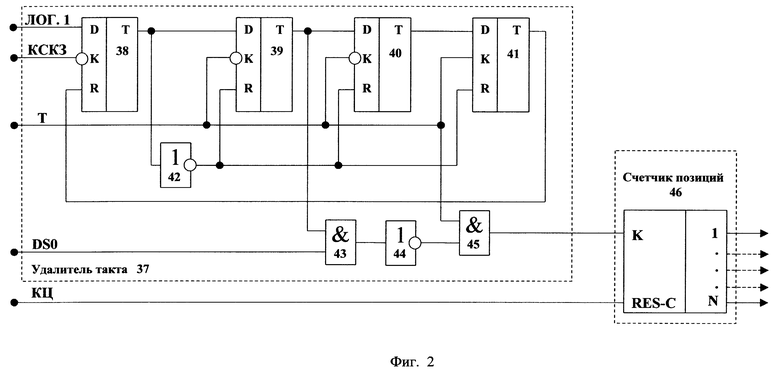

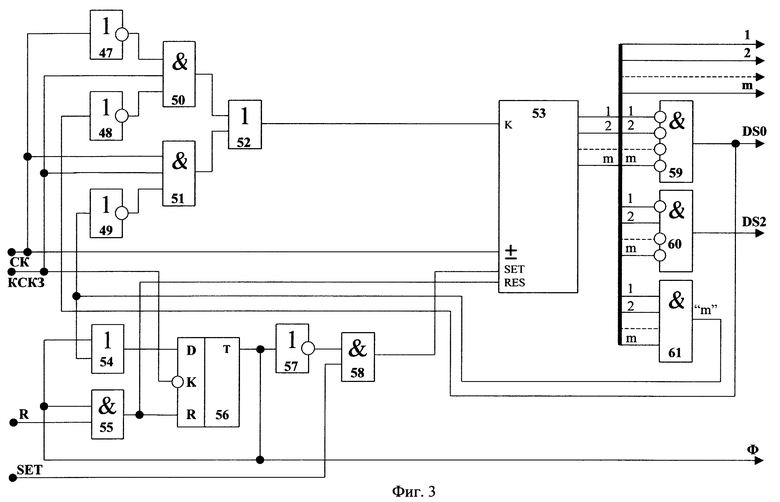

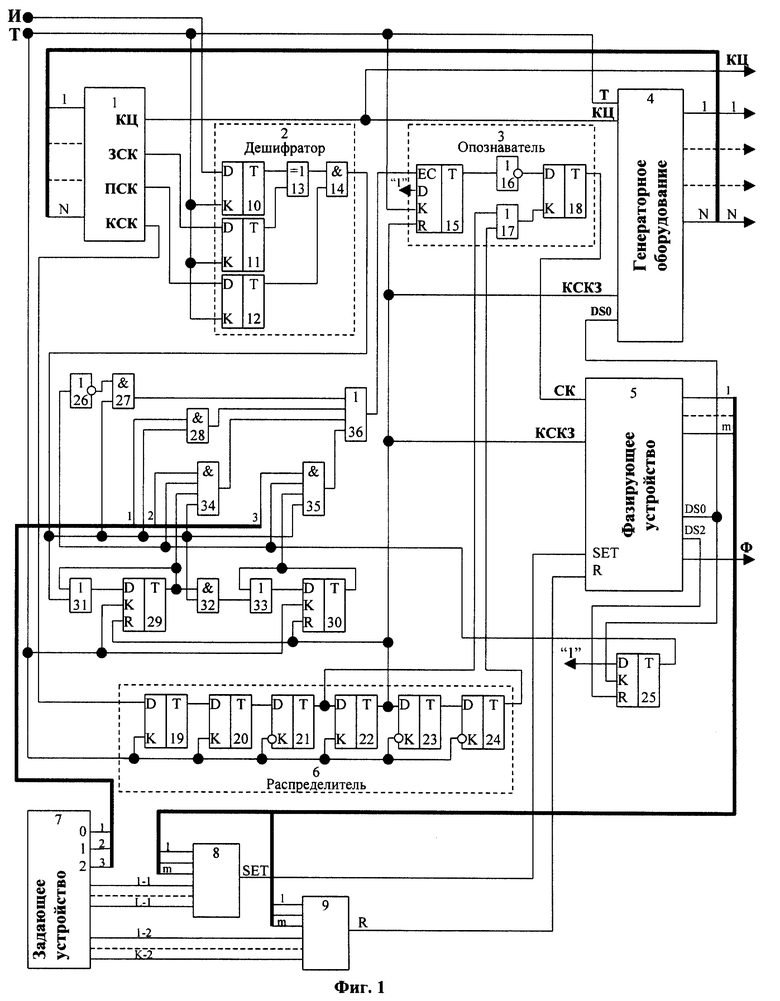

На фиг.1 представлена структурная электрическая схема предлагаемого устройства для цикловой синхронизации, на фиг.2 - электрическая схема генераторного оборудования, на фиг.3 - электрическая схема фазирующего устройства.

Устройство для цикловой синхронизации (ЦС) содержит запоминающее устройство 1 (ЗУ), дешифратор 2, опознаватель 3, генераторное оборудование 4 (ГО), фазирующее устройство 5 (ФУ), распределитель 6, задающее устройство 7, первое и второе устройство совпадения 8 и 9, первый, второй и третий триггеры 10, 11 и 12, инвертор 13, первый, второй, третий, четвертый и пятый элементы И 14, 15, 16, 17 и 18, первый, второй и третий элементы ИЛИ 19, 20 и 21, причем тактовый вход устройства для ЦС соединен с соответствующими входами дешифратора 2, опознавателя 3 и ГО, а информационный вход устройства для ЦС соединен с соответствующим входом дешифратора 2, выход отклика опознавателя 3 соединен с соответствующим входом ФУ, выход нулевого состояния которого соединен с соответствующим входом ГО, выход наличия синхронизации ФУ является выходом устройства для ЦС, адресные 1-N выходы ГО являются соответствующими выходами устройства для ЦС, адресные 1 - N входы ЗУ соединены с соответствующими выходами ГО, выход позиции конца цикла ЗУ соединен с соответствующим входом ГО и является выходом устройства для ЦС, выходы значения синхрокомбинации и позиции синхрокомбинации ЗУ соединены с соответствующими входами дешифратора 2, выход позиции конца синхрокомбинации ЗУ соединен с соответствующим входом распределителя 6, тактовый вход которого соединен с тактовым входом устройства для ЦС, тактовые входы второго и третьего триггеров 11 и 12 соединены с тактовым входом устройства для ЦС, выход дешифратора 2 соединен с вторым входом первого элемента ИЛИ19, вторыми входами первого, второго и третьего элементов И14, 15 и 16, а также с четвертыми входами четвертого и пятого элементов И17 и 18, вход разрешения опознавателя 3 соединен с выходом третьего элемента ИЛИ21, первый выход и третий выход распределителя 6 соединены с соответствующими входами опознавателя 3, второй выход распределителя 6 соединен с соответствующими входами опознавателя 3, ГО и ФУ, а также со входом установки в ноль второго и третьего триггеров 11 и 12, вход установки в максимальное состояние ФУ соединен с выходом первого устройства совпадения 8, вход установки в ноль ФУ соединен с выходом второго устройства совпадения 9, выходы 1 - m разрядов ФУ соединены с соответствующими входами первого и второго устройств совпадения 8 и 9, выходы параметров критериев входа в синхронизм 1 - 1,..., L - 1 задающего устройства 7 соединены с соответствующими входами первого устройства совпадения 8, а выходы параметров критериев выхода из синхронизма 1 - 2,..., К - 2 задающего устройства 7 соединены с соответствующими входами второго устройства совпадения 9, информационный вход первого триггера 10 соединен с шиной питания, тактовый вход первого триггера 10 соединен с выходом нулевого состояния ФУ, вход установки в ноль первого триггера соединен с выходом второго состояния ФУ, выход первого триггера ГО соединен с входом инвертора 13 и вторыми входами четвертого и пятого элементов И17 и 18, выход инвертора 13 соединен с первым входом первого элемента И14, выход которого соединен с первым входом третьего элемента ИЛИ21, первый вход второго элемента И15 соединен с выходом установки режима 0 задающего устройства 7, выход второго элемента И15 соединен с вторым входом третьего элемента ИЛИ21, выход второго триггера 11 соединен с первым входом первого элемента ИЛИ19, с первым входом третьего элемента И16 и с третьим входом четвертого элемента И17, первый вход четвертого элемента И17 соединен с выходом установки режима 1 задающего устройства 7, выход четвертого элемента И17 соединен с третьим входом третьего элемента ИЛИ21, выход первого элемента ИЛИ19 соединен с информационным входом второго триггера 11, выход третьего элемента И16 соединен с вторым входом второго элемента ИЛИ20, выход которого соединен с информационным входом третьего триггера 12, выход которого соединен с первым входом второго элемента ИЛИ20 и третьим входом пятого элемента И18, первый вход пятого элемента И18 соединен с выходом установки режима 2 задающего устройства 7, выход пятого элемента И18 соединен с четвертым входом третьего элемента ИЛИ21.

Генераторное оборудование 4 (фиг.2) содержит удалитель такта 22, состоящий из триггеров 23, 24, 25 и 26, инверторов 27 и 28, элементов И29 и 30, счетчика позиций 31, причем вход РС2 генераторного оборудования (ГО) соединен соответственно со входом К триггера 23, вход D которого соединен с Лог. "1", выход триггера 23 соединен со входом D триггера 24 и входом инвертора 27, выход инвертора 27 соединен со входами R триггеров 24, 25 и 26, тактовый вход ГО соединен со входами К триггеров 24, 25, 26 и с первым входом элемента И30, выход триггера 24 соединен со входом D триггера 25 и с первым входом элемента И29, выход триггера 25 соединен со входом D триггера 26, выход которого соединен со входом R триггера 23, вход DC0 (вход нулевого состояния ФУ) ГО соединен со вторым входом элемента И29, выход которого соединен со входом инвертора 28, выход которого соединен со вторым входом элемента И30, выход которого соединен с тактовым входом К счетчика позиций 31, вход RES-C которого соединен со входом КЦ (вход позиции конца цикла) ГО, адресные выходы 1 - N счетчика позиций 31 соединены с соответствующими выходами ГО.

Фазирующее устройство 5 (фиг.3) содержит инверторы 32, 33, 34 и 35, элементы И36, 37, 38 и 39, элементы ИЛИ40 и 41, триггер 42, реверсивный счетчик 43, дешифраторы 44, 45 и 46, причем вход СК (вход отклика опознователя) фазирующего устройства (ФУ) соединен с входом инвертора 32, первым входом элемента И37 и входом +/- реверсивного счетчика 43, а вход РС2 (вход сигнала со второго входа распределителя) ФУ соединен со вторыми входами элементов И36, 37 и входом К триггера 42, выходы инверторов 32 и 33 соединены соответственно с первым и третьим входами элемента И36, выход инвертора 34 соединен с третьим входом элемента И37, выходы элементов И36 и 37 соединены соответственно с первым и вторым входами элемента ИЛИ41, выход которого соединен со входом К реверсивного счетчика 43, выходы разрядов 1-m реверсивного счетчика 43 соединены с соответствующими входами дешифраторов 44, 45 и 46 и являются соответствующими выходами ФУ, выход DC0 (выход нулевого состояния) дешифратора 44 соединен со входом инвертора 33 и является соответствующим выходом ФУ, выход DC2 (выход второго состояния) дешифратора 45 соединен с соответствующим выходом ФУ, выход "m" (выход максимального состояния) дешифратора 46 соединен со входом инвертора 34 и вторым входом элемента ИЛИ40, выход триггера 42 соединен с первыми входами элементов ИЛИ40 и И38, второй вход элемента И38 соединен со входом R (вход установки в ноль) ФУ, выход элемента И38 соединен со входами R реверсивного счетчика 43 и триггера 42, вход D триггера 42 соединен с выходом элемента ИЛИ40, выход триггера 42 соединен со входом инвертора 35 и является выходом наличия синхронизации ФУ, выход инвертора 35 соединен с первым входом элемента И39, второй вход которого соединен со входом S (вход установки в максимальное состояние) ФУ, выход элемента И39 соединен со входом S реверсивного счетчика 43.

Устройство для цикловой синхронизации работает следующим образом.

В разрядах запоминающего устройства 1 в определенных его адресах 1 - N в соответствии со структурой цифровой передачи информации хранятся следующие параметры:

- КЦ - позиции конца цикла;

- ПСК - позиции синхрокомбинации;

- ЗСК - значения синхрокомбинации;

- КСК - позиции конца синхрокомбинации.

В качестве запоминающего устройства 1 может использоваться либо набор постоянно запрограммированных запоминающих устройств (ПЗУ), количество которых определяется количеством различных цифровых передач информации, либо одно перепрограммируемое запоминающее устройство (ППЗУ). При этом при цикловой синхронизации широкого класса цифровых передач информации необходимо осуществить перепрограммирование ППЗУ на соответствующие параметры конкретной передачи. Запоминающее устройство 1 конструктивно соединяется с устройством для цикловой синхронизации с помощью сокеты.

С целью выбора оптимального по времени режима поиска синхронизации в зависимости от помехозащищенности линейного тракта приема с помощью задающего устройства 7 устанавливаются следующие режимы:

- поиск синхронизма при неискаженной помехами синхрокомбинации;

- поиск синхронизма при искажении помехами одного бита синхрокомбинации;

- поиск синхронизма при искажении помехами двух бит синхрокомбинации.

При искажении трех бит синхрокомбинации и более осуществлять ее дешифрацию нецелесообразно, так как в цифровом сигнале, особенно при его искажении помехами, будет дешифрироваться большое количество ложных синхрокомбинаций, что приведет к значительному увеличению времени поиска синхронизма. Также с помощью задающего устройства 7 устанавливаются критерии входа в синхронизм и критерии выхода из синхронизма. При этом под критерием входа в синхронизм понимается разность между количеством дешифрируемых синхрокомбинаций и недешифрируемых. При достижении этой разностью заданного значения устройство для цикловой синхронизации входит в режим синхронизма и его удержания, как будет описано ниже. Под критерием выхода из синхронизма понимается разность между количеством недешифрируемых и дешифрируемых синхрокомбинаций. При достижении этой разностью заданного значения устройсво для цикловой синхронизации выходит из режима синхронизма и вновь переходит в режим его поиска. Критерии входа в синхронизм и выхода из синхронизма также задаются с учетом помехозащищенности линейного тракта.

На начальном этапе поиска синхронизма при отсутствии на выходе СК (выход отклика) опознавателя 3 положительных откликов о дешифрации синхрокомбинации фазирующее устройство 5 (ФУ) устанавливается в нулевое состояние. Сигнал с выхода нулевого состояния последнего поступает на соответствующий вход генераторного оборудования 4 (ГО) и далее на вход его удалителя такта 22, разрешая работу элемента И29. Тактовые импульсы с тактового входа Т устройства для цикловой синхронизации (ЦС) поступают на соответствующий вход ГО и далее на входы К триггеров 24, 25 и 26 удалителя такта 22 и через элемент И30 на тактовый вход счетчика позиций 31. Сигналы с адресных 1 - N выходов счетчика позиций 31 поступают на выходы ГО и далее на соответствующие адресные входы запоминающего устройства 1 (ЗУ), а также на выходы устройства для ЦС. Сигналом, поступающим с выхода КЦ (выход позиции конца цикла) ЗУ через соответствующий вход ГО на вход RES - С счетчика позиций 31, последний по переднему фронту следующего тактового импульса устанавливается в нулевое состояние (синхронный сброс). Сигнал с выхода КСК (выход позиции конца синхрокомбинации) ЗУ поступает на соответствующий вход распределителя 6, осуществляющего распределение по времени этого сигнала. Сигналом с выхода РС2 (второй выход) распределителя 6, поступающим через соответствующий вход ГО на вход К триггера 23 удалителя такта 22, этот триггер устанавливается в единичное состояние, разрешая через инвертор 27 работу триггеров 24, 25 и 26. Сигналом с выхода триггера 24, поступающим на вход элемента И29 и далее через инвертор 28 на второй вход элемента И30, запрещается прохождение через последний одного тактового импульса на тактовый вход счетчика позиций 31. Выходной сигнал с триггера 26 удалителя такта 22 устанавливает его триггер 23 в нулевое состояние. После чего выходным сигналом низкого уровня Лог. "0" этого триггера через инвертор 27 устанавливаются в нулевое состояние остальные триггеры 24, 25 и 26 удалителя такта 22. После этого осуществляется поиск синхрокомбинации на следующих позициях цифрового потока.

При первом же положительном отклике о дешифрации синхрокомбинации, поступившем с выхода отклика опознавателя 3 на соответствующий вход ФУ в сопровождении сигнала с второго выхода распределителя 6, поступающего на соответствующий вход ФУ, последнее переходит из состояния "0" в состояние "1". При этом сигналом отрицательной полярности, поступающим с выхода нулевого состояния ФУ на соответствующий вход ГО, в последнем запрещается удаление тактового импульса. При этом поиск синхронизма начинает осуществляться на одних и тех же позициях цифрового сигнала.

Фазирующее устройство 5 работает следующим образом. Положительный отклик о дешифрации синхрокомбинации с выхода отклика опознавателя 3 через соответствующий вход фазирующего устройства 5 (ФУ) поступает на вход +/- реверсивного счетчика 43 ФУ, разрешая добавление в нем единицы. Этот же положительный отклик поступает на первый вход элемента И37, разрешая его работу. Сигнал с второго выхода распределителя, поступая через соответствующий вход ФУ и далее через открытый элемент И37 и элемент ИЛИ41 на вход К реверсивного счетчика 43, увеличивает его состояние на единицу. Отрицательный отклик о дешифрации синхрокомбинации, поступая на вход +/- реверсивного счетчика 43, разрешает уменьшение его состояния. Также отрицательный отклик, поступая через инвертор 32 на первый вход элемента И36, разрешает его работу и по сигналу с второго выхода распределителя, поступившему на соответствующий вход ФУ, реверсивный счетчик последнего уменьшает свое состояние на единицу.

В режиме поиска синхронизма триггер 42 ФУ находится в нулевом состоянии. При этом его выходной сигнал через инвертор 35 разрешает по первому входу работу элемента И39, тем самым разрешая прохождение через него сигнала с выхода устройства совпадения 8 на вход установки в максимальное состояние реверсивного счетчика 43 ФУ.

При достижении реверсивным счетчиком 43 состояния, определяемого разностью между количеством положительных и отрицательных откликов при дешифрации синхрокомбинации и заданного с помощью параметров критериев входа в синхронизм 1 - 1, ..., L - 1 задающего устройства 7, поступающих на соответствующие входы устройства совпадения 8, на другие входы 1,..., m которого поступают сигналы с соответствующих выходов реверсивного счетчика 43 через соответствующие выходы ФУ, положительным выходным сигналом с выхода устройства совпадения 8, поступающим через вход установки в максимальное состояние ФУ и далее через открытый элемент И39 на вход установки в максимальное состояние реверсивного счетчика 43, последний следующим сигналом с второго выхода распределителя, поступившим на соответствующий вход ФУ, устанавливается в максимальное состояние. При этом положительный сигнал с выхода максимального состояния дешифратора 46 через элемент ИЛИ40 поступает на вход D триггера 42 и отрицательным фронтом сигнала со второго выхода распределителя, поступившим на соответствующий вход ФУ, этот триггер устанавливается в единичное состояние, своим выходным сигналом через инвертор 35 закрывая элемент И39 и открывая элемент И38. После чего ФУ переходит в режим удержания и выхода из синхронизма. Выходной сигнал с триггера 42 поступает на выход Ф (выход наличия синхронизации) ФУ, который также является выходом устройства для ЦС для индикации режима работы устройства.

В режиме удержания и поиска синхронизма при достижении реверсивным счетчиком 43 ФУ состояния, определяемого разностью между количеством отрицательных и положительных откликов на дешифрацию синхрокомбинации и задаваемой с помощью сигналов с выходов параметров критериев выхода из синхронизма 1 - 2, . .., К - 2 задающего устройства 7, поступающих на соответствующие входы устройства совпадения 9, на другие входы разрядов 1 - m которого поступают сигналы с соответствующих выходов ФУ, положительным выходным сигналом с выхода устройства совпадения 9, поступающим на вход установки в ноль ФУ и далее через элемент И38, на вход R реверсивного счетчика 43 и на вход R триггера 42, последние устанавливаются в нулевое состояние, и устройство для ЦС вновь переводится в режим поиска синхронизма, как было описано ранее.

В нулевом состоянии реверсивного счетчика 43 ФУ сигналом с выхода дешифратора 44 через инвертор 33 запрещается работа элемента И36 и, следовательно, запрещается прохождение сигнала на тактовый вход К реверсивного счетчика 43 при отрицательном отклике. Тем самым запрещается переход реверсивного счетчика из нулевого состояния в максимальное состояние.

Если реверсивный счетчик 43 находится в максимальном состоянии, то сигналом с выхода дешифратора 46 через инвертор 34 запрещается работа элемента И37 и, следовательно, запрещается прохождение сигнала на тактовый вход К реверсивного счетчика 43 при положительном отклике. Тем самым запрещается переход реверсивного счетчика 43 из максимального состояния в нулевое состояние.

Дешифратор 2 устройства для ЦС осуществляет поэлементную дешифрацию текущих значений синхрокомбинации цифрового сигнала, позиции и значения которых задаются в ЗУ и поступают с выхода последнего на соответствующие входы дешифратора 2, на информационный и тактовый вход которого поступают соответственно информационные и тактовые импульсы с соответствующих входов устройства для ЦС.

Появление на выходе дешифратора 2 на позициях синхрокомбинации сигнала единичного уровня означает наличие ошибки дешифрирования. При дешифрации истинных неискаженных помехами символов синхрокомбинации на выходе дешифратора 2 будет удерживаться сигнал нулевого уровня.

Опознаватель 3 работает следующим образом. При отсутствии ошибки дешифрации элементов синхрокомбинации на вход ЕС (вход разрешения) опознавателя 3 с выхода третьего элемента ИЛИ21 поступает сигнал нулевого уровня, запрещающий работу опознавателя 3, а на его выходе отклика удерживается сигнал единичного уровня, что соответствует положительному отклику при дешифрации синхрокомбинации. При наличии ошибки дешифрации символов синхрокомбинации на вход разрешения опознавателя 3 поступает сигнал единичного уровня. После чего по сигналу, поступившему с первого выхода распределителя 6 на соответствующий вход опознавателя 3, на его выходе отклика формируется отрицательный отклик на дешифрацию синхрокомбинации. Сигнал положительного или отрицательного отклика на дешифрацию синхрокомбинации с выхода отклика опознавателя 3 и сигнал со второго выхода распределителя 6 поступают на соответствующие входы ФУ. После последовательного поступления сигналов со второго и третьего выходов распределителя 6 на соответствующие входы опознавателя 3 последний устанавливается в единичное состояние, тем самым подготовив следующий цикл работы.

Режим поиска синхронизма при неискаженной помехами синхрокомбинации осуществляется следующим образом. Единичным сигналом с выхода установки режима 0 задающего устройства 7, поступающим на первый вход второго элемента И15, разрешается работа последнего. Четвертый элемент И17 и пятый элемент И18 закрыты нулевыми сигналами, поступающими на их первые входы соответственно с выходов установки режимов 1 и 2 задающего устройства 7. Первый же сигнал ошибки при дешифрации символов синхрокомбинации поступает с выхода дешифратора 2 через открытый второй элемент И15 и третий элемент ИЛИ21 на вход разрешения опознавателя 3, при этом на его выходе отклика формируется отрицательный отклик. При отсутствии сигнала ошибки на выходе дешифратора 2 на выходе отклика опознавателя 3 формируется положительный отклик, и устройство для ЦС осуществляет поиск синхронизма, как было указано ранее.

Режим поиска синхронизма при искажении помехами одного бита синхрокомбинации осуществляется следующим образом. Единичный сигнал с выхода установки режима 1 задающего устройства 7 поступает на первый вход четвертого элемента И17, на второй вход этого элемента поступает единичный сигнал с выхода первого триггера 10, этот же сигнал поступает на вход инвертора 13. Нулевой выходной сигнал с инвертора 13 закрывает по первому входу первый элемент И14. Второй элемент И15 и пятый элемент И18 закрыты сигналами нулевого уровня с выходов установки режимов 0 и 2 задающего устройства 7, поступающими соответственно на первые входы указанных элементов. Первый триггер 10 устанавливается в единичное состояние сигналом, поступающим на его тактовый вход с выхода нулевого состояния ФУ. Первый сигнал ошибки при дешифрации символов синхрокомбинации через первый элемент ИЛИ19 поступает на информационный вход второго триггера 11. Следующим тактовым импульсом, поступающим с тактового входа устройства для ЦС на тактовый вход второго триггера 11, последний устанавливается в единичное состояние и удерживается в этом состоянии единичным сигналом, поступающим с его выхода на информационный вход через первый элемент ИЛИ19. Единичный сигнал с выхода второго триггера 11 поступает также на третий вход четвертого элемента И17, разрешая его работу. Теперь второй импульс ошибки с выхода дешифратора 2 через четвертый элемент И17 и третий элемент ИЛИ21 поступает на вход разрешения опознавателя 3. При достижении ФУ состояния "2" выходным сигналом с выхода второго состояния DC2 первый триггер 10 устанавливается в нулевое состояние, своим выходным нулевым сигналом запрещая работу четвертого элемента И17 и пятого элемента И18 и разрешая через инвертор 13 работу первого элемента И14. Теперь сигнал первой же ошибки дешифрации символов синхрокомбинации поступает с выхода дешифратора 2 через первый элемент И14 и третий элемент ИЛИ21 па вход разрешения опознавателя 3. Далее поиск синхронизма осуществляется так же, как для случая дешифрации неискаженной синхрокомбинации. Второй и третий триггеры 11 и 12 устанавливаются в нулевое состояние сигналом, поступившим на их входы установки в ноль с второго выхода распределителя 6. Таким образом, до достижения ФУ состояния "2" положительный отклик на выходе отклика опознавателя 3 формируется как при отсутствии ошибки дешифрации символов синхрокомбинации, так и при одиночном искажении их помехами.

Режим поиска синхронизма при искажении помехами двух бит синхрокомбинации осуществляется следующим образом. На первый вход пятого элемента И18 подается разрешающий сигнал единичного уровня с выхода установки режима 2 задающего устройства 7. На второй вход этого элемента подается разрешающий сигнал единичного уровня с выхода первого триггера 10. На первые входы второго элемента И15 и четвертого элемента И17 соответственно с выходов установки режимов 0 и 1 задающего устройства 7 поступают запрещающие сигналы нулевого уровня. Первый сигнал ошибки дешифрации символов синхрокомбинации, как было описано ранее, устанавливает второй триггер 11 в единичное состояние. Выходной сигнал второго триггера 11, поступая на первый вход третьего элемента И16, разрешает работу последнего. Второй сигнал ошибки дешифрации символов синхрокомбинации с выхода дешифратора 2 поступает через открытый третий элемент И16 и второй элемент ИЛИ20 на информационный вход третьего триггера 12, после чего последний тактовым импульсом с тактового входа устройства для ЦС устанавливается в единичное состояние, своим выходным сигналом, поступающим на третий вход пятого элемента И18, разрешая работу последнего. После чего при поступлении третьего сигнала ошибки дешифрации символов синхрокомбинации через пятый элемент И18 и третий элемент ИЛИ21 на вход разрешения опознавателя 3, последний на своем выходе отклика формирует отрицательный отклик. Далее устройство работает, как было описано раннее для случая искажения помехами одного символа синхрокомбинации. Таким образом, до достижения ФУ состояния "2" положительный отклик на выходе отклика СК опознавателя 3 формируется как при отсутствии ошибки дешифрации символов синхрокомбинации, так и при искажении одного или двух ее бит.

Для технической реализации устройства для цикловой синхронизации используются постоянные запоминающие устройства (ПЗУ) или перепрограммируемые постоянные запоминающие устройства (ППЗУ), а также программируемые пользователем логические интегральные схемы (ППЛИС).

Предлагаемое изобретение позволяет расширить функциональные возможности устройства для цикловой синхронизации, осуществив синхронизацию различных передач информации с асинхронным объединением цифровых потоков, уменьшить время поиска синхронизма при значительном сокращении оборудования.

Источники информации

1. Патент РФ N 2019046, Н 04 L 7/08.

2. Левин Л. С. , Плоткин М.А. Цифровые системы передачи информации. М: Радио и связь. С. 102-103. Рис.4.4.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2256295C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2286020C2 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2224378C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1998 |

|

RU2136111C1 |

| Устройство для цикловой синхронизации | 2014 |

|

RU2612620C2 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1999 |

|

RU2173027C2 |

Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением. Устройство для цикловой синхронизации содержит дешифратор, опознаватель, генераторное оборудование, фазирующее устройство, а также запоминающее устройство, распределитель, задающее устройство, два устройства совпадения, три триггера, инвертор, четыре элемента И и три элемента ИЛИ. Устройство для цикловой синхронизации позволяет расширить функциональные возможности устройства, осуществив синхронизацию различных передач информации с асинхронным объединением цифровых потоков, уменьшить время поиска синхронизма при значительном сокращении оборудования, в чем и состоит технический результат, достигаемый при его реализации. 3 ил.

Устройство для цикловой синхронизации, содержащее дешифратор, опознаватель, фазирующее устройство (ФУ) и генераторное оборудование (ГО), причем тактовый вход устройства для цикловой синхронизации (ЦС) соединен с соответствующими входами дешифратора, опознавателя и ГО, а информационный вход устройства для ЦС соединен с соответствующим входом дешифратора, выход отклика опознавателя соединен с соответствующим входом ФУ, выход нулевого состояния которого соединен с соответствующим входом ГО, выход наличия синхронизации ФУ является выходом устройства для ЦС, адресные 1 - N выходы ГО являются соответствующими выходами устройства для ЦС, отличающееся тем, что введены запоминающее устройство (ЗУ), распределитель, задающее устройство, первое и второе устройства совпадения, первый, второй и третий триггеры, инвертор, первый, второй, третий, четвертый и пятый элементы И, первый, второй и третий элементы ИЛИ, причем адресные 1-N входы ЗУ соединены с соответствующими выходами ГО, выход позиции конца цикла ЗУ соединен с соответствующим входом ГО и является выходом устройства для ЦС, выходы значения синхрокомбинации и позиции синхрокомбинации ЗУ соединены с соответствующими входами дешифратора, выход позиции конца синхрокомбинации ЗУ соединен с соответствующим входом распределителя, тактовый вход которого соединен с тактовым входом устройства для ЦС, тактовые входы второго и третьего триггеров соединены с тактовым входом устройства для ЦС, выход дешифратора соединен с вторым входом первого элемента ИЛИ, вторыми входами первого, второго и третьего элементов И, а также с четвертыми входами четвертого и пятого элементов И, вход разрешения опознавателя соединен с выходом третьего элемента ИЛИ, первый выход и третий выход распределителя соединены с соответствующими входами опознавателя, второй выход распределителя соединен с соответствующими входами опознавателя, ГО и ФУ, а также со входом установки в ноль второго и третьего триггеров, вход установки в максимальное состояние ФУ соединен с выходом первого устройства совпадения, вход установки в ноль ФУ соединен с выходом второго устройства совпадения, выходы 1-m разрядов ФУ соединены с соответствующими входами первого и второго устройств совпадения, выходы параметров критериев входа в синхронизм 1-1, . . . , L-1 задающего устройства соединены с соответствующими входами первого устройства совпадения а выходы параметров критериев выхода из синхронизма 1-2, . . . , К-2 задающего устройства соединены с соответствующими входами второго устройства совпадения, информационный вход первого триггера соединен с шиной питания, тактовый вход которого соединен с выходом нулевого состояния ФУ, вход установки в ноль первого триггера соединен с выходом второго состояния ФУ, выход первого триггера соединен с входом инвертора и вторыми входами четвертого и пятого элементов И, выход первого инвертора соединен с первым входом первого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, первый вход второго элемента И соединен с выходом установки режима 0 задающего устройства, выход второго элемента И соединен с вторым входом третьего элемента ИЛИ, выход второго триггера соединен с первым входом первого элемента ИЛИ, первым входом третьего элемента И и третьим входом четвертого элемента И, первый вход четвертого элемента И соединен с выходом установки режима 1 задающего устройства, выход четвертого элемента И соединен с третьим входом третьего элемента ИЛИ, выход первого элемента ИЛИ соединен с информационным входом второго триггера, выход третьего элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с информационным входом третьего триггера, выход которого соединен с первым входом второго элемента ИЛИ и третьим входом пятого элемента И, первый вход пятого элемента И соединен с выходом установки режима 2 задающего устройства, выход пятого элемента И соединен с четвертым входом третьего элемента ИЛИ.

| SU 1608811 A1, 23.11.1990 | |||

| US 54128614 A, 27.06.1995 | |||

| DE 3412736 C1, 17.10.1985 | |||

| US 4727558, 23.02.1988 | |||

| ПРОЕКТОР ДЛЯ КОНТРОЛЯ РАЗМЕРОВ ДЕТАЛЕЙ | 0 |

|

SU258621A1 |

Авторы

Даты

2002-02-27—Публикация

2000-03-07—Подача