мемта ЗАПРЕТ подключен к выходу третьего блока элементов ИЛИ, информационные входы первого и второго элементов ЗАПРЕТ соединены соответственно с выходами первого и второго элементов И.

2.Устройство по п. 1, отличающееся тем, что блок опроса содержит генератор тактовых импульсов, кольцевой сдвигающий регистр, группу триггеров, группу элементов ИЛИ, группу элементов И, элемент ЗАПРЕТ, элемент ИЛИ и дифференцирующую цепочку, причем выход генератора тактовых импульсов соединен с информационным входом элемента ЗАПРЕТ, запрещающий вход которого соединен с запрещающим входом блока/ выход элемента ЗАПРЕТ соединен с входом кольцевого сдвигающего регистра, запус кающий вход блока соединен

с первыми входами элементов ИЛИ группы, вторые входы которых соединены с единичными выходами соответствующи триггеров группы, нулевые выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого через дифференцирующую цепочку соединен с первым выходом блока, выходы элементов ИЛИ группы соединены с первыми входами соответствующих элементов И группы, вторые входы которых соединены с соответствующими выходами кольцевого сдвигающего регистре, и блока, выходы элементов И группы соединены со счетными входами триггеров группы

3.Устройство по п. 1, отличающееся тем, что блок управления содержит дешифратор. Триггер, элементы ИЛИ, НЕ, элементы ЗАПРЕТ, две группы элемейтов И, причем первый вход первого элемента ИЛИ соединен с пятым и седьмым входами .блока, второй вход первого

Элемента ИЛИ соединен с шестым входом блока, выход первого элемента ИЛИ соединен с запрещающим входом первого элемента ЗАПРЕТ, первый вход каждого элемента И первой группы, кроме последнего, соединен с выходом соответствующего элемента ЗАПРЕТ, с первым входом соответствующего элемента И второй группй и с соответствующим входом второго элемента ИЛИ, Лервый вход последнего элемента И первой группы соединен с первым выходом дешифратора, с первым входом последнего элемента И второй группы и с соответствующим входом второго элемента ИЛИ, информационные входы первого и второго элементов ЗАПРЕТ соединены с соответствующим выходом дешифратора, запрещающий йход второго элемента ЗАПРЕТ соединен с шестым входом блока, вторые входы элементов И первой и второй групп соединены соответственно с выходами третьего и четвертого элементов ЗАПРЕТ и с восьмым выходом блока, информационный вход третьего элемента ЗАПРЕТ и запрещающий вход четвертого

элемента ЗАПРЕТ соединены с Первым.

входом блока, запрещающий вход

третьего элемента ЗАПРЕТ и информационный вход четвертого элемента ЗАПРЕТ соединены с вторым вхоом блока, с входом дешифратора и через элемент НЕ-с выходом второго элемента ИЛИ, третий и четвертый входы блока Соединены с соответствующими входами триггера, выход которого соединен с первым выходом блока, выходы первых элементов И первой и второй групп соединены соответственно с вторым и третьим выходами блока, выходы остальных элементов И первой и второй групп соединены с соответствующими выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приоритетного обслуживания сообщений | 1976 |

|

SU636610A1 |

| Устройство для моделирования систем передачи и обработки информации | 1987 |

|

SU1481791A1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1418740A1 |

| Устройство для контроля информационной идентичности объектов управления | 1988 |

|

SU1589256A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для сопряжения каналов связи с ЭВМ | 1985 |

|

SU1278873A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1275459A1 |

| Устройство для моделирования вычислительной системы | 1990 |

|

SU1786492A1 |

1. УСТРОЙСТВО ДЛЯ ПРИОРИТЕТНОГО ОБСЛУЖИВАНИЯ СООБЩЕНИЙ, содержащее три входных блока памяти, первые, вторые, третьи приоритетные выходы которых соединены с входами первого, второго и третьего блоков элементов ИЛИ, блок опросаf запрещающий вход которого через четвертый блок элеме:нтов ИЛИ соединен с индикаторными выходами первого, второго и третьего входных блоков памяти, регистр, разрядные выходы которого соединены с входом пятого блока элементов ИЛИ, выход Которого соединен с первым входом блока управления, три выходных блока памяти, первые входы которых соединены с соответствующими выходами дешифратора адреса и единичными входами соответствующих триггеров группы, вторые входа - с информационными выходами первого,. второго и третьего входных блоКов памяти, с входом деишфратора адреса и вторым .входом блока управления, а выходы первого, второго и третьего выходных блоков пг1мяти подключены к первым входам сигнальных эле- ментов И группы, вторые входы Kotoрых соединены с единичными выходами триггеров, группы, а выходаа - с нулевыми входами триггеров группы и через шестой блок элементов ИЛИ с третьим входом блока управления, первый, второй и третий реверсивные -сч.етчики, выходы которых соединены с первыми входами соответственно первого, второго и третьего элементов И, вторые входы кото4)ЫХ соединены с первым выходом блока управления, вычитающие и суммирующие входы рёверсивИых счетчиков подключены соответственно к Второму -седьмому выходам -блока управления, четвертый вход и восьмой выход которого соединены соответственйо с первым выходом блока опроса и с управЛякадим входоМ; регистра, группу элементов ЗАПРЕТ, информационные входы которых соединены с соответствуквдими выходами блока опроса, а выходы - с разрядными входами регистра и с управляющими входами соответствунадих вхоДйых блоков памяти от л и Ч -а ю щ е е с я -тем, что, с цельй повышения надежности работы,уст- . ройство содержит группу элементов И-НЕ, четвертый элемент И, два элемента ИЛИ и два элемента ЗАПРЕТ, выходы которых подключены к первому и второму входам первого элемейта о ИЛИ, третий вход коTopolo соединен N с выходом третьего элемента. И, а выход - с входом четзвертого Ю элемента И, второй вход которого yt подключен к первому выходу блрка управлений, а выход - к эапус.кеиощему , входу блока опросе и первым входам элементов И-НЕ группы вторые входа которых подключены к соответствующим разрядным выходам-|)ёгистра, а выходы - к запрещайщим входам элементов BAnPEjP соответствукяцих групп; выходы . второго и третьего блоков элементов ИЛИ подключены к пятому и шестому входам блока управления и через второй элемент ИЛИ - к запрещающему входу nepBot b элемента ЗАПРЕТ, выход первого блока элементов ИЛИ подклю;Чен к седьмому входу блока управления, запрещающий вход второго зле

1

Изобретение относится к области вычислительной техники и может быть использовано в системах коммутации сообщений.

Известно устройство для приоритетного обслуживания сообщений, содержащее входные накопители, элементы И, ИЛИ, регистр, реверсивные счетчики, блок управления, блок опроса и выходные накопители l.

Недостатком устройства является низкое быстродействие, обусловленно опросом всех входных накопителей без учета возможности их обслуживания в данный момент времени.

Наиболее близким по технической сущности к предложенному является устройство для приоритетного обслуживания сообщений, содержащее

входные накопители, элементы И,

ИЛИ, ЗАПРЕТ, блок опроса, блок управления, регистр, реверсивные счетчики, выходные накопители и триггеры 2.

Недостатком данного устройства является низкая .надежность работы, обусловленная тем, что возможна длительная задержка обслуживания сообщений , первоначально получивших

отказ.

Цель изобретения - повышение надежности работы устройства iПоставленная цель достигается т что устройство для приоритетного обслуживания сообщений, содержащее три входных блока памяти, первые,,. вторые, третьй приоритетные выходы которых соединены с входами пер вого, второго и третьего блоков элементов ИЛИ; блок опроса, запрещающий вход которого через четвертый блок элементов ИЛИ соединен с индикаторными выходами первого, второго и третьего входных блоков памяти, регистр, разрядные выходы которого соенинены с входом пятого блока элементов ИЛИ, выход кото рого соединен с первым входом блока управления, три выходных блока памяти, первые входы которых соединены с соответствующими выходами дешифратора адреса и единичными входс1ми соответствующих Триггеров группы, вторые входы - с информационными выходами первого, второго и третьего входных блоков памяти, с входом дешифратора адреса и вторым входом блока управления, а выходы первого, второго и третьего выходных блоков памяти Подключены к первым входам сигнальных элементов И группы, вторые входы соединены с единичными выходами триггеров группы, а быходы с нулевыми входами триггеров группы и через шестой блок элементов ИЛИ с третьим входом блока уп авления, первый,, второй и третий реверсивные счетчики,, выходы которых соединены с первыми входами соответственно первого, второго и третьего элементов И, вторые входы 1которых соединены с первым выхр,цом блока управления, вычитающие и суммируивдие входа реверсивных счетчиков подключены соответственно к втоjpoMy - седьмому выходам блока управления, четвертый вход и восьмой выход которого соединены соответственно с,,,первым выходом блока опроса и управляющим входом регистра, группу элементов ЗАПРЕТ, информационные входы которых соединены с СО ответствующими выходами блока опроса , а выходы - с разрядными входами регистра и с управляющими вхо- Дс1ми соответствующих входных блоков памяти, содержит группу элементов И-НЕ, четвертый элемент И, два элемента ИЛИ и два элемента ЗАПРЕТ, выходы которых подключены к первому л второму входам.первого элемента ИЛИ, третий вход которого соединен с выходом третьего элемента И, а выход - с первым входом четвертого элемента И, второй вход которого подключен к первому выходу блока управления, а выхГод - к за пускающему входу блока опроса и первым входам элементов И-НЕ груп.пы, вторые входл которых подключены к соответствующим-разрядным выходам регистра, а выходы - к запрещающим входам элементов ЗАПРЕТ соответствующих групп, выходы, второго и третьего блоков элементов ИЛИ подключены к пятому и шестому входам блока управления и через

0 второй элемент ИЛИ-к запрещающему входу первого элемента ЗАПРЕТ, выход первого блока элементов ИЛИ подключен к седьмому входу блока управления, запрещакющй вход второго

5 элемента ЗАПРЕТ - к выходу третьего блока элементов ИЛИ, информационные входы первого и второго элементов ЗАПРЕТ соединены соответственно с выходами первого и второго элементов И.

0

Блок опроса содержит генератор тактовых импульсов, кольцевой сдвигающий регистр, группу триггеров, группу элементов ИЛИ, группу элементбв И, элемент ЗАПРЕТ,

5 ИЛИ и дифференцирующую цепочку, причем выход генератора тактовых импульсов соединен с информационным входом элемента ЗАПРЕТ, запрещающий вход которого соединен с

0 запрещающим входом блока, выход элемента ЗАПРЕТ соединен с входом кольцевого сдвигающего регистра, запускакяций вход блока соединен с первыми входами элементов ИЛИ груп5пы, вторые входы которых соединены с единичными выходами соответствующих триггеров группы, нулевые выходыкоторых соединены с соответствующими входами элемента ИЛ}И,

0 выход которого через дифференцирующую цепочку соединен с первым выходом блока, выходы элементов- ИЛИ группы соединены с первыми входами соответствующих элементов И группы, вторые входы которых соединены

5 с соответствующими выходами кольцевого сдвигающего регистра и блока, выходы элементов И группы соединены со счетными входами триггеров группы.

0

Кроме того, блок управления содержит детиифратор, триггер, элементы ИЛИ, НЕ, элементы ЗАПРЕТ, . две группы элементов И, причем первый вход первого элемента ИЛИ со5единен с пятым и седьмым входами блока, второй вход первого элемента ИЛИ соединен с шестым входом блока, выход первого элемента ИЛИ соединен с запрещающим входом пер0вого элемента ЗАПРЕТ, первый вход каждого элемента И первой группы,кроме последнего, соединен с выходом соответствующего элемента ЗАПРЕТ, с первым входом соответствующего элемента И второй группы

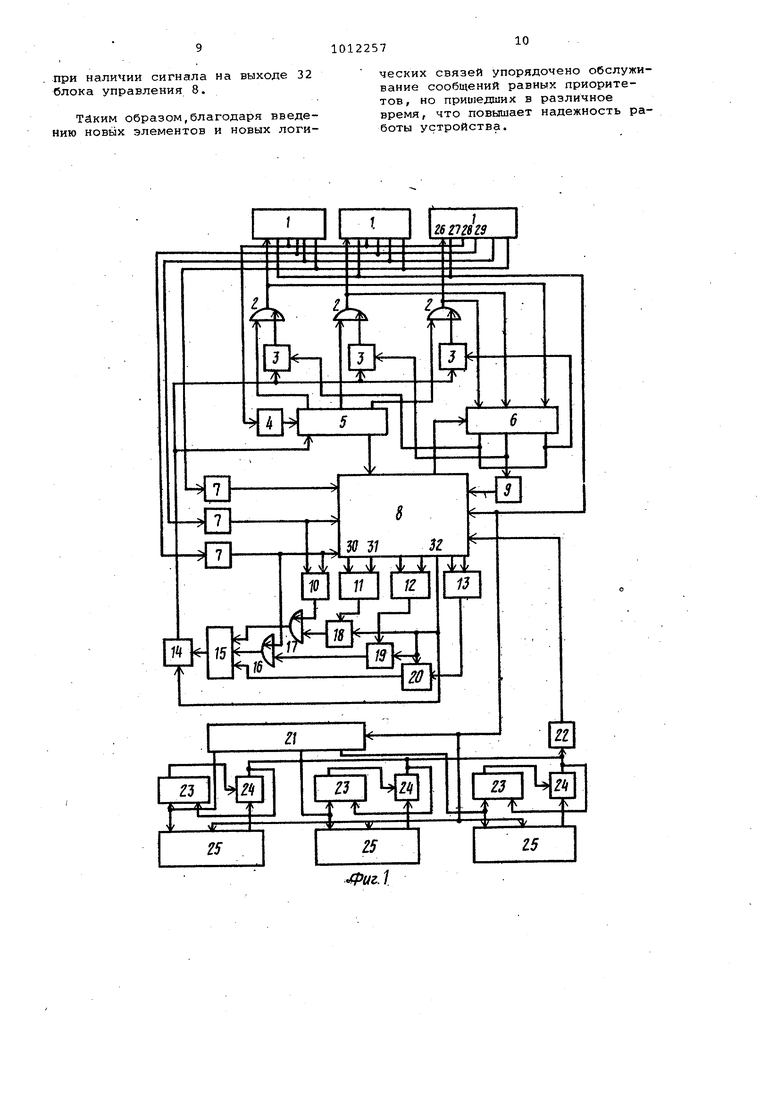

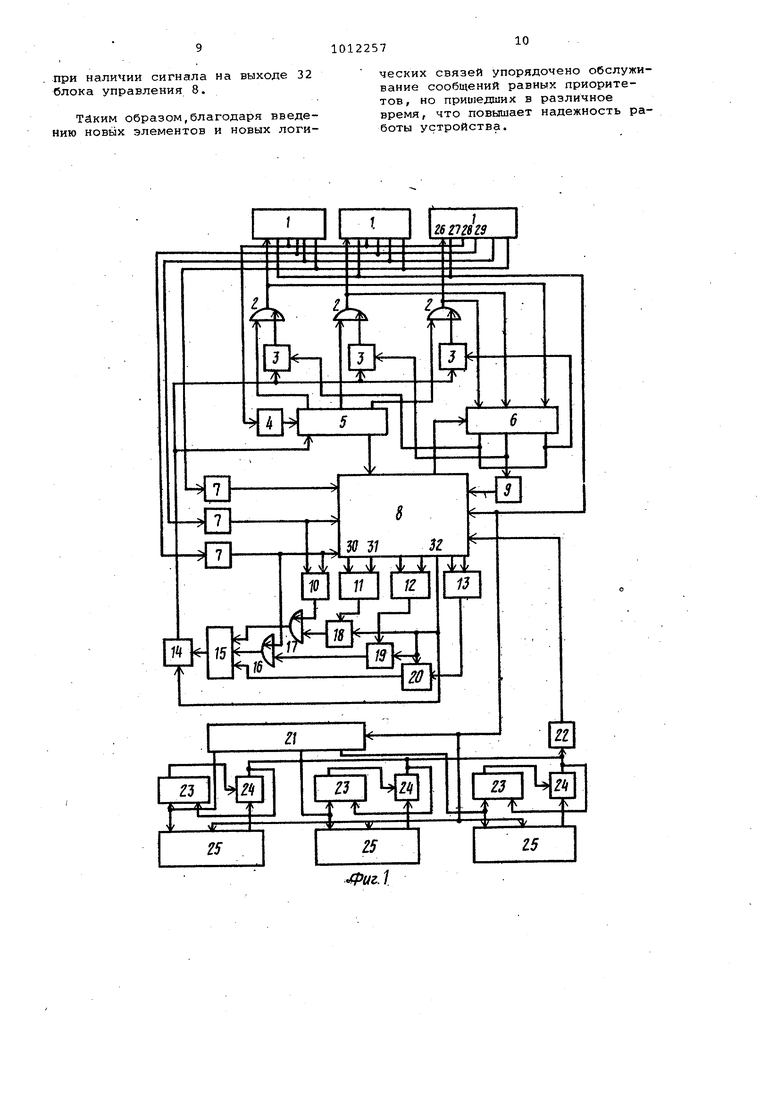

5 и с соответствующим входом второго элемента ИЛИ, первый вход последме1|го элемента И первой группы соединен с первым выходом дешифратора, с первым входом последнего элемента И второй группы и с соответствующим входом второго элемента ИЛИ, информационные входы первого и второго элементов ЗАПРЕТ соединены с соответствующим выходом дешифратора, запрещающий вход второго элемента ЗАПРЕТ соединен с шестым входом блока, вторые входы элементов И первой и второй групп соедине ны соответственно с выходами третье го и четвертого элементов ЗАПРЕТ и с восьмым выходом блока, информац онный вход третьего элемента ЗАПРЕТ и запрещающий вход четвертого элемента ЗАПРЕТ соединены с первым входом блокА, запрещающий вход третьего элемента ЗАПРЕТ и информационный вход четвертого элемента ЗАПРЕТ соединены ; .вторым входом блока, с входом дешифратора и через- элемент НЕ с выходом второго .элемента ИЛИ, третий и четвертый входы блока соединены с соотв-етствующими входами триггера, выход которого соединен с первым выходом блока, выходы первых элементов И первой и второй rpy соединены соответственно с вторым и третьим выходами блока, .выходы ос тальных элементов И первой и второй групп соединены с соответствующими выходами блока. На фиг. 1 приведена структурная схема устройства ; на фиг. 2 - схемы блока опроса и блока управления. Устройство содержит входные блоки памяти 1, группу элементов ЗАПРЕТ 2, группу элементов И-НЕ 3, чет вертый блок элементов ИЛИ 4, блок опроса 5, регистр 6, первый, второй третий блоки элементов ИЛИ 7, блок управления 8, пятый блок элементов ИЛИ 9, второй элемент ИЛИ .10, ревер сивные счетчики 11-13, четвертый эл мент И14, Первый элемент ИЛИ 15, второй элемент ЗАПРЕТ 16, первый эл мент ЗАПРЕТ 17, первый - третий эле менты И 18-20, дешифратор 21 адреса шестой блок элементов ИЛИ 22, группу триггеров 23, группу сигнальных элементов И 24, выходные блоки памяти 25, управляющие входы 26, соответственно информационные, индика торные и приоритетные выходы 27 28 и 29 входных блоков памяти, вычитающие 30 и суммирующие 31 входа реверсивных сметчиков, выход 32. блока управления 8, . Блок опроса 5 предназначен для последовательного опроса вхъдных блоков памяти 1 и содержит генератор тактовых импульсов 33, элемент ЗАПРЕТ 34, кольцевой сдвигающий регистр 35, группу элементов ИЛИ 36, группуэлементов И 37, группу триггеров 38, элемент ИЛИ 39 и дифференцирующую цепочку 40, первый вход блока опроса 5 подключен к выходу элемента ИЛИ 4, второй вход - к йыходу элемента И 14, каждый разрядный выход кольцевого сдвигающего регистра 35 соединен с соответствующим элементом ЗАПРЕТ 2 ичерез элемент И 37 данного разряда со счетным . входом триггера 38, а выход- блока 5 подключен к блоку управления 8. Блок управления. 8 предназначен Для управления работой устройства и содержит дешифратор 41 элемент ИЛИ 42/ эЛемеНтЬ ЗАПРЕТ 43 И 44, группу элементов И45-47, группу элементов И 48-50, элемент ИЛИ 51, элемент ИЕ 52, элементы ЗАПРЕТ 53 и 54, триггер 55. Устройство работает следующим образом. . Обычно сообщение разбивается На несколько блоков, причем в первом ( адресном )блоке указываются приоритет сообщения, адрес получателя и другие служебные признаки. После накопления адресного блока на выходах 29 входных блоков памяти 1 появляется один из сигналов, указывающий приоритет сообщения. Эти сигналы через блоки 7 (в зависимости от приоритета) поступают в блок управления 8; Из блока 5 опроса поочередно выдаютгся сигналы Выэов, опрашивающие входные блоки памяти 1. Пусть в одном из входных блоков памяти 1 Накоплен/адресный блок сообщения с высшим приоритетом. При поступлении .сигнала Вызов на информационном выходе 28 данного Накопителя появляется сигнал, остаНавЛйвающий через блок 4 блок опроса 5. Начинается выборка адреса из выбрйнного входного блока памяти 1. В процессе выборки анализируется приоритет обслуживаемого сообщения , которь1й сравнивается в блоке 8 с приоритетами других сообщений, имеющихся во входных блоках памяти 1. Если на входных блоках памяти 1 имеются сообщения с более высокими приоритетами, чем обслуживаемое, то его обслуживание прекращается Если сообщения с более высокими приоритетами отсутствуют,То информация из выбранного входного блока памяти 1 поступает на дешифратор адреса 21t где в соответствии с адресом сообщения формируется сигнал вызова выходного блока памяти 25. . Ё ответ на этот сигнал из выходного блока памяти 25 выдается либо сигнал Готов принять информацию, либо сигнал Занято. В последнем случае сигналом Занято триггер 23 данного накопителя устанавливается в .единичное coctoHHHe-, а обслуживаемому сообщению дается отказ. Одновременно с опросом входного - блока паМйти 1 происходит анализ . состояния соответствующего разряда регистра б значение которого через блок 9 поступает в блок 8 управления. В случае отказа обслужйваекюму сообщению выходным блоком памяти 2§ и нулейого состояния соответствующего разряда, регистра б блок управйения 8 выдает на суммирующий ,вход 3.1 pesepeHBHoix) счет«1йка 1-1, 12, 13 .(в зависимости от п4)иоритета обслуживаемого сообщенияJ 9игнал, добавляюСЕШй к его значению единицу, а в соответствующий разРид регистра б заносится . . При последующих pTifjisax данному : входному Накрт1Ителк) значение реверсивных счетчиков йзк нягься не буде Если передача информации разреше на, то блок управления 8 выдает сйг мал на вход 30 одного из реверсивны счетчиков li/ 12 и 1з и вычитает из его значений единицу при условии что соЬТйетствующий разряд регист а б находится в единице при этом дан ный разряд регистра б сбрасывается :В нуль. . После проДелаЕНйых операций водится опрос и обслуживание осталь ных блоков памяти 1« ., После завершения первого Цикла опроса содержикюе разряДоб регистра б nocTynaet на входы соответствуквдих элементрй И-НЕ 34 Если значение разряда равно единице, to сигналом с Выхода элемента Й-НЕ 3 закрывается соответстйующий элемент ЗАЙРЕТ 2, и при последу1ощих циклах опрос данного входного блока памйтй 1 блоком опроса .S не Производится. ЕСЛИ значение ЬавнО нулю, то опрос йходНого бЛока памяти 1 идет обычным образом,При передаче информации из вхоЛ ных блоков памяти 1 в выходные блоки Намйти 25 ведется анализ на Наличие сигнала Конец сообщения, который поступает на вход элемента И 24 данного выходного накопителя. Иа второй вход элемента И 24 поступаёт сигнал с единичного выхода триггера 23. Если в процессе обмена информацией между входным и выходным блоком памяти к последнему обреицался еще какой-то входной блок памяти 1 и получил отказ, то триггер 23.находится в единичном состоянии -поэтому сигнал Конец сообщения через открытый элемент И 24 данного входного блока памяти 25 и блок 22 поступает в блок управ ления 8, одновременно возвращая со, оТветствующий триггер 23 в нулевое состояние. Поступление сигнала Конец сообщения в блок управления 8 означает, что с этого момента необходимо учитывать приоритеты сообщений, получивших отказ и хранящихся в реверсивных счётчиках 11, 12 и 13. Кроме того, если имеются сообщения уже получившие отказ и сообщения, еще не обслуживавшиеся, но равных приоритетов, то в первую очередь должны обслуживаться сообщеНия, получившие отказ, так как они пришли раньше. Для этого блок управления 8 выдает сигнал по выходу 32, открывающий элементы И ISi 19 и 20. . Сигналы с выходов реверсивных счётчиков 11 и 12 (третьего и. второго приоритета ) поступают на информационные йходы элементов ЗАПРЕТ 16 и J7, .на запрещающие входы которых поступают сигналы с выходов блоков 7 второго и первого приори тетов. Если из всех накопленных сообщений информация о выса:аеМ приоритете находится в одном из реверсивных счетчиков 11,12 и 13,, то на выходе элемента ИЛИ 15 появляется сигнал, через элемент И 14поступа1б11и1й в блок опроса 5 и на вторые ; входов И-НЕ 3. Этим сигналом в блоке опроса 3 запоминается номер входного блока памяти 1, во время обслуживания которых был получен сигнал Конец сообщений. Совпадение сигналов на входах элементов И-НЕ 3 снимает сигнал запрета с соответствующего элемента ЗАПРЕТ 2, разрешая опрос только Тех входных блоков памяти 1, которые ранее получили отказ и не, опрашивались, и закрывает элементы ЗАПРЕТ 2 остальных входных накопителей. TltkHM образом, при дгшьнейшем опросе опрашмвгиотся только те входные блоки памяти 1, которые содержат сообщение высшего или равного с остальными приоритета, но уже получившие,отказ, что упоряоживает очередность обслуживания сообщеййй; При повторном опросе запомненного блоком 5 входного . блока памяти 1 блок S выДает сигнал Конец цикла, по которому сигнал с выхода 32 блока управления 8 снимается, возвращая устройство в ис-/ ходНое состояние, , Если же шсшее по приоритету сообщение еще не обслуживалось, то сигналами с-блоков 7 (второго и первого приоритетов ) элементы ЗАПРЕТ 16 и 17 закрываются, поэтому обслуживание входных накопителей производится обычным образом даже

при наличии сигнала на выходе 32 блока управления 8.

Тйким образом,благодаря введению новых элементов и новых логических связей упорядочено обслуживание сообщений равных приоритетов , но пришедших в различное время, что повышает надежность работы устройства.

Фиг. /

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для приоритетного обслуживания сообщений | 1972 |

|

SU446061A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ обработки легко рассыпающихся и плохо высыхающих осочно-тростниковых торфов при помощи разбавленных щелочей | 1922 |

|

SU541A1 |

Авторы

Даты

1983-04-15—Публикация

1981-07-02—Подача