Изобретение относится к автоматике и вычислительной технике и может быть использовано в технике цифровой обработки сигналов, например, для сжатия данных, фильтрации сигналов, выделения признаков для распознавания образов и т.д.

Известно устройство для ортогонального преобразования по Уолшу-Адамару, содержащее два блока регистров сдвига, два регистра, коммутатор, сумматор-вычитатель, блок синхронизации и соответствующие связи между ними.

Однако данное устройство обладает значительной сложностью и невысоким быстродействием.

Известно также устройство ортогонального преобразования цифрового сигнала по Уолшу-Адамару, содержащее сумматоры-вычитатели, регистры, блоки элементов ИЛИ, блоки элементов И, блок формирования временных интервалов.

Однако данное устройство также имеет значительную сложность и невысокое быстродействие.

Наиболее близким по технической сущности к изобретению является блок преобразования, осуществляющий сжатое преобразование Уолша-Адамара, содержащий арифметические устройства двух уровней.

Недостатком известного устройства являются его узкие функциональные возможности, так как он выполняет только сжатое преобразование Уолша-Адамара.

Цель изобретения расширение функциональных возможностей за счет выполнения полного преобразования Уолша-Адамара.

Цель достигается тем, что в устройстве для обработки цифрового сигнала, содержащем арифметические устройства и соответствующие связи между ними, вход и выход содержит (N/2)log2N арифметических устройств, объединенных в 2log2N вычислительных ячеек по k(k N/4) арифметических устройств.

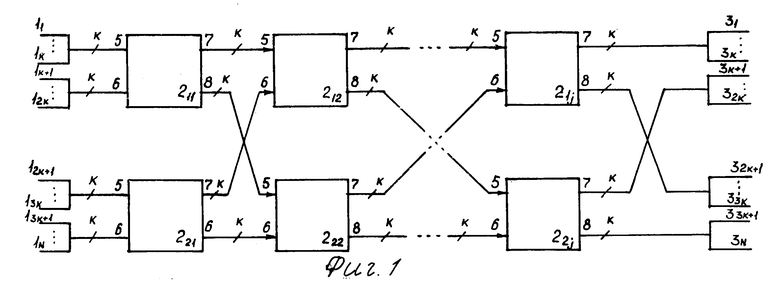

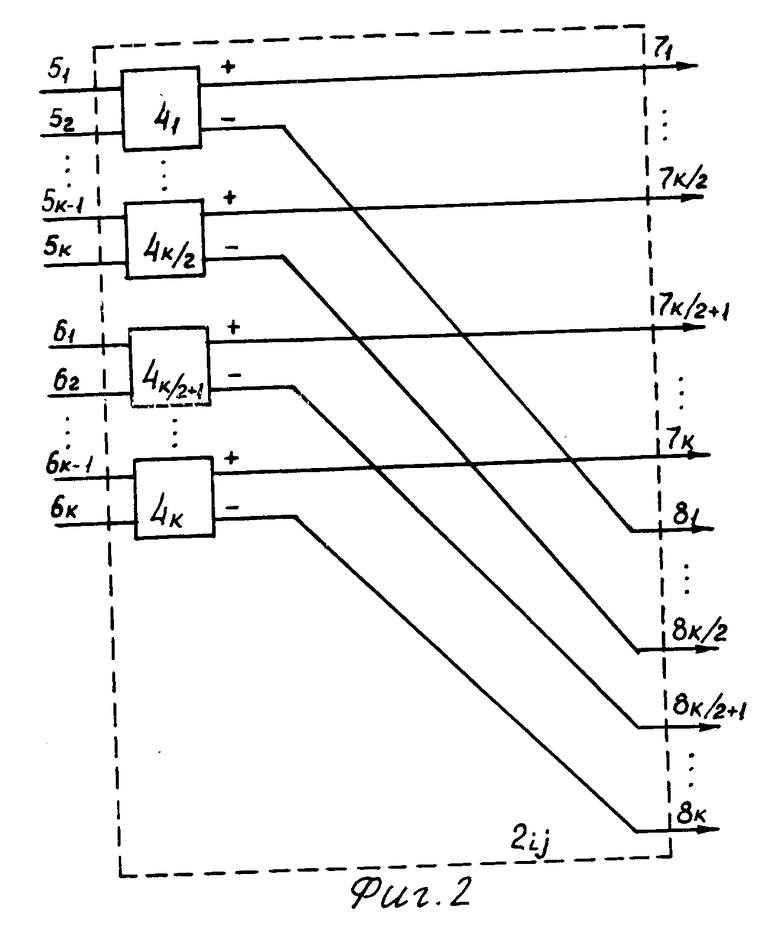

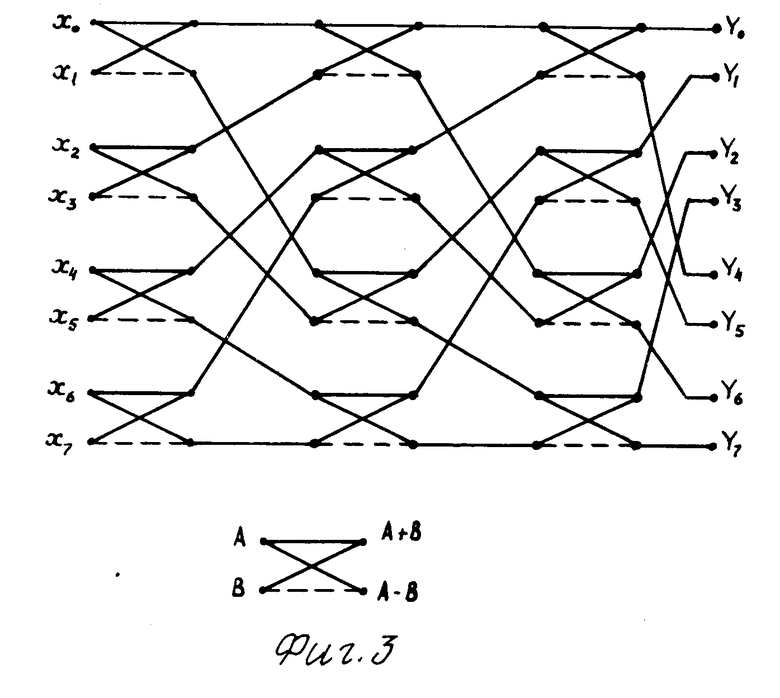

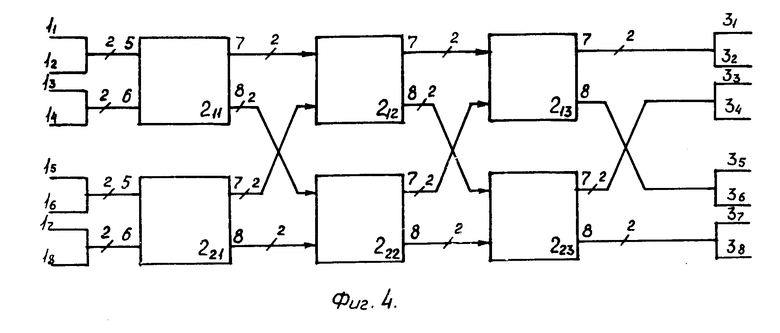

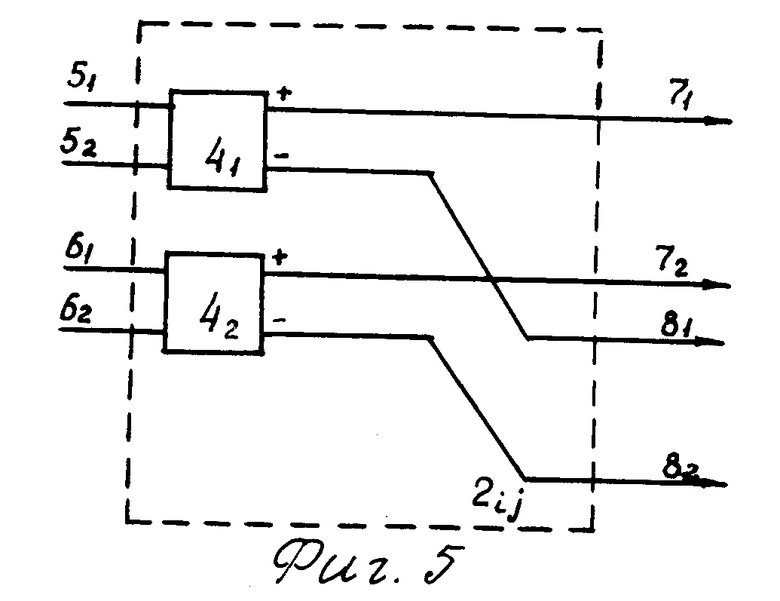

На фиг. 1 приведена функциональная схема устройства для обработки цифрового сигнала; на фиг. 2 функциональная схема вычислительной ячейки; на фиг. 3 показан граф вычислительной процедуры преобразования по Уолшу-Адамару для N 8; на фиг. 4 представлена функциональная схема устройства для N 8; на фиг. 5 функциональная схема вычислительной ячейки для N 8.

Устройство для обработки цифрового сигнала содержит вход 1, матрицу i x j вычислительных ячеек 2(i log2N, j 2), связи между ними, выход 3. Вычислительная ячейка 2 содержит k арифметических устройств 4, входы 5 и 6, выходы 7 и 8. Арифметическое устройство имеет два входа операндов и два выхода суммы и разности этих операндов. Выходы суммы арифметических устройств соединены с выходом 7 вычислительной ячейки. Выходы разности арифметических устройств соединены с выходом 8 вычислительной ячейки. Выходы 7 (1, j)-х вычислительных ячеек соединены с входами 5 (1, j + 1)-х вычислительных ячеек матрицы. Выходы 7 (2, j)-х вычислительных ячеек соединены с входами 6 (1, j + 1)-х вычислительных ячеек матрицы. Выходы 8 (1, j)-х вычислительных ячеек соединены с входами 5 (2, j + 1)-х вычислительных ячеек матрицы. Выходы 8 (2, j)-х вычислительных ячеек соединены с входами 6 (2, j + 1)-х вычислительных ячеек. Выходы 7 и 8 вычислительных ячеек последнего столбца соединены с выходом 3 устройства так, что с выходов 7 этих ячеек снимаются четные отсчеты результата преобразования, а с выходов 8 снимаются нечетные отсчеты результата преобразования.

Принцип действия устройства основан на выполнении над вектором-столбцом исходных данных размерностью N следующего преобразования: =H

=H ,(1) где

,(1) где  вектор-столбец коэффициентов Уолша-Адамара;

вектор-столбец коэффициентов Уолша-Адамара;

HN матрица Уолша-Адамара размерностью N x N;

N 2n, где n положительное целое число.

Преобразования Уолша-Адамара производятся итерационно за n итераций по формуле =

= SNH

SNH SH

SH , (2) где HN(1) HN(2) HN(n) матрица размерностью N x N;

, (2) где HN(1) HN(2) HN(n) матрица размерностью N x N;

SN мономиальная матрица перестановки;

H

H2 матрица Адамара порядка 2,

H2

Вычислительная процедура (2) реализуется за n(n log2N) итераций. Каждая i-я (i  ) итерация сводится к сложению или вычитанию соответствующих элементов вектора

) итерация сводится к сложению или вычитанию соответствующих элементов вектора  и переупорядочению элементов результирующего вектора Хi. Суть перестановки заключается в разделении элементов вектора

и переупорядочению элементов результирующего вектора Хi. Суть перестановки заключается в разделении элементов вектора  на четные и нечетные. При этом массив нечетных элементов вектора

на четные и нечетные. При этом массив нечетных элементов вектора  располагается в первой половине результирующего массива.

располагается в первой половине результирующего массива.

Устройство работает следующим образом.

В статическом режиме исходные данные для преобразования на вход устройства не поступают. В динамическом режиме на вход 1 устройства (фиг. 1) подаются исходные данные для преобразования значения элементов вектора-столбца  x1(i=0,

x1(i=0, )в цифровом виде и поступают на входы 5 и 6 вычислительных ячеек первого столбца, причем первые N/2 отсчетов подаются на вычислительную ячейку 211, а вторые N/2 отсчетов на вычислительную ячейку 221. На входы 5 и 6 этих ячеек подается соответственно по k(k N/4) отсчетов. Вычислительная ячейка (фиг. 2), содержащая k арифметических устройств, формирует на их выходах "+" и "-" одновременно сумму и разность двух элементов вектора

)в цифровом виде и поступают на входы 5 и 6 вычислительных ячеек первого столбца, причем первые N/2 отсчетов подаются на вычислительную ячейку 211, а вторые N/2 отсчетов на вычислительную ячейку 221. На входы 5 и 6 этих ячеек подается соответственно по k(k N/4) отсчетов. Вычислительная ячейка (фиг. 2), содержащая k арифметических устройств, формирует на их выходах "+" и "-" одновременно сумму и разность двух элементов вектора  . Суммы подаются на выход 7 вычислительной ячейки, а разности на выход 8 вычислительной ячейки. Поскольку отсчеты поданы на вход 1 (11 1N) в естественном порядке, то за счет связей между вычислительными ячейками столбцов матрицы должна быть произведена перестановка элементов результирующего вектора путем разделения на четные и нечетные. Поэтому сумма с выхода 7 ячейки 221 подается на вход 5 ячейки 212, сумма с выхода 7 ячейки 221 подается на вход 6 ячейки 212, разность с выхода 8 ячейки 211 подается на вход 5 ячейки 222, разность с выхода 8 ячейки 221подается на вход 6 ячейки 222, разность с выхода 8 ячейки 221 подается на вход 6 ячейки 212. Тем самым осуществляется первая итерация. Аналогично осуществляются последующие итерации. Суммы с выходов 7 ячеек 2ij подаются на вход 5 ячеек 21,j+1. Суммы с выходов 7 ячеек 22jподаются на вход 5 ячеек 2j+1. Разности с выходов 8 ячеек 21j подаются на входы 5 ячеек 22,j+1. Разности с выходов 8 ячеек 22,j подаются на входы 6 ячеек 22,j+1. Через n итераций получают на выходе 3 устройства результат преобразования цифрового сигнала по Уолшу-Адамару в виде элементов вектора-столбца

. Суммы подаются на выход 7 вычислительной ячейки, а разности на выход 8 вычислительной ячейки. Поскольку отсчеты поданы на вход 1 (11 1N) в естественном порядке, то за счет связей между вычислительными ячейками столбцов матрицы должна быть произведена перестановка элементов результирующего вектора путем разделения на четные и нечетные. Поэтому сумма с выхода 7 ячейки 221 подается на вход 5 ячейки 212, сумма с выхода 7 ячейки 221 подается на вход 6 ячейки 212, разность с выхода 8 ячейки 211 подается на вход 5 ячейки 222, разность с выхода 8 ячейки 221подается на вход 6 ячейки 222, разность с выхода 8 ячейки 221 подается на вход 6 ячейки 212. Тем самым осуществляется первая итерация. Аналогично осуществляются последующие итерации. Суммы с выходов 7 ячеек 2ij подаются на вход 5 ячеек 21,j+1. Суммы с выходов 7 ячеек 22jподаются на вход 5 ячеек 2j+1. Разности с выходов 8 ячеек 21j подаются на входы 5 ячеек 22,j+1. Разности с выходов 8 ячеек 22,j подаются на входы 6 ячеек 22,j+1. Через n итераций получают на выходе 3 устройства результат преобразования цифрового сигнала по Уолшу-Адамару в виде элементов вектора-столбца  . Причем на выход 3 устройства результат подается следующим образом: на выходы 31 3k подаются суммы с выхода 7 ячейки 21,j, на выходы 3k+1 32k суммы с выхода 7 ячейки 22,j, на выходы 32k+1 3k разности с выхода 8 ячейки 2i,j, на выходы 32k+1 3N разности с выхода 8 ячейки 22,j. Таким образом, на выходе 3 устройства сформированы элементы вектора-столбца

. Причем на выход 3 устройства результат подается следующим образом: на выходы 31 3k подаются суммы с выхода 7 ячейки 21,j, на выходы 3k+1 32k суммы с выхода 7 ячейки 22,j, на выходы 32k+1 3k разности с выхода 8 ячейки 2i,j, на выходы 32k+1 3N разности с выхода 8 ячейки 22,j. Таким образом, на выходе 3 устройства сформированы элементы вектора-столбца  , расположенные в естественном порядке.

, расположенные в естественном порядке.

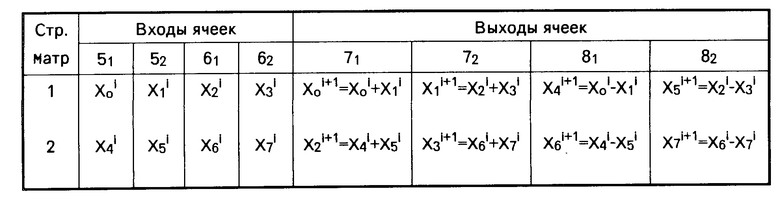

Рассмотрим работу устройства на примере для N 8. Функциональная схема устройства для N 8 приведена на фиг. 4. Устройство содержит шесть вычислительных ячеек 2i,j (2log28 6). Схема вычислительной ячейки 2i,j (i  j

j  ) приведена на фиг. 5. Она содержит два арифметических устройства 41 и 42, входы 51, 52, 61, 62, выходы 71, 72, 81, 82. Пусть на вход 1 устройства подаются элементы вектора-столбца

) приведена на фиг. 5. Она содержит два арифметических устройства 41 и 42, входы 51, 52, 61, 62, выходы 71, 72, 81, 82. Пусть на вход 1 устройства подаются элементы вектора-столбца  х0, х1, х2, х3, х4, х5, х6, х7. Выполняемые в каждой итерации арифметические операции и функционирование устройства описываются таблицей.

х0, х1, х2, х3, х4, х5, х6, х7. Выполняемые в каждой итерации арифметические операции и функционирование устройства описываются таблицей.

Таким образом, рассмотренное устройство обладает более широкими возможностями, так как позволяет выполнять над цифровым сигналом полное преобразование Уолша-Адамара. Кроме того, оно обладает однородными связями между вычислительными ячейками, что определяет его высокую технологичность при реализации на основе СБИС. По сравнению с аналогами предлагаемое устройство обладает более высоким быстродействием, так как все элементы вектора-столбца исходных данных обрабатываются параллельно, а не последовательно, что увеличивает быстродействие, а также обладает меньшей конструктивной сложностью за счет однородности структуры устройства и вследствие этого более высокой технологичностью при реализации на СБИС и более высокой надежностью. Применение данного устройства в рассматриваемой области позволяет достичь следующих общественно-полезных преимуществ: повысить технологичность реализуемых устройств данного класса при реализации их на основе интегральной технологии и, следовательно, снизить их стоимость; расширить области применения, вследствие чего возможно снижение затрат на разработку аналогичных устройств в интересах других областей народного хозяйства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ МАТРИЦ | 1991 |

|

RU2037200C1 |

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| ОДНОРОДНАЯ КОММУТАЦИОННАЯ СТРУКТУРА | 1991 |

|

RU2033635C1 |

| Мультиконвейерный делитель | 1988 |

|

SU1587499A1 |

| Устройство для ортогонального преобразования по Уолшу-Адамару | 1988 |

|

SU1571610A1 |

| Устройство для выполнения быстрого преобразования Уолша | 1983 |

|

SU1141420A1 |

| Устройство для вычисления коэффициентов разложения функции | 1991 |

|

SU1824641A1 |

| Многофункциональный логический модуль | 1987 |

|

SU1474636A1 |

| Ячейка однородной среды | 1986 |

|

SU1397899A1 |

| АНАЛИЗАТОР ФУНКЦИЙ УОЛША | 2000 |

|

RU2203504C2 |

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для обработки цифровых сигналов путем преобразования по Уолшу-Адамару. Цель изобретения - расширение функциональных возможностей устройства. Устройство содержит матрицу вычислительных ячеек, вход, выход и связи между вычислительными ячейками. Вычислительная ячейка содержит арифметические устройства и имеет два входа и два выхода. 1 з.п. ф-лы, 5 ил., 1 табл.

| Устройство ортогонального преобразования | 1988 |

|

SU1594563A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ приготовления консистентных мазей | 1919 |

|

SU1990A1 |

Авторы

Даты

1995-04-20—Публикация

1991-07-09—Подача