3

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для деления m пар п-разрядных чисел в мультиконвейер- ном режиме.

Цель изобретения - повьшение бысродействия .

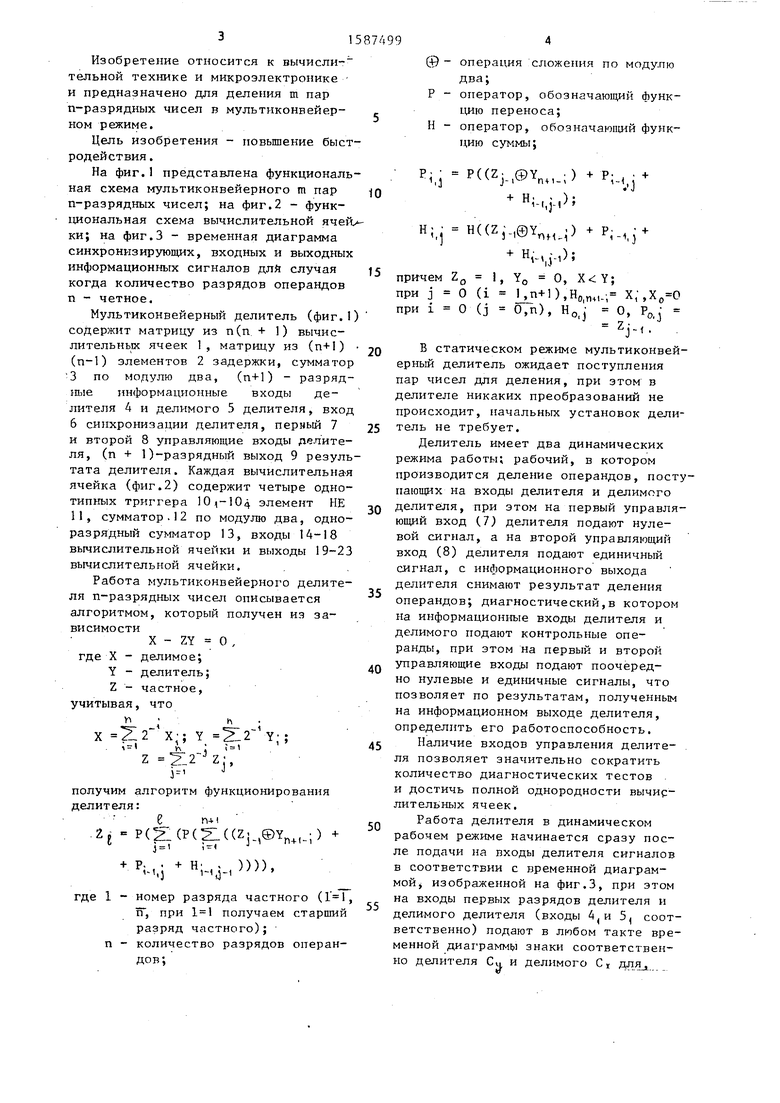

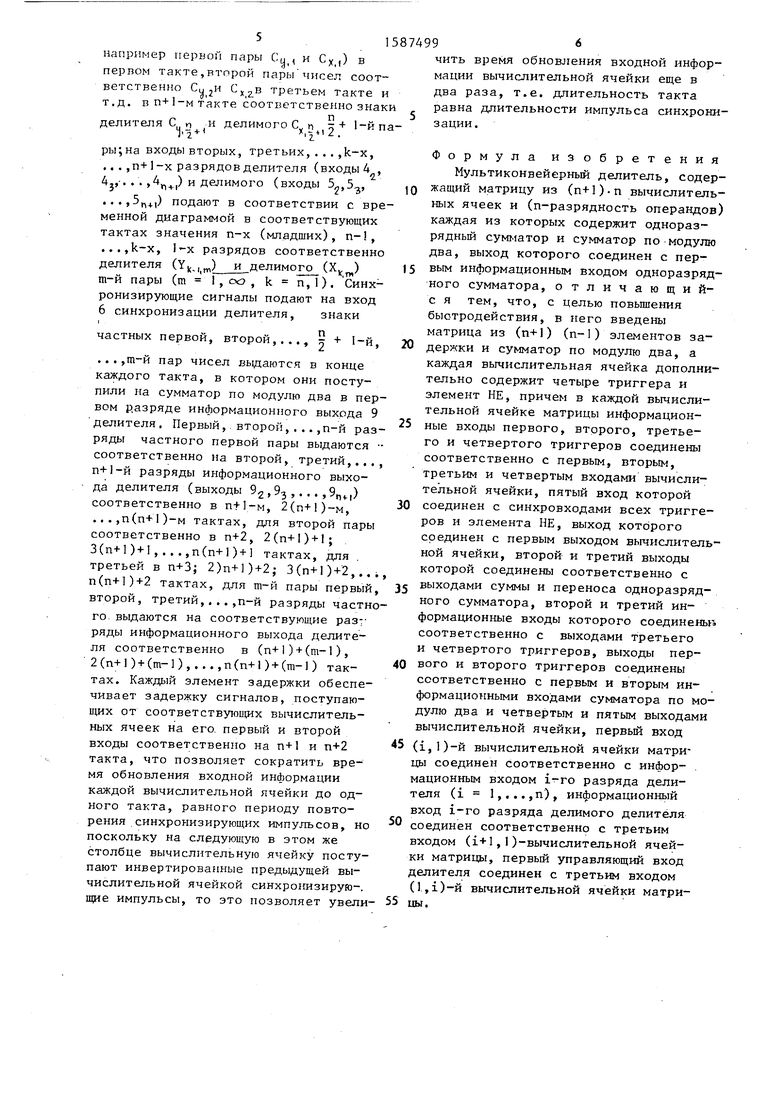

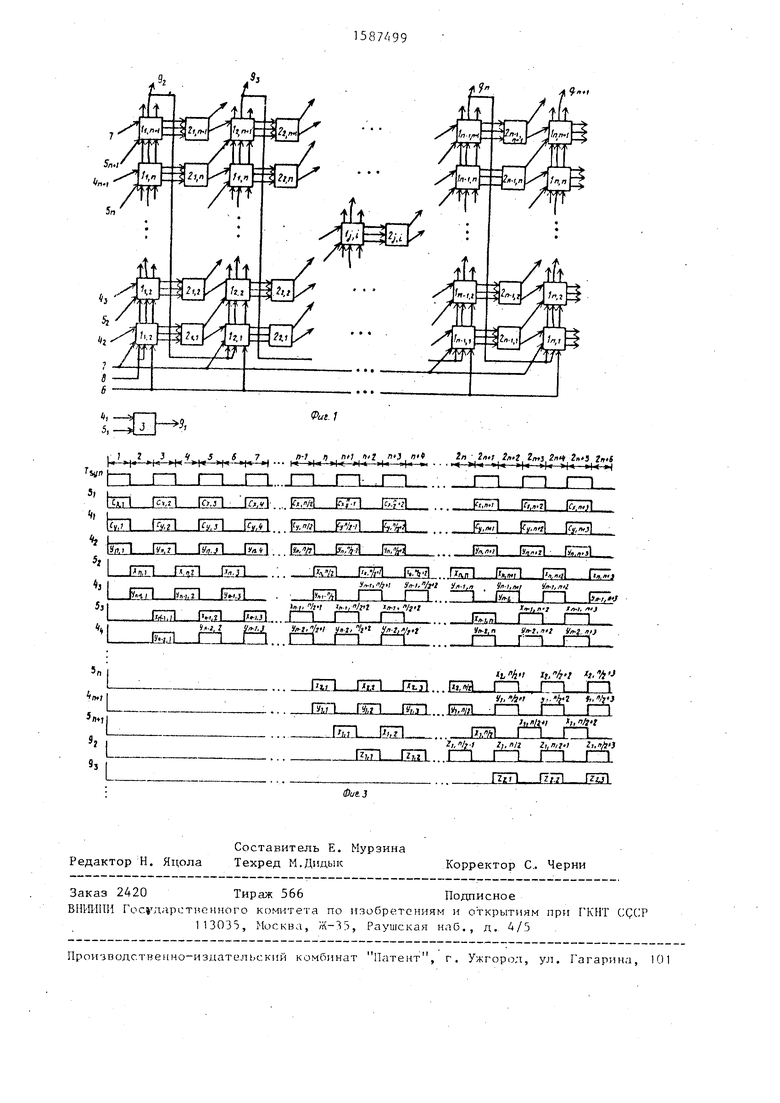

На фиг.1 представлена функционалная схема мультиконвейерного m пар п-разрядных чисел; на фиг.2 - функ- хщональная схема вычислительной яче ки; на фиг.З - временная диаграмма синхронизирующих, входных и выходны информационных сигналов дли случая когда количество разрядов операндов п - четное.

Мультиконвейерный делитель (фиг. содержит матрицу из п(п + 1) вычислительных ячеек 1, матрицу из (п+1) (п-1) элементов 2 задержки, суммато 3 по модулю два, (п+1) - разрядные информационные входы делителя 4 и делимого 5 делителя, вхо 6 синхронизации делителя, первый 7 и второй 8 управляющие входы делителя, (п + 1)-разрядный выход 9 резултата делителя. Каждая вычислительна ячейка (фиг.2) содержит четыре однотипных триггера 10,-104 элемент НЕ 11, сумматор. 12 по модулю два, одноразрядный сумматор 13, входы 14-18 вычислительной ячейки и выходы 19-2 вычислительной ячейки.

Работа мультиконвейерного делителя п-разрядных чисел описывается алгоритмом, который получен из зависимости

О

X - ZY где X - делимое; Y - делитель; Z - частное, учитывая, что

У1

X 2 х ; Y п ; Z

получим алгоритм функционирования делителя:

L Р((Р(

j

J

Е

((2J4©Yn.,-i)

-P;..i -н;,.,)))),

1 - номер разряда частного (, гГ, при получаем старший разряд частного); п - количество разрядов операндов;

операция сложения по модулю два;

оператор, обозначающий функ- 1Ц1ю переноса;

оператор, обозначающий функцию суммы;

P((Zj.,@Y + Н

П+ 1-1

)

1-l,J-((()

-..J

-0

H,,

причем Zg 0 0

при при

,.);

о,

(i ип-и),Но,„„.; х;,

(j 0,n), HO. о, P

Zj.,

О

0

5

0

5

0

5

0

5

В статическом режиме мультиконвей- ерный делитель ожидает поступления пар чисел для деления, при этом в делителе никаких преобразований не происходит, начальных установок делитель не требует.

Делитель имеет два динамических режима работы; рабочий, в котором производится деление операндов, поступающих на входы делителя и делимого делителя, при этом на первый управляющий вход (7) делителя подают нулевой сигнал, а на второй управляющий вход (8) делителя подают единичный сигнал, с информационного выхода делителя снимают результат деления операндов; диагностический,в котором на информационные входы делителя и делимого подают контрольные операнды, при этом на первый и второй управляющие входы подают поочередно нулевые и единичные сигналы, что позволяет по результатам, полученным на информационном выходе делителя, определить его работоспособность.

Наличие входов управления делителя позволяет значительно сократить количество диагностических тестов и достичь полной однородности вычир- лительных ячеек.

Работа делителя в динамическом рабочем режиме начинается сразу после подачи на входы делителя сигналов в соответствии с временной диаграммой j изображенной на фиг.З, при этом на входы первых разрядов делителя и делимого делителя (входы 4,и 5, соответственно) подают в любом такте временной диаграммы знаки соответственно делителя Си и делимого С, для

например первой пары CN , и Су,) в первом такте,второй пары чисел соответственно С.в третьем такте и т.д. в п+1-м такте соответственно знак

S+ 1-й пделителя С о ;И делимого С п - .г. ры;на входы вторых, третьих, . . . ,k-x, ... ,п+1-х разрядов делителя (входы 4 , |) и делимого (входы 5,5-,

п-И подают в соответствии с временной диаграммой в соответствующих тактах значения п-х (младших), п-1

11

...,к-х, l-x разрядов соответственно

делителя (Y,(,,Jи делимого (Х)

т-й пары (т 1, 00 , k п,1). Синхронизирующие сигналы подают на вход 6 синхронизации делителя, знаки

п

частных первой, второй,..., 2

+ 1-й

...,т-й пар чисел выдаются в конце каждого такта, в котором они поступили на сумматор по модулю два в певом разряде информационного выхода делителя. Первый,.второй,...,п-й раряды частного первой пары выдаются соответственно на второй, третий,.. n+1-й разряды информационного выхода делителя (выходы 92 , 9, ,. .. ,9,) соответственно в , 2(п+1)-м, ...,п(п+1)-м тактах, для второй пар соответственно в п+2, 2(п+1)+1;

3(1)+1п(п+1)+ тактах, для

третьей в п+3; 2)п+1)+2,- 3(п+1 )+2,. п(п+1)+2 тактах, для т-й пары первый

второй, третийп-й разряды частнго выдаются на соответствующие раз-ряды информационного выхода делителя соответственно в (п+)+(т-1) 2(n+l)+(m-l),...,n(n+l)+(m-l) тактах. Каждый элемент задержки обеспечивает задержку сигналов, поступающих от соответствуюиа1х вычислительных ячеек на его. первый и второй входы соответственно на п+1 и п+2 такта, что позволяет сократить время обновления входной информации каждой вычислительной ячейки до одного такта, равного периоду повторения синхронизирующих импульсов, но поскольку на следующую в этом же столбце вычислительную ячейку поступают инвертированные предыдущей вычислительной ячейкой синхронизирую-.

щие импульсы, то это позволяет увели

5874996

чить время обновления входной информации вычислительной ячейки еще в два раза, т.е. длительность такта равна длительности импульса синхронизации.

20

25

30

цы.

Формула изобретения

Мультиконвейерный делитель, содер- 10 жащий матрицу из (п+1).п вычислительных ячеек и (п-разрядность операндов) каждая из которых содержит однораз- рядньй сумматор и сумматор по модулю два, выход которого соединен с пер- 15 вьгм информационным входом одноразрядного сумматора, отличающий- с я тем, что, с целью повьшения быстродействия, в него введены матрица из (n+l) (п-1 ) элементов задержки и сумматор по модулю два, а каждая вычислительная ячейка дополнительно содержит четыре триггера и элемент НЕ, причем в каждой вычислительной ячейке матрицы информационные входы первого, второго, третьего и четвертого триггеров соединены соответственно с первым, вторым, третьим и четвертым входами вычислительной ячейки, пятый вход которой соединен с синхровходами всех триггеров и элемента НЕ, выход которого соединен с первым выходом вычислительной ячейки, второй и третий выходы которой соединены соответственно с 35 выходами суммы и переноса одноразрядного сумматора, второй и третий информационные входы которого соединены, соответственно с выходами третьего и четвертого триггеров, выходы пер- 40 вого и второго триггеров соединены соответственно с первым и вторым информационными входами сумматора по модулю два и четвертым и пятым выходами вычислительной ячейки, первый вход 5 (1,1)-й вычислительной ячейки матрицы соединен соответственно с информационным входом i-ro разряда делителя (i 1,,.,,п), информационный вход i-ro разряда делимого делителя соединен соответственно с третьим входом (i+1,1)-вычислительной ячейки матрицы, первый управляющий вход делителя соединен с третьим входом (1,1)-й вычислительной ячейки матри.(

/w

/4

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| Мультиконвейерное вычислительное устройство | 1988 |

|

SU1548785A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Устройство для деления @ -разрядных чисел | 1984 |

|

SU1223224A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Однородная вычислительная структура | 1985 |

|

SU1251104A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Устройство для деления | 1989 |

|

SU1667057A1 |

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для деления M-пар N-разрядных чисел в мультиконвейерном режиме. Цель изобретения - повышение быстродействия. Делитель содержит матрицу вычислительных ячеек, матрицу элементов задержки и сумматор по модулю два. Каждая вычислительная ячейка содержит четыре триггера 10 1 - 10 4, сумматор по модулю два 12, элемент НЕ 11 и одноразрядный сумматор 13. Быстродействие делителя определяется в основном длительностью переходного процесса вычислительной ячейки. Делитель целесообразно реализовать на основе СБИС вследствие его структурной однородности. 3 ил.

9,

Фиг. J

- hr.. .., ,,,f7, J,.

Kt. 1О.я.г| К/,д /|

,д ;||fy, ff,j

bm ГгЩ foJI loT Fm .7l Kv, I 1%г1 ky.jj ICy, f y,/; . А-Я

fc I

lyff.il уГЛ ГУдП , Е31 5 .. , ,, ,, ,. ,, ,. ,.

I-libi.-liiO HiiJl г М К /и к. Д ПглП ЕЛ Г: ,,„

4з I г-1 ,, ., . - / У/ - д . ./ Ktt

У/ -г,Л./ y/j-l,/fl Ул-,я

1 |У.1 /1 1..|,11 |y.jL . I I I Ij It ,

5j I , I-1 n;,/Z t M./2 l ,.;.

IEUJ-ОйЗ-Ot51....I II I r lITrr: rnI I

|y-,..tl |y. „jl

JdV, 7

Уг.// Л y/rj,/: , /,гУд-дп У,

л М iflM)

,, ,.. - t 4 Jr,, , //j,% J

hi.) L nmnmfir I 1I II I

y/. /г У - /г-гft. /г }

ГУГП ГйЛГУГППм;ЛI

l,1lt

/..л/lv; ;,

L

L

Kt. 1О.я.г| К/,д /|

,д ;||fy, ff,j

. ,.

|y-,..tl |y. „jl

l,1lt

ri

/..л/lv; ;,

i,l:-i /л л/г г), г,, «АО

гггл птл ГП ГП f ГП

ГгГП (7771 ГПП

| Конвейерный делитель | 1983 |

|

SU1164699A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шило В.Л | |||

| Популярные цифровые микросхемы./Справочник | |||

| - М.: Радио и связь, 1987 | |||

| Евдокимов В.Ф.,.Стасюк А.И | |||

| Параллельные вычислительные структуры на основе разрядных методов лычис- лений, - Киев.: Наукова думка, 1987, с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-08-23—Публикация

1988-04-26—Подача