Изобретение относится к области измерительной и вычислительной техники и предназначено для спектрального анализа сигналов произвольной формы с целью определения амплитуд ортогональных составляющих Уолша.

Известен дискретно-аналоговый анализатор ортогональных составляющих спектра электрических сигналов [1], содержащий устройство выборки мгновенных значений сигнала, в который входят сдвиговый регистр, две группы ключей соответственно для четных и нечетных частот в косинусном канале и две группы ключей соответственно для четных и нечетных частот в синусном канале, группы развязывающих четырехвходовых элементов ИЛИ соответственно в синусном и косинусном каналах, блоки изменения знака в косинусном и синусном каналах, состоящие из триггера, ключей и инвертирующего операционного усилителя с единичным коэффициентом передачи, а также двух двухвходовых элементов ИЛИ, группу из четырех многовходовых сумматоров соответственно для четных и нечетных частот в синусном и косинусном каналах и генератор импульсов, управляющий работой регистра сдвига.

Недостатками аналога являются сложность и громоздкость схемы, большое количество элементов и связей между ними.

Наиболее близким техническим решением к предлагаемому является устройство для спектрального анализа [2], содержащее блок преобразования, включающий в себя группу квантователей, блок управления с последовательно соединенными генератором импульсов и коммутатором, блок памяти, включающий в себя группу запоминающих ячеек, группу матриц, состоящих из вычислительных ячеек, причем каждая из вычислительных ячеек восьмивходовая и выполнена в виде двух семивходовых суммирующих усилителей, содержащих входные резисторы и резисторы обратной связи; информационные входы всех квантователей блока преобразования соединены с входами устройства, их управляющие входы соединены с выходами коммутатора, а информационные выходы - с входами запоминающих ячеек блока памяти; сигналы, пропорциональные амплитудам ортогональных составляющих комплексного спектра, снимаются с выходов вычислительных ячеек первой от выхода матрицы; каждая из трех вычислительных ячеек этой матрицы связана с четырьмя первыми вычислительными ячейками второй от выхода матрицы, а каждая последующая пара вычислительных ячеек первой от выхода матрицы связана со всеми вычислительными ячейками последующей четверки ячеек второй матрицы, одновременно у остальных матриц вычислительных ячеек каждая k-я вычислительная ячейка предыдущей матрицы, в пределах периода повторения связей двух соседних матриц по их высоте, соединена с (k+2)βn вычислительными ячейками последующей матрицы (где β = 2, 3... - номер той из рассматриваемых двух матриц, которая ближе к выходу устройства; n=0, 1, 2...), причем k-я вычислительная ячейка последней матрицы связана с k-й и (k+N/2)-й запоминающими ячейками блока памяти при log2N - нечетном и с (k+Nn/4)-й при log2N - четном, а период повторения связей по высоте матрицы равен 4m-1 (где m - номер вычислительной ячейки).

Недостатками прототипа являются сложность и громоздкость схемы, большое количество элементов и связей между ними.

Техническая задача, решаемая изобретением, - упрощение анализатора.

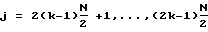

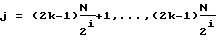

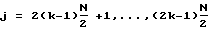

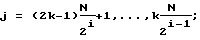

Указанная техническая задача решается благодаря тому, что в устройство для спектрального анализа, содержащее группу из N (где N=2n - число ортогональных составляющих определяемого спектра) аналоговых блоков памяти, информационные входы которых объединены между собой и подключены ко входному зажиму устройства, генератор прямоугольных импульсов, дополнительно введены заполненная матрица арифметических блоков размера N•n, представляющих собой двухвходовые блоки суммирования и блоки вычитания, дешифратор, счетчик и одновибратор, вход запуска которого объединен с тактовым входом счетчика и подключен к выходу генератора прямоугольных импульсов, а выход соединен со входом стробирования дешифратора, управляющие входы которого подключены к информационным выходам счетчика, а каждый j-й выход соединен с управляющим входом j-го аналогового блока памяти, выходы аналоговых блоков памяти соединены соответственно со входами матрицы арифметических блоков, у которой блоки суммирования являются ij-ми (где i=1,...,n - номер столбца матрицы, a j= 1,..., N - номер строки матрицы) элементами матрицы арифметических блоков при i=1,..., n,  (где k=1,..., 2i-1 - номера групп строк элементов матрицы в i-м столбце, заполненных или только блоками суммирования, или только блоками вычитания; k=1,..., N/2; Mi=N/2i - число элементов в группе строк i-го столбца; M=N/2,..., 1), а блоки вычитания являются ij-ми элементами матрицы арифметических блоков при i= 1, ..., n,

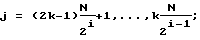

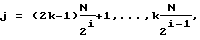

(где k=1,..., 2i-1 - номера групп строк элементов матрицы в i-м столбце, заполненных или только блоками суммирования, или только блоками вычитания; k=1,..., N/2; Mi=N/2i - число элементов в группе строк i-го столбца; M=N/2,..., 1), а блоки вычитания являются ij-ми элементами матрицы арифметических блоков при i= 1, ..., n,  , k=1,..., N/2.

, k=1,..., N/2.

Причем входы блоков i-го столбца матрицы арифметических блоков подключены к выходам блоков (i-1)-го столбца следующим образом (при i=2,...,n, j= 1, ...,N): один из входов блока суммирования j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-гo столбца, другой вход блока суммирования j-й строки i-го столбца подключен к выходу блока (j+N/2i)-й строки (i-1)-го столбца, вход вычитаемого блока вычитания j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-го столбца, вход уменьшаемого блока вычитания j-й строки i-го столбца подключен к выходу блока (j-N/2i)-й строки (i-1)-го столбца; входы блоков 1-го столбца матрицы подключены к выходам группы аналоговых блоков памяти следующим образом (при j=1,..., N): один из входов блока суммирования j-й строки подключен к выходу аналогового блока памяти j-й строки, другой вход блока суммирования j-й строки подключен к выходу аналогового блока памяти (j+N/2i)-й строки, вход вычитаемого блока вычитания j-й строки подключен к выходу аналогового блока памяти j-й строки, вход уменьшаемого блока вычитания j-й строки подключен к выходу аналогового блока памяти (j-N/2i)-й строки; выход каждого j-го (при j=1,..., N) блока n-го столбца матрицы арифметических блоков соединен с j-м выходным зажимом анализатора.

Каждый из блоков суммирования в первом варианте реализации содержит операционный усилитель, выход которого является выходом блока суммирования и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый дополнительный резистор соединен с шиной нулевого потенциала, которая через второй дополнительный резистор соединена с неинвертирующим входом операционного усилителя, который через первый и второй входные резисторы подключен к первому и второму входам блока суммирования; каждый из блоков вычитания в первом варианте реализации содержит операционный усилитель, выход которого является выходом блока вычитания и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый входной резистор подключен ко входу вычитаемого блока вычитания, вход уменьшаемого которого через второй входной резистор соединен с неинвертирующим входом операционного усилителя, который соединен с шиной нулевого потенциала через дополнительный резистор.

Каждый из блоков суммирования во втором варианте реализации содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через первый и второй входные резисторы подключен к первому и второму входам блока суммирования, выход первого операционного усилителя через третий входной резистор соединен с инвертирующим входом второго операционного усилителя, который через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока суммирования, неинвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала; каждый из блоков вычитания во втором варианте реализации содержит первый операционный усилитель, выход которого через первый резистор обратной связи соединен с инвертирующим входом первого операционного усилителя, который через первый входной резистор подключен ко входу уменьшаемого блока вычитания, выход первого операционного усилителя через второй входной резистор соединен с инвертирующим входом второго операционного усилителя, который через третий входной резистор подключен ко входу вычитаемого блока вычитания и через второй резистор обратной связи соединен с выходом второго операционного усилителя, который является выходом блока вычитания, неинвертирующие входы первого и второго операционных усилителей соединены с шиной нулевого потенциала.

Существенными отличиями предлагаемого технического решения являются использование матрицы арифметических блоков, элементы которой представляют собой двухвходовые блоки суммирования и блоки вычитания, а также использование значительно меньшего количества связей между арифметическими блоками матрицы, организованных по новому алгоритму. В предлагаемом анализаторе используется меньшее количество арифметических блоков (при обеспечении той же точности анализа), причем эти блоки имеют по 2 входа вместо 7 у прототипа. Это, в свою очередь, позволяет значительно сократить число связей (в несколько раз) между блоками анализатора. Эти существенные отличия обеспечивают достижение положительного эффекта - упрощение анализатора.

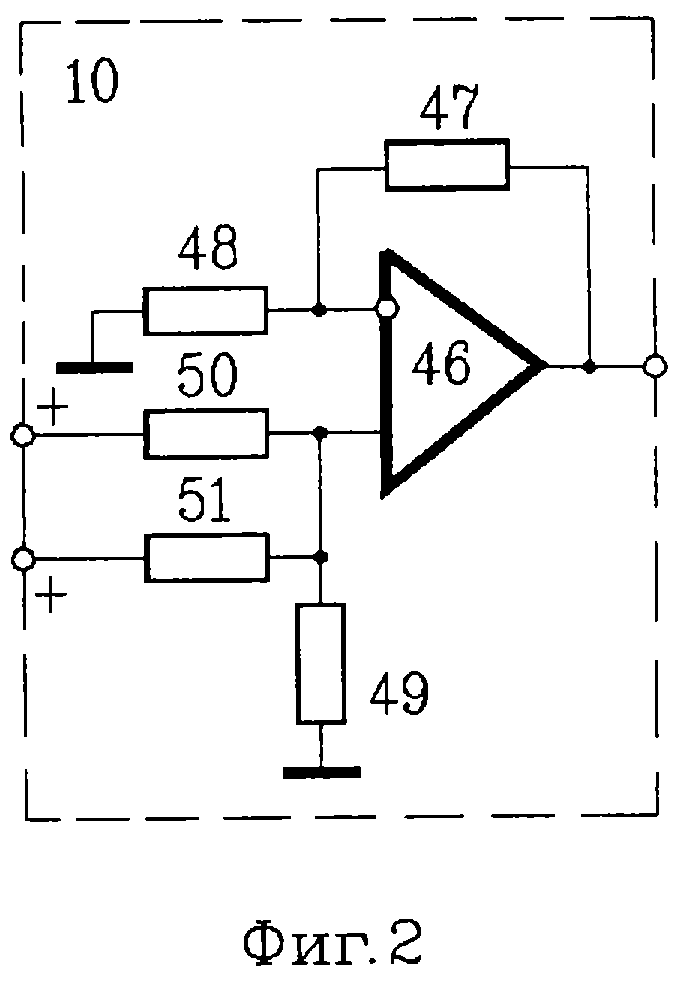

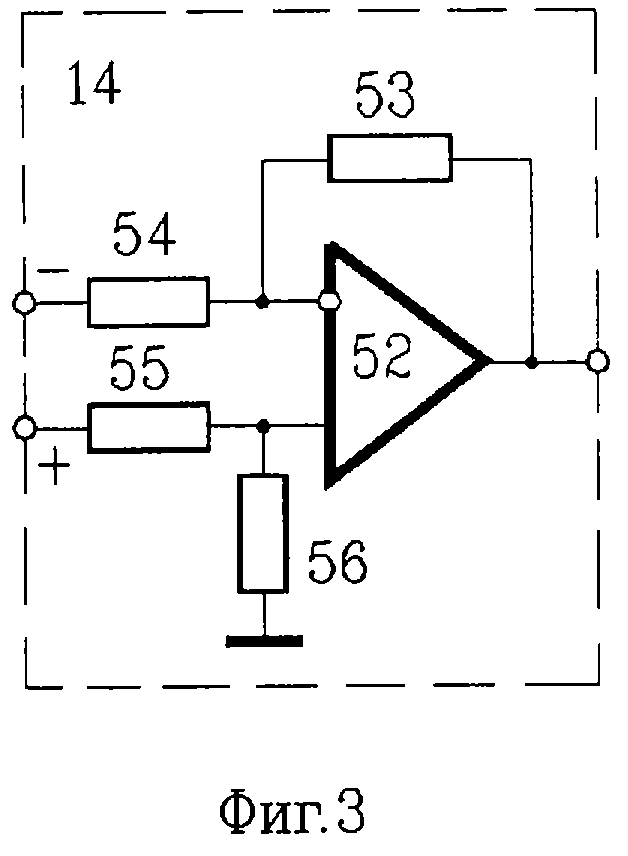

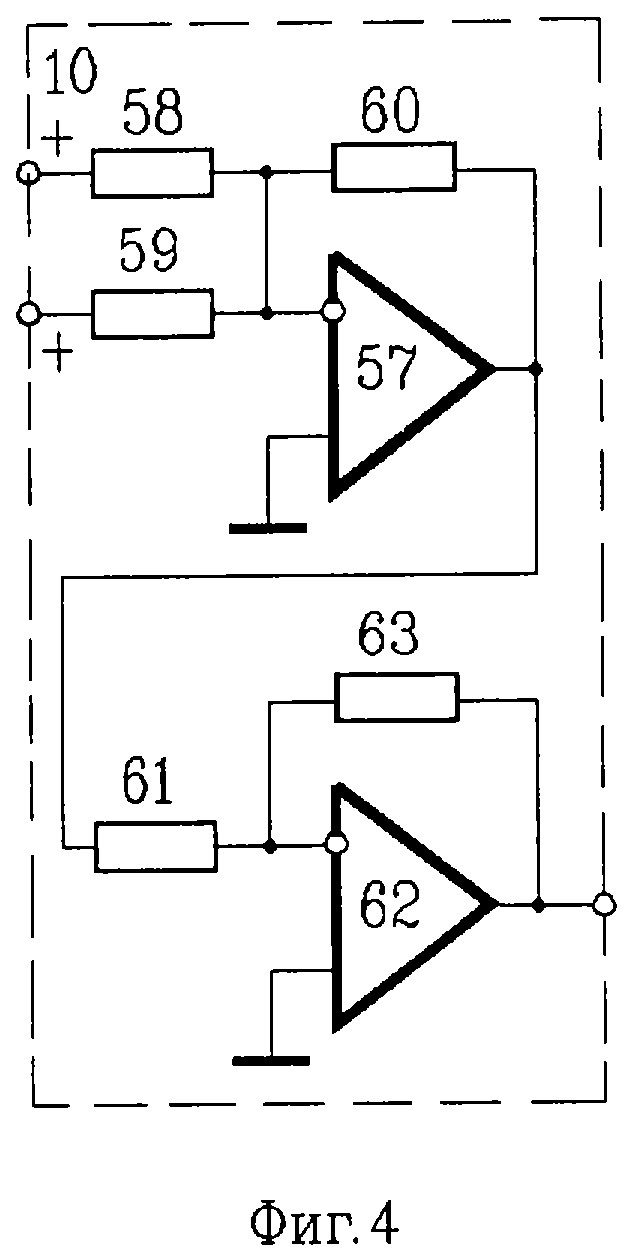

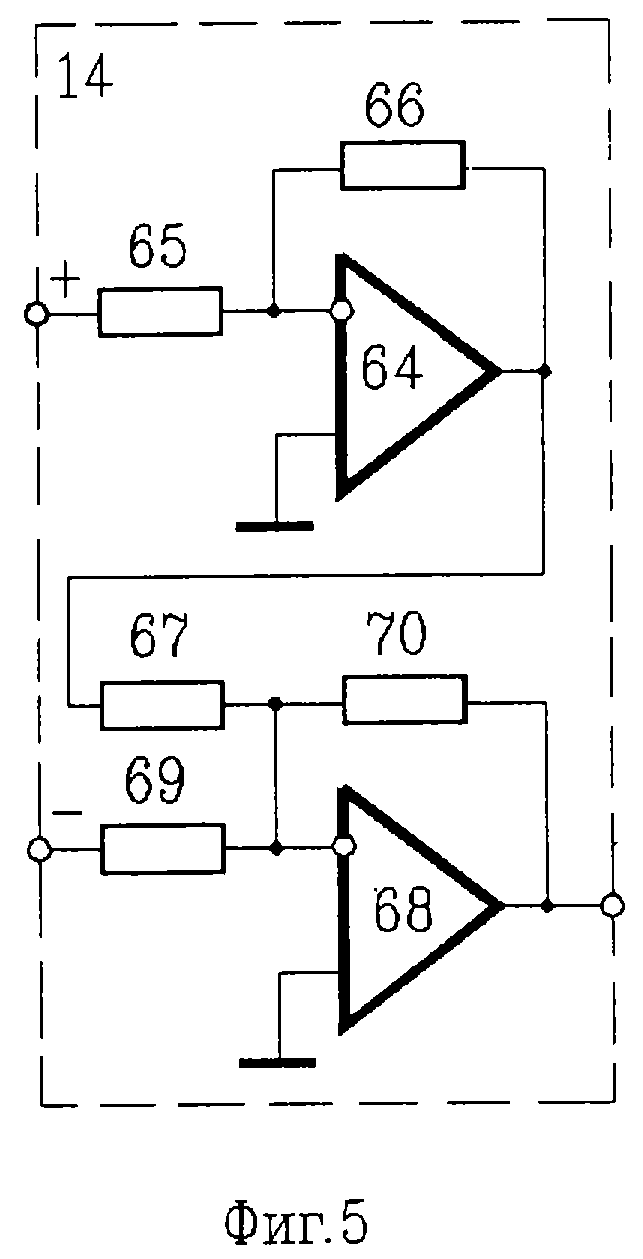

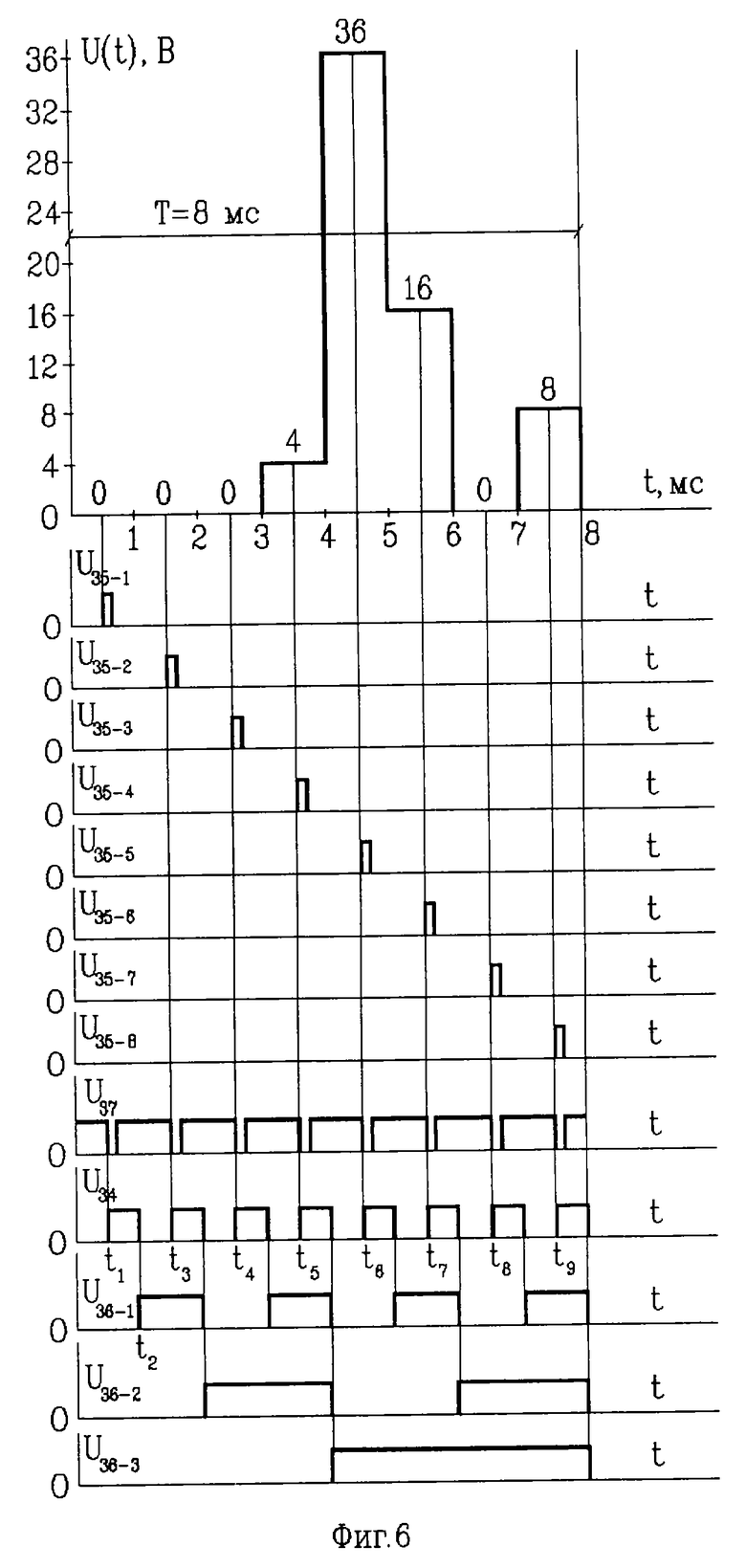

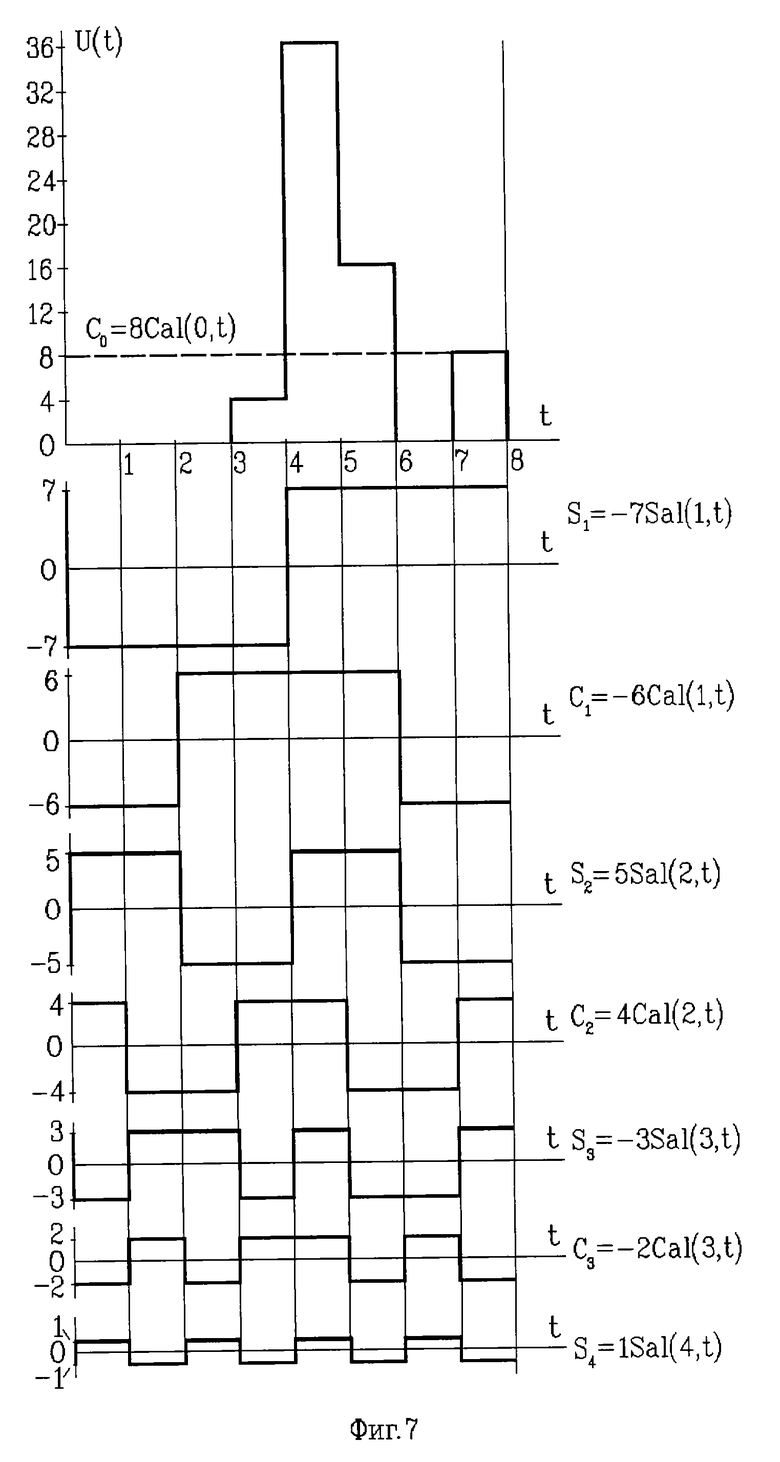

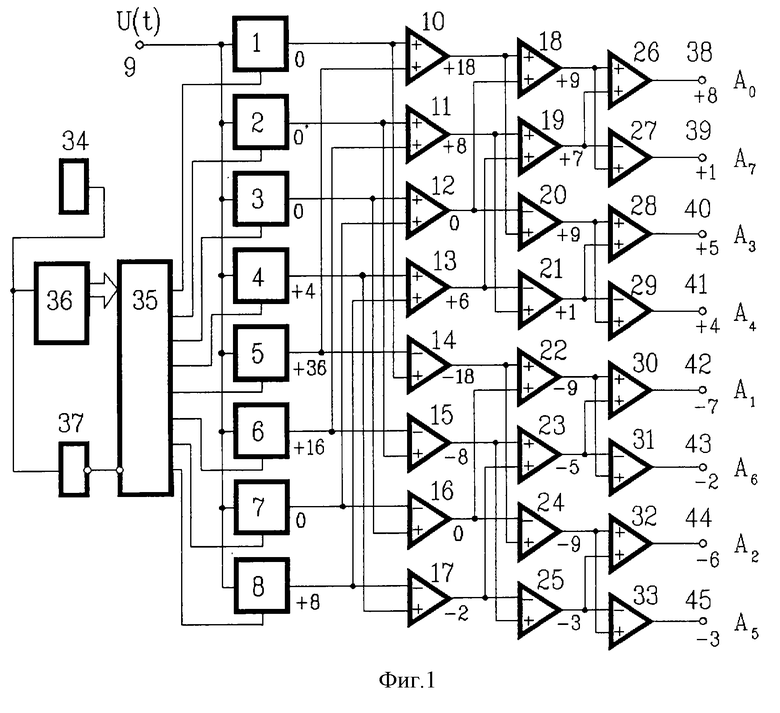

На фиг. 1 представлена структурная схема анализатора, на фиг.2 и 4 предложены варианты реализации схемы блока суммирования, на фиг.3 и 5 - варианты реализации схемы блока вычитания, на фиг.6 приведены графики изменений напряжения на элементах схемы анализатора, а на фиг.7 представлено разложение в ряд ортогональных составляющих Уолша исходного входного сигнала U(t).

Анализатор содержит группу из N (где N=2n - число ортогональных составляющих определяемого спектра; в рассматриваемом примере N=8, n=3) аналоговых блоков 1-8 памяти (АБП), информационные входы которых объединены между собой и подключены ко входному зажиму 9 устройства, а выходы соединены соответствующим образом со входами заполненной матрицы размера N•n арифметических блоков (МАБ) 10-33, представляющих собой двухвходовые блоки суммирования (БС) 10-13, 18, 19, 22, 23, 26, 28, 30, 32, которые являются ij-ми (где i=1, . . . , n - номер столбца матрицы, a j=1,..., N - номер строки матрицы) элементами МАБ при i=l,..., n,  (где k=1,..., 2i-1 - номера групп строк элементов матрицы в i-м столбце, заполненных или только блоками суммирования, или только блоками вычитания; k=1,..., N/2; Mi=N/2i - число элементов в группе строк i-го столбца; M=N/2,...,1), и блоки вычитания (БВ) 14-17, 20, 21, 24, 25, 27, 29, 31, 33, которые являются ij-ми элементами МАБ при i=1,...,n,

(где k=1,..., 2i-1 - номера групп строк элементов матрицы в i-м столбце, заполненных или только блоками суммирования, или только блоками вычитания; k=1,..., N/2; Mi=N/2i - число элементов в группе строк i-го столбца; M=N/2,...,1), и блоки вычитания (БВ) 14-17, 20, 21, 24, 25, 27, 29, 31, 33, которые являются ij-ми элементами МАБ при i=1,...,n,  , k=1,..., N/2, генератор 34 прямоугольных импульсов (ГПИ), дешифратор 35, счетчик 36 и одновибратор 37, вход запуска которого объединен с тактовым входом счетчика 36 и подключен к выходу ГПИ 34, а выход соединен со входом стробирования дешифратора 35, управляющие входы которого подключены к информационным выходам счетчика 36, а выходы соответственно соединены с управляющими входами АБП 1-8.

, k=1,..., N/2, генератор 34 прямоугольных импульсов (ГПИ), дешифратор 35, счетчик 36 и одновибратор 37, вход запуска которого объединен с тактовым входом счетчика 36 и подключен к выходу ГПИ 34, а выход соединен со входом стробирования дешифратора 35, управляющие входы которого подключены к информационным выходам счетчика 36, а выходы соответственно соединены с управляющими входами АБП 1-8.

Причем входы блоков i-го столбца МАБ подключены к выходам блоков (i-1)-го столбца следующим образом (при i=2,...,n, j=1,...,N): один из входов БС j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-гo столбца, другой вход БС j-й строки i-го столбца подключен к выходу блока (j+N/2i)-й строки (i-1)-гo столбца, вход вычитаемого БВ j-й строки i-го столбца подключен к выходу (i-1)-го блока j-й строки, вход уменьшаемого БВ j-й строки i-го столбца подключен к выходу (i-1)-го блока (j-N/2i)-й строки; входы блоков 1-го столбца МАБ подключены к выходам группы АБП 1-8 следующим образом (при j=1,...,N): один из входов БС j-й строки подключен к выходу АБП j-й строки, другой вход БС j-й строки подключен к выходу АБП (j+N/2i)-й строки, вход вычитаемого БВ j-й строки подключен к выходу АБП j-й строки, вход уменьшаемого БВ j-й строки подключен к выходу АБП (j-N/2i)-й строки; выходы блоков 26-33 n-го столбца МАБ соединены соответственно с выходными зажимами 38-45 анализатора.

Каждый из блоков 10-13, 18, 19, 22, 23, 26, 28, 30, 32 суммирования в первом варианте реализации (фиг.2) содержит (на примере БС 10) операционный усилитель (ОУ) 46, выход которого является выходом БС 10 и через резистор 47 обратной связи соединен с инвертирующим входом ОУ 46, который через первый дополнительный резистор 48 соединен с шиной нулевого потенциала, которая через второй дополнительный резистор 49 соединена с неинвертирующим входом ОУ 46, который через первый и второй входные резисторы 50 и 51 подключен к первому и второму входам БС 10.

Каждый из блоков 14-17, 20, 21, 24, 25, 27, 29, 31, 33 вычитания в первом варианте реализации (фиг.3) содержит (на примере БВ 14) ОУ 52, выход которого является выходом БВ 14 и через резистор 53 обратной связи соединен с инвертирующим входом ОУ 52, который через первый входной резистор 54 подключен ко входу вычитаемого БВ 14, вход уменьшаемого которого через второй входной резистор 55 соединен с неинвертирующим входом ОУ 52, который соединен с шиной нулевого потенциала через дополнительный резистор 56.

Каждый из блоков 10-13, 18, 19, 22, 23, 26, 28, 30, 32 суммирования во втором варианте реализации (фиг.4) содержит (на примере БС 10) первый ОУ 57, инвертирующий вход которого через первый 58 и второй 59 входные резисторы подключен к первому и второму входам БС 10, а также через первый резистор 60 обратной связи соединен с выходом первого ОУ 57, который через третий входной резистор 61 соединен с инвертирующим входом второго ОУ 62, который через второй резистор 63 обратной связи соединен с выходом второго ОУ 62, являющегося выходом БС 10, неинвертирующие входы первого ОУ 57 и второго ОУ 62 соединены с шиной нулевого потенциала.

Каждый из блоков 14-17, 20, 21, 24, 25, 27, 29, 31, 33 вычитания во втором варианте реализации (фиг.5) содержит (на примере БВ 14) первый ОУ 64, инвертирующий вход которого через первый входной резистор 65 подключен ко входу уменьшаемого БВ 14 и через первый резистор 66 обратной связи соединен с выходом первого ОУ 64, который через второй входной резистор 67 соединен с инвертирующим входом второго ОУ 68, который через третий входной резистор 69 подключен ко входу вычитаемого БВ 14 и через второй резистор 70 обратной связи соединен с выходом второго ОУ 68, являющегося выходом БВ 14, неинвертирующие входы первого ОУ 64 и второго ОУ 68 соединены с шиной нулевого потенциала.

Все блоки 10-33 МАБ имеют одинаковые коэффициенты передачи по входам, равные 0,5.

При подготовке анализатора к работе выбирается частота ГПИ 34 по следующей формуле:

где Т=8 мс - длительность периода исследуемого входного сигнала U(t) на фиг.6.

Анализатор работает следующим образом.

В момент времени t=0 счетчик 36 находился в состоянии, при котором его выходной код был равен 000 (см. на фиг.6 напряжения первого, второго и третьего разрядов выхода счетчика 36 U36-1,U36-2, U36-3).

В момент времени t1 на выходе ГПИ 34 появляется импульс, который своим передним фронтом запускает одновибратор 37. Выходной отрицательный импульс последнего стробирует дешифратор 35, на первом выходе (поскольку к управляющим входам дешифратора 35 приложен код 000 с выхода счетчика 36) которого появляется единичный управляющий импульс (см. на фиг.6 напряжение U35-1). Этот импульс подается на управляющий вход АБП 1, в результате чего в АБП 1 вписывается напряжение U(t1)=0. На фиг.1 это напряжение показано на выходе АБП 1 (как и на выходах остальный АБП 2-8, блоков 10-33 МАБ, а также на выходных зажимах 38 - 45 анализатора) уменьшенным шрифтом снизу.

В момент времени t2 выходной импульс ГПИ, заканчивась, переводит счетчик 36 в состояние 001, при котором на первом разряде выхода счетчика 36 появляется единичное напряжение (см. на фиг.6 напряжение U36-1).

Появляющийся в момент времени t3 отрицательный импульс на выходе одновибратора 37 стробирует дешифратор 35 - на втором выходе последнего появляется единичный управляющий импульс, который вписывает в АБП 2 напряжение U(t3)=0.

Аналогичным образом далее через одинаковые промежутки времени в 1 мс в АБП 3-8 вписываются следующие напряжения (см. фиг.6): в АБП 3 - U(t4)=0, в АБП 4 - U(t5)= 4 В, в АБП 5 - U(t6)=36 В, в АБП 6 - U(t7)=16 В, в АБП 7 - U(t8)=0, в АБП 8 - U(t9)=8 В.

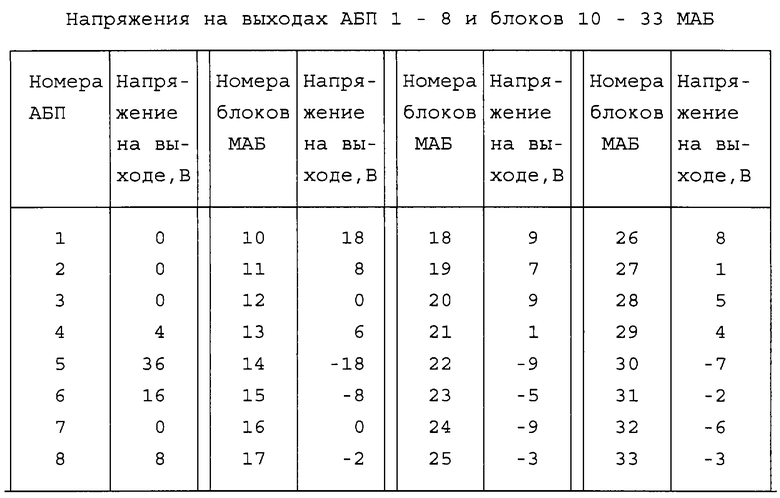

Выходные напряжения АБП 1-8 прикладываются ко входам блоков 10-17 МАБ, на выходах арифметических блоков 10-33 которой появляются напряжения согласно таблице (см. также фиг.1).

Напряжения на выходах блоков 26-33 МАБ являются выходными напряжениями анализатора, они присутствуют на выходных зажимах 38-45. Модули этих напряжений задают амплитуды Аi ортогональных составляющих Уолша, а знаки определяют начальный угол этих составляющих.

На фиг. 7 представлено разложение исходного входного сигнала U(t) в ряд ортогональных составляющих Уолша:

= А0Саl(0, t)+A1Sal(1, t)+А2Саl(2, t)+A3Sal(3, t)+А4Саl(4, t)+A5Sal(5, t)+A6Cal(6, t)+A7Sal(7, t)= 8Саl(0, t)-7Sal(1, t)-6Саl(1, t)+5Sal(2, t)+4Саl(2, t)-3Sal(3, t)-2Саl(3, t)+1Sal(4, t), (2)

где AjWal(j, t) - j-я функция Уолша;

AjCal(j/2, t) - j-я четная ортогональная составляющая Уолша;

AjCal((j+1)/2, t) - j-я нечетная ортогональная составляющая Уолша.

Преимуществом предлагаемого анализатора по сравнению с известными техническими решениями является его упрощение. Схема анализатора легко реализуется на интегральных микросхемах отечественного производства.

Источники информации

1. Авторское свидетельство СССР N 553547, кл. G 01 R 23/16, 1977.

2. Авторское свидетельство СССР N 1083124, кл. G 01 R 23/16, 1984 (прототип).

Изобретение относится к области вычислительной техники и может быть использовано для спектрального анализа сигналов произвольной формы. Техническим результатом является расширение функциональных возможностей. Анализатор содержит группу аналоговых блоков памяти, генератор прямоугольных импульсов, матрицу арифметических блоков, представляющих собой двухвходовые блоки суммирования и блоки вычитания, дешифратор, счетчик и одновибратор. 4 з.п.ф-лы, 7 ил., 1 табл.

(где k=1,..., 2i-1 - номера групп строк элементов матрицы в i-м столбце, заполненных или только блоками суммирования, или только блоками вычитания; k= 1,..., N/2; Mi=N/2i - число элементов в группе строк i-го столбца; M=N/2, . .., 1), а блоки вычитания являются ij-ми элементами матрицы арифметических блоков при i=1,..., n; k=1,..., N/2, причем входы блоков i-го столбца матрицы арифметических блоков подключены к выходам блоков (i-1)-го столбца следующим образом (при i=2,..., n, j=1,..., N): один из входов блока суммирования j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-гo столбца, другой вход блока суммирования j-й строки i-го столбца подключен к выходу блока (j+N/2i)-й строки (i-1)-го столбца, вход вычитаемого блока вычитания j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-гo столбца, вход уменьшаемого блока вычитания j-той строки i-го столбца подключен к выходу блока (j-N/2i)-й строки (i-1)-гo столбца; входы блоков 1-го столбца матрицы подключены к выходам группы аналоговых блоков памяти следующим образом (при j=1,..., N): один из входов блока суммирования j-й строки подключен к выходу аналогового блока памяти j-й строки, другой вход блока суммирования j-й строки подключен к выходу аналогового блока памяти (j+N/2i)-й строки, вход вычитаемого блока вычитания j-й строки подключен к выходу аналогового блока памяти j-й строки, вход уменьшаемого блока вычитания j-й строки подключен к выходу аналогового блока памяти (j-N/2i)-той строки; выход каждого j-го (при j=1,..., N) блока n-го столбца матрицы арифметических блоков соединен с j-м выходным зажимом анализатора.

k=1,..., N/2, причем входы блоков i-го столбца матрицы арифметических блоков подключены к выходам блоков (i-1)-го столбца следующим образом (при i=2,..., n, j=1,..., N): один из входов блока суммирования j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-гo столбца, другой вход блока суммирования j-й строки i-го столбца подключен к выходу блока (j+N/2i)-й строки (i-1)-го столбца, вход вычитаемого блока вычитания j-й строки i-го столбца подключен к выходу блока j-й строки (i-1)-гo столбца, вход уменьшаемого блока вычитания j-той строки i-го столбца подключен к выходу блока (j-N/2i)-й строки (i-1)-гo столбца; входы блоков 1-го столбца матрицы подключены к выходам группы аналоговых блоков памяти следующим образом (при j=1,..., N): один из входов блока суммирования j-й строки подключен к выходу аналогового блока памяти j-й строки, другой вход блока суммирования j-й строки подключен к выходу аналогового блока памяти (j+N/2i)-й строки, вход вычитаемого блока вычитания j-й строки подключен к выходу аналогового блока памяти j-й строки, вход уменьшаемого блока вычитания j-й строки подключен к выходу аналогового блока памяти (j-N/2i)-той строки; выход каждого j-го (при j=1,..., N) блока n-го столбца матрицы арифметических блоков соединен с j-м выходным зажимом анализатора.

| Устройство для спектрального анализа | 1979 |

|

SU1083124A1 |

| Дискретно-аналоговый анализатор ортогональных составляющих спектра электрических сигналов | 1975 |

|

SU553547A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| US 5252416 А, 22.12.1998. | |||

Авторы

Даты

2003-04-27—Публикация

2000-05-15—Подача