Изобретение относится к вычислительной технике и может быть использовано в системах оперативной обработки больших массивов информации.

Известно оптическое оперативное запоминающее устройство, содержащее источник излучения, адресную систему, формирующую оптику, управляемый транспарант, реверсивную регистрирующую среду, фотоприемную матрицу и устройство управления [1]

Однако известное устройство не отличается широкими функциональными возможностями, так как обеспечивает только адресную обработку информации.

По технической сущности наиболее близким к предлагаемому устройству является оптическое оперативное запоминающее устройство, содержащее последовательно расположенные и оптически связанные основные источник излучения, блок адресации луча, первый блок формирования луча, первый управляемый транспарант, первый блок фокусировки луча, реверсивный носитель информации, оптический блок считывания, светоделительный элемент, первую матрицу фотоприемников, второй блок формирования луча, второй управляемый транспорант, второй блок фокусировки луча, вторую матрицу фотоприемников и блок управления, первый выход группы информационных выходов которого соединен с управляющим входом первого управляемого транспаранта [2]

Однако и это известное устройство не обладает широкими функциональными возможностями, так как не позволяет осуществлять одновременную ассоциативную пословную выборку, перегруппировку и предподготовку данных для обработки по многим носителям.

Технической задачей является расширение функциональных возможностей за счет обеспечения одновременной ассоциативной пословной выборки, перегруппировки и предподготовки данных для обработки по многим носителям.

Сущность изобретения заключается в том, что введение n-1 дополнительных источников излучения, блоков адресации луча, первых и вторых блоков формирования луча, первых и вторых управляемых транспарантов, первых и вторых блоков фокусировки луча, реверсивных носителей информации, оптических блоков считывания, светоделительных элементов, первых и вторых матриц фотоприемников, двух входных регистров, двух входных коммутаторов, блока преобразования массивов, блока ассоциативной буферной памяти, блока выборки данных, блока регистров, выходного коммутатора и двух выходных регистров и соответствующие связи между ними позволило обеспечить одновременное обращение ко всем n группам оптических носителей и направлять запрос к блоку ассоциативной буферной памяти, а при заполнении всех оптических носителей осуществлять перегруппировку, выделяя свободные страницы.

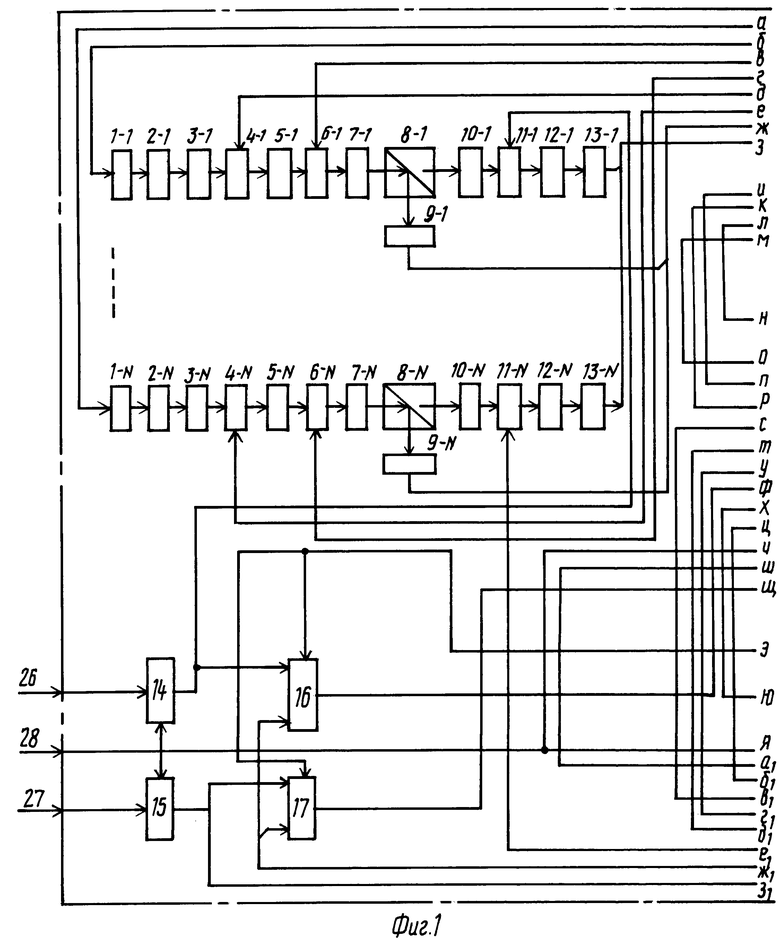

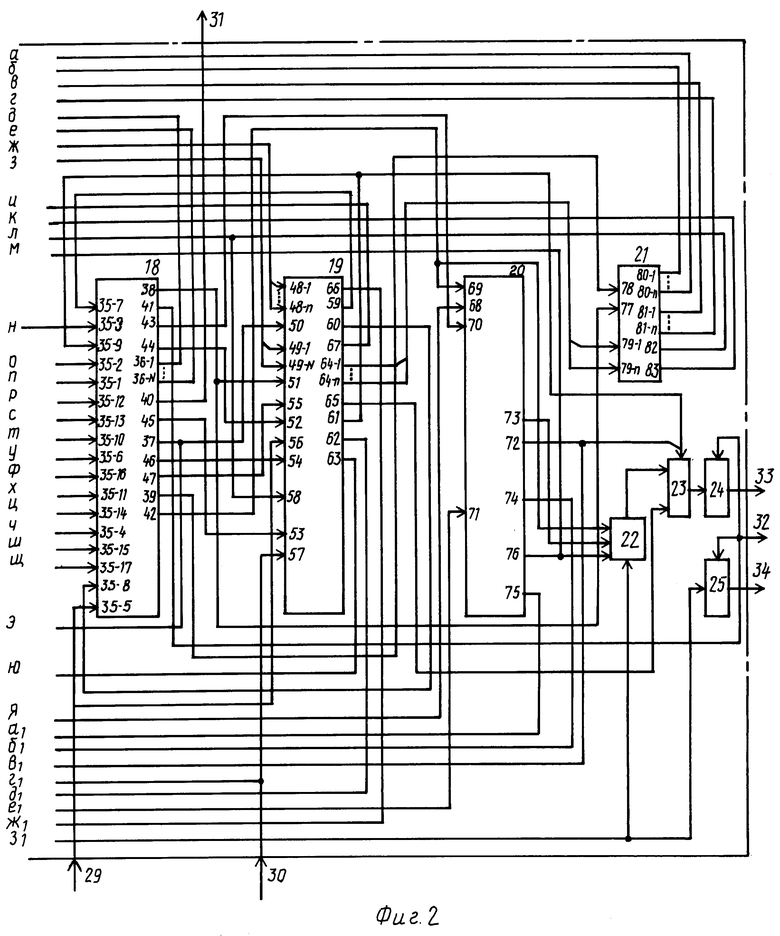

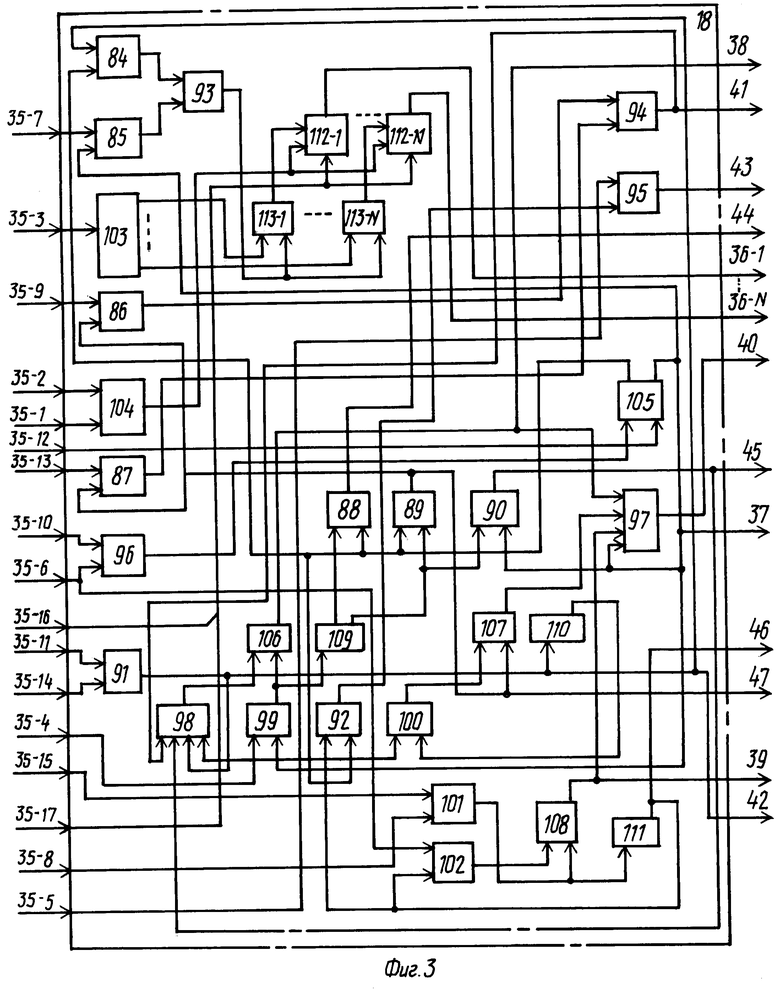

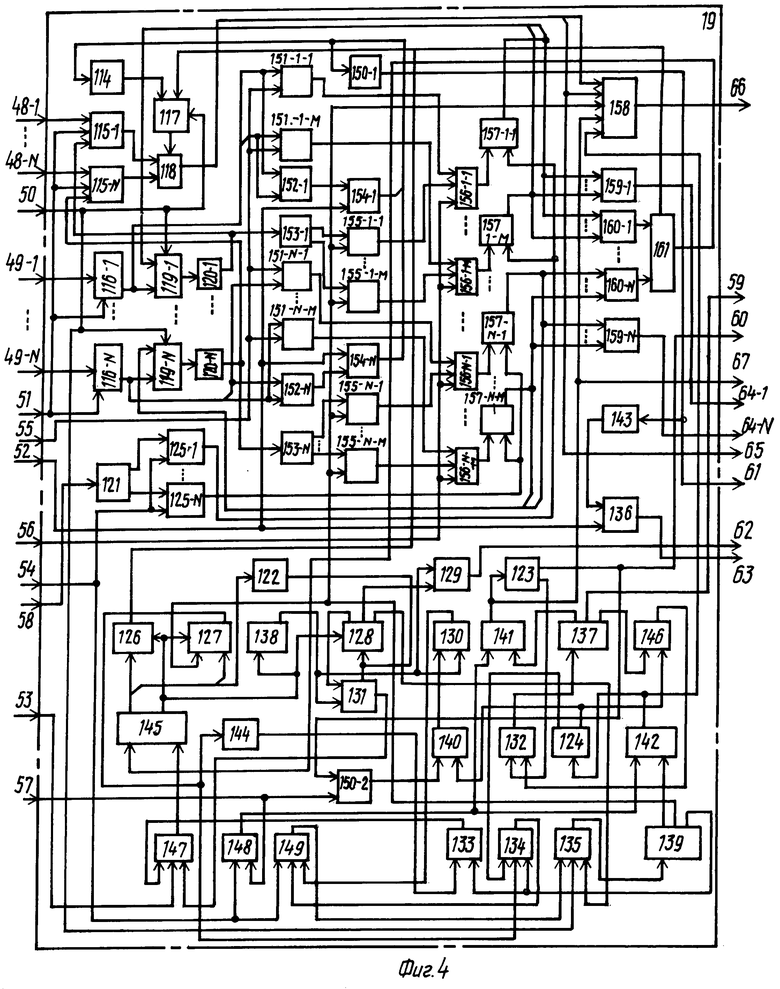

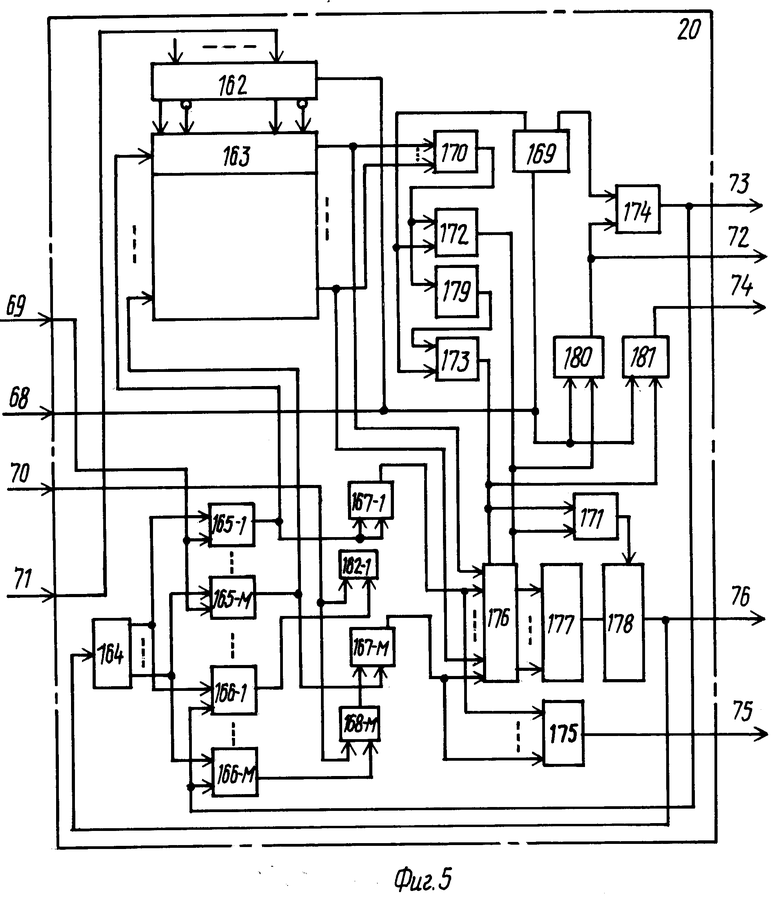

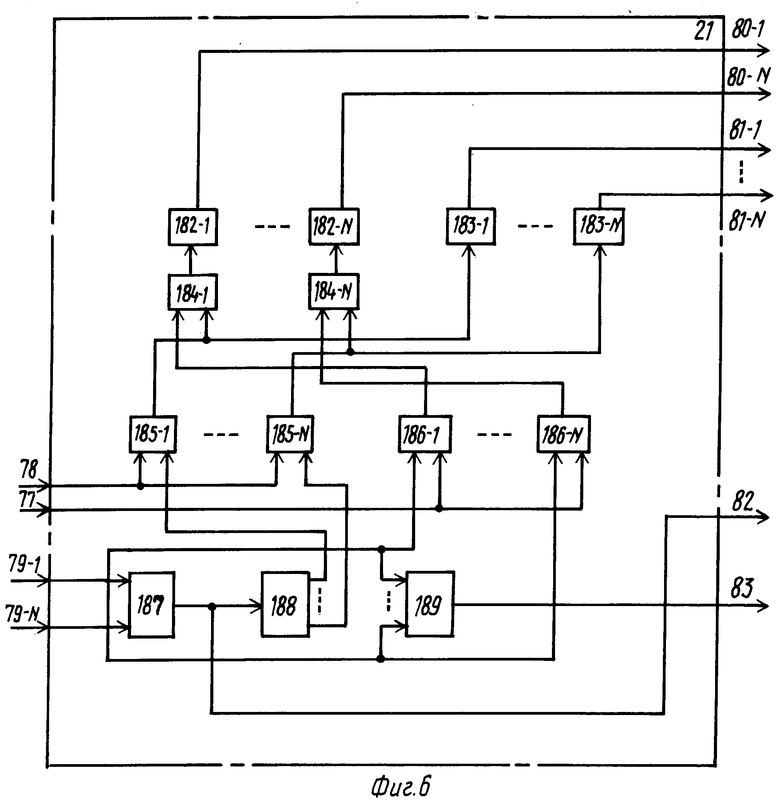

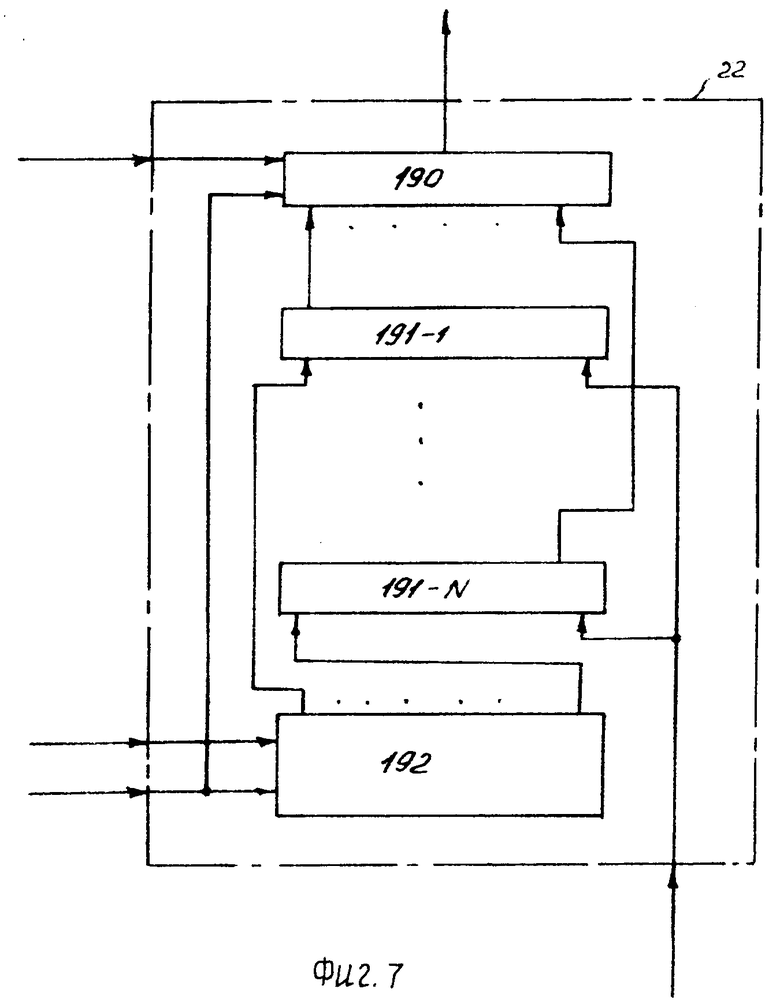

На фиг. 1 и 2 представлена функциональная блок-схема устройства; на фиг. 3 электрическая схема блока управления; на фиг. 4 блок преобразования массивов; на фиг. 5 блок ассоциативной буферной памяти; на фиг. 6 блок выборки данных; на фиг. 7 блок регистров.

Оптическое оперативное запоминающее устройство содержит последовательно расположенные и оптически связанные основные и дополнительные источники 1-1 и 1-2.1-N излучения, блоки 2-1 и 2-2.2-N адресации луча, первые блоки 3-1 и 3-2. 3-N формирования луча, первые управляемые транспаранты 4-1 и 4-2.4-N, первые блоки 5-1 и 5-2.5-N фокусировки луча, реверсивные носители 6-1 и 6-2. 6-N информации, оптические блоки 7-1 и 7-2.7-N считывания, светоделительные элементы 8-1 и 8-2.8-N, первые матрицы 9-1 и 9-2.9-N фотоприемников, вторые блоки 10-1 и 10-2.10-N формирования луча, вторые управляемые транспаранты 11-1 и 11-2.11-N, вторые блоки 12-1 и 12-2.12-N фокусировки луча, вторые матрицы 13-1 и 13-2.13-N фотоприемников. Кроме того, устройство содержит первый и второй входные регистры 14 и 15, первый и второй входные коммутаторы 16 и 17, блок 18 управления блок 19 преобразования массивов, блок 20 ассоциативной буферной памяти, блок 21 выборки данных, блок 22 регистров, выходной коммутатор 23 и первый и второй выходные регистры 24 и 25.

Устройство имеет первый и второй информационные входы 26 и 27, первый, второй и третий управляющие входы 28, 29 и 30, первый и второй управляющие выходы 31 и 32 и первый и второй информационные выходы 33 и 34 соответственно.

Синхронизация устройства однофазная. Блок 18 управления имеет с первого по третий адресные входы 35-1.35.3, с первого по двенадцатый управляющие входы 35-4.35-15, первый и второй информационные входы 35-16 и 35-17, группу информационных выходов 36-1.36-N и с первого по одиннадцатый управляющие выходы 37.47.

Блок 19 преобразования массивов имеет группу информационных входов 48-1. 48-N, группу адресных входов 49-1.49-N, с первого по восьмой управляющие входы 50.57, адресный вход 58, с первого по пятый управляющие выходы 59.63, группу управляющих выходов 64-1.64-N, первый и второй информационные выходы 65 и 66 и адресный выход 67. Блок 20 ассоциативной буферной памяти имеет с первого по третий управляющие входы 68.70, адресный вход 71 и с первого по четвертый управляющие выходы 72.75 и адресный выход 76. Блок 21 выборки данных имеет первый и второй управляющие входы 77 и 78, группу управляющих входов 79-1. 79-N, первую и вторую группы управляющих выходов 80-1.80-N и 81-1. 81-N, адресный выход 82 и управляющий выход 83. Первый и второй информационные входы 26 и 27 устройства соединены с информационными входами первого и второго входных регистров 14 и 15 соответственно, выходы которых соединены с первыми информационными входами первого и второго входных коммутаторов 16 и 17 соответственно, вторые информационные входы которой подключены к второму информационному выходу 66 блока 19 преобразования массивов. Первый управляющий вход 50 блока 19 преобразования массивов и управляющие входы первого и второго входных коммутаторов 16 и 17 соединены с первым управляющим выходом 37 блока 18 управления, второй управляющий выход 38 которого подключен к второму управляющему входу 51 блока 19 преобразования массивов и первому управляющему входу 77 блока 21 выборки данных. Второй управляющий вход 78 блока 21 выборки данных соединен с третьим управляющим выходом 39 блока 18 управления, четвертый и пятый управляющие выходы 40 и 41 которого являются соответственно, первым и вторым управляющими выходами 31 и 32 устройства, к последнему из которых подключены управляющие входы выходных регистров 24 и 25, выходы которых являются соответственно, первым и вторым информационными выходами 33 и 34 устройства. Первый управляющий вход 28 устройства соединен с управляющими входами первого и второго входных регистров 14 и 15, первым управляющим входом 35-4 блока 18 управления и первым управляющим входом 68 блока 20 ассоциативной буферной памяти, второй управляющий вход 69 которого и первый управляющий вход блока 22 регистров подключены к шестому управляющему выходу 42 блока 18 управления. С седьмого по одиннадцатый управляющие выходы 43.47 блока 18 управления соединены соответственно с третьим управляющим входом 70 блока 20 ассоциативной буферной памяти и с третьего по шестой управляющими входами 52.55 блока 19 преобразования массивов. Седьмой управляющий вход 56 блока 19 преобразования массивов и второй управляющий вход 35-5 блока 18 управления соединены с вторым управляющим входом 29 устройства, третий управляющий вход 30 которого подключен к третьему управляющему входу 35-6 блока 18 управления и восьмому управляющему входу 57 блока 19 преобразования массивов. С первого по пятый управляющие и адресный выходы 59.63 и 67 блока 19 преобразования массивов соединены соответственно с четвертого по восьмой управляющими и первым адресным входами 35-7.35-11 и 35-1 блока 18 управления, первый и второй информационные входы 35-16 и 35-17 которого подключены соответственно к выходам первого и второго входных коммутаторов 16 и 17. Адресный вход 71 блока 20 ассоциативной буферной памяти и управляющие входы вторых управляемых транспарантов 11-1.11-N подключены к выходу первого входного регистра 14. Информационные входы блока 22 регистров и второго выходного регистра 25 соединены с выходом второго входного регистра 15. Адресный выход 76 блока 20 ассоциативной буферной памяти подключены к адресному входу блока 22 регистров и к второму адресному входу 35-2 блока 18 управления, девятый и десятый управляющие входы 35-12 и 35-13 которого соединены соответственно с управляющим выходом 83 блока 21 выборки данных и первым управляющим выходом 72 блока 20 ассоциативной буферной памяти, к которому подключен первый разряд управляющего входа выходного коммутатора 23, второй разряд управляющего входа которого соединен с третьим управляющим выходом 61 блока 19 преобразования массивов, первый информационный выход 65 которого подключен к первому информационному входу выходного коммутатора 23. Второй информационный вход выходного коммутатора 23 соединен с выходом блока 22 регистров, второй управляющий вход которого соединен с вторым управляющим выходом 73 блока 20 ассоциативной буферной памяти, третий и четвертый управляющие выходы 74 и 75 которого подключены соответственно к одиннадцатому и двенадцатому управляющим входам 35-14 и 35-15 блока 18 управления. Выходы группы информационных выходов 36-1.36-N блока 18 управления соединены с управляющими входами соответствующих первых управляемых транспарантов 4-1.4-N. Входы источников излучения 1-1.1-N подключены к соответствующим выходам первой группы управляющих выходов 80-1.80-N блока 21 выборки данных, к выходам второй группы управляющих выходов 81-1.81-N которого подключены управляющие входы соответствующих реверсивных носителей 6-1.6-N информации, а выход выходного коммутатора 23 соединен с информационным входом первого выходного регистра 24.

Блок 18 управления содержит с первого по девятый элементы И 84.92, с первого по десятый элементы ИЛИ 93.102, дешифратор 103, коммутатор 104, с первого по четвертый триггеры 105.108, с первого по третий сдвиговые регистры 109.111, группу блоков 112-1.112-N регистровых памятей, группу элементов И 113-1.113-N. Первый и второй управляющие входы 35-4 и 35-5 блока соединены с первыми входами седьмого и третьего элементов ИЛИ 99 и 95 соответственно, третий управляющий вход 35-6 подключен к первым входам четвертого, шестого, восьмого и десятого элементов ИЛИ 96, 98, 100 и 102, второй вход первого из которых является седьмым управляющим входом 35-10 блока. Четвертый, пятый и шестой управляющие входы 35-7, 35-8 и 35-9 соединены с первыми входами второго элемента И 85, девятого элемента ИЛИ 101 и третьего элемента И 86 соответственно, второй вход второго из которых является двенадцатым управляющим входом 35-15 блока, восьмой и одиннадцатый управляющие входы 35-11 и 35-14 соединены с первым и вторым входами соответственно восьмого элемента И 91. Девятый и десятый управляющие входы 35-12 и 35-13 соединены с установочным входом первого триггера 105 и первым входом четвертого элемента И 87 соответственно. Первый и второй адресные входы 35-1 и 35-2 блока соединены с первым и вторым входами соответственно, коммутатора 104, выход которого подключен к входам группы блоков 112-1.112-N регистровых памятей, управляющие входы которых соединены с выходами соответствующих элементов группы элементов И 113-1.113-N, первые входы которых подключены к соответствующим выходам дешифратора 103, вход которого является третьим адресным входом 35-3 блока, первый и второй информационные входы 35-16 и 35-17 которого соединены с информационными входами группы блоков 112-1.112-N регистровых памятей, выходы которых являются группой информационных выходов 36-1.36-N блоков. Первый управляющий выход 37 блока является первым выходом первого триггера 105, который соединен с вторыми входами второго элемента И 85 и седьмого элемента ИЛИ 99 и первыми входами седьмого элемента И 90 и пятого элемента ИЛИ 97, выходы двух последних из которых являются девятым и четвертым управляющими выходами 45 и 40. Второй и третий управляющие выходы 38 и 39 блока соединены с выходами второго и четвертого триггерв 106 и 108, соответственно с пятого по восьмой управляющие выходы 41, 42, 43 и 44 блока соединены с выходами второго элемента ИЛИ 94, восьмого элемента И 91, третьего элемента ИЛИ 95 и пятого элемента И 88, первый вход последнего из которых соединен с вторым выходом первого триггера 105 и первыми входами первого, шестого и девятого элементов И 84, 89 и 92, второй вход последнего из которых и второй вход десятого элемента ИЛИ 102 подключены к выходу третьего сдвигового регистра III, который является десятым управляющим выходом 46 блока, одиннадцатый управляющий выход 47 которого соединен с выходом шестого элемента И 89, к которому подключены вторые входы третьего и четвертого элементов 86 и И 87.

Блок 19 преобразования массивов содержит приоритетный шифратор 114, группу блоков 115-1.115-N регистровых памятей, группу регистров 116-1.116-N, первый и второй коммутаторы 117 и 118, группу коммутаторов 119-1.119-N, группу приоритетных шифраторов 120-1.120-N, с первого по четвертый дешифраторы 121, 122, 123 и 124, первую группу элементов И 125-1.125-N, с первого по третий регистры 126, 127 и 128, с первого по восьмой элементы И 129.136, с первого по третий сдвиговые регистры 137, 138 и 139, триггер 140, первый и второй счетчики 141 и 142, первый и второй элементы НЕ 143 и 144, узел 145 обработки информации типа К 1810, с первого по шестой элементы 146.149, 150-1 и ИЛИ 150-2, первый N группы по М элементов И 151-1-1.151-1-М.151-N-1. 151-N-М, первую группу элементов ИЛИ 152-1.152-N, группу дешифраторов 153-1. 153-N, вторую группу элементов И 154-1.154-N, вторые группы по М элементов И 155-1-1.155-1--М.155-N-М, N группы по М элементов ИЛИ 156-1-1.156-1-М.156-N-1. 156-N-М, N групп по М триггеров 157-1-1.157-1-М.157-N-1.157-N-М, блок 158 регистровой памяти, вторую группу элементов ИЛИ 159-1.159-N, группу шифраторов 160-1.160-N, коммутатор 161.

Адресный вход 58 блока соединен с входом первого дешифратора 121, каждый i-й выход которого соединен с первым входом соответствующего i-того элемента из первой группы элементов И 125-1.125-N, выход которого соединен с первыми входами М триггеров соответствующей i-й группы из N групп по М триггеров 157-1-1. 157-1-М.157-N-1.157-N-М, второй вход каждого j-го триггера из которых подключен к выходу соответствующего j-го элемента соответствующей i-й группы из N групп по М элементов ИЛИ 156-1-1.156-1-М.156-N-1.156-N-М, первый и второй входы которого соединены с выходами соответствующих j-х элементов соответствующих i-х групп из первых и вторых N групп по М элементов И 151-1-1. 151-1-М.151-N-1.151-N-М и 155-1-1.155-1-М.155-N-1.155-N-М соответственно. Каждый j-й выход каждого i-го дешифратора из группы дешифраторов 153-1. 153- соединены с первым входом соответствующего j-го элемента соответствующей i-й группы из вторых N групп по М элементов И 155-1-1.155-1-М. 155-N-1.155-N-М. Каждый i-й вход из группы информационных входов 48-1.48-N блока соединен с первым информационным входом соответствующего i-го регистра памяти из группы блоков 115-1.115-N, регистровых памятей, второй информационный вход которого и вход соответствующего i-го дешифратора из группы дешифраторов 153-1.153-N соединены с выходом соответствующего i-го приоритетного шифратора из группы приоритетных шифраторов 120-1.120-N, вход которого подключен к выходу соответствующего i-го коммутатора из группы коммутаторов 119-1.119-N, управляющие входы которых соединены с управляющим входом первого коммутатора 117 и первым управляющим входом 50 блока.

Второй управляющий вход 51 блока соединен с управляющими входами группы регистров 116-1.116-N и управляющими входами группы блоков 115-1.115-N, группы блоков регистровых памятей, выход каждой i-й из которых соединен с соответствующим i-тым входом второго коммутатора 118, выход которого соединен с первым и вторым управляющими входами регистровой памяти 158, выход которой является вторым информационным выходом 66 блока. Первый информационный выход 65 блока соединен с выходом второго коммутатора 118. Первый информационный вход первого коммутатора 117 соединен с выходом приоритетного шифратора 114, а второй информационный вход и управляющий вход коммутатора 161 с выходом первого регистра 128. Выход коммутатора 161 соединен с информационным входом узла 145 обработки информации, а каждый i-й вход с выходом соответствующего i-го приоритетного шифратора из группы приоритетных шифраторов 120-1.120-N, каждый j-й вход которого и соответствующий j-й вход соответствующего i-го элемента второй группы элементов ИЛИ 159-1.159-N подключены к выходу соответствующего i-го триггера 157-N-1.157-N-М. Выход каждого i-го элемента второй группы элементов ИЛИ 159-1.159-N является соответствующим i-тым выходом из группы управляющих выходов 64-1.64-N блока, каждый i-й адресный вход из группы адресных входов 49-1.49-N которого соединен с входом соответствующего i-го регистра из группы регистров 116-1.116-N, выход которого соединен с входом соответствующего i-го коммутатора из группы коммутаторов 119-1.119-N, первыми входами М элементов соответствующей i-й первой группы из первых групп по М элементов И 151-1-1.151-1-М.151-N-1.151-N-М и входами соответствующего i-го элемента из первой группы элементов ИЛИ 152-1.152-N, выход которого соединен с первым входом соответствующего i-го элемента из второй группы элементов И 154-1.154-N. Выходы второй группы элементов И 154-1.154-N соединены с входом приоритетного шифратора 114, а вторые входы с третьим управляющим входом 52 блока. Адресный выход 67 блока соединен с входом блока 158 регистровой памяти и выходом первого счетчика 141, счетный вход которого подключен к первому выходу первого сдвигового регистра 137, второй и третий выходы которого соединены соответственно с первым управляющим выходом 59 блока и первым входом первого элемента ИЛИ 146. Первый вход второго элемента ИЛИ 147 является четвертым управляющим входом 53 блока, пятый управляющий вход 54 которого соединен с вторыми входами первой группы элементов И 125-1. 125-N и первыми входами третьего и четвертого элементов ИЛИ 148 и 149, выход первого из которых соединен с установочными входами первого и второго счетчиков 141 и 142, выход второго из которых соединен с первым управляющим входом блока 158 регистровой памяти. Шестой и седьмой управляющие входы блока соединены соответственно с вторыми входами элементов первых N групп по М элементов И 151-1-1.151-1-М.151-N-1.151-N-М и третьими входами элементов N групп по М элементов ИЛИ 156-1-1.156-1-М.156-N-1.156-N-М. Информационный выход узла 145 обработки информации соединен с информационными входами первого и второго регистров 126 и 127 и входом второго дешифратора 122, выход которого соединен с информационным входом третьего регистра 128, управляющий вход которого, вход второго сдвигового регистра 138 и управляющие входы первого и второго регистров 126 и 127 соединены с управляющим выходом узла 145 обработки информации, управляющий вход которого соединен с выходом второго элемента ИЛИ 147. Вход пятого элемента ИЛИ 150-1 соединен с входом приоритетного шифратора 114, а выход с входом первого элемента НЕ 143 и третьим управляющим выходом 61 блока, четвертый управляющий выход 62 которого соединен с выходом первого элемента И 129. Выход второго сдвигового регистра 138 соединен с первыми входами второго, третьего и первого элементов 130, 131 и И 129, вторые входы двух последних из которых подключены к первому и второму выходам соответственно, третьего регистра 128. Входы третьего и четвертого дешифраторов 123 и 124 подключены к выходам первого и второго счетчиков 141 и 142 соответственно, счетный вход последнего из которых соединен с первым выходом третьего сдвигового регистра 139, второй выход которого соединен с вторыми входами элементов вторых N групп по М элементов И 155-1-1. 155-1-М.155-N-1.155-N-М, вторым управляющим входом блока 158 регистровой памяти и управляющим входом второго регистра 127, выход которого соединен с входом второго элемента НЕ 144. Вход первого сдвигового регистра 137 подключен к выходу четвертого элемента И 132, первый и второй выходы которого соединены с первым выходом третьего дешифратора 123 и выходом первого элемента ИЛИ 146, соответственно второй вход последнего из которых и первый установочный вход триггера 140 соединены с первым выходом четвертого дешифратора 124. Второй установочный вход триггера 140 подключен к выходу шестого элемента ИЛИ 150-2, первый вход которого соединен с вторым выходом третьего дешифратора 123, а второй с вторым входом третьего элемента ИЛИ 148 и восьмым управляющим входом 57 блока. Второй вход второго элемента ИЛИ 147 подключен к выходу пятого элемента И 133, первый вход которого соединен с выходом второго элемента НЕ 144, а второй вход и первый вход шестого элемента И 134 с третьим выходом третьего сдвигового регистра 139, вход которого подключен к выходу седьмого элемента И 135, первый, второй и третий входы которого соединены с третьим выходом третьего регистра 128, первым управляющим входом 50 блока и выходом четвертого элемента ИЛИ 149 соответственно, второй и третий входы последнего из которых подключены к выходам шестого элемента ИЛИ 150-2 и второго элемента И 130 соответственно, второй вход последнего из которых соединен с выходом триггера 140. Третий вход второго элемента ИЛИ 147 подключен к выходу третьего элемента И 131, второй и третий входы шестого элемента И 134 соединены с вторым выходом четвертого дешифратора 124 и выходом второго регистра 127 соответственно. Пятый и второй управляющие выходы 63 и 60 блока соединены с выходом восьмого элемента И 136 и вторым выходом третьего дешифратора 123 соответственно, первый и второй входы первого из которых соединены с выходом первого элемента НЕ 143 и третьим управляющим входом 52 блока соответственно. Выход первого коммутатора 117 соединен с управляющим входом второго коммутатора 118.

Блок 20 ассоциативной буферной памяти содержит первый регистр 162, матрицу 163 ассоциативных запоминающих элементов, дешифратор 164, первую и вторую группы элементов И 165-1.165-М и 166-1.166-М, группу регистров 167-1. 167-М, группу элементов ИЛИ 168-1.168-М, регистр 169 сдвига, первый и второй элементы ИЛИ 170 и 171, с первого по четвертый элементы И 172.175 коммутатор 176, приоритетный шифратор 177, второй регистр 178, элемент НЕ 179, первый и второй триггеры 180 и 181.

Вторые управляющие вход 69 и выход 73 блока соединены с первыми входами каждого i-го элемента первой и второй групп элементов И 165-1.165-М и 166-1. 166-М соответственно, вторые входы которых подключены к соответствующему i-тому выходу дешифратора 164, вход которого соединен с адресным выходом 76 блока. Адресный вход 71 блока соединен с адресными входами первого регистра 162, прямые и инверсные информационные выходы которого соединены с соответствующими информационными входами матрицы 163 ассоциативных запоминающих элементов, каждый i-й управляющий вход которой и информационный вход соответствующего i-того триггера изгруппы триггеров 167-1.167-М соединены с выходом соответствующего i-того элемента из первой группы элементов И 165-1. 165-М. Каждый i-й выход матрицы 163 ассоциативных запоминающих элементов соединен с соответствующими i-тыми входом первого элемента ИЛИ 170 и первым информационным входом коммутатора 176, каждый i-й второй информационный вход которого подключен к выходу соответствующего i-го триггера из группы триггеров 167-1.167-М, управляющий вход которого подключен к выходу соответствующего i-го элемента из группы элементов ИЛИ 168-1,168-М, первый вход которого соединен с выходом соответствующего i-того элемента из второй группы элементов И 166-1.166-М. Выход первого элемента ИЛИ 170 соединен с первым входом первого элемента И 172 и входом элемента НЕ 179, выход которого соединен с первым входом второго элемента И 173. Вторые входы первого и второго элементов 172 и 173 И соединены с первым выходом регистра 169 сдвига, а выходы с первым и вторым соответственно управляющими входами коммутатора 176, которые соединены соответственно с первым и вторым входами второго элемента ИЛИ 171, которые соединены с первыми входами первого и второго триггеров 180 и 181, выходы которых являются первым и третьим управляющими выходами 72 и 74 блока. Вторые входы первого и второго триггеров 180 и 181, вход регистра 169 сдвига и управляющий вход первого регистра 162 соединены с первым управляющим входом 68 блока. Третий управляющий вход 70 блока соединен со вторым входом каждого i-го элемента из группы элементов ИЛИ 168-1. 168-М. Первый и второй входы третьего элемента И 174 соединены с первым управляющим выходом 72 блока и вторым выходом регистра 169 сдвига соответственно, а выход с вторым управляющим выходом 73 блока. Четвертый управляющий выход 75 блока соединен с выходом четвертого элемента И 175, каждый i-й вход которого соединен с соответствующими i-тыми вторыми информационными входами коммутатора 176, каждый i-й выход которого соединен с соответствующим i-тым выходом приоритетного шифратора 177, выход которого соединен с информационным входом второго регистра 178, управляющий вход которого подключен к выходу второго элемента ИЛИ 171, а выход к адресному выходу 176 блока.

Блок 21 выборки данных содержит первую и вторую группы усилительных элементов 182-1.182-N и 183-1.183-N, группу элементов ИЛИ 184-1.184-N, первую и вторую группы элементов И 185-1.185-N и 186-1.186-N, приоритетный шифратор 187, дешифратор 188 элемент И 189.

Второй управляющий вход 78 блока соединен с первыми входами первой группы элементов И 185-1.185-N, вторые входы которых подключены к соответствующим выходам дешифратора, вход которого соединен с выходом приоритетного шифратора 187, который является адресным выходом 82 блока. Управляющий выход 83 блока соединен с выходом элемента И 189, входы которого, соответствующие входы приоритетного шифратора 187 и первые входы соответствующих элементов второй группы элементов И 186-1.186-N соединены с соответствующими входами группы управляющих входов 79-1.79-N блока. Первый управляющий вход 77 блока соединен со вторыми входами второй группы элементов И 186-1.186-N, выходы которых подключены к первым входам соответствующих элементов группы элементов ИЛИ 184-1.184-N, выходы которых соединены со входами первой группы усилительных элементов 182-1.182-N, выходы которых являются первой группой управляющих выходы 80-1.80-N блока, вторая группа управляющих выходов 81-1. 81-N которого соединена с выходами соответствующих элементов второй группы усилительных элементов 183-1.183-N, входы которых и входы соответствующих элементов группы элементов ИЛИ 184-1.184-N соединены с выходами соответствующих элементов первой группы элементов И 185-1.185-N.

Блок 22 регистров (фиг. 7) содержит коммутатор 190, регистры 191-1.191-N и дешифратор 192. Входы регистров 191-1.191-N соединены с информационным входом блока 22, а выход коммутатора 190 является выходом блока 22.

Устройство работает следующим образом.

При подаче на первый управляющий вход 28 сигнала "Запрос" и поступлении входной информации с первого и второго информационных входов 26 и 27 на соответствующие входы первого и второго входных регистров 14 и 15 последние принимают информацию о разрядах кода ключа поиска и разрядах числа, для которого должна быть найдена соответствующая пара. В том случае, если необходимых данных не будет найдено, входная информация должна быть записана для хранения.

С выхода первого входного регистра 14 разряды кода ключа, определяющего условия поиска данных, поступают на входы вторых управляемых транспарантов 11-1.11-N, на первый информационный вход первого входного коммутатора 16 и на адресный вход 71 блока 20 ассоциативной буферной памяти. С выхода второго входного регистра 15 разряды числа передаются на первый информационный вход второго входного коммутатора 17 и на информационные входы блока 22 регистров и второго выходного регистра 25. Сигнал "Запрос" поступает также на первый управляющий вход 35-4 блока 18 управления и первый управляющий вход 68 блока 20 ассоциативной буферной памяти. При этом на каждой из вторых управляемых транспарантов 11-1.11-N и выходе коммутатора 16 устанавливается код, соответствующий входному ключу, а на выходе коммутатора 17 код, соответствующий значению входных данных (при этом сигнал управления на коммутаторах 16 и 17 имеет нулевое значение).

Одновременно по сигналу "Запрос" в блоке 18 управления производится установка второго триггера 106, и на управляющем выходе 38 блока формируется сигнал чтения (ЧТ), а на управляющих выходах 44 и 47 с задержкой во времени формируются соответственно сигналы ЧТ1 и ЧТ2.

При этом в блоке 21 выборки данных на первой группе управляющих выходов 80-1.80-N формируются сигналы УПРИ-1.УПРИ-управления источниками излучения 1-1. 1-N в соответствии со значением разрядов кода занятости реверсивных носителей информации 6-1.6-N, который поступает на группу управляющих входов 79-1. 79-N блока 21 выборки данных с группы управляющих выходов 64-1.64-N блока 19 преобразования массивов.

Световой поток от каждого i-го из выбранных таким образом источников излучения 1-1.1-N через последовательную цепь элементов блоков 2-i адресации луча, блоков 3-i формирования луча, транспарантов 4-i, блоков 5-i фокусировки луча, освещает выбранный носитель 6-i, в результате чего на i-ю матрицу 9-i через оптический блок 7-i и светоделительный элемент 8-i проецируется изображение содержимого области данных носителя 6-i.

При этом на матрицу 13-i проецируется результат пространственно-временной модуляции содержимого поля ключей носителя в соответствии с кодом входного ключа, поданного на вход каждого из транспарантов 11-1.11-N. В результате производится одновременный процесс сравнения кода входного ключа с соответствующим полем всех носителей 6-1.6-N.

Там, где произошло совпадение ключей, на соответствующей i-й матрице 13-i высвечивается признак, определяющий положение (адрес) соответствующих j-тых данных на носителе 6-i. Содержимое матриц 9-i и 13-i передается в блок 19 преобразования массивов соответственно на i-й блок 115-i регистровой памяти из группы и i-й регистр 116-i из группы, в результате чего на выходе i-го приоритетного шифратора 120-i из группы формируется код адреса, определяющий положение искомых данных в блоке 115-i регистровой памяти. Одновременно состояние выходных разрядов группы регистров 116-1.116-N передается на соответствующую группу элементов ИЛИ 152-1.152-N, с выхода которых сигнал поступает на первые входы соответствующих элементов И 154-1.154-N, на вторые входы которых поступает сигнал ЧТ1 с управляющего входа 52 блока 19. При этом выходы всех элементов И 154-1.154-N группы подключены на вход элемента ИЛИ 150-1, на выходе которого формируется сигнал СРОП, который используется для управления коммутатором 23 и поступает на управляющий выход 61 блока 19. Одновременно происходит модификация состояния j-го триггера 157-i-j, который соответствует положению искомых данных.

Модификация (в данном случае установка в "0") производится по сигналу ЧТ2 с шестого управляющего входа 55 блока 19 через i-ю группу элементов И 151-i-1.151.i-М и j-й элемент ИЛИ из i-й группы элементов 56-i-1.156-i-М.

Выборка данных осуществляется через коммутатор 23 и далее на первый выходной регистр 24. При этом на регистр 25 поступают входные данные с выхода регистра 15. Прием информации на регистры 24 и 25 производится по сигналу ПРРГ2 с пятого управляющего выхода 41 блока 18 управления. С выхода указанных регистров входные данные и данные, выбранные в соответствии со значением входного ключа, поступают на второй и первый информационные выходы 34 и 33 устройства.

В том случае, когда искомые данные на оптических носителях 6-1.6-N отсутствуют, на пятом управляющем выходе 63 блока 19 преобразования массивов формируется сигнал НСРОП, который поступает на восьмой управляющий вход 35-11 блока 18 управления. При этом дальнейшая работа устройства определяется наличием (отсутствием) искомых данных в блоке 20 ассоциативной буферной памяти. Как было указано выше, поиск информации в оптической и полупроводниковой частях устройства производится одновременно. При этом управляющие сигналы и информация, необходимая для поиска данных, поступают соответственно на входы 68 и 71 блока 20, после чего производится сравнение разрядов входного ключа с разрядами соответствующих ключей в ячейке матрицы 163.

В случае совпадения значений разрядов входного ключа (на регистре 162) и кода, хранящегося в j-й строке матрицы 163, на соответствующем j-ом входе элемента ИЛИ 170 и коммутатора 176 формируется сигнал признака сравнения, который с выхода элемента ИЛИ 170 поступает на первый вход элемента И 172 и вход элемента НЕ 179, причем на второй вход элемента И 172 поступает сигнал с первого выхода сдвигового регистра 189. При этом на выходе элемента И 172 формируется сигнал, который поступает на первый вход триггера 180, на первый вход элемента ИЛИ 171 и на первый управляющий вход коммутатора 176. При этом на выходе триггера 180 устанавливается сигнал логической "1", который поступает на первый вход элемента И 174 и первый управляющий выход 72 блока 20 в виде сигнала СРПП. При этом на второй вход элемента И 174 поступает сигнал с второго выхода сдвигового регистра 169. На выходе элемента И 174 формируется сигнал УПРЧТ управления чтением, который поступает на второй управляющий выход 73 блока 20 и на первые входы группы элементов И 166-1.166-М, на вторые входы которых поступает сигнал с соответствующего выхода дешифратора 164. При этом происходит сброс в нулевое состояние соответствующего триггера из группы триггеров 167-1.167-М (через соответствующий элемент ИЛИ из группы элементов 168-1.168-М ИЛИ). При этом код на входе дешифратора 164, соответствующий той ячейке матрицы 163, где произошло совпадение разрядов, формируется на выходе регистра 178, на вход которого он поступает от коммутатора 176 через приоритетный шифратор 177 (как было указано выше на вход коммутатора, при этом поступают результаты сравнения кодов во всех ячейках матрицы 163). Кроме того, разряды адреса с выхода регистра 178 поступают на адресный выход 76 блока 20, откуда они передаются на адресный вход блока регистров 2 и на вход 35-2 блока 18 управления. При этом в блоке 22 осуществляется передача на информационный выход содержимого регистра, номер которого совпадает с кодом адреса, поступившего из блока 20. Данные с информационного выхода блока 22 поступают на первый информационный вход коммутатора 23, причем при этой передаче код на первом разряде управляющего входа коммутатора 23 определяется сигналом СРПП с выхода 72 блока 29. Дальнейшая передача данных осуществляется аналогично рассмотренному выше случаю.

В том случае, когда сравнения ключей в ячейках матрицы 163 блока 20 не происходит, то формируется сигнал на выходе элемента И 173, который поступает на первый вход триггера 181, на второй управляющий вход коммут атора 176 и второй вход элемента ИЛИ 171. При этом на третьем управляющем выходе 74 блока 20 формируется сигнал НСРПП, а на выходе регистра 178 код адреса, соответствующий свободной ячейке матрицы 163, который поступает на вход дешифратора 164 и на адресный выход 76 блока 20. При этом, если сравнения кодов не происходит и в оптической части устройства, то сигнал НСРПП поступает на управляющий вход 35-14 блока 18 управления, где он объединяется на элементе И 91 с аналогичным сигналом НСРОП. При этом с выхода элемента И 91 сигнал поступает на третий вход элемента ИЛИ 97 для сброса в нулевое состояние триггера 106, на первый вход триггера 107, на вход регистра 110 сдвига, на второй вход элемента И 84 и на управляющий выход 42 блока 18 в виде сигнала УПРЗПП, который поступает на второй управляющий вход 69 блока 20 и первый управляющий вход блока 22 регистров. При этом в блоке 22 регистров производится запись входной информации с выхода регистра 15 в свободный регистр, определяемый адресом, поступающим из блока 20, а в блоке 20 запись разрядов кода входного ключа с выхода регистра 162 в ячейку матрицы 163, определяемую выходом дешифратора 164 (сигнал УПРЗПП поступает при этом на первые входы группы элементов И 165-1.165-М). Кроме того, в блоке 18 производится запись входной информации (разрядов ключа с информационного входа 35-16 и разрядов данных с информационного входа 35-17) в блок регистровой памяти из группы блоков 112-1.112-N. Причем выбор блока производится в соответствии с адресом на входе 35-3 блока 18, а выбор регистра внутри нее в соответствии с адресом на адресном входе 35-2.

Когда объем матрицы 163 блока 20 (и соответственно объем блока 22 и объем блока регистровой памяти из группы блоков 112-1.112-N в блоке 18) будет заполнен, на управляющем выходе 75 блока 20 формируется сигнал ПРПП, который поступает на вход 35-15 блока 18 управления. При этом происходит установка в единичное состояние триггера 108, а на выходе 46 формируется сигнал УПРЗПСТ, который поступает на управляющий вход 78 блока 21 выборки данных. Причем на i-ых выходах групп выходов 80-1.80-N и 81-1.81-N формируются соответственно сигналы управления i-м источником 1-i излучения и i-м носителем 6-i информации. При этом в блоке 18 управления в соответствии с адресом на адресном входе 35-3 выбирается i-й блок 112-i регистровой памяти, содержимое регистров которого подключается к соответствующим ячейкам i-го управляемого транспаранта 4-i. В результате световой поток от источника 1-i излучения создает в плоскости носителя 6-i информации изображение кода, отображенного на управляемом транспаранте 4-i, которое фиксируется в присутствии управляющего напряжения с выхода 81-i блока 21. При этом с задержкой на процесс записи в блоке 18 на выходе сдвигового регистра III вырабатывается сигнал КНЗПСТ, который через выход 46 блока 18 поступает на вход 54 блока 19 преобразования массивов. Одновременно с выхода 43 блока 18 управления на вход 70 блока 20 поступает сигнал СБРОС ПП. При этом в блоке 19 производится установка в единичное состояние группы триггеров 157-i (в соответствии с сигналом на выходе элементе И 125-i), а в блоке 20 производится установка в нулевое состояние группы триггеров 167-1.167-N, в результате чего блок 20 ассоциативной буферной памяти становится свободным для приема новой информации. Одновременно в блоке 19 производится установка в единичное состояние i-й группы триггеров 157-N-1.157-N-М, что соответствует переводу i-го носителя 6-i информации в число занятых.

В том случае, когда все носители 6-1.6-N группы будут заполнены, на выходе 83 блока 21 выборки данных формируется сигнал ПРОН переполнения оптических носителей, который поступает на вход 35-12 блока 18 управления, где производится установка в единичное состояние триггера 105, и на выходе 37 формируется сигнал ПРМ преобразования массивов. При этом происходит установка в единичное состояние триггера 106 и на выходе 38 блока 18 формируется сигнал ЧТ. По этому сигналу в блоке 19 преобразования массивов производится запись в группу блоков 115-1.115-N регистровых памятей информации с соответствующих носителей 6-1.6-N аналогично тому, как это производилось при запросе на поиск данных. Кроме того, на выходе 45 блока 18 управления формируется сигнал ЗАПМКР запуска узла 145 обработки информации, который поступает на вход 53 блока 19 преобразования массивов и далее через элемент ИЛИ 147 на управляющий вход узла 145 обработки информации. При этом последний производит реализацию заложенной в него программы по преобразованию размещения массивов информации на носителях 6-1.6-N. На первом этапе производится последовательное считывание через коммутатор 161 кода размера массивов, размещенных на каждом носителе к моменту переполнения устройства. Этот код формируется на выходе группы шифраторов 160-1.160-N. При этом на входы 1.М (по числу слов, размещаемых на каждом носителе) i-го шифратора 160-i группы поступают сигналы с выходов соотвтствующей i-ой группы триггеров 157-i-1.157-i-М, которые определяют загрузку i-го носителя 6-i. На информационном выходе узла 145 обработки информации при этом формируется последовательность кодов, соответствующих адресам (номерам) носителей 6-1.6-N (эти коды последовательно поступают на регистр 126), соответствующий режиму работы узла 145 обработки информации, который через дешифратор 122 поступает на регистр 128. Указанные кодовые группы сопровождаются сигналом прерывания на управляющем выходе узла 145 обработки информации, который поступает на управляющие входы регистров 126, 128 и на вход сдвигового регистра 138, сигнал с выхода которого поступает на вход элемента И 131, на второй вход которого поступает с первого выхода регистра 128 разряд кода режима работы узла 145 обработки информации. При этом на выходе элемента И 131 формируется сигнал прерывания, который поступает через элемент ИЛИ 147 на управляющий вход узла 145 обработки информации и сопровождает информацию о размерах массивов, поступающего на его информационный вход с выхода коммутатора 161, который в свою очередь управляется с выхода регистра 126, т.е. в соответствии с адресной информацией, формируемой узлом 145 обработки информации. Когда вся последовательность данных о размерах информации, хранящихся на оптических носителях 6-1.6-N будет принята, узел 145 обработки информации производит их сравнительную оценку и формирует очередь номеров (адресов) носителей 6-1.6-N, в соответствии с которой должны быть взаимно объединены их массивы информации с целью высвобождения полностью свободных носителей. При этом на вход регистра 126 поступает код, соответствующий адресу первого преобразуемого массива, на регистр 127 код, соответствующий его размеру, а на регистр 128 через дешифратор 122 код, соответствующий режиму преобразования массива. Сигнал прерывания управляющего выхода узла 145 обработки информации поступает на вход сдвигового регистра 138, а его выходной сигнал поступает через элементы И 130, ИЛИ 149 и И 135 на вход сдвигового регистра 139, с первого выхода которого сигнал поступает на счетный вход счетчика 142, который формирует адрес для размещения информации в блоке 158 регистровый памяти, которая выполняет роль промежуточного буфера. При этом на первый управляющий вход блока 158 регистровой памяти поступает сигнал управления записью со второго выхода сдвигового регистра 139, на третий управляющий вход поступает адрес с выхода счетчика 142, а на первый и второй информационные входы поступает информация (разряды ключа и разряды данных) с выхода коммутатора 118, которая представляет собой содержимое соответствующего блока регистровой памяти из группы блоков 115-1.115-N регистровых памятей. При этом управление коммутатором 118 производится разрядным кодом, поступающим на его управляющий вход с выхода коммутатора 117, который в свою очередь управляется сигналом ПРМ преобразования массивов, поступающим на его управляющий вход с входа 50 блока 19. При значении сигнала ПРМ, равном уровню логической "1", код на выходе коммутатора 117 будет соответствовать значению кода на выходе регистра 126 (таким образом реализуется передача в блок 158 регистровой памяти содержимого того из носителей 6-1.6-N, адрес которого был установлен узлом 145 обработки информации на регистре 126). При этом выборка очередного слова из выбранного блока памяти ( в группе блоков 115-1.115-N) производится в соответствии с кодом на выходе соответствующего приоритетного шифратора из группы шифраторов 120-1. 120-N, на вход которых через группу коммутаторов 119-1.119-N (управляемых сигналом ПРМ со входа 50 блока 19) поступает код, соответствующий состоянию триггеров занятости преобразуемого массива (из группы триггеров 157-1-1.157-1-М,157-N-1.157-N-М). При перезаписи очередного слова в блок 158 регистровой памяти происходит модификация кода массива на регистре 127 за счет подачи на его вход управления сдвигом сигнала с второго выхода сдвигового регистра 139. Одновременно производится модификация состояния соответствующей группы триггеров 157-1-1.157-1-М, 157-N-1.157-N-М по цепи: второй выход сдвигового регистра 139, входы группы элементов И 155-1-1. 155-N-М, входы группы элементов ИЛИ 156-1-1.156-N-M. Когда все содержимое выбранного блока регистровой памяти (из группы блоков 115-1.115-N) будет переписано в блок 158 регистровой памяти, код размера массива на выходе регистра 127 будет равен "0", в результате чего прекратится запуск счетчика 142 (на входе элемента И 134 будет нулевой уровень и произойдет очередной запуск узла 145 обработки информации по цепи через элементы И 133 и ИЛИ 147), в результате чего на его выходе установится информация для следующего преобразования, и процесс будет повторяться до тех пор, пока не будет заполнен блок 158 регистровой памяти. При этом на прямом выходе дешифратора 124 устанавливается единичный уровень, в результате чего производятся установка триггера 140 и одновременный запуск через элемент ИЛИ 147 и элемент И 132 сдвигового регистра 137, с первого выхода которого производится запуск счетчика 141. Выход последнего управляет выборкой информации из блока 158, а через выход 67 блока 19 преобразования массивов выход счетчика 141 подключается к входу 35-1 блока 18 управления, где через коммутатор 104 производится выбор адреса на размещение информации в блоке регистровой памяти из группы блоков 112-1.112-N. Причем выбор номера этого блока регистровой памяти производится в соответствии с адресом, поступающим на вход 35-3 блока 18, а управление записью в соответствии с сигналом на входе 35-7 блока 18, который формируется на втором выходе сдвигового регистра 137 блока 19 преобразования массивов. Когда процесс перезаписи будет закончен, на прямом выходе дешифратора 123 формируется уровень логической "1", в результате чего происходят установка в исходное положение триггера 140 и передача на выход 60 блока 19 сигнала ЗАППРСТ записи преобразованного массива, который поступает на вход 35-8 блока 18 управления. Запись массива на один из носителей 6-1.6-N производится согласно описанному ранее случаю записи при переполнении блока 20 ассоциативной буферной памяти. При этом сигнал КНЗПСТ окончания записи массива на соответствующий один из носителей 6-1.6-N с выхода 46 блока 18 поступает на вход 54 блока 19 преобразования массивов и производит очередной запуск счетчика 142 (через элемент ИЛИ 149, элемент И 135 и сдвиговой регистр 139), в результате чего начинается преобразование очередной группы массивов. Если записанный на носитель массив последний, то на выходе узла 145 обработки информации формируется код, который соответствует окончанию процесса преобразования массивов. Этот код через дешифратор 122 и регистр 128 поступает на первый вход элемента И 129, на второй вход которого поступает сигнал с выхода сдвигового регистра 138, в результате чего на выходе 62 блока 19 формируется сигнал КНПРМ конца преобразования, который поступает на вход 35-10 блока 18 управления. По этому сигналу производится установка в исходное состояние триггера 105 и устройство переходит в режим обработки входной информации.

Таким образом, введение дополнительных узлов позволяет производить одновременный ассоциативный поиск одиночного слова по всему объему информационных массивов, размещенных на оптических носителях, производить ассоциативный поиск одиночного слова в процессе подготовки к записи очередного массива данных и перегруппировку массивов, размещенных на оптических носителях, с целью высвобождения свободных мест для записи информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1994 |

|

RU2092891C1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| Устройство для автоматизированного контроля производственных процессов | 1977 |

|

SU734724A1 |

| Сбоеустойчивое микропрограммное устройство управления | 1982 |

|

SU1101823A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1998 |

|

RU2148857C1 |

| Устройство для моделирования маршрутов сообщений и управления процессом коммутации в сети связи | 1980 |

|

SU922757A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| АККОРДНЫЙ ШИФРАТОР | 1990 |

|

RU2022465C1 |

Изобретение относится к вычислительной технике. Оптическое оперативное запоминающее устройство содержит последовательно расположенные и оптически связанные основные и дополнительные источники излучения, блоки адресации луча, первые блоки формирования луча, первые управляемые транспаранты, первые блоки фокусировки луча, реверсивные носители информации, оптические блоки считывания, светоделительные элементы, первые матрицы фотоприемников, вторые блоки формирования луча, вторые управляемые транспаранты, вторые блоки фокусировки луча, вторые матрицы фотоприемников. Кроме того, устройство содержит первый и второй входные регистры, первый и второй входные коммутаторы, блок управления, блок преобразования массивов, блок ассоциативной буферной памяти, блок выборки данных, блок регистров, выходной коммутатор, первый и второй входные регистры. 3 з.п. ф-лы, 7 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Оптическое оперативное запоминающее устройство | 1977 |

|

SU701346A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-05-10—Публикация

1992-12-25—Подача