Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации при реализации технических средств цифровых вычислительных машин и дискретной автоматики.

Известно суммирующее устройство [1] выполняющее сложение m чисел, содержащее ассоциативный запоминающий блок, первую и вторую группы элементов И, первую и вторую группы элементов задержки, первый и второй преобразователи двоичного кода в уплотненный код и блок деления на два в уплотненном коде, причем входы первого преобразователя двоичного кода в уплотненный код соединены со входами слагаемых устройства, первые входы элементов И первой группы соединены с первым входом синхронизации устройства, вторые входы с соответствующими выходами первого преобразователя двоичного кода в уплотненный код, а выходы ко входам блока деления на два в уплотненном коде, выход первого разряда ассоциативного запоминающего блока соединен с выходом результата устройства, а выходы остальных разрядов со входами элементов задержки первой группы, выходы целой части результата блока деления на два в уплотненном коде соединены со входами элементов задержки второй группы, выходы элементов задержки первой и второй групп и выход остатка блока деления на два в уплотненном коде соединены со входами второго преобразователя двоичного кода в уплотненный код, первый входы элементов И второй группы соединены со вторым входом синхронизации устройства, вторые входы с соответствующими выходами второго преобразователя двоичного кода в уплотненный код, а выходы со входами ассоциативного запоминающего блока, при этом блок деления на два в уплотненном коде содержит группу элементов И, группу элементов ЗАПРЕТ и элемент ИЛИ, выход которого является выходом остатка блока, а входы подключены к выходам элементов ЗАПРЕТ группы, информационные входы которых соединены с первыми входами соответствующих элементов И группы блока и подключены к соответствующим нечетным входам блока, управляющие входы элементов ЗАПРЕТ группы блока соединены со вторыми входами соответствующих элементов И группы блока и подключены к соответствующим четным входам блока, выходы элементов И группы блока являются выходами целой части результата блока.

Недостаткам этого устройства является время, требующееся для сложения чисел, равное t=n+log(m), где n разрядность складываемых чисел, m - количество складываемых чисел.

Наиболее близким по технической сущности к предлагаемому решению является суммирующее устройство [2] содержащее преобразователь двоичного кода в уплотненный код, группу элементов И, блок деления на два в уплотненном коде, группу элементов задержки. Блок деления на два в уплотненном коде состоит из группы элементов И, группы элементов ЗАПРЕТ, элементов ИЛИ. Устройство имеет входы слагаемых, вход синхронизации, выход суммы. Первая группа входов преобразователя двоичного кода в уплотненный код соединена с входами устройства. Первые входы элементов И соединены с входом синхронизации, а вторые входы с соответствующими выходами преобразователя двоичного кода в уплотненный код. Выходы элементов И соединены с соответствующими входами блока деления на два в уплотненном коде. В блоке деления на два в уплотненном коде выход элемента ИЛИ является выходом остатка блока и соединен с выходом устройства, входы элемента ИЛИ соединены с выходами соответствующих элементов ЗАПРЕТ, выходы элементов И соединены с входами соответствующих элементов задержки, информационные входы элементов ЗАПРЕТ соединены с первыми входами соответствующих элементов И и подключены к соответствующим нечетным входам блока деления на два в уплотненном коде, управляющие входы элементов ЗАПРЕТ соединены со вторыми входами соответствующих элементов И и подключены к соответствующим четным входам блока деления на два в уплотненном коде.

Недостатком этого устройства является большое количество тактов, требующихся для выработки суммы, равное t=n+log(m)+1, где n разрядность складываемых чисел, m количество складываемых чисел.

Цель изобретения увеличение быстродействия устройства.

Поставленная цель достигается тем, что дополнительно вводится шифратор и группа элементов ЗАПРЕТ, которые позволяют после подачи на шифратор старших разрядов складываемых кодов получить результат непосредственно путем преобразования позиционного кода в соответствующий двоичный код.

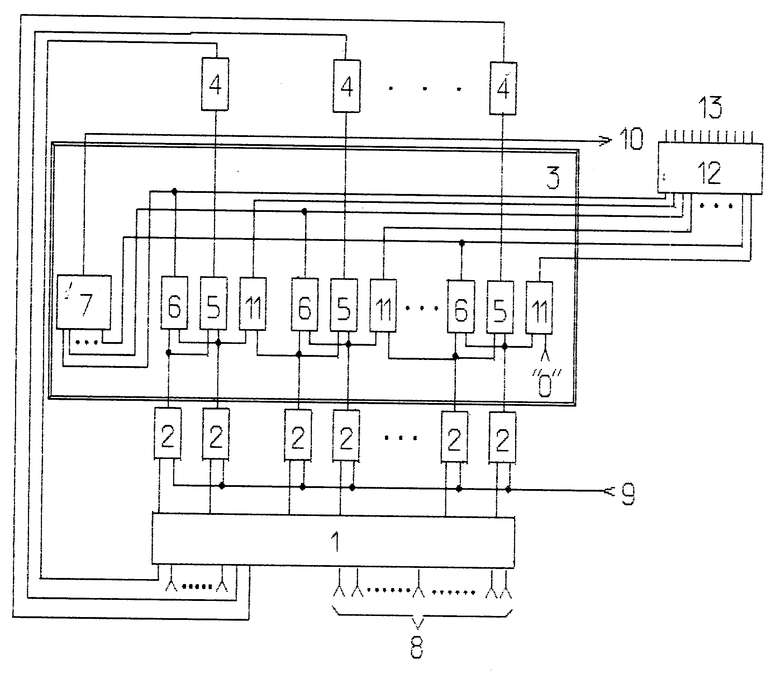

На чертеже представлена структурная схема суммирующего устройства.

Устройство содержит преобразователь 1 двоичного кода в уплотненный код, группу элементов И 2, блок 3 деления на два в уплотненном коде и выдачи позиционного кода, группу элементов 4 задержки, шифратор 12. Блок 3 деления на два в уплотненном коде и выдачи позиционного кода состоит из группы элементов И 5, группы элементов ЗАПРЕТ 6, элемента ИЛИ 7 и дополнительной группы элементов ЗАПРЕТ 11. Устройство имеет входы 8 слагаемых, вход 9 синхронизации, последовательный выход 10 младших разрядов суммы и параллельный выход 13 старших разрядов суммы. Первая группа входов преобразователя 1 двоичного кода в уплотненный код соединена с входами 8 устройства. Первые входы элементов И 2 соединены с входом синхронизации, а вторые входы с соответствующими выходами преобразователя 1 двоичного кода в уплотненный код. Выходы элементов И 2 соединены с соответствующими входами блока 3 деления на два в уплотненном коде и выдачи позиционного кода. В блоке 3 деления на два в уплотненном коде и выдачи позиционного кода выход элемента ИЛИ 7 является выходом остатка блока 3 и соединен с выходом 10 младших разрядов суммы устройства, входы элемента ИЛИ 7 соединены с выходами соответствующих элементов ЗАПРЕТ 6 и с нечетными выходами выдачи позиционного кода блока 3, выхода элементов И 5 соединены с входами соответствующих элементов 4 задержки, выходы которых соединены со второй группой входов преобразователя двоичного кода в уплотненный код, информационные входы элементов ЗАПРЕТ 6 соединены с первыми входами соответствующих элементов И 5 и, начиная со второго элемента ЗАПРЕТ 6, с управляющими входами соответствующих элементов ЗАПРЕТ 11 и подключены к соответствующим нечетным входам блока 3, управляющие входы элементов ЗАПРЕТ 6 соединены со вторыми входами соответствующих элементов И 5 и с информационными входами соответствующих элементов ЗАПРЕТ 11 и подключены к соответствующим четным входам блока 3, на управляющий вход последнего элемента группы ЗАПРЕТ 11 подается постоянно нулевой сигнал, выходы соответствующих элементов ЗАПРЕТ 11 соединены с четными выходами выдачи позиционного кода блока 3. Выходы позиционного кода блока 3 соединены со входами шифратора 12, выходы которого являются выходами 13 старших разрядов суммы.

Устройство работает следующим образом. На входы 8 поступают одноименные разряды всех слагаемых, начиная с младших разрядов. Преобразователь 1 преобразует поступающий на его входы двоичный код в уплотненный код, который через элементы И 2 поступает на входы блока 3 деления на две в уплотненном коде и выдачи позиционного кода в течение тактового импульса по входу 9. Полученное частное через элементы задержки 4 поступает на вторую группу входов преобразователя 1 двоичного кода в уплотненный код вместе со следующими разрядами поступающих слагаемых. На выходе 10 формируется очередной разряд суммы. Общее число тактов вычисления суммы равно t=n, где n разрядность слагаемых.

Пусть необходимо просуммировать следующие семь слагаемых 010110; 101011; 011011; 111111; 101110; 110011; 101010. Обрабатываемые срезы на входах 8 имеют вид 0111010; 1111111; 1001100; 0111101; 1011010; 0101111. На входе преобразователя 1 образуемые срезы имеют вид 1111000; 1111111; 1110000; 1111100; 1111000; 11111100. В течение первого тактового импульса, поданного на вход 9 синхронизации, на вход блока 3 деления на два в уплотненном коде и выдачи позиционного кода подаются младшие разряды слагаемых, т.е. 1111000. В результате преобразования этого кода блоком 3 порождается частное 1100, которое через элементы 4 задержки поступает на вторую группу входов преобразователя 1, а остаток, равный "0", без задержки подается на выход 10. В течение второго импульса, поданного на вход 9 синхронизации, на входе преобразователя 1 оказывается код, равный 11001111111, составленный из частного 1100 и второго разрядного среза слагаемых, т.е. кода 1111111. Он преобразуется в код 11111111100, который, поступив на вход блока 3 деления на два и выдачи позиционного кода, преобразуется в частное, равное 111100. И остаток, равный "1", поступает на выход 10, формируя второй разряд искомой суммы. В течение третьего импульса, данного на вход 9 синхронизации, на вход преобразователя 1 подается составной срез из полученного частного и третьего обрабатываемого среза 1111001001100. Преобразователь кода в уплотненный код преобразовывает его в слово 1111111000000, которое поступает на вход блока 3 деления на два в уплотненном коде и выдачи позиционного кода, соответственно на выходе блока -1110000, остаток которого "1" является третьим разрядом искомой суммы.

Аналогичным образом предлагаемое устройство продолжает работу до получения пятого разряда суммы. При подаче шестого, последнего разряда суммы на вход блока деления на два в уплотненном коде и выдачи позиционного кода поступает слово 11111111100000, а на выходах выдачи позиционного кода слово 00000000100000, которое порождает на выходах шифратора 12 код 1001, соответствующий номеру позиции 9. Таким образом, результативный код суммы составляется из последнего полученного на пяти тактах кода 00110 и параллельного кода 1001, что дает код 100100110.

Следовательно, предлагаемое устройство реализует ту же функцию, что и прототип, но результат достигается за меньшее число тактов.

Существенными отличиями заявляемого устройства от имеющихся аналогов являются: введение дополнительных элементов, позволяющее получать сумму в результате клейки младших разрядов суммы, получаемых последовательным способом, и старших разрядов суммы, получаемых параллельным способом.

Технико-экономический эффект предлагаемого устройства заключается в том, что достигается ускорение работы устройства более чем на log(m) тактов, где m число операндов.

Список литературы:

1. Авторское свидетельство СССР N 1495784, кл. G 06 F 7/50, 1987.

2. Авторское свидетельство СССР n 1591004, G 06 F 7/50, 1990.

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1987 |

|

SU1495784A1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОД - ЧАСТОТА | 1995 |

|

RU2092973C1 |

| АККОРДНЫЙ ШИФРАТОР | 1990 |

|

RU2022465C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ | 1990 |

|

RU2022466C1 |

| Суммирующее устройство | 1990 |

|

SU1714591A1 |

| Двоичный шифратор | 1989 |

|

SU1755273A1 |

| ОПТИЧЕСКОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2035069C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Многофункциональное ассоциативное запоминающее устройство | 1984 |

|

SU1191942A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах обработки информации при реализации технических средств. Цель изобретения - увеличение быстродействия устройства. Устройство содержит преобразователь 1 двоичного кода в уплотненный код, группу элементов И 2, блок 3 деления на два в уплотненном коде и выдачи позиционного кода, группу элементов задержки 4, шифратор 12. На выходе устройства 10 формируется очередной разряд суммы. Общее число тактов вычисления суммы равно n, где n - разрядность слагаемых. 1 ил.

Суммирующее устройство, содержащее преобразователь двоичного кода в уплотненный код, группу элементов И, группу элементов задержки, блок деления на два в уплотненном коде, состоящий из группы элементов И, группы элементов ЗАПРЕТ, элемента ИЛИ, при этом первая группа входов преобразователя двоичного кода в уплотненный код соединена с входами слагаемых устройства, первые входы элементов И группы подключены к входу синхронизации устройства, вторые входы к выходам преобразователя двоичного кода в уплотненный код, а выходы к входам блока деления на два в уплотненном коде, выходы группы элементов И блока деления на два в уплотненном коде соединены с входами элементов задержки группы, выходы которых соединены с второй группой входов преобразователя двоичного кода в уплотненный код, выход элемента ИЛИ соединен с выходом младших разрядов суммы устройства, входы элемента ИЛИ соединены с выходами соответствующих элементов ЗАПРЕТ группы, информационные входы элементов ЗАПРЕТ группы соединены с первыми входами соответствующих элементов И группы блока деления на два в уплотненном коде, управляющие входы элементов ЗАПРЕТ группы соединены с вторыми входами соответствующих элементов И группы блока деления на два в уплотненном коде, отличающееся тем, что оно содержит шифратор и дополнительную группу элементов ЗАПРЕТ, при этом информационные входы элементов ЗАПРЕТ дополнительной группы подключены к четным входам блока деления на два в уплотненном коде, а управляющие к нечетным входам блока деления на два в уплотненном коде, начиная с третьего, управляющий вход последнего элемента ЗАПРЕТ дополнительной группы подключен к входу логического нуля устройства, нечетные входы шифратора подключены к выходам элементов ЗАПРЕТ группы, четные входы шифратора подключены к выходам элементов 3AПPET дополнительной группы, выходы шифратора являются выходами старших разрядов суммы устройства.

| SU, авторское свидетельство N 1495784, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидеельство N 1591004, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-10-10—Публикация

1994-10-27—Подача