хронизации, а выход регистра адреса перезапуска соединен с вторым информационным входом блока адресации, шестой выход блока синхронизации соединен с входом третьего триггера, единичный выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента Икс пятым входом блока обработки прерываний, шестой вход которого соединен с выходом элемента ИЛИ, выход генератора импульсов максимальной длительности соединен с первым входом элемента К, второй вход которого соединен с выходом второго триггера.

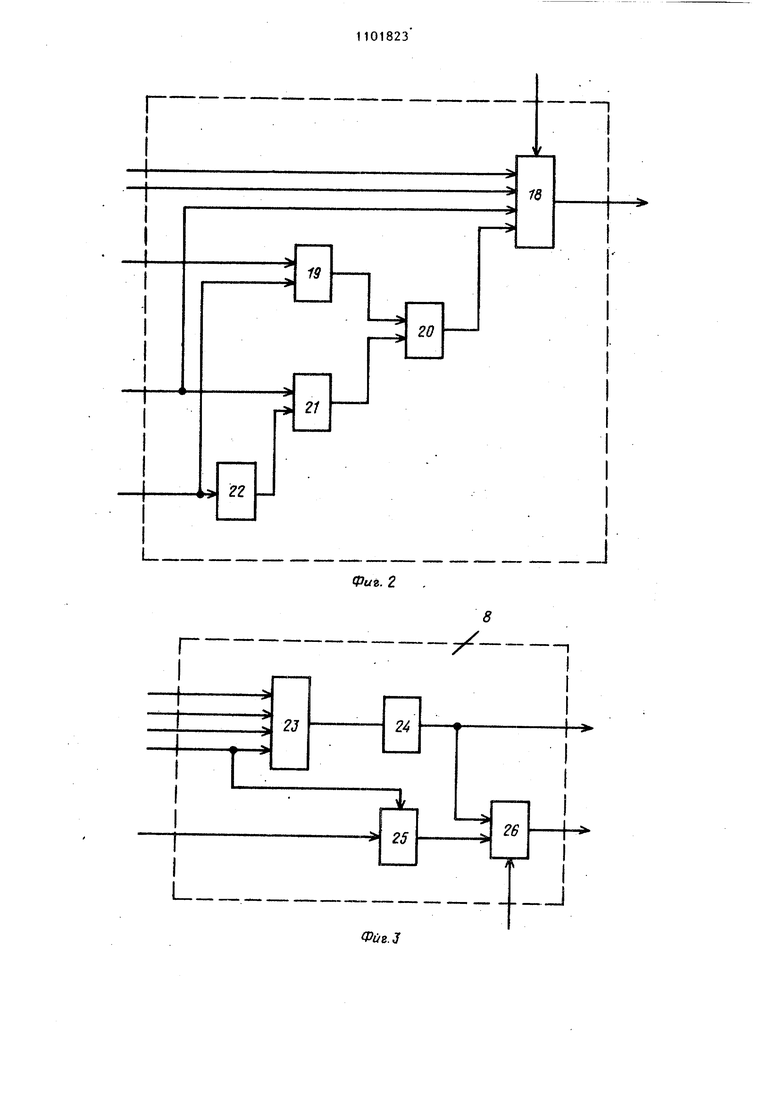

2. Устройство по П.1, отличающееся тем, что блок обработки

прерываний содержит первый, второй регистры, шифратор и схему сравнения, первый и второй информационные входы которой соединены соответственно с выходами шифратора и первог регистра, управляющий вход схемы сравнения соединен с шестым входом блока, а выход - с вторым выходом блока, управляющие входы первого и второго регистров соединены с четвертым входом блока, информационный вход первого регистра соединен с первым входом блока, второй, трет и пятый входы блока объединены и пoдкJDOчeны к информационному входу второго регистра, выход которого соединен с взсодом шифратора, выход которого подключен к первому выходу блока..

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропрограммное устройство управления и отладки микропрограмм процессора | 1984 |

|

SU1168937A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Микропроцессор для управления памятью микрокоманд | 1979 |

|

SU803700A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1354192A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

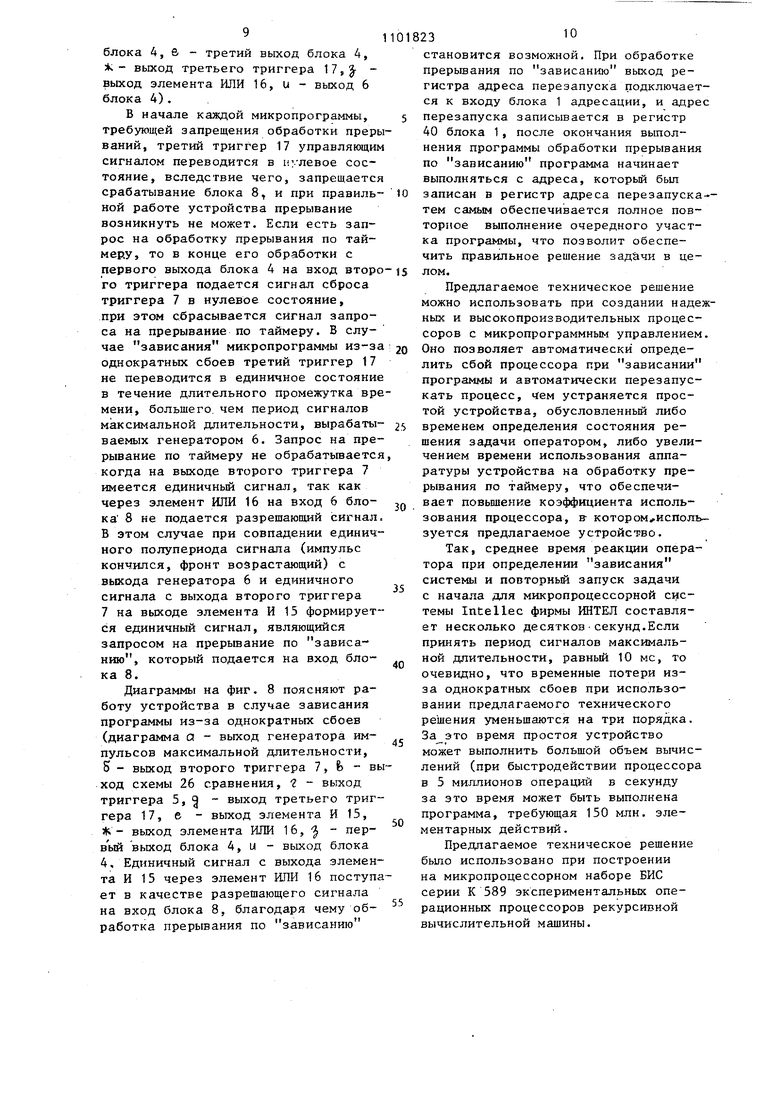

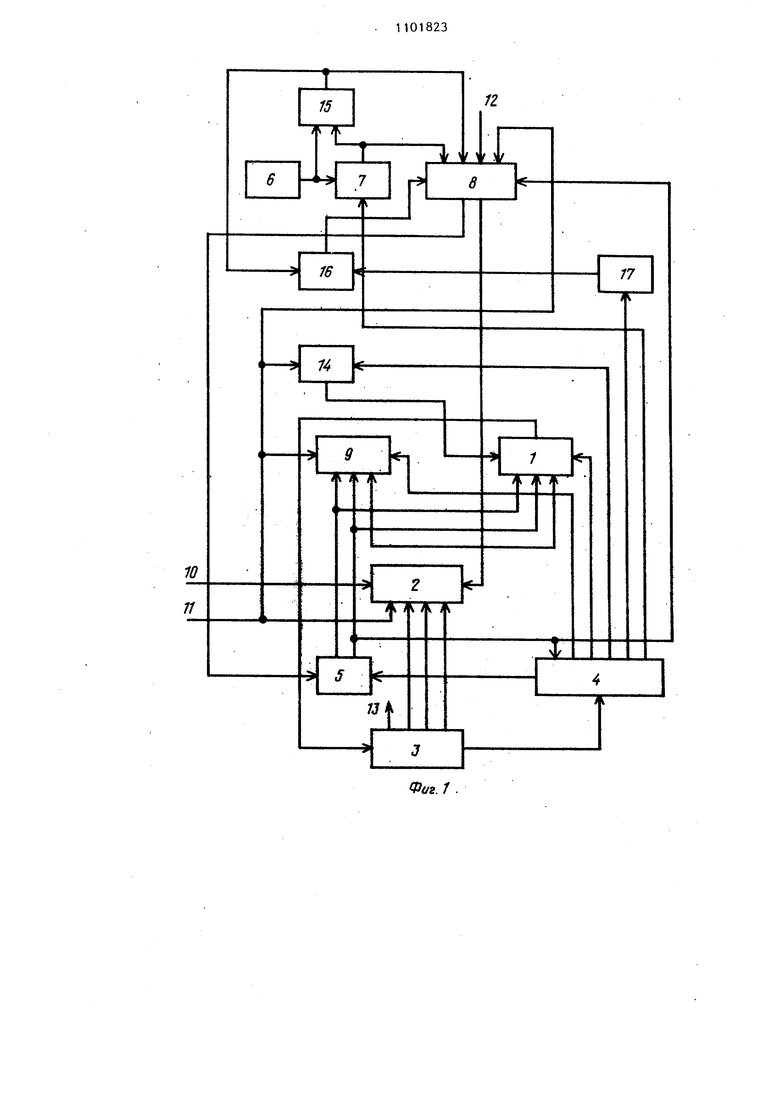

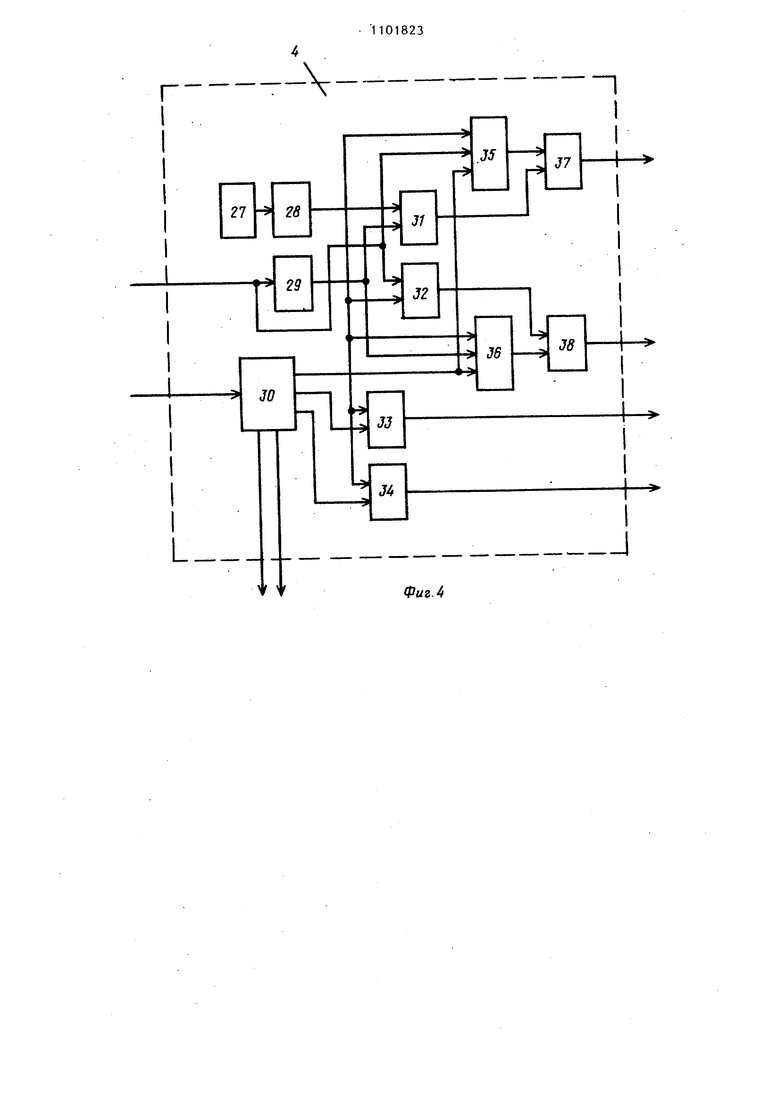

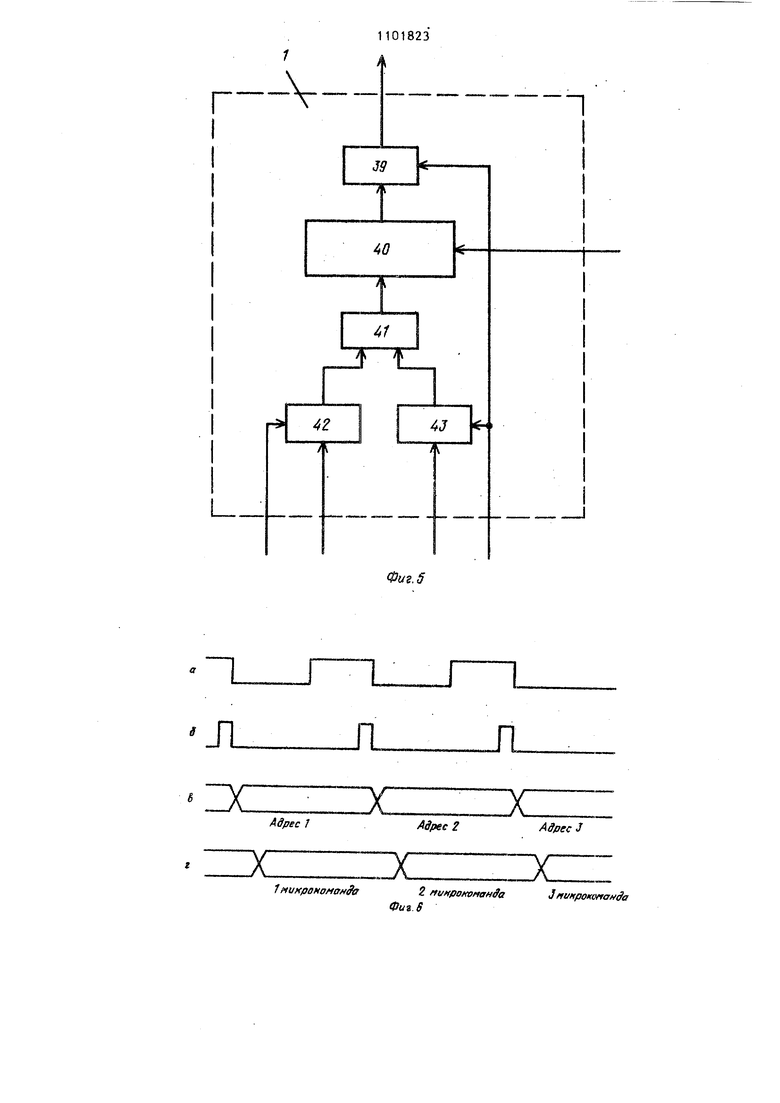

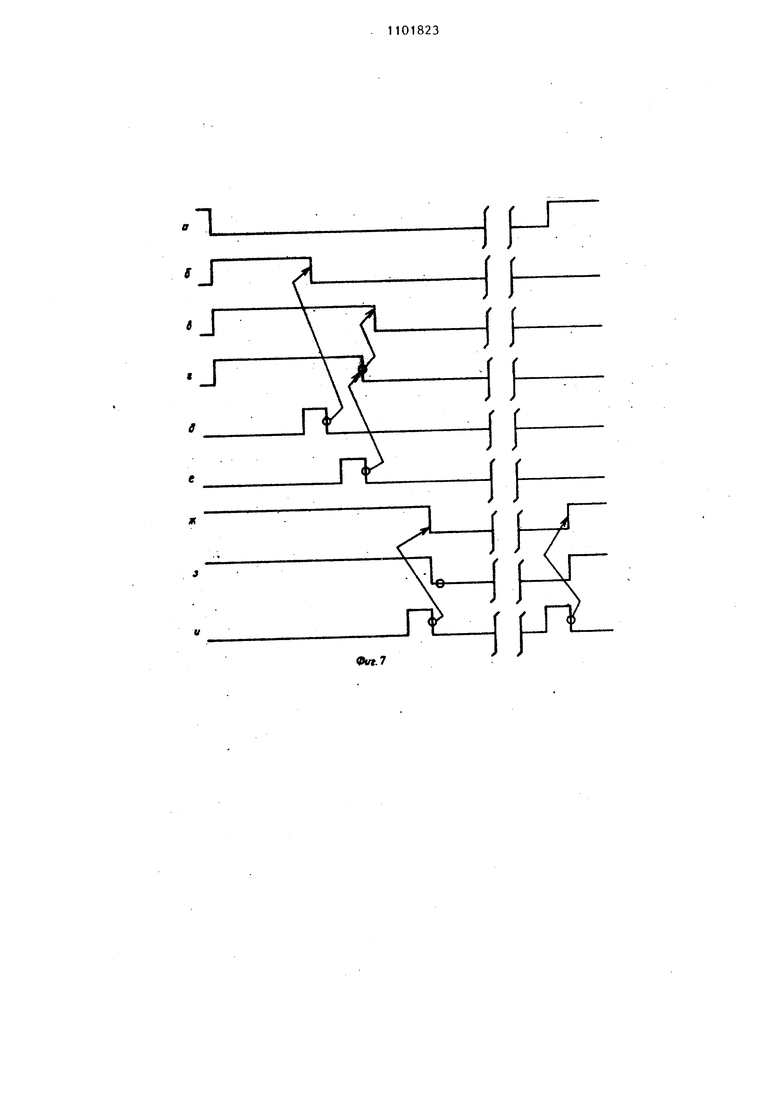

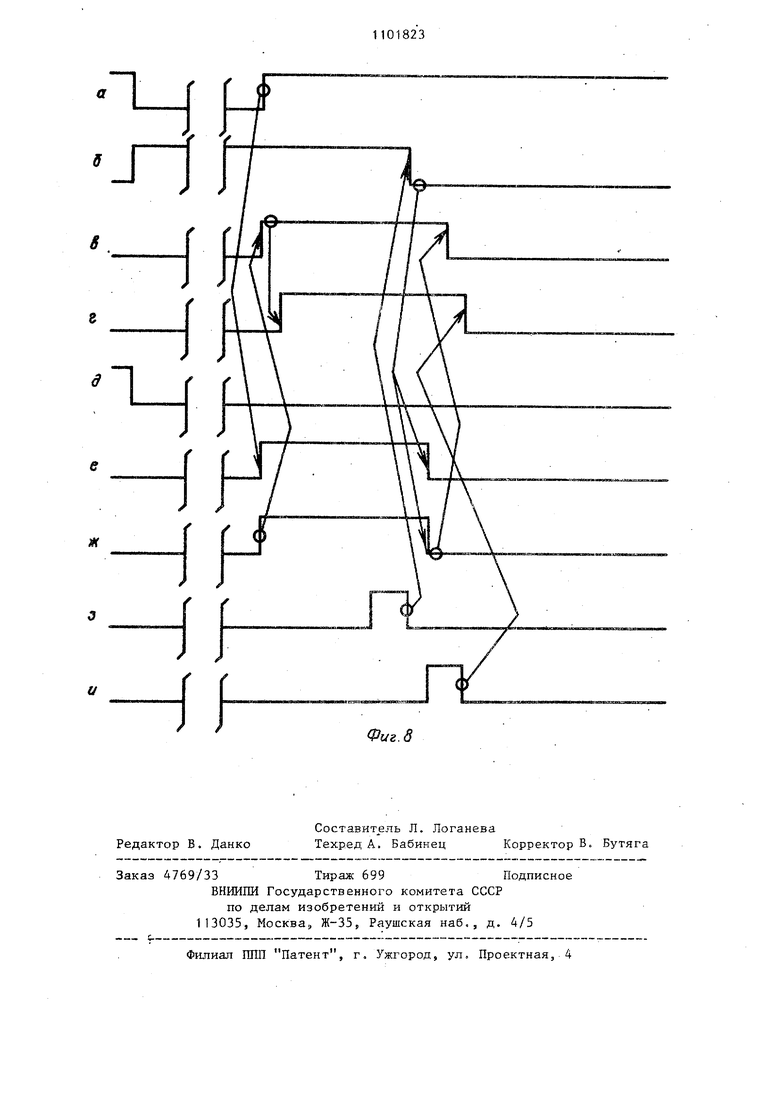

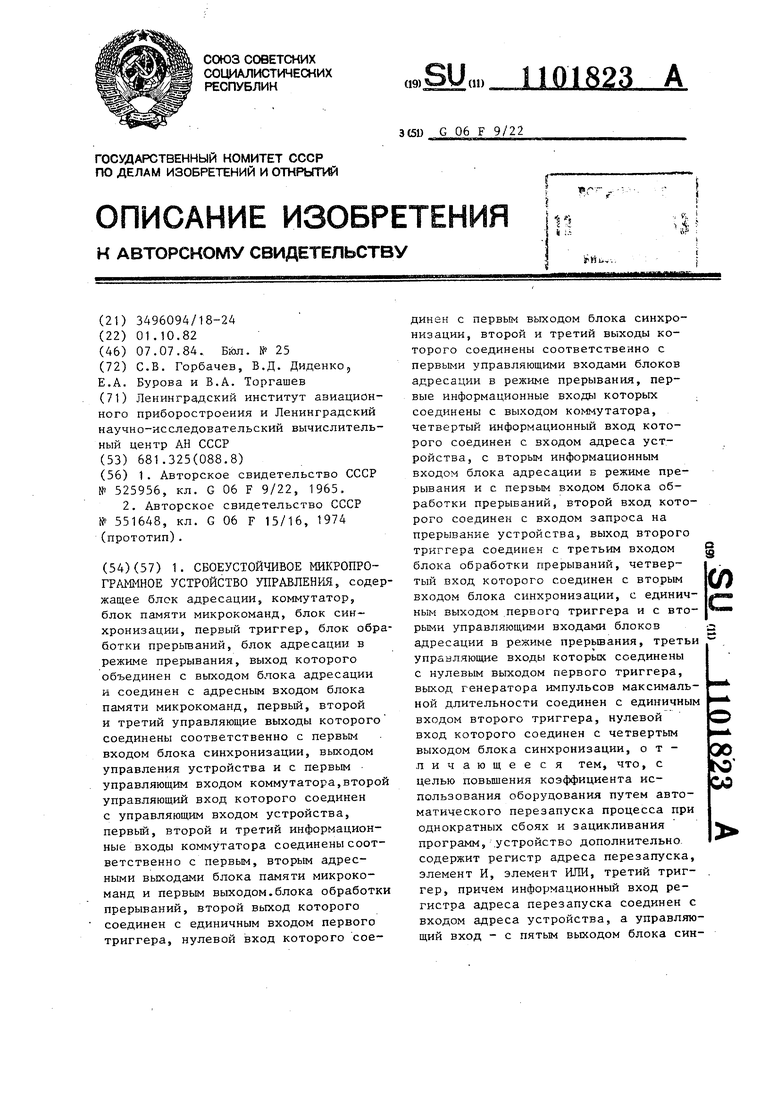

1. СБОЕУСТОЙЧИВОЕ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок адресации, коммутатор, блок памяти микрокоманд, блок синхронизации, первый триггер, блок обработки прерьгеаний, блок адресации в режиме прерывания, выход которого объединен с выходом блока адресации и соединен с адресным входом блока памяти микрокоманд, первый, второй и третий управляющие выходы которого соединены соответственно с первым входом блока синхронизации, выходом управления устройства и с первым управляющим входом коммутатора,второй управляющий вход которого соединен с управляющим входом устройства, первьй, второй и третий информационные входы коммутатора соединены соответственно с первым, вторь м адресными выходами блока памяти микрокоманд и первым выходом.блока обработки прерываний, второй выход которого соединен с единичным входом первого триггера, нулевой вход которого соединен с первым выходом блока синхронизации, второй и третий выходы которого соединены соответственно с первыми управляющими входами блоков адресации в режиме прерывания, первые информационные входы которых , соединены с выходом коммутатора, четвертый информационный вход которого соединен с входом адреса устройства, с вторым информационным входом блока адресации в режиме прерывания и с первым входом блока обработки прерываний, второй вход которого соединен с входом запроса на прерыван 1е устройства, выход второго триггера соединен с третьим входом блока обработки прерываний, четвер(Л тый вход которого соединен с вторым входом блока синхронизации, с единичным выходом первого триггера и с вторыми управляющими входами блоков адресации в режиме прерьшания, третьи управляющие входы которых соединены с нулевьм вьпходом первого триггера, выход генератора импульсов максимальной длительности соединен с единичным входом второго триггера, нулевой вход которого соединен с четвертым выходом блока синхронизации, отличающее ся тем, что, с целью повышения коэффициента использования оборудования путем автоматического перезапуска процесса при однократных сбоях и зацикливания программ, .устройство дополнительно, содержит регистр адреса перезапуска, элемент И, элемент ШШ, третий триггер, причем информационный вход регистра адреса перезапуска соединен с входом адреса устройства, а управляющий вход - с пятым выходом блока син

Изобретение относится к вычислительной технике и может найти применение при создании микропрограммируеМых специализированных и универсальных высокопроизводительных цифровых вычислительных машин, а именно устройств управления работой процессоров с микропрограммной реализацией.

Известно микропрограммное устройство управления, которое предусматривает вхождение в режим прерывания при обнаружении зависания вычислительного процесса lj

Однако существующие методы обнарушения и вхождения в режим прерывания существенно снижают коэффициент использования оборудования и, в конечном итоге, увеличивают время прохождения задачи.

г

Наиболее близким к изобретению является устройство, содержащее блок адресации, коммутатор, блок хранения микрокоманд, блок управления и Синхронизации, первый триггер, генератор импульсов максимальной длительности, второй триггер, блок обработки прерываний, блок адресации в режиме прерывания, шину управления выбором прямого и альтернативного адреса, шину начальной установки, шину внешних запросов на прерывания,

шину управления элементами процессора, причем выход блока адресации подключен к выходу блока адресации в режиме прерывания и к входу блока хранения микрокоманд, второй и пятый входы которого соединены соответственно с шиной управления элементами процессора и с шестым входом коммутатора, четвертый вход которого

подключен к третьему выходу блока хранения микрокоманд, первый и четвертый выходы которого соединены соответственно с первым входом блока управления и синхронизации и пятым

входом коммутатора, первый и второй входы которого подключены соответственно к шине управления выбором прямого и альтернативного адреса и первым выходом блока обработки прерываНИИ, третий вход которого соединен

с вторым входом управления и синхронизации, с третьим входом блока адресации, с четвертым входом блока адресации в режиме прерывания и с первым выходом первого триггера, второй и первый входы которого подключены к третьему выходу блока управления и синхронизации и второму выходу блока обработки прерываний, четвертый

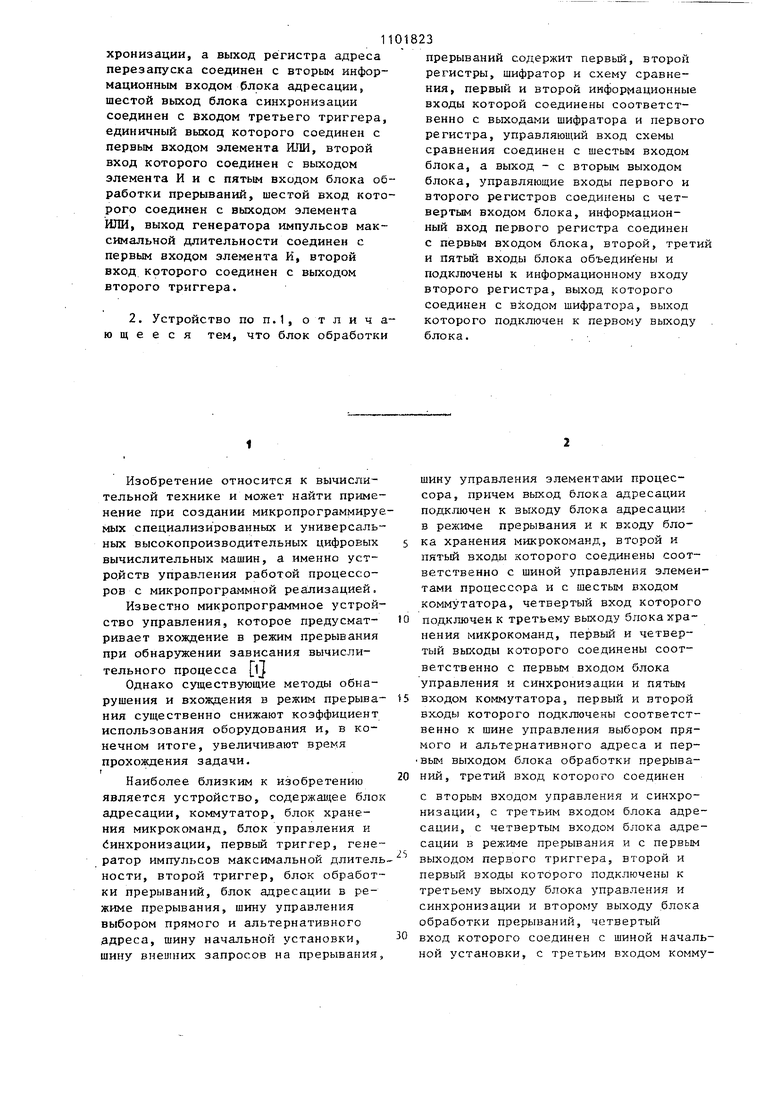

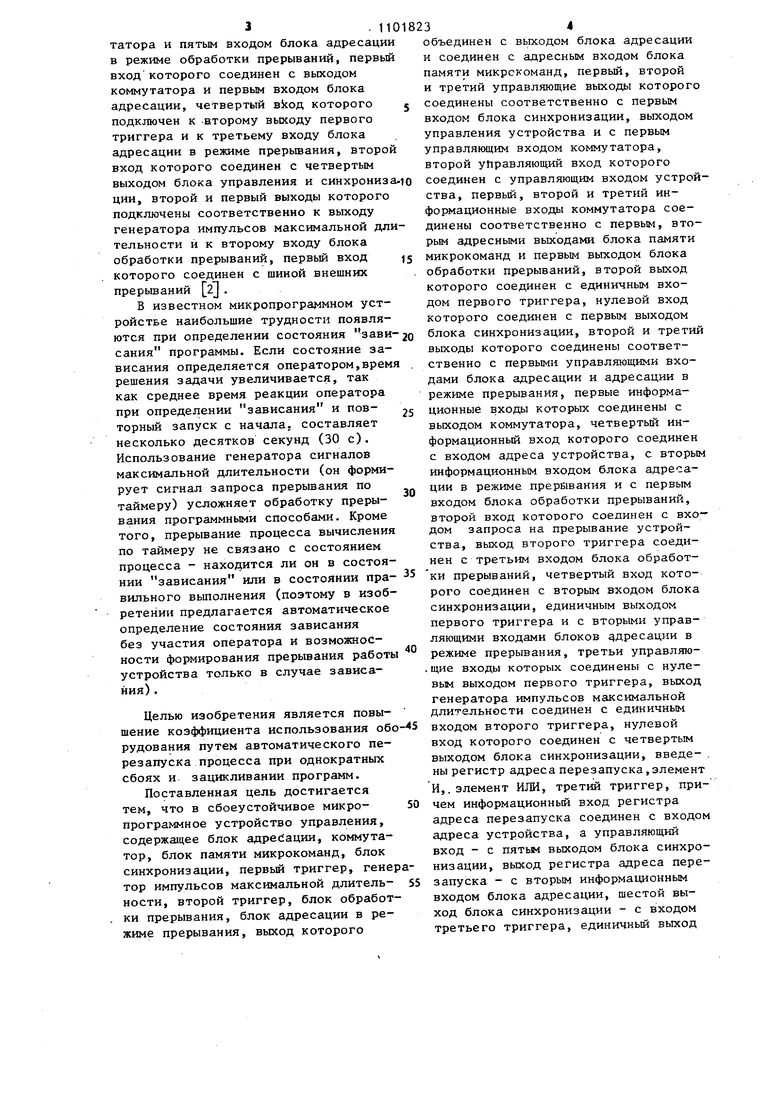

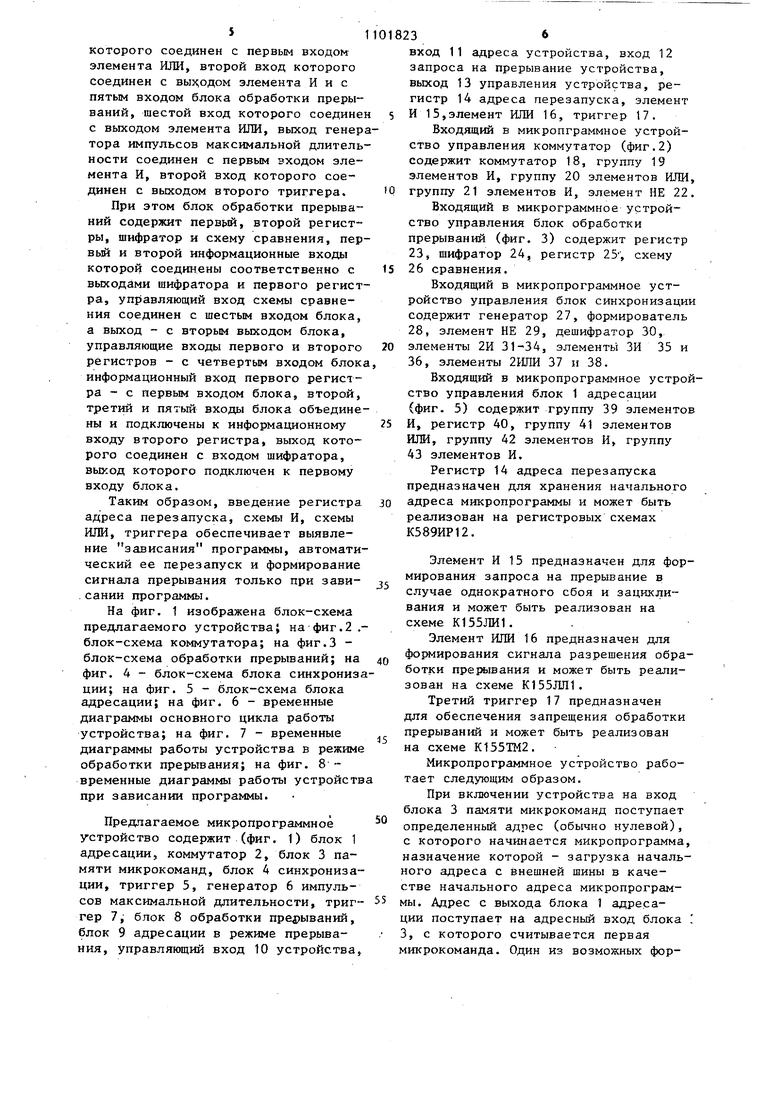

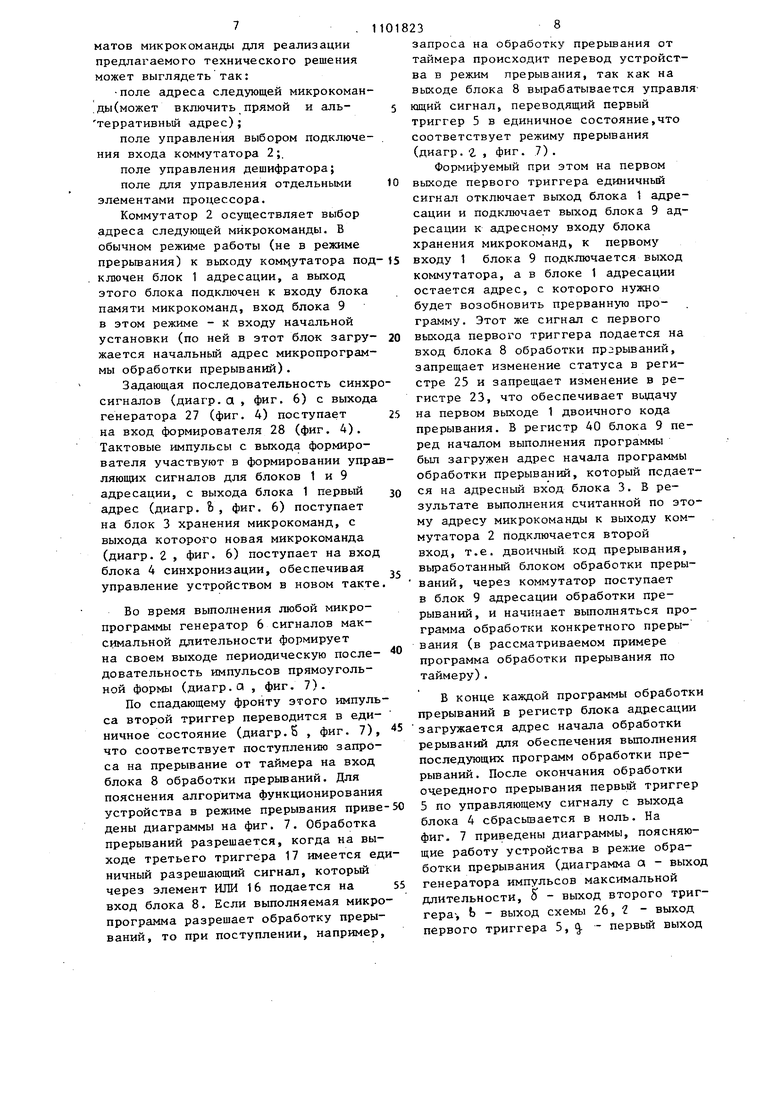

вход которого соединен с шиной начальной установки, с третьим входом коммутатора и пятым входом блока адресаци в режиме обработки прерываний, первы входкоторого соединен с выходом коммутатора и первым входом блока адресации, четвертый вkoд которого подключен к -второму вьгходу первого триггера и к третьему входу блока адресации в режиме прерьшания, второ вход которого соединен с четвертым выходом блока управления и синхрониз ции, второй и первый выходы которого подключены соответственно к выходу генератора импульсов максимальной дл тельности и к второму входу блока обработки прерываний, первьй вход которого соединен с шиной внешних прерываний zj . В известном микропрограммном устройстве наибольшие трудности появляются при определении состояния зави сания программы. Если состояние зависания определяется оператором,врем решения задачи увеличивается, так как среднее время реакции оператора при определении зависания и повторный запуск с начала, составляет несколько десятков секунд (30 с). Использование генератора сигналов максимальной длительности (он формирует сигнал запроса прерывания по таймеру) усложняет обработку прерывания программными способами. Кроме того, прерывание процесса вычисления по таймеру не связано с состоянием процесса - находится ли он в состоя нии зависания или в состоянии пра вильного выполнения (поэтому в изоб ретении предлагается автоматическое определение состояния зависания без участия оператора и возможносности формирования прерывания работ устройства только в случае зависания) . Целью изобретения является повышение коэффициента использования об рудования путем автоматического перезапуска процесса при однократных сбоях и зацикливании программ. Поставленная цель достигается тем, что в сбоеустойчивое микропрограммное устройство управления, содержа1цее блок адресации, коммутатор, блок памяти микрокоманд, блок синхронизации, первый триггер, гене тор импульсов максимальной длительности, второй триггер, блок обработ ки прерывания, блок адресации в режиме прерывания, выход которого объединен с выходом блока адресации и соединен с адресным входом блока памяти микрокоманд, первый, второй и третий управляющие выходы которого соединены соответственно с первым входом блока синхронизации, выходом управления устройства и с первым управляющим входом коммутатора, второй управляющий вход которого соединен с управляющим входом устройства, первый, второй и третий информационные входы коммутатора соединены соответственно с первым, вторым адресными выходами блока памяти микрокоманд и первым выходом блока обработки прерываний, второй выход которого соединен с единичньм входом первого триггера, нулевой вход которого соединен с первым выходом блока синхронизации, второй и третий выходы которого соединены соответственно с первыми управляющими входами блока адресации и адресации в режиме прерывания, первые информационные входы которых соединены с выходом коммутатора, четвертый информационный вход которого соединен с входом адреса устройства, с вторым информационным входом блока адресации в режиме прервтания и с первым входом блока обработки прерываний, второй вход которого соединен с входом запроса на прерывание устройства, выход второго триггера соединен с третьим входом блока обработки прерываний, четвертый вход которого соединен с вторым входом блока синхрониза1ши, единичным выходом первого триггера и с вторыми управляющими входами блоков адресации в режиме прерывания, третьи управляющие входы которых соединены с нулевым выходом первого триггера, выход генератора импульсов максимальной длительности соединен с единичным входом второго триггера, нулевой вход которого соединен с четвертым выходом блока синхронизации, введе- , ны регистр адреса перезапуска, элемент И,, элемент ИЛИ, третий триггер, причем информационный вход регистра адреса перезапуска соединен с входом адреса устройства, а управляющий вход - с пятым выходом блока синхронизации, выход регистра адреса перезапуска - с вторым информационным входом блока адресации, шестой выход блока синхронизации - с входом третьего триггера, единичный вьиод которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с вых;одом элемента И и с пятым входом блока обработки прерываний, шестой вход которого соедине с выходом элемента ИЛИ, выход генер тора импульсов максимальной длитель ности соединен с первым входом элемента И, второй вход которого соединен с выходом второго триггера. При этом блок обработки прерываний содержит первой, второй регистры, шифратор и схему сравнения, пер вьй и второй информационные входы которой соединены соответственно с выходами шифратора и первого регист ра, управляющий вход схемы сравнения соединен с шестым входом блока, а выход - с вторым выходом блока, управляющие входы первого и второго регистров - с четвертым входом блок информационный вход первого регистра - с первым входом блока, второй, третий и пятый входы блока объедине ны и подключены к информационному входу второго регистра, выход которого соединен с входом шифратора, выход которого подключен к первому входу блока. Таким образом, введение регистра адреса перезапуска, схемы И, схемы ИЛИ, триггера обеспечивает выявление зависания программы, автомати ческий ее перезапуск и формирование сигнала прерывания только при зави.сании программы. На фиг. 1 изображена блок-схема предлагаемого устройства} на фиг.2. блок-схема коммутатора; на фиг.З блок-схема обработки прерываний; на фиг. 4 - блок-схема блока синхрониз ции; на фиг. 5 - блок-схема блока адресации; на фиг. 6 - временные диаграммы основного цикла работы устройства; на фиг. 7 - временные диаграммы работы устройства в режиме обработки прерывания; на фиг. 8 временные диаграммы работы устройств при зависании программы. Предлагаемое микропрограммное устройство содержит (фиг. 1) блок 1 адресации, коммутатор 2, блок 3 памяти микрокоманд, блок 4 синхронизации, триггер 5, генератор 6 импульсов максимальной длительности, триггер 7, блок 8 обработки пре4)ываний, блок 9 адресации в режиме прерывания, управляющий вход 10 устройства вход 11 адреса устройства, вход 12 запроса на прерывание устройства, выход 13 управления устройства, регистр 14 адреса перезапуска, элемент И 15,элемент ИЛИ 16, триггер 17. Входящий в микропграммное устройство управления коммутатор (фиг.2) содержит коммутатор 18, группу 19 элементов И, группу 20 элементов ИЛИ, группу 21 элементов И, элемент НЕ 22. Входящий в микрограммное устройство управления блок обработки прерываний (фиг. 3) содержит регистр 23, шифратор 24, регистр 25, схему 26 сравнения. Входящий в микропрограммное устройство управления блок синхронизации содержит генератор 27, формирователь 28, элемент НЕ 29, дешифратор 30, элементы 2И 31-34, элементы ЗИ 35 и 36, элементы 2РШИ 37 и 38. Входящий в микропрограммное устройство управлений блок 1 адресации (фиг. 5) содержит группу 39 элементов И, регистр 40, группу 41 элементов HJM, группу 42 элементов И, группу 43 элементов И. Регистр 14 адреса перезапуска предназначен для хранения начального адреса микропрограммы и может быть реализован на регистровых схемах К589ИР12. Элемент И 15 предназначен для формирования запроса на прерывание в случае однократного сбоя и зацикливания и может быть реализован на схеме К155ЛИ1. Элемент ИЛИ 16 предназначен для формирования сигнала разрешения обработки прерывания и может быть реализован на схеме К155ЛЛ1. Третий триггер 17 предназначен для обеспечения запрещения обработки прерываний и может быть реализован на схеме К155ТМ2. Микропрограммное устройство работает следующим образом. При включении устройства на вход блока 3 памяти микрокоманд поступает определенный адрес (обычно нулевой), с которого начинается микропрограмма, назначение которой - загрузка началього адреса с внешней шины в качетве начального адреса микропрограмы. Адрес с выхода блока 1 адресаии поступает на адресный вход блока , с которого считывается первая икрокоманда. Один из возможных форматов микрокоманды для реализации предлагаемого технического решения может выглядеть так: -поле адреса следующей микрокоман,ды(может включить прямой и альтерративный адрес); поле управления выбором подключения входа коммутатора 2;. поле управления дешифратора; поле для управления отдельными элементами процессора. Коммутатор 2 осуществляет выбор адреса следующей микрокоманды. В обычном режиме работы (не в режиме прерьшания) к выходу коммутатора под ключен блок 1 адресации, а выход этого блока подключен к входу блока памяти микрокоманд, вход блока 9 в этом режиме - К входу начальной установки (по ней в этот блок загружается начальный адрес микропрограммы обработки прерываний). Задающая последовательность синхр сигналов (диагр.а , фиг. 6) с выхода генератора 27 (фиг. 4) поступает на вход формирователя 28 (фиг. 4). Тактовые импульсы с выхода формирователя участвуют в формировании упра ляюца1х сигналов для блоков 1 и 9 адресации, с выхода блока 1 первый адрес (диагр. 6, фиг. 6) поступает на блок 3 хранения микрокоманд, с выхода которого новая микрокоманда (диагр. 2 , фиг. 6) поступает на вход блока 4 синхронизации, обеспечивая управление устройством в новом такте Во время выполнения любой микропрограммы генератор 6 сигналов максимальной длительности формирует на своем выходе периодическую последовательность импульсов прямоугольной формы (диагр.а , фиг. 7). По спадающему фронту этого импуль са второй триггер переводится в единичное состояние (диагр.S , фиг. 7) что соответствует поступлению запроса на прерывание от таймера на вход блока 8 обработки прерьшаний. Для пояснения алгоритма функционирования устройства в режиме прерывания приве дены диаграммы на фиг. 7. Обработка прерываний разрешается, когда на выходе третьего триггера 17 имеется ед ничный разрешающий сигнал, который через элемент ИЛИ 16 подается на вход блока 8. Если выполняемая микро программа разрешает обработку прерываний, то при поступлении, например 238 запроса на обработку прерьшания от таймера происходит перевод устройства в режим прерывания, так как на выходе блока 8 вырабатывается управляющий сигнал, переводящий первый триггер 5 в единичное состояние,что соответствует режиму прерывания (диагр. 1 , фиг. 7). Формируемый при этом на первом выходе первого триггера единичный сигнал отключает выход блока 1 адресации и подключает выход блока 9 адресации к адресному входу блока хранения микрокоманд, к первому входу 1 блока 9 подключается выход коммутатора, а в блоке 1 адресации остается адрес, с которого нужно будет возобновить прерванную программу. Этот же сигнал с первого выхода первого триггера подается на вход блока 8 обработки прэрьшаний, запрещает изменение статуса в регистре 25 и запрещает изменение в регистре 23, что обеспечивает выдачу на первом выходе 1 двоичного кода прерывания. В регистр 40 блока 9 перед началом выполнения программы был загружен адрес начала программы обработки прерываний, который подается на адресный вход блока 3. В результате выполнения считанной по этому адресу микрокоманды к выходу коммутатора 2 Подключается второй вход, т.е. двоичный код прерывания, выработанньй блоком обработки прерываний, через коммутатор поступает в блок 9 адресации обработки прерываний, и начинает выполняться программа обработки конкретного прерывания (в рассматриваемом примере программа обработки прерывания по таймеру). В конце каждой программы обработки прерываний в регистр блока адресации загружается адрес начала обработки рерываний для обеспечения вьтолнения последующих программ обработки прерьгааний. После окончания обработки очередного прерывания первый триггер 5 по управляющему сигналу с выхода блока 4 сбрасьшается в ноль. На фиг. 7 приведены диаграммы, поясняющие работу устройства в режие обработки прерывания (диаграмма а - выход генератора импульсов максимальной длительности, 5 - выход второго триггера-, Ь - выход схемы 26, 2 - выход первого триггера 5, ij. - первый выход блока 4, в - третий выход блока 4, « - выход третьего триггера 17, выход элемента ИЛИ 16, U - выход 6 блока 4). В начале каждой микропрограммы, требующей запрещения обработки прер ваний, третий триггер 17 управляющи сигналом переводится в и.левое состояние, вследствие чего, запрещаетс срабатывание блока 8, и при правиль ной работе устройства прерывание возникнуть не может. Если есть запрос на обработку прерывания по таймер.у, то в конце его обработки с первого выхода блока 4 на вход втор го триггера подается сигнал сброса триггера 7 в нулевое состояние, при этом сбрасывается сигнал запроса на прерывание по таймеру. В случае зависания микропрограммы из-з однократньк сбоев третий триггер 17 не переводится в единичное состояни в течение длительного промежутка вр мени, большего, чем период сигналов максимальной длительности, вырабаты ваемых генератором 6. Запрос на пре рывание по таймеру не обрабатьшаетс когда на выходе второго триггера 7 имеется единичньй сигнал, так как через элемент ИЛИ 16 на вход 6 блока 8 не подается разрешающий В этом случае при совпадении единич ного полупериода сигнала (импульс кончился, фронт возрастающий) с выхода генератора 6 и единичного сигнала с выхода второго триггера 7 на выходе элемента И 15 формирует ся единичный сигнал, являющийся запросом на прерывание по зависанию, который подается на вход блока 8. Диаграммы на фиг. 8 поясняют работу устройства в случае зависания программы из-за однократных сбоев (диаграмма а - выход генератора импульсов максимальной длительности, 5 - выход второго триггера 7,1)- в ход схемы 26 сравнения, Z - выход триггера 5, - выход третьего триг гера 17, е - выход элемента И 15, 5k- выход элемента ИЛИ 16, J - первый выход блока 4, и - выход блока 4, Единичный сигнал с выхода элемен та И 1 5 через элемент ИЛИ 16 поступ ет в качестве разрешающего сигнала на вход блока 8, благодаря чему об работка прерывания по зависанию 2310 становится возможной. При обработке прерьшания по зависанию выход регистра адреса перезапуска подключается к входу блока 1 адресации, и адрес перезапуска записывается в регистр 40 блока 1, после окончания выполнения программы обработки прерывания по зависанию программа начинает выполняться с адреса, которьй был записан в регистр адреса перезапуска-«тем самым обеспечивается полное повторное выполнение очередного участка программы, что позволит обеспечить Правильное решение задачи в целом. Предлагаемое техническое решение можно использовать при создании надежных и высокопроизводительных процессоров с микропрограммным управлением. Оно позволяет автоматически определить сбой процессора при зависании программы и автоматически перезапускать процесс, ч:ем устраняется простой устройства, обусловленный либо временем определения состояния решения задачи оператором, либо увеличением времени использования аппаратуры устройства на обработку прерывания по таймеру, что обеспечивает повьш1ение коэффициента использования процессора, в котором,используется предлагаемое устройство. Так, среднее время реакции оператора при определении зависания системы и повторньй запуск задачи с начала для микропроцессорной системы Intellec фирмы ИНТЕЛ составляет несколько десятковсекунд.Если принять период сигналов максимальной длительности, равный 10 мс, то очевидно, что временные потери изза однократных сбоев при использовании предлагаемого технического решения уменьшаются на три порядка. За это время простоя устройство может выполнить большой объем вычислений (при быстродействии процессора в 5 МИЛ.ПИОНОВ операций в секунду за это время может быть выполнена программа, требующая 150 млн. элементарных действий. Предлагаемое техническое решение было использовано при построении на микропроцессорном наборе БИС серии К 589 экспериментальных операционных процессоров рекурсивной вычислительной машины.

-

19

-

Г

23

П

J

Фиг. 2

8

У424

26

25

I

Т

..

г

п

Y

г

п

у t

4

п

л

:х

Адрес 1

1 HUKftBHOHo ffa2 пи грокопан а3пинрокопа а

л

х

Адрес 2

Адрес 3

Фиг.В

J J

И

ib if

.

.Hf 4f

f /

iF

ФпЛ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 551648, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-07—Публикация

1982-10-01—Подача