Изобретение относится к вычислительной технике и может быть использовано для восстановления информации в полупроводниковых динамических запоминающих устройствах, входящих в состав специализированных ЭВМ, подвергающихся в процессе эксплуатации воздействию физических полей повышенной интенсивности, например в информационно-измерительных системах контроля радиологической обстановки, в рентгеновских и ЯМР томографах, в промышленных роботах и т.п.

При повышенной интенсивности воздействующих на ЭВМ ионизирующих излучений и/или электромагнитных полей в первую очередь необходимо обеспечить сохранность записанной в запоминающие устройства информации. Эта задача чаще всего решается путем использования в вычислительных системах полупроводниковых динамических запоминающих устройств (ДЗУ), в которых периодически осуществляется регенерация хранимой информации. При этом регенерация содержимого ячеек памяти производится через заранее заданные и, как правило, неизменные интервалы времени, при определении длительности которых необходимо учитывать два противоречащих одно другому обстоятельства.

Во-первых, при работе ДЗУ в режиме регенерации оно не может взаимодействовать с другими частями ЭВМ, работа которой прерывается на время выполнения цикла регенерации. Следовательно, для сокращения непроизводительных суммарных затрат машинного времени требуется увеличение интервала времени между циклами регенерации, то есть уменьшение частоты запуска регенерации ДЗУ.

Во-вторых, хранящаяся в ячейках памяти ДЗУ информация со временем разрушается, в связи с чем для повышения помехоустойчивости ДЗУ и повышения надежности его работы за счет обеспечения сохранности занесенных в него данных нужно уменьшать интервал времени между циклами регенерации, то есть увеличивать чистоту запуска регенерации ДЗУ.

При воздействии на полупроводниковые ДЗУ ионизирующих излучений и/или сильных электромагнитных полей увеличивается скорость разрушения записанной в него информации, что требует повышения частоты запуска регенерации ДЗУ, приводящее к дополнительному снижению производительности ЭВМ.

При эксплуатации ЭВМ с ДЗУ в стабильных условиях возможен выбор оптимальной частоты запуска регенерации ДЗУ, при которой достигаются требуемые помехоустойчивость и надежность работы ДЗУ при определенном и неизменном снижении ее производительности.

В случае же воздействия на ЭВМ с полупроводниковым ДЗУ физических полей изменяющейся интенсивности сохранение неизменной частоты запуска регенерации ДЗУ при повышении интенсивности полей сверх предусмотренных значений может привести к нарушению работоспособности ЭВМ из-за резкого снижения надежности работы ДЗУ. Выбор же повышенной частоты регенерации ДЗУ, ориентированной на максимальные пиковые значения интенсивности физических полей, приводит к неоправданным потерям машинного времени при средней и низкой их интенсивности.

Обеспечение возможности автоматического изменения частоты запуска регенерации ДЗУ в зависимости от изменения интенсивности воздействующих на ЭВМ внешних физических полей позволит устранить отмеченный недостаток.

Известно устройство для регенерации динамической памяти, обеспечивающее повышение производительности ЭВМ как за счет исключения регенерации ячеек памяти, расположенным в строках, к которым вообще не было обращения при записи информации в память, так и за счет осуществления регенерации только тех ранее задействованных строк памяти, к которым не было обращения в течение заданного промежутка времени [1]

Известное устройство для регенерации динамической памяти содержит первый и второй генераторы тактовых импульсов, первый и второй триггеры, первый и второй шинные формирователи, блок местного управления, группу счетчиков, дешифратор, шифратор, регистр, элемент И, элемент ИЛИ, элемент задержки, группу триггеров и группу элементов И, выход первого генератора тактовых импульсов подключен к синхровходам блока местного управления и первого триггера, прямой выход которого является выходом требования прямого доступа к памяти (ПДП), входом предоставления ПДП является установочный вход второго триггера, прямой выход которого является выходом подтверждения захвата канала, а также связан с управляющими входами первого и второго шинных формирователей, с входом режима работы блока местного управления и с входом сброса первого триггера, установочный вход которого соединен с выходом элемента ИЛИ, инверсный выход второго триггера подсоединен к одному из входов элемента И, другой вход которого подключен к выходу второго генератора тактовых импульсов, а выход к одному из входов каждого из элементов И группы элементов И, другой вход каждого из которых соединен с прямым выходом соответствующего триггера группы триггеров, а выход со счетным входом соответствующего счетчика группы счетчиков, выход старшего разряда каждого из которых связан с одним из входов элемента ИЛИ и с одним из входов шифратора, выходы которого подключены ко входам второго шинного формирователя, выходы которого являются выходами адреса, входом стробирования записи является вход элемента задержки, выход которого соединен с входом сброса каждого из триггеров группы триггеров, установочный вход каждого из которых подсоединен к соответствующему выходу дешифратора, подключенного своими информационными входами к выходам регистра, информационные входы которого являются входами адреса, выходы первого шинного формирователя являются управляющими выходами устройства, управляющими входами которого является группа входов блока местного управления, группа выходов которого соединена со входами первого шинного формирователя, блок местного управления своими выходами сигнала синхронизации и сигнала разрешения записи подсоединен к соответствующим входам регистра, выходом сигнала стробирования к управляющему входу дешифратора, а выходом сигнала сброса к входу сброса второго триггера, при этом вход обнуления каждого из счетчиков группы связан с соответствующим выходом дешифратора.

Однако данное устройство не обеспечивает при изменении интенсивности внешних физических полей автоматического изменения промежутка времени, по истечении которого осуществляется запуск регенерации ранее задействованных ячеек памяти.

Задачей изобретения является обеспечение возможности адаптации частоты запуска регенерации ДЗУ к изменению интенсивности внешних физических полей, что позволяет повысить среднее эффективное быстродействие ДЗУ при сохранении требуемых помехоустойчивости и надежности его работы, следствием чего является повышение производительности ЭВМ.

Это достигается тем, что в устройство для управления регенерацией в полупроводниковом динамическом запоминающем устройстве, содержащее первый и второй генераторы тактовых импульсов, первый и второй триггеры, первый и второй шинные формирователи, блок местного управления, группу счетчиков, дешифратор, шифратор, регистр, элемент И, элемент ИЛИ, элемент задержки, группу триггеров и группу элементов И, выход первого генератора тактовых импульсов подключен к синхровходам блока местного управления и первого триггера, прямой выход которого является выходом требования прямого доступа к памяти, входом предоставления прямого доступа к памяти является установочный вход второго триггера, прямой выход которого является выходом подтверждения захвата канала, а также связан с управляющими входами первого и второго шинных формирователей, с входом режима работы блока местного управления и с входом сброса первого триггера, установочный вход которого соединен с выходом элемента ИЛИ, инверсный вход второго триггера подсоединен к одному из входов элемента И, другой вход которого подключен к выходу второго генератора тактовых импульсов, а выход к одному из входов каждого из элементов И группы элементов И, другой вход каждого из которых соединен с прямым выходом соответствующего триггера группы триггеров, а выход со счетным входом соответствующего счетчика группы счетчиков, выход старшего разряда каждого из которых связан с одним из входов элемента ИЛИ и с одним из входов шифратора, выходы которого подключены ко входам второго шинного формирователя, выходы которого являются выходами адреса, входом стробирования записи является вход элемента задержки, выход которого соединен с входом сброса каждого из триггеров группы, установочный вход каждого из которых подсоединен к соответствующему выходу дешифратора, подключенного своими информационными входами к выходам регистра, информационные входы которого являются входами адреса, выходы первого шинного формирователя являются управляющими выходами устройства, управляющими входами которого является группа входов блока местного управления, группа выходов которое соединена со входами первого шинного формирователя, блок местного управления своими выходами сигнала синхронизации и сигнала разрешения записи подсоединен к соответствующим входом регистра, выходом сигнала стробирования к управляющему входу дешифратора, а выходом сигнала сброса к входу сброса второго триггера, введены группа измерительных датчиков параметров внешних физических полей и блок формирования кода управления частотой регенерации, входы которого связаны с выходами группы измерительных датчиков параметров внешних физических полей, а выходы с информационными входами всех, кроме старшего, разрядов каждого из счетчиков группы счетчиков, вход разрешения записи каждого из которых подключен к соответствующему выходу дешифратора.

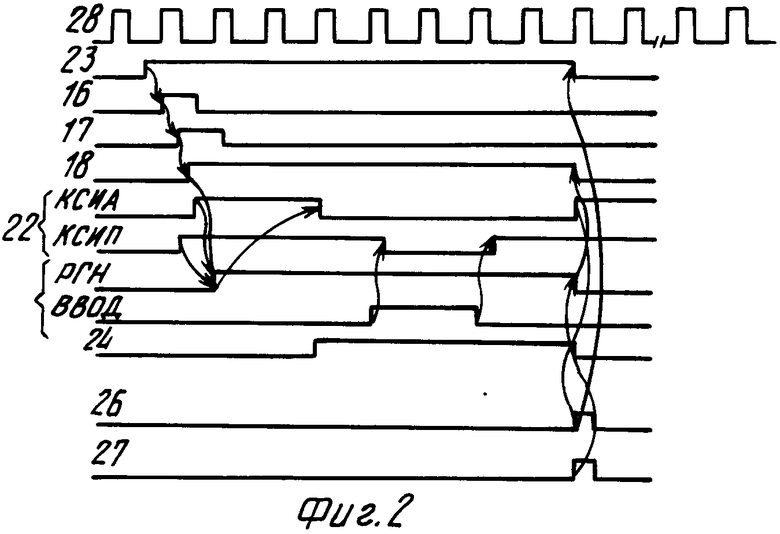

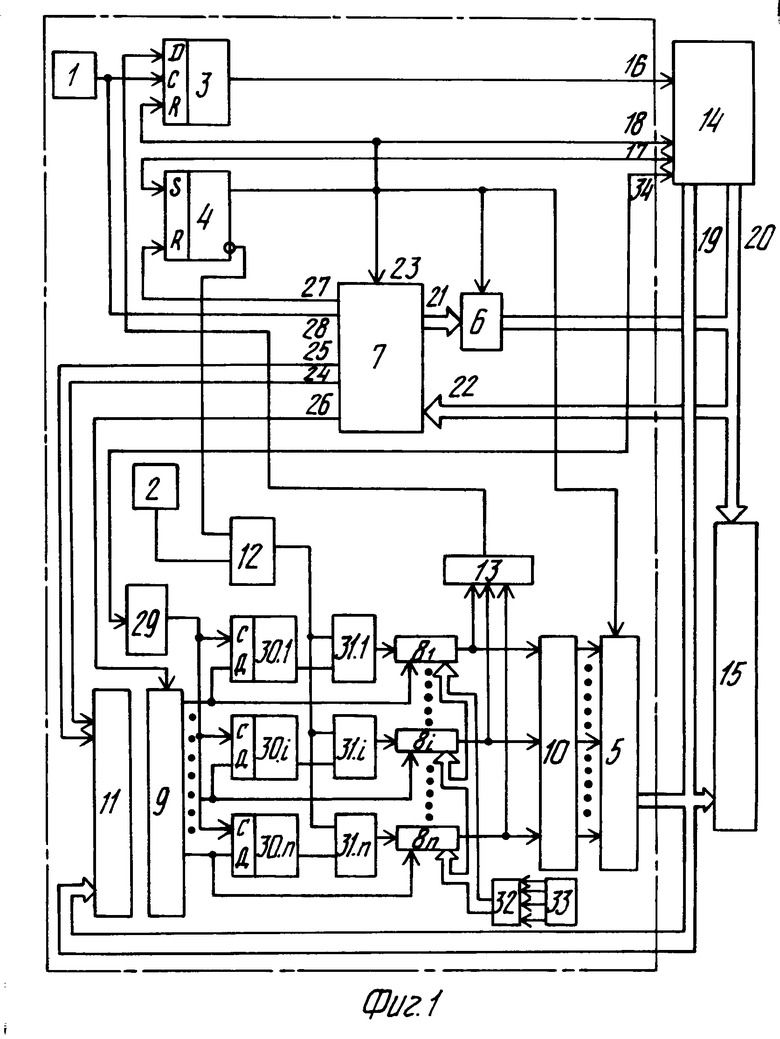

На фиг. 1 представлена функциональная схема устройства, выполненного согласно изобретению; на фиг. 2 временная диаграмма работы устройства в режиме регенерации информации.

Устройство содержит первый 1 и второй 2 генераторы тактовых импульсов, первый 3 и второй 4 триггеры, второй 5 и первый 6 шинные формирователи, блок 7 местного управления, счетчики 8, дешифратор 9, шифратор 10, регистр 11, элемент И 12, элемент ИЛИ 13. На фиг. 1 также приведены элементы ЭВМ, взаимодействующие с устройством: центральный процессор 14 и оперативная память 15, в качестве которой использовано полупроводниковое ДЗУ. Кроме того, на фиг. 1 показаны выход 16 требования прямого доступа к памяти (ПДП), вход 17 предоставления ПДП, выход 18 подтверждения захвата канала (ПЗ), адресная шина 19, шина 20 управления памятью, группа 21 выходов и группа 22 входов блока 7 местного управления, вход 23 режима работы блока 7 местного управления, выход 24 сигнала синхронизации, выход 25 сигнала разрешения записи, выход 26 сигнала стробирования, выход 27 сигнала сброса, синхровход 28 блока 7 местного управления.

Кроме того, устройство содержит элемент 29 задержки, группу триггеров 30.1,30.i,30.n, группу элементов И 31.1,31.i,31.n, блок 32 формирования кода управления частотой регенерации, группу 33 измерительных датчиков параметров внешних физических полей и вход 34 стробирования записи.

В качестве блока 7 местного управления может быть использован блок местного управления известного устройства.

Группа 33 измерительных датчиков параметров внешних физических полей может содержать, в зависимости от условий эксплуатации устройства, датчики интенсивности α и β излучений, датчики напряженности электромагнитного поля и т.д.

При использовании датчиков с аналоговым выходом блок 32 формирования кода управления частотой регенерации может содержать, например, весовой аналоговый сумматор, входы которого являются входами блока, и аналого-цифровой преобразователь, преобразующий аналоговый сигнал на выходе сумматора в выходной код блока 32.

При использовании датчиков с цифровым выходом блок 32 может быть выполнен в виде многовходового суммирующего устройства, осуществляющего весовое суммирование входных кодов.

Если используются датчики как с аналоговым выходом, так и с цифровым, то в этом случае к одному из входов многовходового суммирующего устройства может быть подключен аналого-цифровой преобразователь, преобразующий в код выходной сигнал аналогового весового сумматора, обрабатывающего выходные сигналы соответствующих датчиков.

Устройство работает следующим образом.

В исходном состоянии триггеры 3, 4, 30.1 30.n сброшены, а счетчики 8.1 8. n обнулены, а на выходах блока 7 нулевые уровни сигналов. Импульсы с выхода генератора 2 тактовых импульсов через элемент И 12 и группу элементов И 31.1 31.n на счетные входы счетчиков 8 соответствуют адресам строк, к которым было обращение при записи информации в память. На счетные входы счетчиков 8.1 8.n, к которым не было обpащения при записи информации в память, импульсы поступать не будут, так как соответствующие элементы И 31.1 31.n группы заблокированы низкими уровнями сигналов на соответствующих выходах триггеров 30.1 30.n группы.

При переполнении одного из счетчиков 8.1 8.n сигнал с выхода его старшего разряда через элемент ИЛИ 13 поступает на вход установки триггера 3.

Одновременно на выходе шифратора 10 устанавливается код счетчика 8.i (от 1 до n), соответствующий коду адреса строки тех ячеек оперативной памяти, для которых истекло время хранения информации и требуется регенерация.

По переднему фронту импульса генератора 1 тактовых импульсов устанавливается триггер 3, на его прямом выходе вырабатывается сигнал 16 требования прямого доступа к памяти. Процессор 14 приостанавливает выполнение операций, освобождает адресную шину 19 и выдает ответный сигнал на вход 17 предоставления ПДП, устанавливающий триггер 4, который в свою очередь сбрасывает триггер 3, вырабатывает сигнал на выходе 18 подтверждения захвата канала (ПЗ), а также открывает шинные формирователи 5 и 6.

Сигнал с инверсного выхода триггера 4 запрещает прохождение импульсов генератора 2 тактовых импульсов через элемент И 12 на входы счетчиков 8. Сигнал с прямого выхода триггера 4 поступает в блок 7 местного управления и разрешает после завершения текущего цикла обращения к оперативной памяти 15 и снятия сигналов синхронизации активного устройства (КСИА), синхронизации пассивного устройства (КСИП), поступающий на входы 22 блока 7 местного управления, формирование по положительному перепаду тактового импульса (ТИ) от генератора 1 тактовых импульсов сигнала регенерации (РГН) на одном из выходов группы 21 выходов блока 7 местного управления. Этот сигнал поступает через шинный формирователь 6 в оперативную память 15 и остается активным в течение всего времени регенерации.

По следующим тактовым импульсам блок 7 местного управления формирует на соответствующих выходах группы 21 выходов сигналы СИА и "Ввод", которые поступают в оперативную память 15 через шинный формирователь 6 вместе с кодом адреса сроки с выхода шинного формирователя 5. Одновременно код адреса строки поступает на информационные входы регистра 11. Запись в регистр 11 происходит по переднему фронту сигнала на выходе 24 сигнала синхронизации, поступающего из блока 7 местного управления. В ответ на сигнал "Ввод" оперативная память 15 формирует сигнал КСИП, поступающий в блок 7 через группу 22 входов. После этого через один ТИ снимается сигнал "Ввод", в ответ на который оперативная память 15 снимает сигнал КСИП. По второму после этого ТИ снимается сигнал СИА, а по заднему фронту этого импульса блок 7 формирует на выходе 26 сигнала стробирования одиночный импульс, который поступает на управляющий вход дешифратора 9, записывая тем самым в счетчик 8.i, соответствующий коду, хранящемуся в регистре 11, код, сформированный на выходах блока 32 формирования кода управления частотой регенерации. Вслед за этим на выходе 27 сигнала сброса появляется импульс, обнуляющий триггер 4. Снимаются сигналы РГН и ПЗ, цикл регенерации закончен.

Таким образом, может осуществляться регенерация для любой строки оперативной памяти 15. Если в процессе работы устройства ни один из счетчиков 8 не переполнен, т.е. время хранения информации ни для одной строки не вышло, то работа устройства происходит следующим образом.

В режиме обращения к оперативной памяти 15 процессор 14 устанавливает на шине 19 код адреса ячейки памяти, а на шине 20 вырабатываются сигналы управления, поступающие в блок 7 местного управления по группе 22 входов: канальный сигнал синхронизации пассивного устройства (КСИП), канальный сигнал выбора внешнего устройства (КВУ). Младшие разряды кода адреса, являющиеся кодом адреса строки по сигналу с выхода 24 блока 7 местного управления при наличии разрешающего сигнала на его выходе 25 сигнала разрешения записи записываются в регистр 11. Запрещающий запись сигнал появляется на выходе блока 7 местного управления при обращении процессора 14 не к оперативной памяти 15, а к регистрам внешних устройств. При этом не формируется сигнал на выходе 26 блока 7 местного управления.

Так как при обращении к оперативной памяти 15 происходит регенерация всех ячеек памяти с заданным адресом строки, то по окончании цикла обращения к оперативной памяти 15 по сигналу с выхода 26 блока 7 местного управления сигналом с выхода дешифратора 9 происходит занесение кода с выходов блока 32 в счетчик 8.1, порядковый номер которого совпадает с кодом адреса строки, хранящимся в регистре 11. Запрос на регенерацию ячеек оперативной памяти 15 с данным адресом строки может поступить с выхода данного счетчика 8, только через время Тргн периода регенерации, при условии, что за это время процессор 14 больше не обратится к ячейкам с этим адресом строки.

Текущие коды счетчиков 8.1 8.n определяют допустимое время хранения информации для каждой строки оперативной памяти 15, которое не может превысить величину, определяемую выражением

TРГН=  · (2k-1-N) где f2 частота импульсов на выходе генератора 2 тактовых импульсов;

· (2k-1-N) где f2 частота импульсов на выходе генератора 2 тактовых импульсов;

К разрядность счетчиков 8.1 8.n;

N (K-1) разрядный код на выходе блока 32 формирования кода управления частотой регенерации.

Код числа N вырабатывается блоком 32 формирования кода управления частотой регенерации, осуществляющего математическую обработку информации о текущих значениях параметров, характеризующих интенсивность воздействующих на ДЗУ внешних физических полей, поступающей с выходов группы 33 измерительных датчиков. В простейшем случае код числа N представляет собой линейную комбинацию значений измеренных параметров, приведенных к единому масштабу с помощью весового суммирования. Важно лишь то, чтобы увеличение текущего значения хотя бы одного параметра (при неизменности текущих значений других параметров) приводило к увеличению числа N.

При этом отсутствуют какие-либо принципиальные ограничения по реализации более сложных функциональных зависимостей числа N от измеренных текущих значений параметров, характеризующих интенсивность воздействующих на ДЗУ внешних физических полей. В частности, как на входах, так и на выходах блока 32 могут быть установлены функциональные преобразователи, либо сам блок 32 может быть реализован в виде специализированного вычислителя, осуществляющего более сложную обработку входных данных.

Как следует из приведенной выше формулы, при возрастании числа N вследствие увеличения интенсивности воздействующих на ДЗУ внешних физических полей величина допустимого времени хранения информации для каждой строки оперативной памяти 15 уменьшается, то есть возрастает частота регенерации ячеек памяти ДЗУ.

При записи информации в любую ячейку оперативной памяти 15 сигналом с входа 34 стробирования записи поступающим на синхровходы триггеров 30.1 30.n группы через элемент 29 задержки, соответствующий триггер устанавливается в единичное состояние, так как на установочном входе у него присутствует сигнал высокого уровня, формируемый дешифратором 9. Установка триггера 30.i группы происходит при первоначальной записи информации, при повторном обращении к ячейкам оперативной памяти 15 с этим же адресом строки, триггер 30.i остается в установленном состоянии, элемент 29 задержки также обеспечивает согласование по нагрузочным характеристикам магистрали процессора 14 с синхровходами триггеров 30.1 30.n группы.

Таким образом, из цикла регенерации исключается регенерация ячеек динамической памяти, в которые не заносилась информация.

Изобретение относится к вычислительной технике и может быть использовано для восстановления информации в полупроводниковых динамических запоминающих устройствах, входящих в состав специализированных ЭВМ, подвергающихся в процессе эксплуатации воздействию физических полей повышенной интенсивности. Устройство содержит первый 1 и второй 2 генераторы тактовых импульсов, первый 3 и второй 4 триггеры, второй 5 и первый 6 шинные формирователи, блок 7 местного управления, счетчики 8, дешифратор 9, шифратор 10, регистр 11, элемент И 12, элемент ИЛИ 13, блок формирования кода управления частотой регенерации 32, группа измерительных датчиков параметров внешних физических полей 33. 2 ил.

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ, содержащее первый и второй генераторы тактовых импульсов, первый и второй триггеры, первый и второй шинные формирователи, блок местного управления, группу счетчиков, дешифратор, шифратор, регистр, элемент И, элемент ИЛИ, элемент задержки, группу триггеров и группу элементов И, выход первого генератора тактовых импульсов подключен к синхровходам блока местного управления и первого триггера, прямой выход которого является выходом требования прямого доступа к памяти, входом предоставления прямого доступа к памяти является установочный вход второго триггера, прямой выход которого является выходом подтверждения захвата канала, а также связан с управляющими входами первого и второго шинных формирователей, с входом режима работы блока местного управления и с входом сброса первого триггера, установочный вход которого соединен с выходом элемента ИЛИ, инверсный вход второго триггера подсоединен к одному их входов элемента И, другой вход которого подключен к выходу второго генератора тактовых импульсов, а выход к одному их входов каждого из элементов И группы элементов И, другой вход каждого из которых соединен с прямым выходом соответствующего триггера группы триггеров, а выход со счетным входом соответствующего счетчика группы счетчиков, выход старшего разряда каждого из которых связан с одним из входов элемента ИЛИ и с одним из входом шифратора, выходы которого подключены ко входам второго шинного формирователя, выходы которого являются выходами адреса, входом стробирования записи является вход элемента задержки, выход которого соединен с входом сброса каждого из триггеров группы, установочный вход каждого из которых подсоединен к соответствующему выходу дешифратора, подключенного своими информационными входами к выходам регистра, информационные входы которого являются входами адреса, выходы первого шинного формирователя являются управляющими выходами устройства, управляющими входами которого является группа входов блока местного управления, группа выходов которого соединена со входами первого шинного формирователя, блок местного управления своими выходами сигнала синхронизации и сигнала разрешения записи подсоединен к соответствующим входам регистра, выходом сигнала стробирования к управляющему входу дешифратора, а выходом сигнала сброса к входу сброса второго триггера, отличающееся тем, что в него введены группа измерительных датчиков параметров внешних физических полей и блок формирования кода управления частотой регенерации, входы которого связаны с выходами группы измерительных датчиков параметров внешних физических полей, а выходы с информационными входами всех, кроме старшего, разрядов каждого из счетчиков группы счетчиков, вход разрешения записи каждого из которых подключен к соответствующему выходу дешифратора.

| Устройство для регенерации динамической памяти | 1988 |

|

SU1534509A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-07-25—Публикация

1994-04-22—Подача