Изобретение относится к вычислительной технике, может быть использовано для регенерации динамической памяти ЭВМ и является усовершенствованием известного устройства по авт. св. № 1434497.

Целью изобретения является повышение быстродействия памяти.

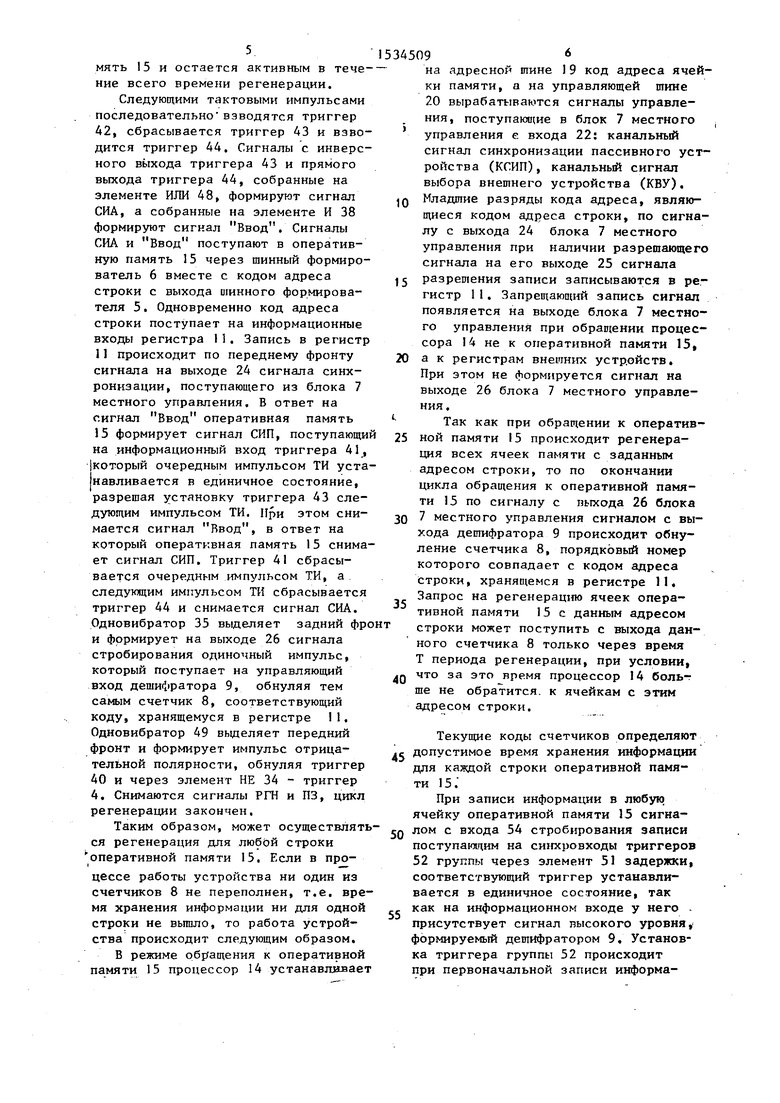

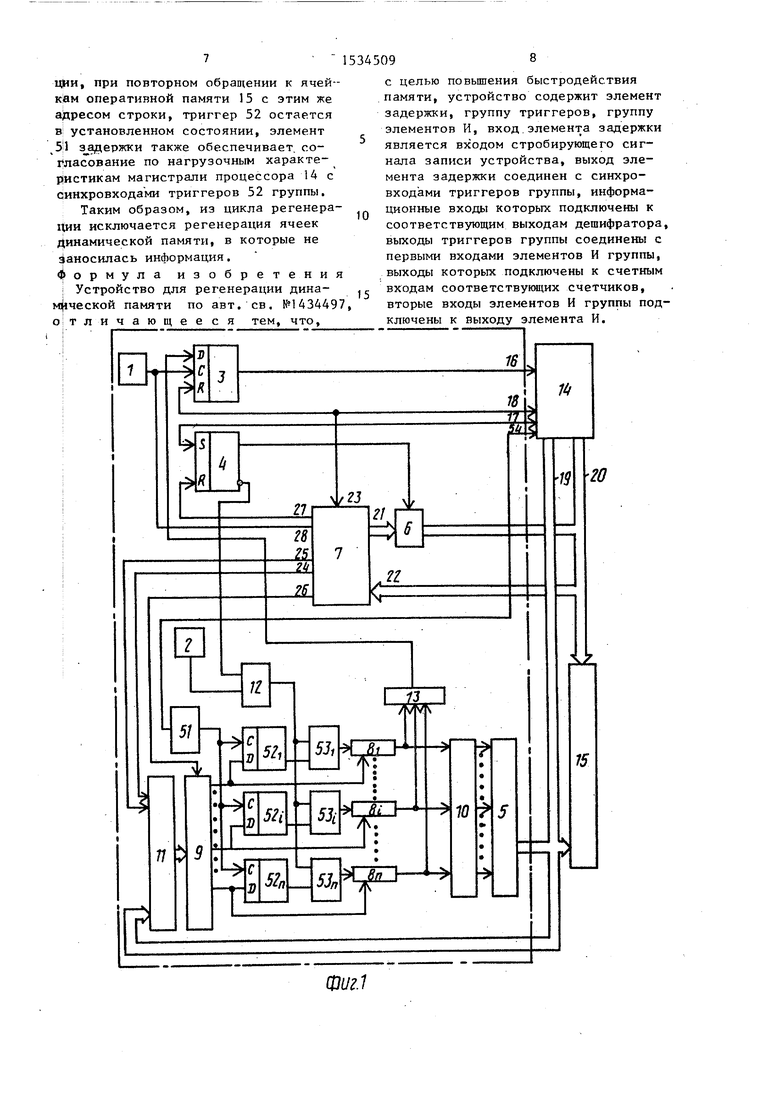

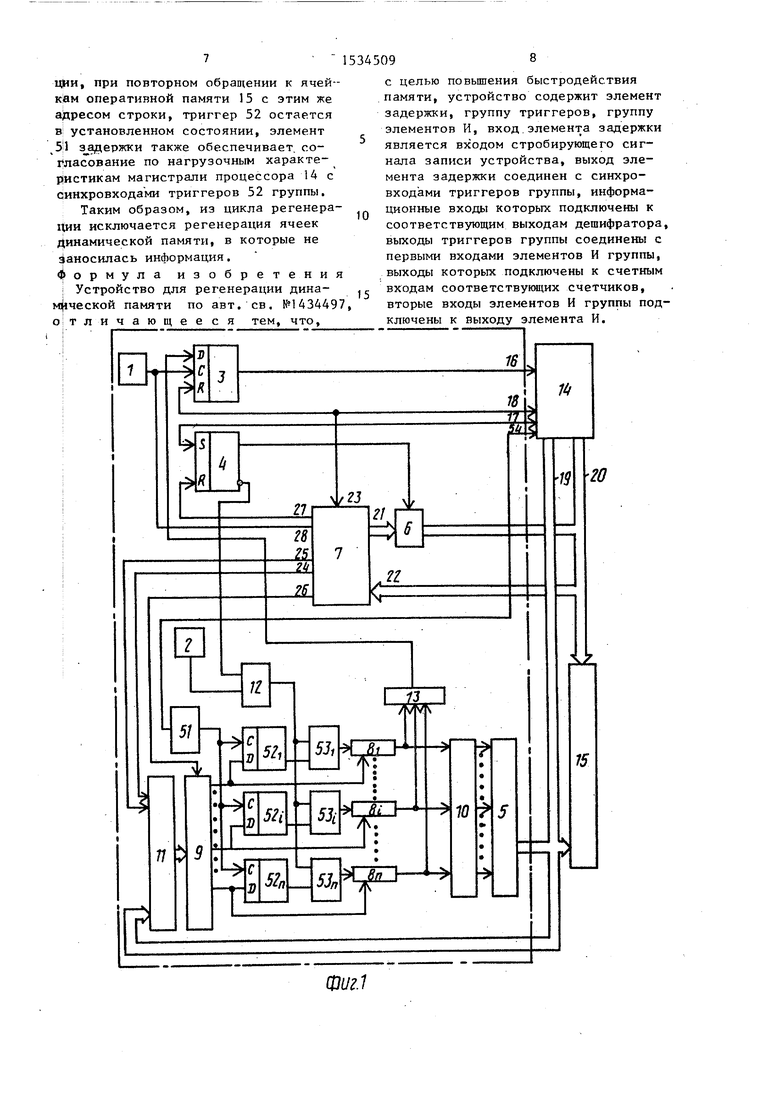

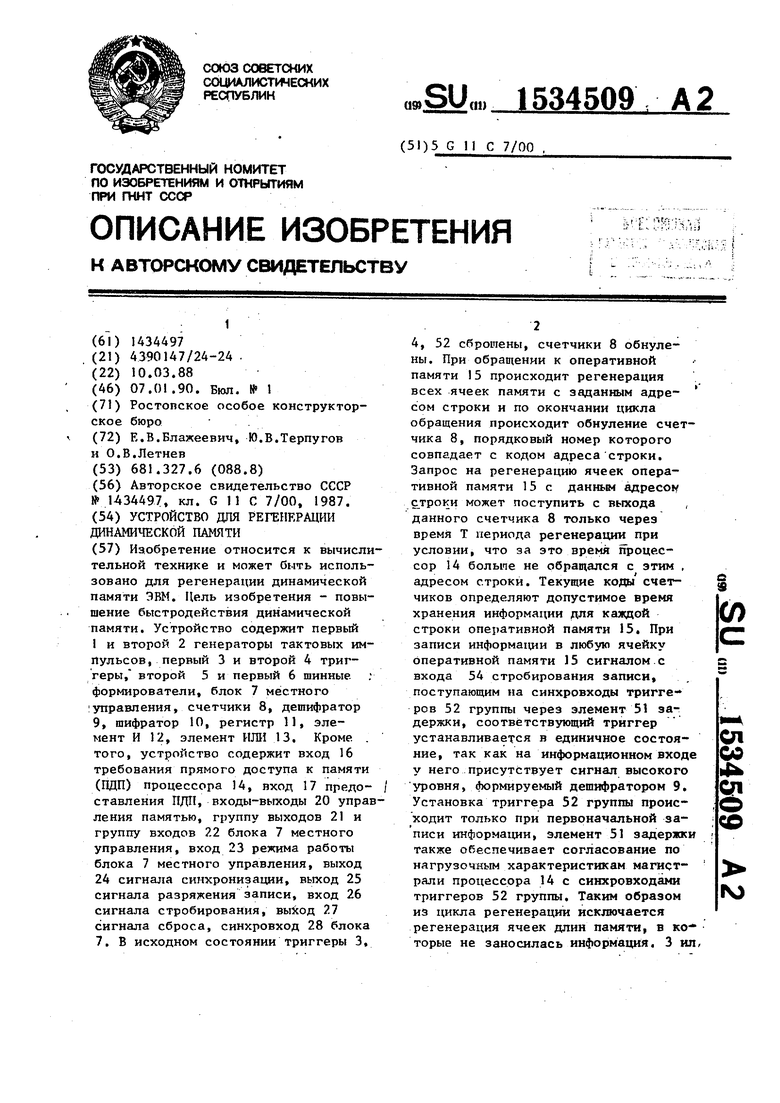

На фиг.1 приведена функциональная схема устройства; на фиг.2 - схема блока местного управления; на фиг.З временная диаграмма работы устройства в режиме регенерации информации.

Устройство содержит первый I и второй 2 генераторы тактовых импульсов, первый 3 и второй 4 триггеры, второй 5 и первый 6 шинные формирователи, блок 7 местного управления, счетчики 8, дешиАратор 9, шифратор 10, регистр 11, элемент И 12, элемент ИЛИ 13. На фиг.1 также приведены элементы DBM, взаимодействующие с устройством: центральный процессор 14 и оперативная память 15. Кроме того, VCTDOUCTBO содепжит выход 16 требования прямого доступа к памяти (ПДП), процессора 14, вход 17 предоставления ПЛП, выход 18 подтверждения захвата канала (ПЗ), адресные входы-выходы 19, входы-выходы 20 управления памятью, группу выходов 21 и группу входов 22 блока 7 местного управления, вход 23 режима работы блока 7 местного управления, выход 24 сигнала синхронизации, выход 25 сигнала разрешения записи, выход 26 сигнала стробнрования выход 27 сигнала сброса, синхровход 28 блока 7 местного управления.

Блок 7 местного управления содержит элементы ИЛИ-НЕ 29-33, элемент НЕ 34, одновнбратор 35, элементы И 36-39, триггеры 40-44, элементы И-НЕ , элемент ИЛИ 48, одновибратор 49 и резистор 50.

Кроме того, устройство содержит элемент 51 задержки, группу 52 триг- .геров, группу 53 элементов И, вход 54 стробирования записи.

Устройство работает следующим образом.

В исходном состоянии триггеры 3, 4, 40-42, 44 и 52 сброшены, триг :гер 43 взведен, счетчики 8 обнулены Импульсы с выхода генератора 2 тактовых импульсов через элемент И 12 и группу элементов И 53 поступают

на счетные входы счетчиков 8, соответствующим адресам строк, к которым было обращение при записи информации в память. На счетные входы

счетчиков 8, к которым не было обращения при записи информации в память, импульсы поступать не будут, так как соответсвующие элементы

группы И 53 заблокированы низкими уровнями сигналов на соответствующих выходах триггеров 52 группы.

При переполнении одного из счетчиков 8 сигнал с выхода его послед5 него разряда через элемент ИЛИ 13 поступает на вход установки триггера 3.

Одновременно на выходе шифратора 10 устанавливается код счетчика 8t0 (от 0 до п), соответствующий коду адреса строки тех ячеек оперативной памяти, для которых истекло время хранения информации и требуется регенерация .

5 По переднему фронту импульса

генератора 1 тактовых импульсов устанавливается триггер 3, на его прямом выходе вырабатывается сигнал 16 требования прямого доступа (ТПД)

о Процессор 14 приостанавливает выполнение операций, освобождает адресную шину 19 и выдает ответный сигнал на вход 17 предоставления ПДП, устанавливающий триггер 4,

с который в свою очередь сбрасывает триггер 3, вырабатывает сигнал на выходе 18 подтверждения захвата ка- . нала (ПЗ), а также открывает тинные формирователи 5 и 6.

0 Сигнал с инверсного выхода триггера 4 запрещает прохождение импульсов генератора 2 тактовых импульсов через элемент И 12 на входы счетчи ков 8. Сигнал с прямого выхода триг5 гера 4 поступает в блок 7 местного управления и разрешает установку триггера 40, который взведется после завершения текущего цикла обращения к оперативной памяти 15 и сня0 тия сигналов синхронизации активного устройства (СИА), синхронизации пассивного устройства (СИП), .поступаю- тщих на входы 22 блока 7 местного управления, положительным перепадом тактового импульса (ТИ) от генератора 1 тактовых импульсов. Сигнал регенерации (РГН) с прямого выхода триггера 40 поступает через шинный формирователь 6 в оперативную па5

10

15

20

25

5 1534509 мять 15 и остается активным в тече

ние всего времени регенерации.

Следующими тактовыми импульсами последовательно взводятся триггер 42, сбрасывается триггер 43 и взводится триггер 44. Сигналы с инверсного выхода триггера 43 и прямого выхода триггера 44, собранные на элементе ИЛИ 48, формируют сигнал СИА, а собранные на элементе И 38 формируют сигнал Ввод. Сигналы СИА и Ввод поступают в оперативную память 15 через шинный формирователь 6 вместе с кодом адреса строки с выхода шинного формирователя 5. Одновременно код адреса строки поступает на информационные входы регистра II. Запись в регистр 11 происходит по переднему фронту сигнала на выходе 24 сигнала синхронизации, поступающего из блока 7 местного управления. В ответ на сигнал Ввод оперативная память 15 формирует сигнал СИП, поступающий на информационный вход триггера 41, который очередным импульсом ТИ устанавливается в единичное состояние, разрешая установку триггера 43 слеующим импульсом ТИ. При этом снимается сигнал Ввод, в ответ на который оперативная память I5 снимает сигнал СИП. Триггер 41 сбрасывается очередным импульсом ТИ, а следующим импульсом ТИ сбрасывается триггер 44 и снимается сигнал СИА. дновибратор 35 выделяет задний фронт и формирует на выходе 26 сигнала стробирования одиночный импульс, который поступает на управляющий вход дешифратора 9, обнуляя тем самым счетчик 8, соответствующий коду, хранящемуся в регистре 11. Одновибратор 49 выделяет передний ронт и формирует импульс отрицательной полярности, обнуляя триггер 0 и через элемент НЕ 34 - триггер 4. Снимаются сигналы РГН и ПЗ, цикл егенерации закончен.

Таким образом, может осуществляться регенерация для любой строки перативной памяти 15. Если в процессе работы устройства ни один из счетчиков 8 не переполнен, т.е. время хранения информации ни для одной строки не вышло, то работа устройства происходит следующим образом.

В режиме обращения к оперативной памяти 15 процессор 14 устанавливает

30

35

40

к 2 н у с р вы Мл щ лу уп си ра ги по го со а Пр вы ни

но ци ад ци ти 7 хо ле ко ст За ти ст но Т чт ше ад

50

.с доп для ти

яч лом пос 52 соо вае как при фор ка при

55

0

5

0

5

4509

0

5

0

на адресной шине 19 код адреса ячейки памяти, а на управляющей шине 20 вырабатываются сигналы управления, поступающие в блок 7 местного управления е входа 22: канальный сигнал синхронизации пассивного устройства (КСИП), канальный сигнал выбора внешнего устройства (КВУ). Младшие разряды кода адреса, являющиеся кодом адреса строки, по сигналу с выхода 24 блока 7 местного управления при наличии разрешающего сигнала на его выходе 25 сигнала разрешения записи записываются в регистр 11. Запрещающий запись сигнал появляется на выходе блока 7 местного управления при обращении процессора I4 не к оперативной памяти 15, а к регистрам внешних устройств. При этом не формируется сигнал на выходе 26 блока 7 местного управления.

Так как при обращении к оперативной памяти 15 происходит регенерация всех ячеек памяти с заданным адресом строки, то по окончании цикла обращения к оперативной памяти 15 по сигналу с ныхода 26 блока 7 местного управления сигналом с выхода дешифратора 9 происходит обнуление счетчика 8, порядковый номер которого совпадает с кодом адреса строки, хранящемся в регистре 11. Запрос на регенерацию ячеек опера- тинной памяти 15 с данным адресом строки может поступить с выхода данного счетчика 8 только через время Т периода регенерации, при условии, что за это время процессор 14 больше не обратится к ячейкам с этим адресом строки.

Текущие коды счетчиков определяют допустимое время хранения информации для каждой строки оперативной памяти is;

При записи информации в любую ячейку оперативной памяти 15 сигналом с входа 54 стробирования записи поступающим на синхровходы триггеров 52 группы через элемент 51 задержки, соответствующий триггер устанавливается в единичное состояние, так как на информационном входе у него присутствует сигнал высокого уровня, формируемый дешифратором 9. Установка триггера группы 52 происходит при первоначальной записи информа

ции, при повторном обрап1ении к ячейкам оперативной памяти 15 с этим же адресом строки, триггер 52 остается в установленном состоянии, элемент ч51 задержки также обеспечивает согласование по нагрузочным характеристикам магистрали процессора 14 с синхровходами триггеров 52 группы.

Таким образом, из цикла регенерации исключается регенерация ячеек динамической памяти, в которые не заносилась информация. Формула изобретения

Устройство для регенерации динамической памяти по авт. св. №1434497 отличающееся тем, что,

с целью повышения быстродействия памяти, устройство содержит элемент задержки, группу триггеров, группу элементов И, вход элемента задержки является входом стробирующего CHI- нала записи устройства, выход элемента задержки соединен с синхровходами триггеров группы, информационные входы которых подключены к соответствующим выходам дешифратора, выходы триггеров группы соединены с первыми входами элементов И группы, выходы которых подключены к счетным входам соответствующих счетчиков, вторые входы элементов И группы подключены к выходу элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для регенерации динамической памяти | 1987 |

|

SU1434497A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Электронная вычислительная машина с прямым доступом в память | 1990 |

|

SU1751776A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| ЭВМ | 1990 |

|

RU2024928C1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных гиперкубических циклических системах | 2019 |

|

RU2718166C1 |

Изобретение относится к вычислительной технике и может быть использовано для регенерации динамической памяти ЭВМ. Цель изобретения - повышение быстродействия динамической памяти. Устройство содержит первый 1 и второй 2 генераторы тактовых импульсов, первый 3 и второй 4 триггеры, второй 5 и первый 6 шинные формирователи, блок 7 местного управления, счетчики 8, дешифратор 9, шифратор 10, регистр 11, элемент И 12, элемент ИЛИ 13. Кроме того, устройство содержит вход 16 требования прямого доступа к памяти (ПДП) процессора 14, вход 17 предоставления ПДП, входы-выходы 20 управления памятью, группу выходов 21 и группу входов 22 блока 7 местного управления, вход 23 режима работы блока 7 местного управления, выход 24 сигнала синхронизации, выход 25 сигнала разряжения записи, выход 26 сигнала стробирования, выход 27 сигнала сброса, синхровход 28 блока 7. В исходном состоянии триггеры 3, 4, 52 сброшены, счетчики 8 обнулены. При обращении к оперативной памяти 15 происходит регенерация всех ячеек памяти с заданным адресом строки, и по окончании цикла обращения происходит обнуление счетчика 8, порядковый номер которого совпадает с кодом адреса строки. Запрос на регенерацию ячеек оперативной памяти 15 с данным адресом строки может поступить с выхода данного счетчика 8 только через время T периода регенерации при условии, что за это время процессор 14 больше не обращался с этим адресом строки. Текущие коды счетчиков определяют допустимое время хране

черняков владимир сергеевич+7552080реRмаNеNт мемоRY13 310141 харьков13 310202 харьков, пр.л.свободы 39-232

13 310070 харьков, старошишковская 12-103Изобретение относится к области автоматики и вычислительной техники и является усовершенствованием постоянного запоминающего устройства по а.с. N 746730. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что устройство содержит ключевой элемент 10 и триггер 11. Элемент 10 и триггер 11 автоматически обеспечивают определенную п

Фиг.1

14

«nJbTUUUULJbrUlJVlJlФи.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-01-07—Публикация

1988-03-10—Подача