Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах, работающих в реальном времени, для выполнения операций сложения, вычитания, умножения и деления чисел, представленных в форме с плавающей запятой.

Цель изобретения - расширение функциональных возможностей за счет выполнения операций умножения и деления.

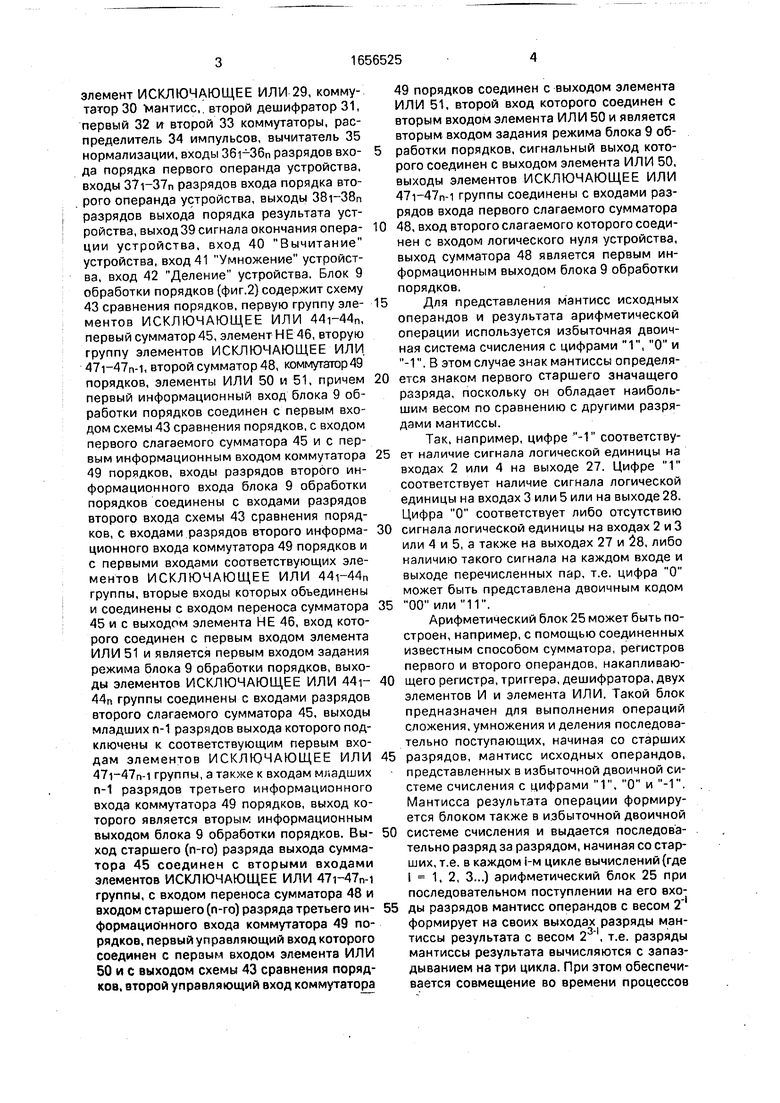

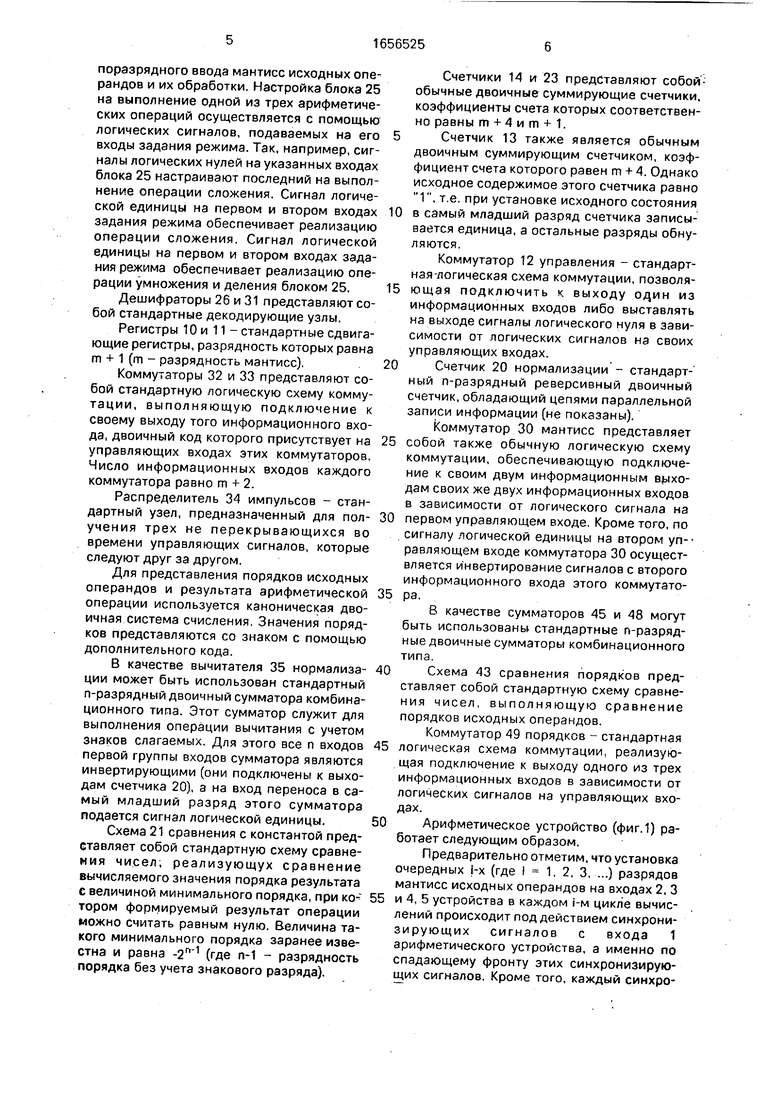

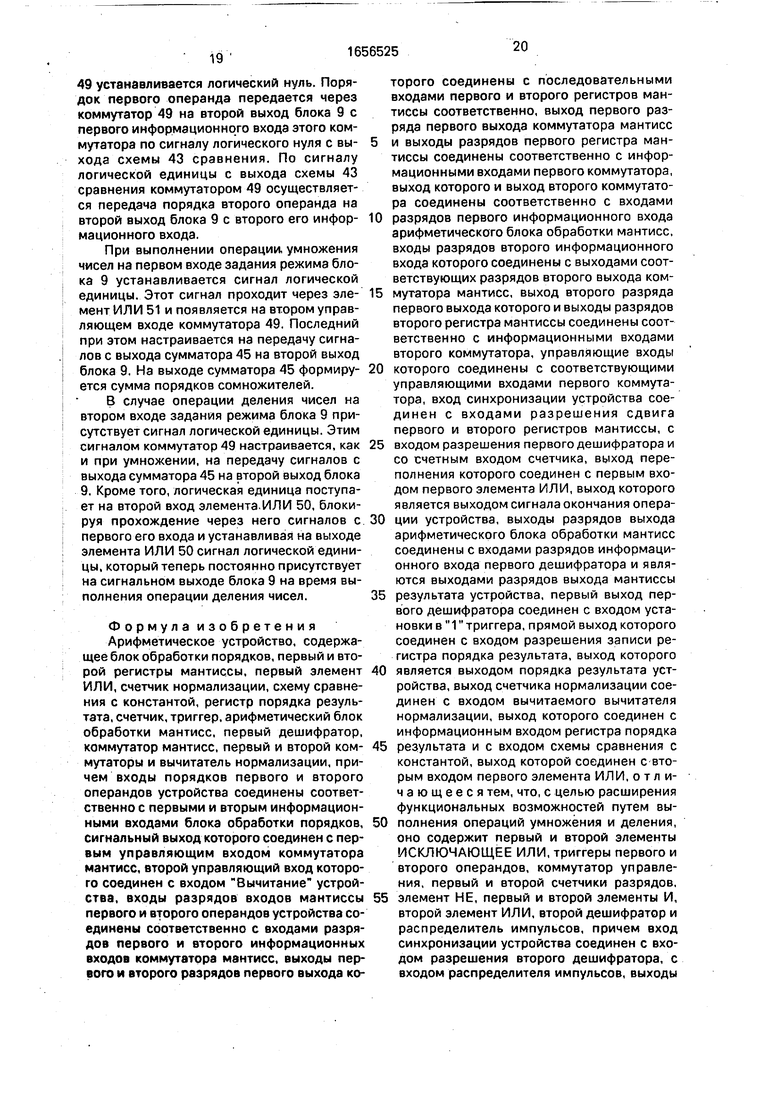

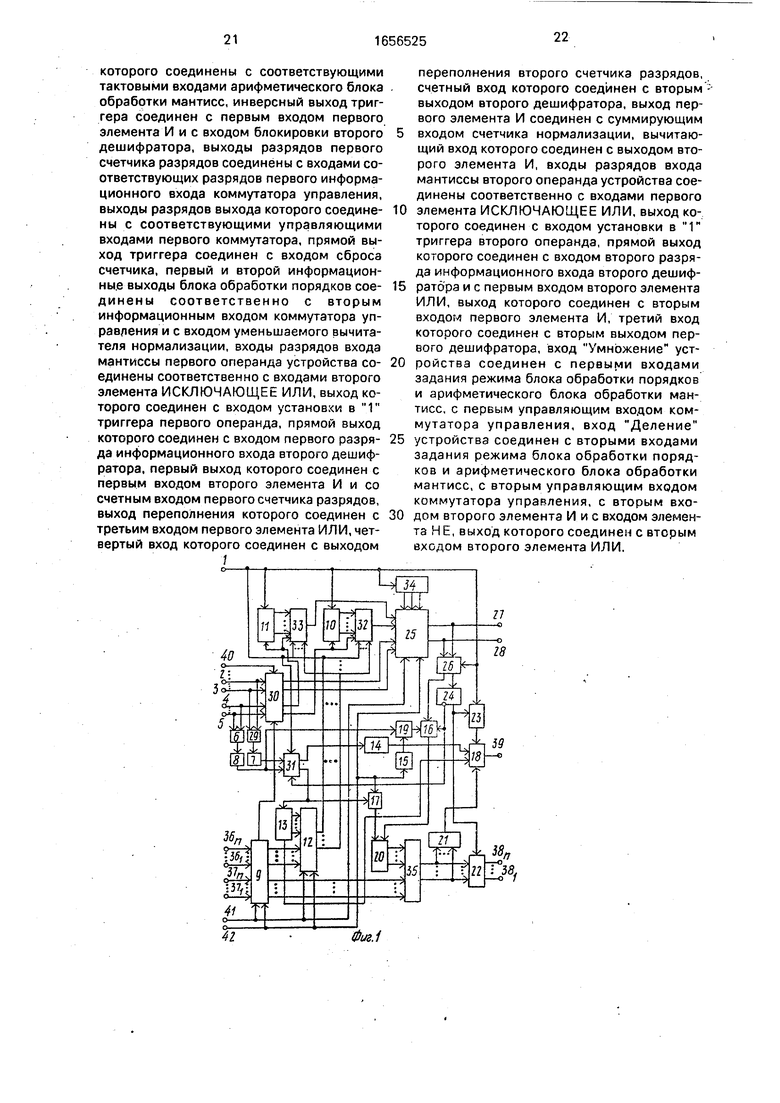

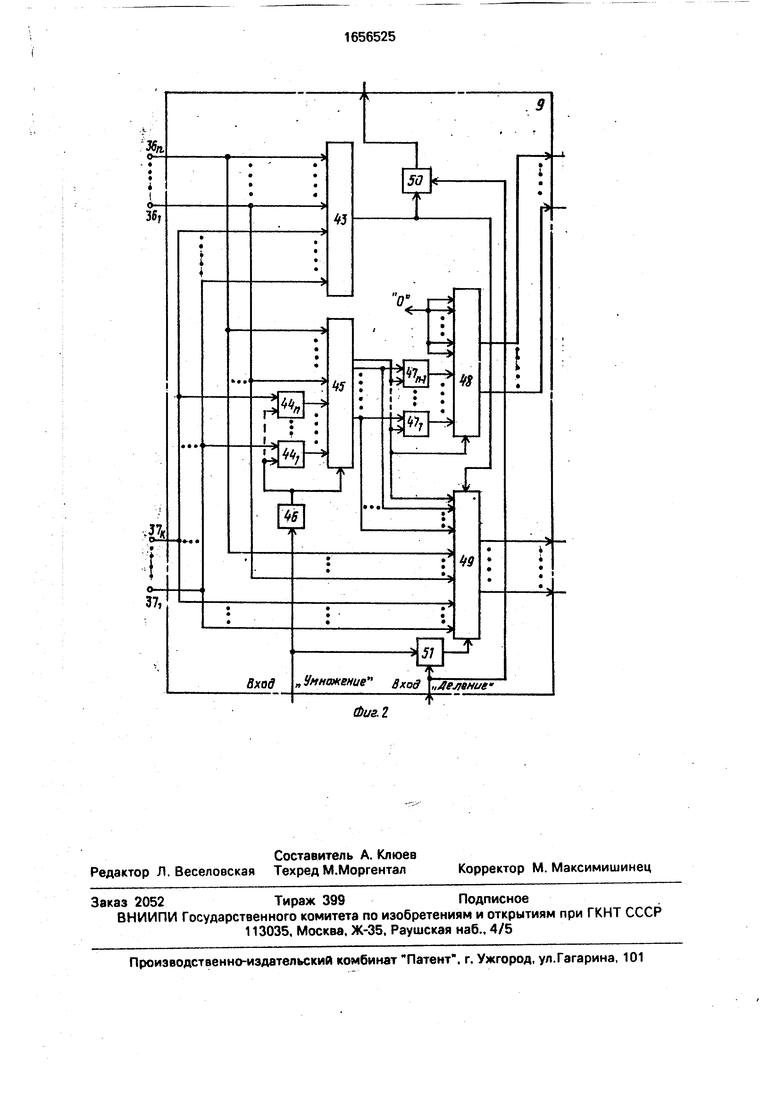

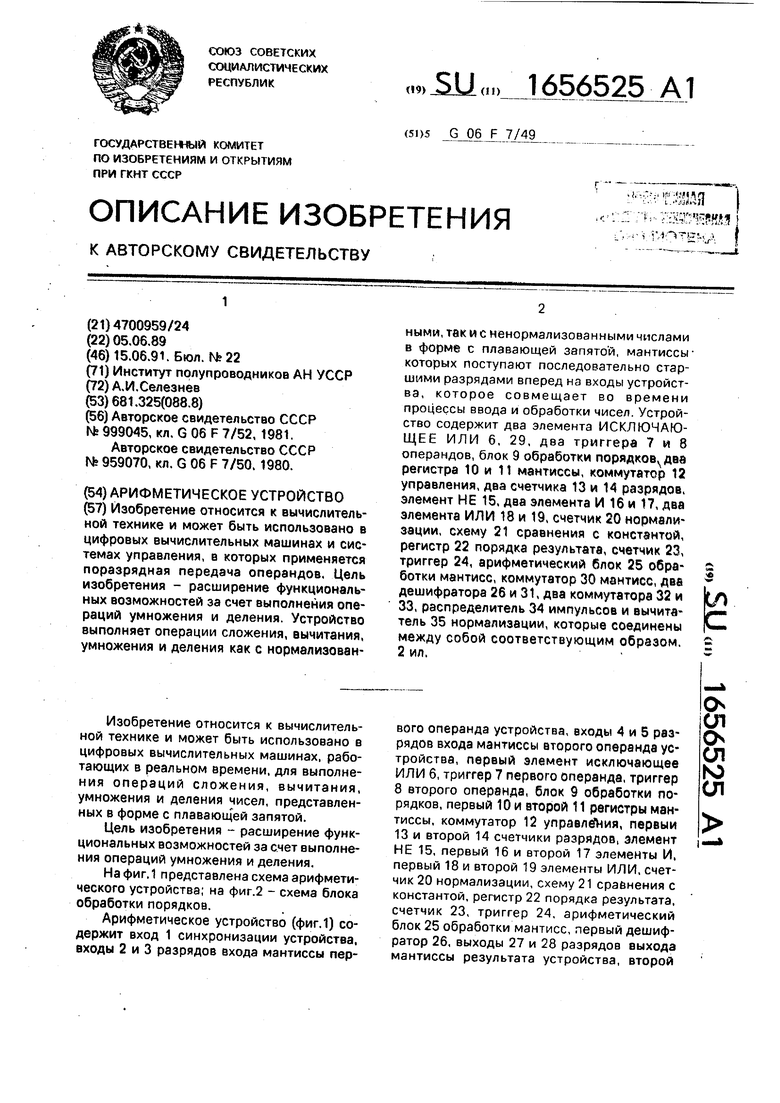

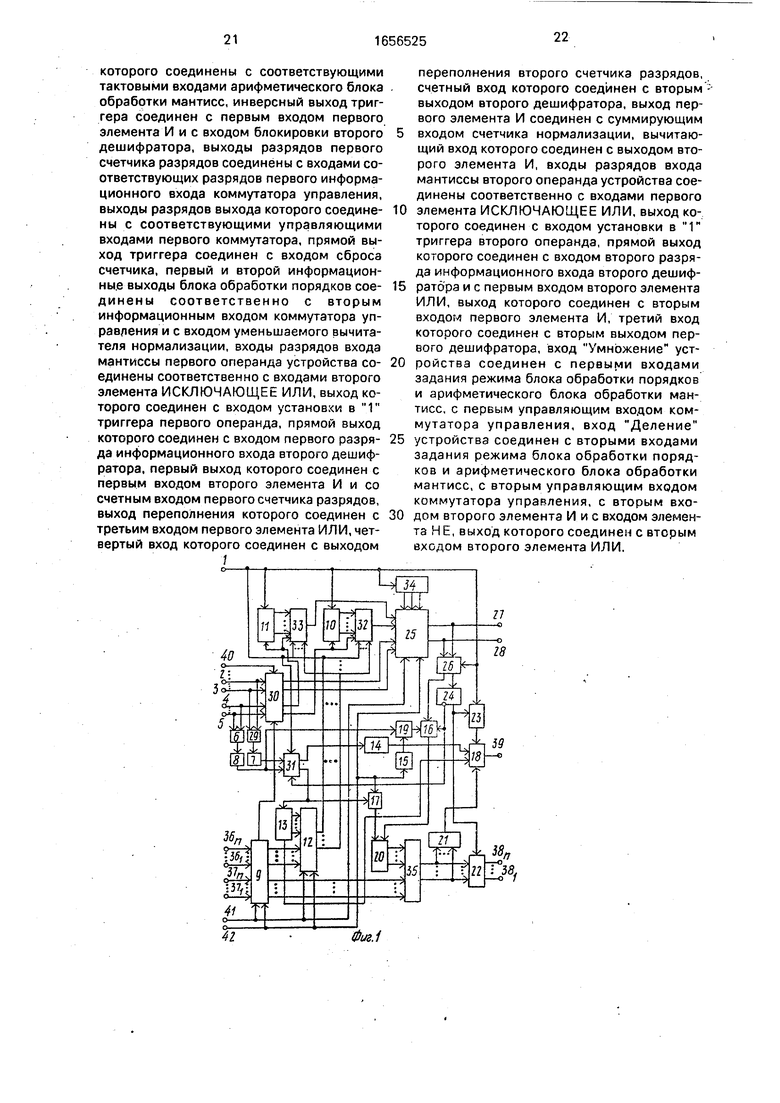

На фиг. 1 представлена схема арифметического устройства; на фиг.2 - схема блока обработки порядков.

Арифметическое устройство (фиг.1) содержит вход 1 синхронизации устройства, входы 2 и 3 разрядов входа мантиссы первого операнда устройства, входы 4 и 5 разрядов входа мантиссы второго операнда устройства, первый элемент исключающее ИЛИ б, триггер 7 первого операнда, триггер 8 второго операнда, блок 9 обработки порядков, первый 10 и второй 11 регистры мантиссы, коммутатор 12 управления, первый 13 и второй 14 счетчики разрядов, элемент НЕ 15, первый 16 и второй 17 элементы И, первый 18 и второй 19 элементы ИЛИ, счетчик 20 нормализации,схему 21 сравнения с константой, регистр 22 порядка результата, счетчик 23, триггер 24. арифметический блок 25 обработки мантисс, первый дешифратор 26, выходы 27 и 28 разрядов выхода мантиссы результата устройства, второй

О СП Os

ел ю ел

элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 29, коммутатор 30 Мантисс, второй дешифратор 31, первый 32 и второй 33 коммутаторы, распределитель 34 импульсов, вычитатель 35 нормализации, входы разрядов входа порядка первого операнда устройства, входы разрядов входа порядка второго операнда устройства, выходы 38i-38n разрядов выхода порядка результата устройства, выход 39 сигнала окончания операции устройства, вход 40 Вычитание устройства, вход 41 Умножение устройства, вход 42 Деление устройства. Блок 9 обработки порядков (фиг.2) содержит схему 43 сравнения порядков, первую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 44i-44n, первый сумматор 45, элемент НЕ 46, вторую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 47i-47n-i, второй сумматор 48, коммутатор49 порядков, элементы ИЛИ 50 и 51, причем первый информационный вход блока 9 обработки порядков соединен с первым входом схемы 43 сравнения порядков, с входом первого слагаемого сумматора 45 и с первым информационным входом коммутатора

49порядков, входы разрядов второго информационного входа блока 9 обработки порядков соединены с входами разрядов второго входа схемы 43 сравнения порядков, с входами разрядов второго информационного входа коммутатора 49 порядков и с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 44i-44n группы, вторые входы которых объединены и соединены с входом переноса сумматора 45 и с выходом элемента НЕ 46, вход которого соединен с первым входом элемента ИЛИ 51 и является первым входом задания режима блока 9 обработки порядков, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 44i- 44П группы соединены с входами разрядов второго слагаемого сумматора 45, выходы младших п-1 разрядов выхода которого подключены к соответствующим первым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 47i-47n-i группы, а также к входам мпадших п-1 разрядов третьего информационного входа коммутатора 49 порядков, выход которого является вторым информационным выходом блока 9 обработки порядков. Выход старшего (n-го) разряда выхода сумматора 45 соединен с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 47i-47n-i группы, с входом переноса сумматора 48 и входом старшего (n-го) разряда третьего информационного входа коммутатора 49 порядков, первый управляющий вход которого соединен с первым входом элемента ИЛИ

50и с выходом схемы 43 сравнения порядков, второй управляющий вход коммутатора

49 порядков соединен с выходом элемента ИЛИ 51, второй вход которого соединен с вторым входом элемента ИЛИ 50 и является вторым входом задания режима блока 9 обработки порядков, сигнальный выход которого соединен с выходом элемента ИЛИ 50, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 47i-47n-i группы соединены с входами разрядов входа первого слагаемого сумматора

0 48, вход второго слагаемого которого соединен с входом логического нуля устройства, выход сумматора 48 является первым информационным выходом блока 9 обработки порядков.

5 Для представления мантисс исходных операндов и результата арифметической операции используется избыточная двоичная система счисления с цифрами 1, О и -1. В этом случае знак мантиссы определя0 ется знаком первого старшего значащего разряда, поскольку он обладает наибольшим весом по сравнению с другими разрядами мантиссы.

Так, например, цифре -1 соответству5 ет наличие сигнала логической единицы на входах 2 или 4 на выходе 27, Цифре 1 соответствует наличие сигнала логической единицы на входах 3 или 5 или на выходе 28. Цифра О соответствует либо отсутствию

0 сигнала логической единицы на входах 2 и 3 или 4 и 5, а также на выходах 27 и 28, либо наличию такого сигнала на каждом входе и выходе перечисленных пар, т.е. цифра О может быть представлена двоичным кодом

5 00 или 11.

Арифметический блок 25 может быть построен, например, с помощью соединенных известным способом сумматора, регистров первого и второго операндов, накапливаю0 щего регистра, триггера, дешифратора, двух элементов И и элемента ИЛИ. Такой блок предназначен для выполнения операций сложения, умножения и деления последовательно поступающих, начиная со старших

5 разрядов, мантисс исходных операндов, представленных в избыточной двоичной системе счисления с цифрами 1, О и -1. Мантисса результата операции формируется блоком также в избыточной двоичной

0 системе счисления и выдается последовательно разряд за разрядом, начиная со старших, т.е. в каждом l-м цикле вычислений (где 1 1,2, 3...) арифметический блок 25 при последовательном поступлении на его вхо5 ды разрядов мантисс операндов с весом формирует на своих выходах разряды мантиссы результата с весом , т.е. разряды мантиссы результата вычисляются с запаздыванием на три цикла. При этом обеспечивается совмещение во времени процессов

поразрядного ввода мантисс исходных операндов и их обработки. Настройка блока 25 на выполнение одной из трех арифметических операций осуществляется с помощью логических сигналов, подаваемых на его входы задания режима. Так, например, сигналы логических нулей на указанных входах блока 25 настраивают последний на выполнение операции сложения. Сигнал логической единицы на первом и втором входах задания режима обеспечивает реализацию операции сложения. Сигнал логической единицы на первом и втором входах задания режима обеспечивает реализацию операции умножения и деления блоком 25.

Дешифраторы 26 и 31 представляют собой стандартные декодирующие узлы.

Регистры 10 и 11 - стандартные сдвигающие регистры, разрядность которых равна m + 1 (m - разрядность мантисс).

Коммутаторы 32 и 33 представляют собой стандартную логическую схему коммутации, выполняющую подключение к своему выходу того информационного входа, двоичный код которого присутствует на управляющих входах этих коммутаторов. Число информационных входов каждого коммутатора равно m + 2.

Распределитель 34 импульсов - стандартный узел, предназначенный для получения трех не перекрывающихся во времени управляющих сигналов, которые следуют друг за другом.

Для представления порядков исходных операндов и результата арифметической операции используется каноническая двоичная система счисления. Значения порядков представляются со знаком с помощью дополнительного кода.

В качестве вычитателя 35 нормализации может быть использован стандартный n-разрядный двоичный сумматора комбинационного типа. Этот сумматор служит для выполнения операции вычитания с учетом знаков слагаемых. Для этого все п входов первой группы входов сумматора являются инвертирующими (они подключены к выходам счетчика 20), а на вход переноса в самый младший разряд этого сумматора подается сигнал логической единицы.

Схема 21 сравнения с константой представляет собой стандартную схему сравнения чисел, реализующух сравнение вычисляемого значения порядка результата с величиной минимального порядка, при котором формируемый результат операции можно считать равным нулю. Величина такого минимального порядка заранее известна и равна (где п-1 - разрядность порядка без учета знакового разряда).

Счетчики 14 и 23 представляют собой обычные двоичные суммирующие счетчики, коэффициенты счета которых соответственно равны m + 4 и m + 1.

5Счетчик 13 также является обычным

двоичным суммирующим счетчиком, коэффициент счета которого равен m + 4. Однако исходное содержимое этого счетчика равно 1, т.е. при установке исходного состояния

0 в самый младший разряд счетчика записывается единица, а остальные разряды обнуляются.

Коммутатор 12 управления - стандартная логическая схема коммутации, позволя5 ющая подключить ч выходу один из информационных входов либо выставлять на выходе сигналы логического нуля в зависимости от логических сигналов на своих управляющих входах.

0Счетчик 20 нормализации - стандартный n-разрядный реверсивный двоичный счетчик, обладающий цепями параллельной записи информации (не показаны).

Коммутатор 30 мантисс представляет

5 собой также обычную логическую схему коммутации, обеспечивающую подключение к своим двум информационным выходам своих же двух информационных входов в зависимости от логического сигнала на

0 первом управляющем входе. Кроме того, по сигналу логической единицы на втором уп- равляющем входе коммутатора 30 осуществляется инвертирование сигналов с второго информационного входа этого коммутато5 ра.

В качестве сумматоров 45 и 48 могут быть использованы стандартные п-разряд- ные двоичные сумматоры комбинационного типа

0Схема 43 сравнения порядков представляет собой стандартную схему сравнения чисел, выполняющую сравнение порядков исходных операндов.

Коммутатор 49 порядков - стандартная

5 логическая схема коммутации, реализующая подключение к выходу одного из трех информационных входов в зависимости от логических сигналов на управляющих входах.

0Арифметическое устройство (фиг.1) работает следующим образом.

Предварительно отметим, что установка очередных i-x (где I 1. 2, 3, ...) разрядов мантисс исходных операндов на входах 2, 3

5 и 4, 5 устройства в каждом i-м цикле вычислений происходит под действием синхронизирующих сигналов с входа 1 арифметического устройства, а именно по спадающему фронту этих синхронизирующих сигналов. Кроме того, каждый синхронизирующий сигнал своим спадающим фронтом выполняет сдвиги информации на один разряд в регистрах 10 и 11, инкремен- тирует содержимое счетчика 23 (если на входе сброса этого счетчика присутствует сигнал логической единицы) и запускает распределитель 34 Перед началом счета на входы 40, 41 и 42 устройства подают код необходимой арифметической операции и удерживают этот код до получения окончательного результата вычислений. Сигнал логического нуля с входа 42, пройдя элемент НЕ 15, устанавливается логической единицей на втором входе элемента ИЛИ 19 и блокирует прохождение сигналов логических единиц с первого входа элемента ИЛИ 19 через него, удерживая на выходе элемента ИЛИ 19 логическую единицу, которая постоянно будет присутствовать на втором входе элемента И 16 при выполнении устройством операций сложения, вычитания и умножения.

Рассмотрим работу арифметического устройства отдельно для каждой арифметической операции. Предлагаемое устройство позволяет выполнять арифметические операции как с нормализованными, так и ненормализованными исходными операндами, а также можэт обрабатывать ситуации, когда одна либо обе мантиссы исходных операндов равны нулю.

Для реализации операции сложения чисел на входы 40, 41 и 42 устройства подаются сигналы логических нулей. При этом коммутатор 12 по сигналам логических нулей на своих управляющих входах настраивается для передачи информации с второго информационного входа на свой выход, а блок 9 - для выдачи большего порядка исходных операндов на второй информационный выход. Перед проведением вычислений в нулевое состояние сбрасываются триггеры 7, 8 и 24, регистры 10, 11 и 22 и счетчик 14. Предварительно также в счетчик 20 заносится число -4 в дополнительном коде, а блок 25 и счетчик 13 приводятся в исходное состояние.

На входы 36i-36n устройства поступает двоичный код порядка первого операнда, а на входы 37i-37n - двоичный код порядка второго операнда. Блок 9 по поступившим кодам порядков вычисляет двоичный код модуля разности порядков, который устанавливается на его первом информационном выходе. Через коммутатор 12 двоичный код модуля разности порядков подается на управляющие входы коммутаторов 32 и 33, задавая им двоичный код номера из информационного эхода. подключаемого к их выходам Кроме того, блок 9 определяет

больший порядок из двух поступивших. При этом на сигнальном выходе блока 9 формируется сигнал логического нуля, если порядок второго операнда не превышает

порядка первого операнда. В противном же случае на сигнальном выходе блока 9 появляется сигнал логической единицы. На втором информационном выходе блока 9 устанавливается двоичный код большего

0 порядка, а вслучае их равенства -двоичный код порядка первого операнда.

Одновременно с поступлением порядков исходных операндов на входы 2, 3 и 4, 5 устройства подаются двоичные коды пер5 вых старших (с весом 2 ) разрядов мантисс этих операндов-. По сигналу логического нуля на своем первом управляющем входе коммутатор 30 (порядок второго операнда не превышает порядка первого операнда)

0 осуществляет передачу сигналов с входоь 4 и 5 устройства на входы последовательного ввода регистров 10 и 11 соответственно и на первые информационные входы коммутаторов 32 и 33 соответственно. Сигналы с вхо5 дов 2 и 3 устройства при этом передаются коммутатором 30 на второй информационный вход блока 25. Если же с сигнального выхода блока 9 будет выдан сигнал логической единицы (порядок второго операнда

0 при сложении чисел превышает порядок первого операнда) на первый управляющий вход коммутатора 30, то последний будет выполнять передачу сигналов с входов 4 и 5 устройства на второй информационный

5 вход блока 25, а сигналы с входов 2 и 3 устройства при этом будут передаваться коммутатором 30 на входы последовательного ввода регистров 10 и 11 соответственно и на первые информационные входы

0 коммутаторов 32 и 33 соответственно. Сигнал логического нуля с входа 40 устройства присутствует на втором управляющем входе коммутатора 30 и запрещает ему производить передачу сигналов с входов 4 и 5 уст5 ройства с инверсией

В арифметическом устройстве при суммировании процесс выравнивания порядков, который необходим для сложения разрядов одного веса, совмещен во време0 ни с процессом поразрядного ввода мантисс операндов. Это достигается задержкой в поступлении на первый информационный вход блока 25 двоичных кодов разрядов мантиссы, обладающей меньшим порядком,

5 по отношению к поступлению двоичных кодов разрядов другой мантиссы на второй информационный вход блока 25. Величина задержки равняется модулю разности порядков операндов, двоичный код которого формируется на первом информационном

выходе блока 9 и через коммутатор 12 устанавливается на управляющих входах коммутаторов 32 и 33. Если модуль разности порядков равен нулю (порядки равны), то двоичные коды разрядов мантиссы второго операнда подаются на первый информационный вход блока 25 без задержки с первого выхода коммутатора 30 через коммутаторы 32 и 33, которые при этом передают на выход сигналы с первого своего информационного входа. Если же, например, модуль разности порядков равен единице, то коды разрядов мантиссы, имеющей меньший порядок, возникают на первом информационном входе блока 25 с задержкой на один цикл вычислений по сравнениюс разрядами на втором информационном входе блока 25. В этом случае используется информация с выходов первых разрядов регистров 10 и 11, которая передается через вторые информационные входы коммутаторов 32 и 33. Когда же модуль разности порядков равен m + 1, то задержка составляет m + 1 цикл вычислений и при этом для подачи на первый информационный вход блока 25 используется информация с выходов (т + 1)-х разрядов регистров 10 и 11, которая передается через (т + 2)-е информационные входы коммутаторов 32 и 33. Для тех случаев, когда значе ние модуля разности порядков превышает m + 1, коммутаторы 32 и 33 на своих выходах устанавливают сигналы логических нулей.

Блок 25 выполняет суммирование поступивших на его входы разрядов мантисс слагаемых в каждом i-м цикле вычислений под управлением трех сигналов от распределителя 34. Последний под действием каждого i-ro синхронизирующего сигнала на своем входе вырабатывает следующие друг за другом и не перекрывающиеся во времени три управляющих сигнала, которые воздействуют на тактирующие входы блока 25. На выходе этого блока формируются коды разрядов мантиссы суммы с запаздыванием на три цикла вычислений. По каждому i-му синхронизирующему сигналу с входа 1 через выходы 27 и 28 выдаются из арифметического устройства коды разрядов мантиссы результата, которые при этом анализируются дешифратором 26. Причем, если анализируемой цифрой мантиссы результата является О, то при наличии-ло- гической единицы синхронизирующего сигнала на входе разрешения дешифратора 26 последний формирует на своем втором выходе сигнал логической единицы. Этот сигнал поступает на третий вход элемента И 16, на первом и втором входах которого установлены логические единицы. Логическая единица на первом входе элемента И 16

присутствует до момента получения первого значащего разряда мантиссы результата на выходе блока 25. Сигнал логической единицы с второго выхода дешифратора 26 про- 5 ходит через элемент И 16 и поступает на суммирующий вход счетчика 20, увеличивая его содержимое на единицу. При помощи вычитателя 35 определяется разность между числом (уменьшаемое) с второго выхода

0 блока 9 и содержимым (вычитаемое) счетчика 20. Таким образом, по каждому разряду вычисляемой блоком 25 мантиссы результата, начиная с первого старшего разряда, равного нулю, осуществляется уменьшение

5 большего порядка на единицу. В случае получения первого значащего разряда мантиссы результата, равного 1 или -1, дешифратор 26 по синхронизирующему сигналу с входа 1 выдает сигнал логической

0 единицы на своем первом выходе, устанавливая триггер 24 в единичное состояние. После этого на первом входе элемента И 16 появляется сигнал логического нуля с инверсного выхода триггера 24, блокируя вы5 работку выходных сигналов дешифратором 31 и прохождение возможных последующих сигналов логической единицы через .элемент И 16 с второго выхода дешифратора 26. Сигнал логической единицы с единичного

0 выхода триггера 24 снимает запрещение счетного режима для счетчика 23, происходит запись в регистр 22 значения откорректированного на вычитателе 35 порядка результата. Вследствие этого на выходах

5 устанавливается порядок еще вычисляемой, но уже нормализованной мантиссы результата. Под действием последующих синхронизирующих сигналов счетчика 23 осуществляется отсчет числа

0 выдаваемых разрядов нормализованной мантиссы результата. Вычисления разрядов мантиссы результата устройством прекращаются, когда на выходе переполнения счетчика 23 появляется сигнал логической

5 единицы, который проходит через элемент ИЛИ 18 и появляется на выходе 39 устройства, что служит признаком окончания операции. При этом через выходы 27 и 28 устройства выдается m + 1 разряд нормали0 зованной мантиссы результата.

Если же в процессе одновременного вычисления мантиссы результата, ее нормализации и соответствующей корректировки порядка результата значение этого порядка

5 на выходах вычитателя 35 становится равным значению минимального допустимого порядка, то схема 2 1 сравнения определяет это и на ее выходе устанавливается сигнал логической единицы. Этот сигнал попадает на второй вход элемента ИЛИ 18, и пройдя

через этот элемент, появляется на выходе 39, свидетельствуя о том, что операция закончена.

Для случая, когда обе мантиссы исходных операндов равны нулю, формирование сигнала конца операции на выходе 39 устройства может происходить и по-иному.

Поскольку мантиссы операндов равны нулю, триггеры 7 и 8 не будут устанавливаться в единичное состояние, так как на выхо- дахэлементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и 29 не будут возникать сигналы логических единиц. В этих условиях осуществляется отсчет числа сигналов логических единиц с второго выхода дешифратора 31с помощью счетчика 14 до выработки последним на своем выходе переполнения сигнала логической единицы. Выработка выходных сигналов дешифратором 31 производится под действием стробирующих. сигналов на одноименном входе этого дешифратора, куда стробирующие сигналы подаются с входа 1 устройства. С выхода переполнения счетчика 14 сигнал логической единицы приходит на четвертый вход элемента ИЛИ 18 и, пройдя через него, устанавливается на выходе 39,

При выполнении арифметическим устройством операции вычитания чисел на входе 40 устройства необходимо установить сигнал логической единицы. Такой сигнал поступает на второй управляющий вход коммутатора 30, который в этой ситуации будет инвертировать коды цифр разрядов мантиссы второго операнда со своей второй группы входов, что достаточно для реализации операции вычитания чисел, представляемых в избыточной двоичной системе счисления. Предварительная же установка устройства в исходное состояние и выполнение вычитания осуществляется в остальном аналогично операции сложения чисел. Затраты времени, выраженные в циклах вычисления ten на получение суммы (разности) двух операндов с помощью предлагаемого устройства, находятся в диапазоне значений:

m + 3 ten 2m + 3.

Операция умножения чисел арифметическим устройством выполняется, если на входе 41 присутствует сигнал логической единицы, а на входах 40 и 42 - сигналы логических нулей. В этой ситуации коммутатор 12 на всех своих выходах разрядов устанавливает сигналы логических нулей, а блок 9 настраивается таким образом, чтобы на второй выход выдавать сумму порядков исходных операндов. Перед выполнением счета в нулевое состояние сбрасываются триггеры 7. 8 и 24, регистры 10, 11 и 22 и

счетчик 14. Предварительно также в счетчик 20 заносится число -4 в дополнительном коде, а блок 25 и счетчик 13 приводятся в исходное состояние.

Процесс вычисления произведения, как

и процесс вычисления суммы, начинается с того, что на входы 36i-36n устройства поступает двоичный код порядка первого операнда, а на входы 37i-37n - двоичный код

0 порядка второго операнда. Блок 9 формирует на втором выходе сумму поступивших на его входы порядков сомножителей. Эта сумма порядков сомножителей подается на вход уменьшаемого вычитателя 35 для по5 следующих преобразований в соответствии со значениями разрядов мантиссы произведения, которые в каждом цикле вычислений выдаются из блока 25.

Одновременно с установкой порядков

0 сомножителей на входы 2, 3 и 4, 5 устройства подаются двоичные коды первых старших (с весом ) разрядов мантисс исходных операндов. В зависимости от логического значения сигнала на первом уп5 равляющем входе коммутатора 30 двоичные коды разрядов мантиссы одного из сомножителей поступают на первый информационный вход блока 25 через коммутаторы 30,

32и 33, а двоичные коды разрядов мантиссы 0 другого из сомножителей подаются на второй информационный вход блока 25 только через коммутатор 30. У коммутаторов 32 и

33к выходам подключены их первые информационные входы, поскольку на управляю5 щих входах этих коммутаторов присутствуют сигналы логических нулей с выходов коммутатора 12. В остальном же процесс вычисления произведения аналогичен процессу получения суммы чисел в уст0 ройстве. Обработка ситуации, когда оба сомножителя равны нулю, происходит так же, как и при сложении. Однако возможны ситуации, когда мантисса одного из сомножителей равна нулю. Рассмотрим сначала

5 тот случай, когда мантисса первого операнда равна нулю. При этом независимо от состояния триггера 8, а следовательно, независимо от значения логического сигнала на входе второго разряда входа дешиф0 ратораЗ и при нулевом логическом сигнале на входе первого разряда входа этого дешифратора последний по каждому строби- рующему сигналу со входа 1 устройства формирует на своем втором выходе счетные

5 сигналы логических единиц для счетчика 14. Поэтому работа арифметического устройства может быть окончена по сигналу логической единицы на выходе переполнения счетчика 14. Сигнал с выхода переполнения счетчика 14. пройдя через элемент ИЛИ 18,

появляется на выходе 39 устройства, свидетельствуя о том, что операция закончена. Но поскольку разряды мантиссы произведения равны нулю в данной ситуации, окончание работы арифметического устройства может произойти раньше, чем счетчик 14 выдает сигнал переполнения, если значение порядка на выходе вычитателя 35 станет равным значению минимально допустимого порядка, а это будет определено схемой 21 срав- нения. Это возможно ввиду того, что по каждому нулевому разряду мантиссы произведения сигналом логической единицы с второго выхода дешифратора 26, проходящему через элемент И 16, инкрементирует- ся содержимое счетчика 20, чем каждый раз уменьшается значение порядка на выходе вычитателя 35. Если же мантисса второго операнда равна нулю, то счетные сигналы логических единиц для счетчика 13 на своем первом выходе устанавливает дешифратор 31, поскольку теперь на входе первого разряда входа этого дешифратора присутствует сигнал логической единицы с выхода триггера 7, а на входе второго разряда входа дешифратора 31 - сигнал логического нуля. Установка в единичное состояние триггера 7 осуществляется после прихода на входы 2 и 3 устройства двоичного кода первого значащего разряда мантиссы первого операн- да с помощью сигнала логической единицы с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 29. Выработка сигнала логической единицы конца операции на выходе 39 устройства при этом может осуществляться по сигналу логической единицы на выходе переполнения счетчика 13. Для нулевых мантисс операндов можно представить диапазон возможных значений затрат времени tyn на вычисление произведения двух операндов с помощью арифметического устройства в следующем виде:

m +4 tyn 3 (m + 1).

Для проведения операции деления чи сел на входе 42 устройства устанавливается сигнал логической единицы, а на входах 40 и 41 устройства -сигналы логических нулей. При этом коммутатор 12 к своему выходу подключает первый информационный вход, куда подсоединены выходы разрядов счет- чика 13, а блок 9 настраивается таким образом, чтобы на второй выход выдавать разность порядков исходных операндов и сигнал логической единицы на свой сигнальный выход. Перед выполнением деле- ния чисел в нулевое состояние сбрасываются триггеры 7, 8 и 24, регистры 10, 11 и 22 и счетчик 14. Предварительно также в счетчик 20 заносится число -5 в дополнительном коде, а блок 25 и счетчик 13

приводятся в исходное состояние. Сигнал логической единицы с входа 42, пройдя элемент НЕ 15, устанавливается логическим нулем на втором входе элемента ИЛИ 19, разблокируя его для прохождения логических сигналов с первого входа.

Рассмотрим процесс деления нормализованных и ненулевых исходных операндов.

Порядок делимого устанавливается на входах 36i-36n устройства, а порядок делителя - на входах 37i-37n устройства. Блок 9 вычисляет разность поступивших двоичных кодов порядков операндов. Полученная разность выдается на вход уменьшаемого вычитателя 35 для последующих преобразований в соответствии с получаемыми значениями разрядов мантиссы частного, которые в каждом 1-м цикле вычислений Формирует на своих выходах блок 25. Этст блик производит вычисления разрядов мантиссы частного с каждом -м цикле под управлением трех сигналов от распределителя 34.

Одновременно с установкой порядков операндов на входы 2, 3 и 4, 5 устройства подаются двоичные коды первых старших (с весом 2 ) значащих разрядов мантисс делимого и делителя соответственно. При э,том элементы ИСКЛЮЧАЮЩЕЕ ИЛИ б и 29 зы- рабатывают на своих выходах сигналы логических единиц, которые устанавливают в единичное состояние триггеры 8 и 7 соответственно. Состояния триггеров 8 и 7 анализирует дешифратор 31 по каждому стробирующему сигналу на его одноименном входе. На первом выходе дешифратора 31 сигнал логической единицы возникает тогда, когда в единичном состоянии нахо дится триггер 7. Появление сигнала логической единицы на втором выходе дешифратора 31 происходит в том случае, когда триггер 7 находится в нулевом состоянии, а состояние триггера 8 при этом может быть произвольным. Если же оба триггера 7 и 8 находятся в единичном состоянии, то формирования сигналов логических единиц на выходах дешифратора 31 не происходит. Поэтому для случая нормализованных и ненулевых мантисс операндов исходное состояние счетчика 13 (его младший разряд установлен в единичное состояние, а все остальные - в нулевое) остается неизменным после прихода первых старших разрядов мантисс операндов и не меняется в процессе счета. Двоичный код с выходов счетчика 13, пройдя через коммутатор 12, присутствует на управляющих входах коммутаторов 32 и 33, которые по установленному управляющему коду к своим выходам через свои информационные входы подключают выходы первых разрядов регистров 10

и 11 соответственно. С выходов коммутаторов 32 и 33 двоичные коды разрядов мантиссы делимого, задержанные с помощью регистров 10 и 11 на один цикл вычислений по отношению к двоичным кодам разрядов мантиссы делителя, подаются на первый информационный вход блока 25. Задержка разрядов мантиссы делимого необходима для правильного функционирования блока 25, поскольку для него необходимо, чтобы делимое было всегда меньше делителя. Таким образом, по каждому l-му синхронизирующему сигналу двоичный код разрядов мантиссы делимого с входов 2 и 3 устройства, пройдя через коммутатор 30 (на первом управляющем входе коммутатора 30 присутствует для операции деления сигнал логической единицы), последовательно вводится в регистры 10 и 11 и в следующем цикле вычислений с выходов первых разрядов этих регистров через коммутаторы 32 и 33 появляется на первом информационном входе блока 25. Двоичные коды мантиссы делителя со входов 4 и 5 устройства попадают через коммутатор 30 на второй информационный вход блока 25. Последний на основании поступивших разрядов мантисс операндов формирует на своих выходах разряды мантиссы частного с запаздыванием на три цикла вычислений. По каждому l-му синхронизирующему сигналу через выходы 27 и 28 выдаются из устройства двоичные коды разрядов мантиссы частного, которые при этом анализируются дешифратором 26. Причем, если анализируемой цифрой мантиссы частного является О, то по синхронизирующему сигналу с входа 1 устройства дешифратор 26 на своем втором выходе вырабатывает сигнал логической единицы. Этот сигнал поступает на третий вход элемента И 16, на первом и втором входе которого в настоящее время, т.е. до появления первого значащего разряда мантиссы частного на выходах блока 25 (триггер 24 находится в нулевом состоянии) и после прихода первого старшего значащего разряда мантиссы делителя (триггер 7 находится в единичном состоянии), установлены сигналы логических единиц. Поэтому сигнал логической единицы с второго выхода дешифратора 26 через элемент И 16 попадает на суммирующий вход счетчика 20 и увеличивает его содержимое на единицу. Последующие процессы по вычислению частного протекают в устройстве по аналогии получения суммы или произведения чисел. Рассмотрим работу устройства при делении ненулевых и ненормализованных мантисс исходных операндов. Предварительно заметим, что в указанной ситуации

при одновременном появлении первых значащих разрядов мантисс делимого и делителя работа устройства аналогична делению нормализованных мантисс.

Если же первым значащий разряд в процессе поразрядного ввода возникает на входах 2 и 3 разрядов мантиссы делимого, то это определяет элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 29, формируя на своем выходе сигнал

0 логической единицы. Такой сигнал устанавливает триггер 7 в единичное состояние. После этого и до момента появления на входах 4 и 5 первого значащего разряда мантиссы делителя по каждому

5 синхронизирующему сигналу с входа 1 устройства дешифратором 31 на его первом выходе вырабатывается сигнал логической единицы. Этот сигнал поступает на вычитающий вход счетчика 20, пройдя через эле0 мент И 17, поскольку на его втором входе присутствует разрешающий сигнал логической единицы с входа 42 устройства. Содержимое счетчика 20 уменьшается на единицу по каждому сигналу логической единицы на

5 его вычитающем входе. Кроме того, сигнал логической единицы с первого выхода дешифратора 31 инкрементирует содержимое счетчика 13. Уменьшение содержимого счетчика 20 приводит к росту значения чис0 ла на выходе вычитателя 35, где происходит коррекция порядка вычисляемого частного. Таким образом достигается совмещение во времени процесса поразрядного ввода ненормализованных мантисс операндов и

5 процесса коррекции порядка частного по нулевым разрядам мантиссы делителя до прихода на входы 4 и 5 первого значащего разряда мантиссы делителя. Двоичные коды разрядов мантиссы делимого с входов 2 и 3

0 устройства последовательно разряд за разрядом по каждому синхронизирующему сигналу вводятся в регистры 10 и 11 через коммутатор 30. До момента поступления первого значащего разряда мантиссы дели5 теля на входы 4 и 5 с помощью счетчика 13 и коммутаторов 32 и 33 осуществляется слежение за движением кодов разрядов мантиссы делимого в регистрах 10 и 11. С появлением первого значащего разряда

0 мантиссы делителя на входах 4 и 5 триггер 8 по сигналу логической единицы с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 переходит в единичное состояние, после чего дешифратор 31 прекращает формировать на

5 своем первом выходе сигналы логических единиц. Содержимое счетчика 13 фиксируется и задает двоичный код подключаемого к выходу информационного входа коммутаторов 32 и 33, обеспечивая тем самым поступление разрядов мантиссы делимого на

первый информационный вход блока 25 с задержкой на один цикл вычислений по отношению к разрядам мантиссы делителя, которые подаются на второй информационный вход блока 25. Такая задержка необходима для правильной работы блока 25, поскольку она обеспечивает условие превышения мантиссы делителя над мантиссой делимого. Дальнейший процесс вычисления частного аналогичен работе устройства при делении нормализованных операндов.

В том случае, когда первым значащий разряд поступает на входы 4 и 5 разрядов мантиссы делителя, происходит установка в единичное состояние триггера 8 сигналом логической единицы с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6. После этого на суммирующий вход счетчика 20 по каждому синхронизирующему сигналу начинают поступать сигналы логических единиц с второго выхода дешифратора 26 через элемент И 16, поскольку на втором входе элемента И 16 возникает разрешающий сигнал логической единицы с выхода элемента ИЛИ 19 после установки в единичное состояние триггера 8. На вычитателе 35 с помощью счетчика 20 коррекция порядка вычисляемого частного протекает указанным образом до тех пор, пока на выходе блока 25 не появится двоичный код первого значащего разряда мантиссы частного. При получении первого значащего разряда мантиссы частного, равного 1 или -1, дешифратор 26 по синхронизирующему сигналу выдает сигнал логической единицы на своем первом выходе, устанавливая триггер 24 в единичное состояние. Порядок частного с выхода вычитателя 35 запоминается в регистре 22 по сигналу логической единицы с единичного выхода триггера 24. Далее, как и при обработке нормализованных мантисс исходных операндов, осуществляется вычисление и поразрядная выдача через выходы 27 и 28 остальных разрядов мантиссы частного. В случаях, когда один либо оба операнда равны нулю, при выполнении операции деления чисел арифметическое устройство функционирует точно так же, как и при реализации операций сложения и умножения чисел. Для ненулевых мантисс операндов диапазон принимаемых значений затрат времени tqn на получение частного с помощью устройства составляет

m + 4 tqn 2 m + 3.

Блок 9 обработки порядков, схема которого показана на фиг.2, работает следующим образом.

Для операций сложения и вычитания чисел на его входы задания режима подаются сигналы логических нулей. Элементом НЕ

46 сигнал логического нуля с входа задания режима преобразуется в сигнал логической единицы, который с его выхода поступает на вторые входы группы элементов ИСКЛ ЮЧА- 5 ЮЩЕЕ ИЛИ 44i-44n и на вход переноса в младший разряд сумматора 45. При этом группой элементов ИЛИ 44i-44n осуществляется инвертирование сигналов на их первых входах, которые являются вторым

0 информационным входом блока 9 С помощью сумматора 45 и группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 44i-44n для операций сложения, вычитания и деления операндов определяется разность порядков

5 исходных операндов, которые присутствуют на входах блока 9.

Формирование модуля разности порядков операндов на первом выходе блока 9 осуществляется группой эпементое ИСК0 ЛЮЧАЮЩЕЕ ИЛИ 47i-47n-i и сумматором 48 следующим образом.

Сигнал с выхода старшего разряда (знаковый разряд порядка) сумматора 45 подается на вторые входы группы элементов

5 ИСКЛЮЧАЮЩЕЕ ИЛИ 47i 47n-i и управляет ими по части передачи с инверсией либо без нее сигналов с выходов младших разрядов сумматора 45 на первый вход сумма ора 48. На второй вход сумматора 48

0 сигналы логических нулей. Поэтому, если число на выходе сумматора 45 положительно (знаковый разряд сумматора 45 - логический нуль), то это число появляется на выходе сумматора 48 без изменений. Рели

5 число на выходе сумматора 45 отрицательно (знаковый разряд сумматора 45 - логическая единица), то с помощью группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 47i 47n-i сигналы с выходов младших разрядов сум0 матора 45 инвертируются и к этому инвертированному коду осуществляется прибавление единицы при помощи сумматора 48. С выхода сумматора 48 двоичный код модуля разности порядков устанавлива5 ется на первом выходе блока 9.

Схема 43 сравнения определяет, какой из двух поступивших на его входы порядков больший. На ее выходе устанавливается сигнал логического нуля в том случае, когда

0 порядок первого операнда больше либо равен порядку второго операнда. Если же порядок второго операнда больше порядка первого операнда, то схема 43 сравнения на своем выходе формирует сигнал логической

5 единицы. Для операций сложения и вычитания чисел сигнал с выхода схемы 43 сравнения передается через элемент ИЛИ 50 на сигнальный выход блока 9 и на первый управляющий вход коммутатора 49. При этом на втором управляющем входе коммутатора

49 устанавливается логический нуль. Порядок первого операнда передается через коммутатор 49 на второй выход блока 9 с первого информационного входа этого коммутатора по сигналу логического нуля с выхода схемы 43 сравнения. По сигналу логической единицы с выхода схемы 43 сравнения коммутатором 49 осуществляется передача порядка второго операнда на второй выход блока 9 с второго его информационного входа.

При выполнении операции, умножения чисел на первом входе задания режима блока 9 устанавливается сигнал логической единицы. Этот сигнал проходит через элемент ИЛИ 51 и появляется на втором управляющем входе коммутатора 49. Последний при этом настраивается на передачу сигналов с выхода сумматора 45 на второй выход блока 9. На выходе сумматора 45 формируется сумма порядков сомножителей.

В случае операции деления чисел на втором входе задания режима блока 9 присутствует сигнал логической единицы. Этим сигналом коммутатор 49 настраивается, как и при умножении, на передачу сигналов с выхода сумматора 45 на второй выход блока 9. Кроме того, логическая единица поступает на второй вход элемента ИЛИ 50, блокируя прохождение через него сигналов с первого его входа и устанавливая на выходе элемента ИЛИ 50 сигнал логической единицы, который теперь постоянно присутствует на сигнальном выходе блока 9 на время выполнения операции деления чисел.

Формула изобретения Арифметическое устройство, содержащее блок обработки порядков, первый и второй регистры мантиссы, первый элемент ИЛИ, счетчик нормализации, схему сравнения с константой, регистр порядка результата, счетчик, триггер, арифметический блок обработки мантисс, первый дешифратор, коммутатор мантисс, первый и второй коммутаторы и вычитатель нормализации, причем входы порядков первого и второго операндов устройства соединены соответственно с первыми и вторым информационными входами блока обработки порядков, сигнальный выход которого соединен с первым управляющим входом коммутатора мантисс, второй управляющий вход которого соединен с входом Вычитание устройства, входы разрядов входов мантиссы первого и второго операндов устройства соединены соответственно с входами разрядов первого и второго информационных входов коммутатора мантисс, выходы первого и второго разрядов первого выхода которого соединены с последовательными входами первого и второго регистров мантиссы соответственно, выход первого разряда первого выхода коммутатора мантисс

и выходы разрядов первого регистра мантиссы соединены соответственно с информационными входами первого коммутатора, выход которого и выход второго коммутатора соединены соответственно с входами

0 разрядов первого информационного входа арифметического блока обработки мантисс, входы разрядов второго информационного входа которого соединены с выходами соответствующих разрядов второго выхода ком5 мутатора мантисс, выход второго разряда первого выхода которого и выходы разрядов второго регистра мантиссы соединены соответственно с информационными входами второго коммутатора, управляющие входы

0 которого соединены с соответствующими управляющими входами первого коммутатора, вход синхронизации устройства соединен с входами разрешения сдвига первого и второго регистров мантиссы, с

5 входом разрешения первого дешифратора и со счетным входом счетчика, выход переполнения которого соединен с первым входом первого элемента ИЛИ, выход которого является выходом сигнала окончания опера0 ции устройства, выходы разрядов выхода арифметического блока обработки мантисс соединены с входами разрядов информационного входа первого дешифратора и являются выходами разрядов выхода мантиссы

5 результата устройства, первый выход первого дешифратора соединен с входом установки в 1 триггера, прямой выход которого соединен с входом разрешения записи регистра порядка результата, выход которого

0 является выходом порядка результата устройства, выход счетчика нормализации соединен с входом вычитаемого вычитателя нормализации, выход которого соединен с информационным входом регистра порядка

5 результата и с входом схемы сравнения с константой, выход которой соединен с вторым входом первого элемента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей путем вы0 полнения операций умножения и деления, оно содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ. триггеры первого и второго операндов, коммутатор управления, первый и второй счетчики разрядов.

5 элемент НЕ, первый и второй элементы И, второй элемент ИЛИ, второй дешифратор и распределитель импульсов, причем вход синхронизации устройства соединен с входом разрешения второго дешифратора, с входом распределителя импульсов, выходы

которого соединены с соответствующими тактовыми входами арифметического блока обработки мантисс, инверсный выход триггера соединен с первым входом первого элемента И и с входом блокировки второго дешифратора, выходы разрядов первого счетчика разрядов соединены с входами соответствующих разрядов первого информа ционного входа коммутатора управления, выходы разрядов выхода которого соедине- ны с соответствующими управляющими входами первого коммутатора, прямой выход триггера соединен с входом сброса счетчика, первый и второй информационные выходы блока обработки порядков сое- динены соответственно с вторым информационным входом коммутатора управления и с входом уменьшаемого вычитэ- теля нормализации, входы разрядов входа мантиссы первого операнда устройства со- единены соответственно с входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом установки в 1 триггера первого операнда, прямой выход которого соединен с входом первого разря- да информационного входа второго дешиф ратора, первый выход которого соединен с первым входом второго элемента И и со счетным входом первого счетчика разрядов, выход переполнения которого соединен с третьим входом первого элемента ИЛИ, четвертый вход которого соединен с выходом

переполнения второго счетчика разрядов, счетный вход которого соединен с вторым выходом второго дешифратора, выход первого элемента И соединен с суммирующим входом счетчика нормализации, вычитающий вход которого соединен с выходом второго элемента И, входы разрядов входа мантиссы второго операнда устройства соединены соответственно с входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом установки в Г триггера второго операнда, прямой выход которого соединен с входом второго разряда информационного входа второго дешифратора и с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, третий вход которого соединен с вторым выходом первого дешифратора, вход Умножение устройства соединен с первыми входами задания режима блока обработки порядков и арифметического блока обработки мантисс, с первым управляющим входом коммутатора управления, вход Деление устройства соединен с вторыми входами задания режима блока обработки порядков и арифметического блока обработки мантисс, с вторым управляющим входом коммутатора управления, с вторым входом второго элемента И и с входом элемента НЕ, выход которого соединен с вторым входом второго элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и системах управления, в которых применяется поразрядная передача операндов. Цель изобретения - расширение функциональных возможностей за счет выполнения операций умножения и деления. Устройство выполняет операции сложения, вычитания, умножения и деления как с нормализованными, так и с ненормализованными числами в форме с плавающей запятой, мантиссы которых поступают последовательно старшими разрядами вперед на входы устройства, которое совмещает во времени процессы ввода и обработки чисел. Устройство содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, 29, два триггера 7 и 8 операндов, блок 9 обработки порядков два регистра 10 и 11 мантиссы, коммутатор 12 управления, два счетчика 13 и 14 разрядов, элемент НЕ 15, два элемента И 16 и 17, два элемента ИЛИ 18 и 19, счетчик 20 нормализации, схему 21 сравнения с константой, регистр 22 порядка результата, счетчик 23, триггер 24, арифметический блок 25 обработки мантисс, коммутатор 30 мантисс, два дешифратора 26 и 31, два коммутатора 32 и 33, распределитель 34 импульсов и вычита- тель 35 нормализации, которые соединены между собой соответствующим образом. 2 ил, И

Фиг.1

36,

45

Kb

iff

Bu

Вход

, Вход ,l4fJieHue.

I

w

4

-i

4

R

т Вход ,l4fJieHue

Фиг. I

I

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1991-06-15—Публикация

1989-06-05—Подача