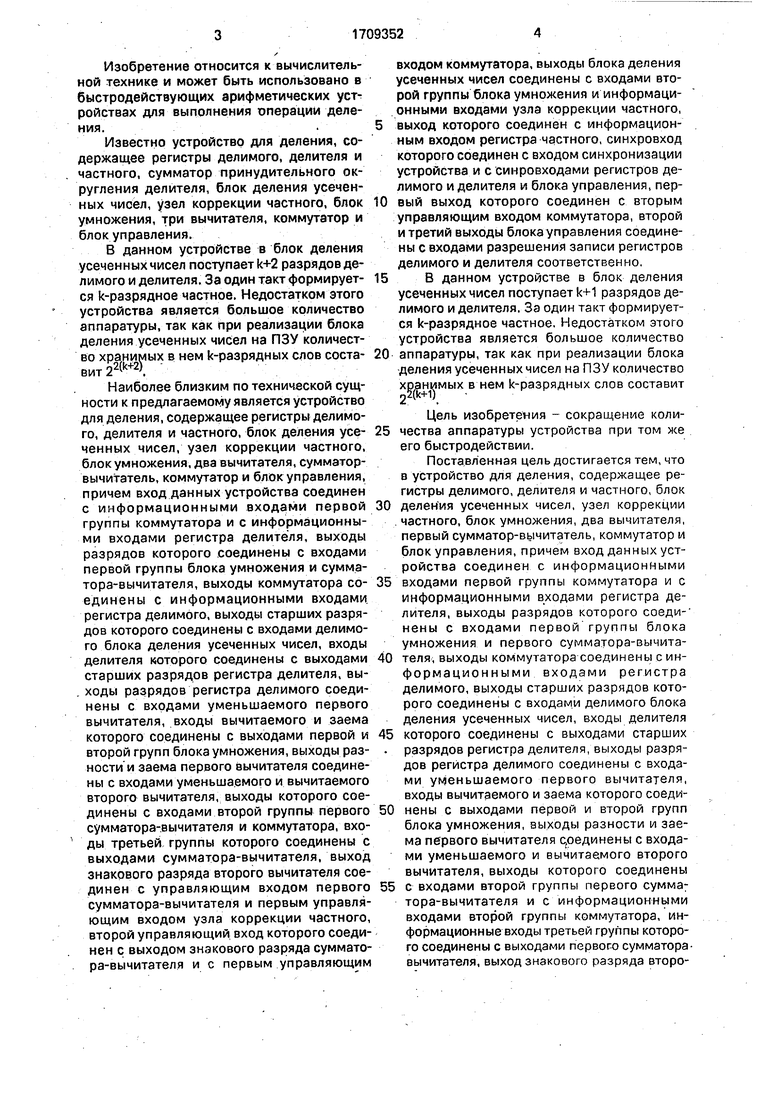

Фиг.1

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих арифметических устройствах для выполнения операции деления.

Известно устройство для деления, содержащее регистры делимого, делителя и частного, сумматор принудительного округления делителя, блок деления усеченных чисел, узел коррекции частного, блок умножения, три вычитателя, коммутатор и блок управления.

В данном устройстве в блок деления усеченных чисел поступает k+2 разрядов делимого и делителя. За один такт формируется k-разрядное частное. Недостатком этого устройства является большое количество аппаратуры, так как при реализации блока деления усеченных чисел на ПЗУ количество хранимых в нем k-разрядных слов составит

Наиболее близким по технической сущности к предлагаемому является устройство для деления, содержащее регистры делимого, делителя и частного, блок деления усеченных чисел, узел коррекции частного, блок умножения, два вычитателя, сумматорвычитатель, коммутатор и блок управления, причем вход данных устройства соединен с информационными входами первой группы коммутатора и с информационными входами регистра делителя, выходы разрядов которого соединены с входами первой группы блока умножения и сумматора-вычитателя, выходы коммутатора соединены с информационными входами, регистра делимого, выходы старших разрядов которого соединены с входами делимого блока деления усеченных чисел, входы делителя которого соединены с выходами старших разрядов регистра делителя, вы. ходы разрядов регистра делимого соединены с входами уменьшаемого первого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп блока умножения, выходы разности и заема первого вычитателя соединены с входами уменьшаемого и вычитаемого второго вычитателя, выходы которого соединены с входами второй группы первого сумматора-вычитателя и коммутатора, входы третьей группы которого соединены с выходами сумматора-вычитателя, выход знакового разряда второго вычитателя соединен с управляющим входом первого сумматора-вычитателя и первым управляющим входом узла коррекции частного, второй управляющий вход которого соединен с выходом знакового разряда сумматора-вычитателя и с первым управляющим

входом коммутатора, выходы блока деления усеченных чисел соединены с входами второй группы блока умножения и информационными входами узла коррекции частного,

выход которого соединен с информационным входом регистра частного, синхровход которого соединен с входом синхронизации устройства и с синровходами регистров делимого и делителя и блока управления, первый выход которого соединен с вторым управляющим входом коммутатора, второй и третий выходы блока управления соединены с входами разрешения записи регистров делимого и делителя соответственно.

5 В данном устройстве в блок деления усеченных чисел поступает k+1 разрядов делимого и делителя. За один такт формируется k-разрядное частное. Недостатком этого устройства является большое количество

0 аппаратуры, так как при реализации блока деления усеченных чисел на ПЗУ количество

хранимых в нем k-разрядных слов составит 2

Цель изобретения - сокращение колм5 чества аппаратуры устройства при том же его быстродействии.

Поставленная цель достигается тем, что в устройство для деления, содержащее регистры делимого, делителя и частного, блок

0 деления усеченных чисел, узел коррекции . частного, блок умножения, два вычитателя, первый сумматор-вычитатель, коммутатор и блок управления, причем вход данных устройства соединен с информационными

5 входами первой группы коммутатора и с информационными входами регистра делителя, выходы разрядов которого соединены с входами первой группы блока умножения и первого сумматора-вычита0 теля, выходы коммутатора соединены с информационными входами регистра делимого, выходы старших разрядов которого соединены с входами делимого блока деления усеченных чисел, входы делителя

5 которого соединены с выходами старших . разрядов регистра делителя, выходы разрядов регистра делимого соединены с входами уменьшаемого первого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп блока умножения, выходы разности и заема первого вычитателя соединены с входами уменьшаемого и вычитаемого второго вычитателя, выходы которого соединены

5 с входами второй группы первого сумма тора-вычитателя и с информационными входами второй группы коммутатора, информационные входы третьей группы которого соединены с выходами первого сумматора вычитателя, выход знакового разряда второго вычитателя соеАинен с управляющим входом первого сумматора-вычитателя и первым управляющим входом узла коррекции частного, второй управляющий вход которого соединен с выходом знакового разряда первого сумматора-вычитателя, выходы блока деления усеченных чисел соединены с входами второй группы блока умножения и информационными входами узла коррекции частного, выход которого соединен с информационным входом регистра частного, синхровход которого соединен с входом синхронизации устройства и с синхровходами регистров делимого и делителя и..блока управления, первый выход которого соединен с управляющим входом коммутатора, второй и третий выходы блока управления соединены с входами разрешения записи регистров делимого и делителя соответственно, введен второй суммауорвычитатель, управляющий вход которого соединен с выходом знакового разряда второго вычитателя, выходы регистра делителя и выходы второго вычитателя соединены с входами соответственно первой и второй групп второго сумматора-вычитателя, выход знакового разряда которого соединен с третьим управляющим входом узла коррекции частного, первый, второй и третий входы блока управления соединены с выходами знаковых разрядрв соответственно второго вычитателя, первого

сумматора-вычитателя и второго сумматора-вычитателя, выходы которого соединены с информационными входами четвертой группы коммутатора.

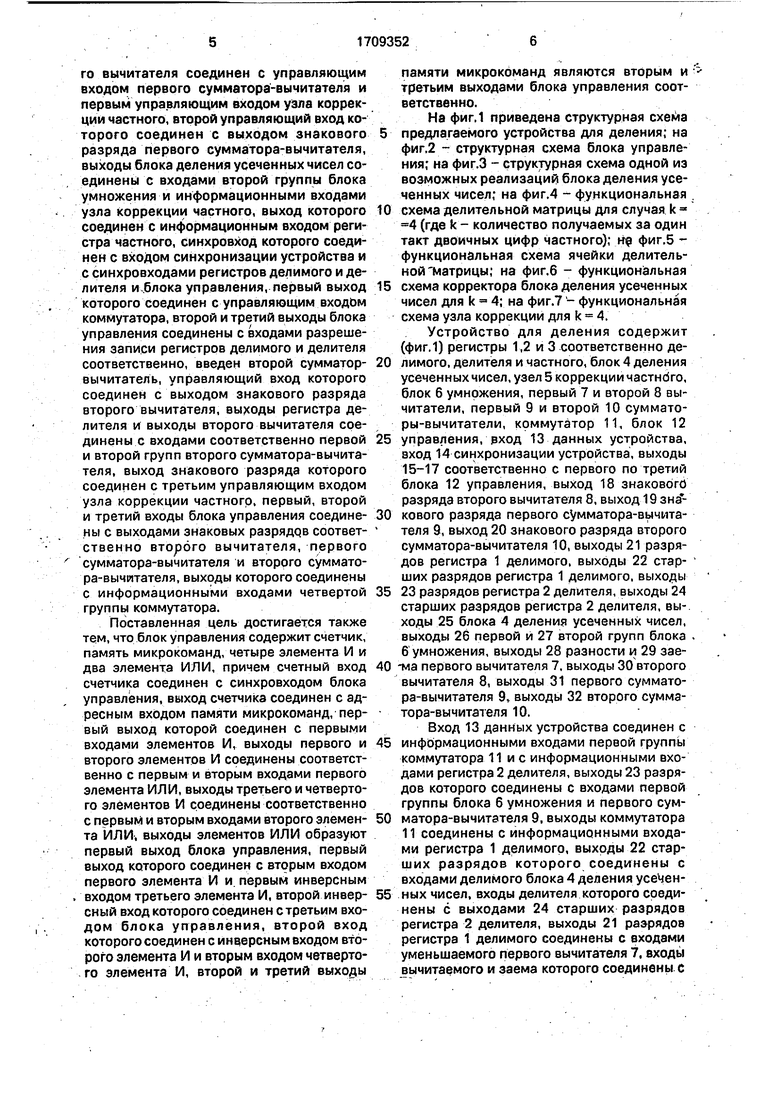

Поставленная цель достигается также тем, что блок управления содержит счетчик, память микрокоманд, четыре элемента И и два элемента ИЛИ, причем счетный вход счетчика соединен с синхровходом блока управления, выход счетчика соединен с адресным входом памяти микрокоманд, первый выход которой соединен с первыми входами элементов И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выходы элементов ИЛИ образуют первый выход блока управления, первый выход которого соединен с вторым входом первого элемента И и. первым инверсным

входом третьего элемента И, второй инверсный вход которого соединен с третьим входом блока управления, второй вход которого соединен с инверсным входом второго элемента И и вторым входом четвертого элемента И, второй и третий выходы

памяти микрокоманд являются вторым и третьим выходами блока управления соответственно.

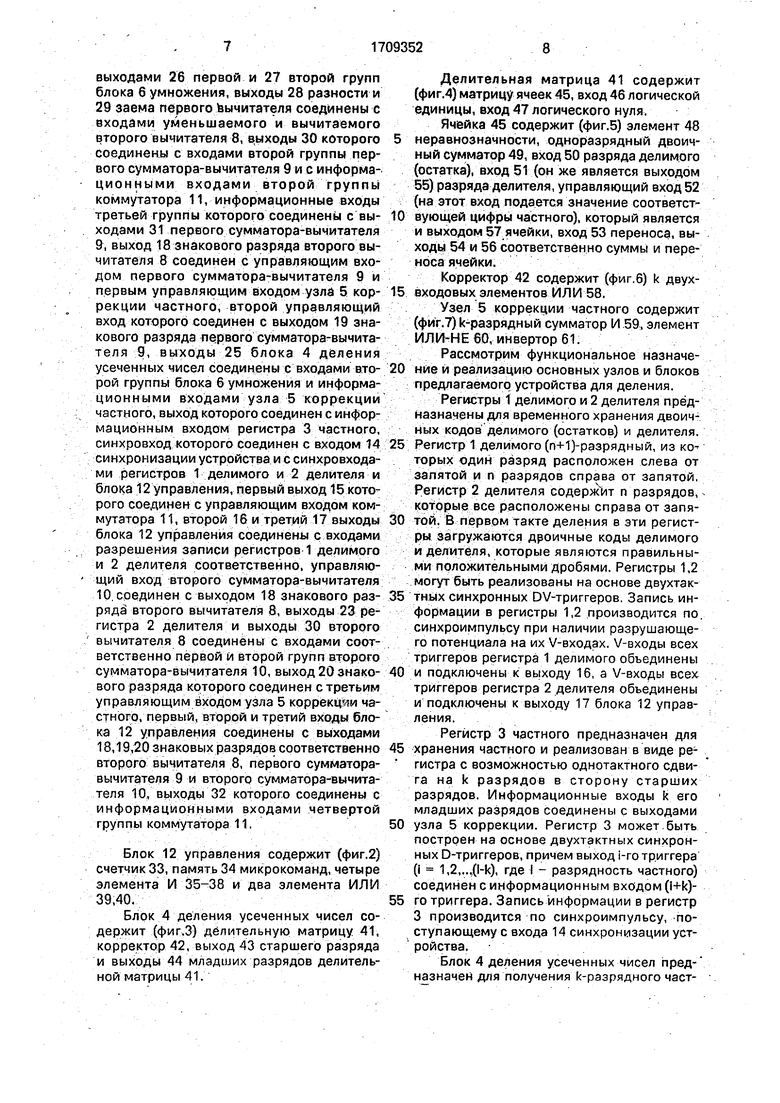

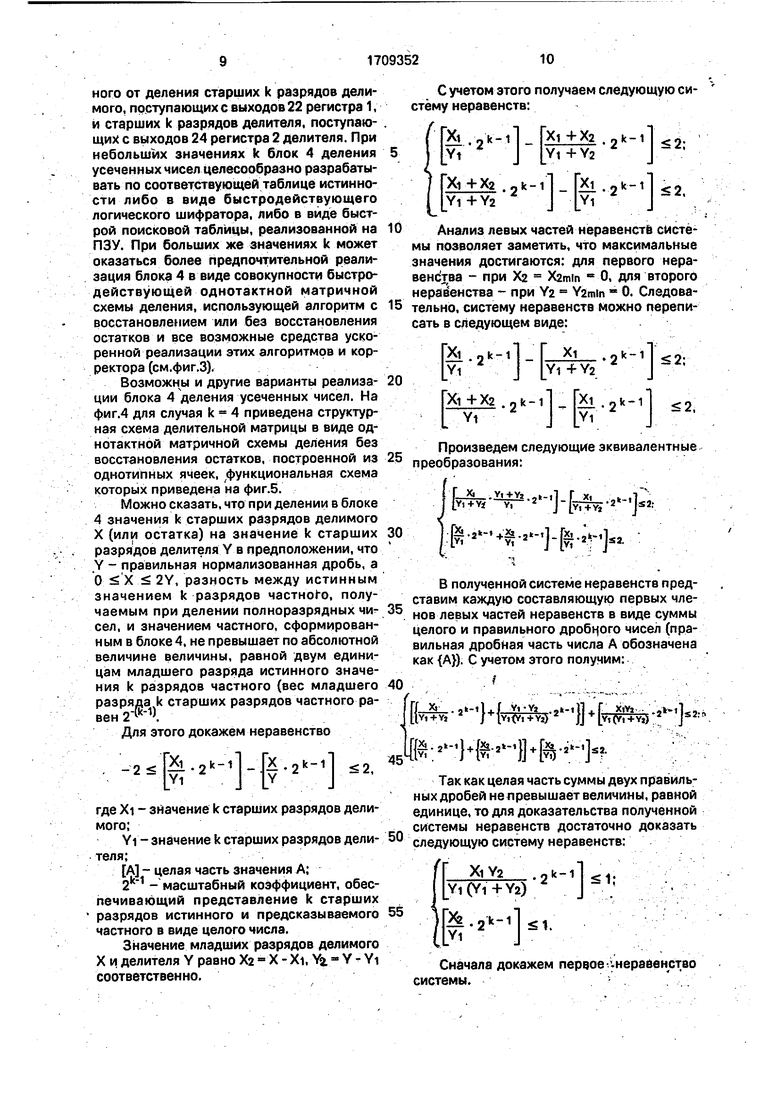

На фиг. 1 приведена структурная схейа 5 предлагаемого устройства для деления,- на фиг.2-структурная схема блока управления; на фиг.З - структурная схема одной из возможных реализаций блока деления усеченных чисел; на фиг.4 - функциональная

0 схема делительной матрицы для случая k 4 (где k - количество получаемых за один такт двоичных цифр частного); н фиг.5 функциональная схема ячейки делительной матрицы; на фиг.б - функциональная

5 схема корректора блока деления усеченных чисел для k 4; на фиг.7 - функциональная схема узла коррекции для k 4.

Устройство для деления содержит (фиг.1) регистры 1,2 и 3 соответственно делимого, делителя и частного, блок 4 деления усеченных чисел, узел 5 коррекции частнбго, блок 6 умножения, первый 7 и второй 8 вычитатели, первый 9 и второй 10 сумматоры-вычитатели, коммутатор 11, блок 12

5 управления, вход 13 данных устройства, вход 14 синхронизации устройства, выходы 15-17 соответственно с первого по третий блока 12 управления, выход 18 знакового разряда второго вычитателя 8, выход 19 знй0 кового разряда первого сумматора-вычитателя 9, выход 20 знакового разряда второго сумматора-вычитателя 10, выходы 21 разрядов регистра 1 делимого, выходы 22 старших разрядов регистра 1 делимого, выходы

5 23 разрядов регистра 2 делителя, выходы 124 старших разрядов регистра 2 делителя, выходы 25 блока 4 деления усеченных чисел, выходы 26 первой и 27 второй групп блока . 6 умножения, выходы 28 разности и 29 зае0 -ма первого вычитателя 7, выходы 30 второго вычитателя 8, выходы 31 первого сумматора-вычитателя 9, выходы 32 второго сумматора-вычитателя 10.

Вход 13 данных устройства соединен с

5 информационными входами первой группы коммутатора 11 и с информационными входами регистра 2 делителя, выходы 23 разрядов которого соединены с входами первой группы блока б умножения и первого сум0 матора-вычитэтеля 9, выходы коммутатора 11 соединены с информационными входами регистра 1 делимого, выходы 22 старших разрядов которого соединены с входами делимого блока 4 деления усеЦен5 ных чисел, входы делителя которого соединены с выходами 24 старших разрядов регистра 2 делителя, выходы 21 разрядов регистра 1 делимого соединены с входами уменьшаемого первого вычитателя 7. входы вычитаемого и заема которого соединены с

выходами 26 первой и 27 второй групп блока 6 умножения, выходы 28 разности и 29 заема первого Ьычитателя соединены с входами уменьшаемого и вычитаемого второго вычитателя 8, выходы 30 которого соединены с входами второй группы первого сумматора-вычитателя 9 и с информационными входами второй группы коммутатора 11, информационные входы третьей группы которого соединены с выходами 31 первого сумматора-вычитателя

9,выход 18 знакового разряда второго вычитателя 8 соединен с управляющим входом первого сумматора-вычитателя 9 и первым управляющим входом узла 5 коррекции частного, второй управляющий вход которого соединен с выходом 19 знакового разряда первого сумматора-вычитаталя 9, выходы 25 блока 4 деления усеченных чисел соединены с входами второй группы блока 6 умножения и информационными входами узла 5 коррекции частного, выход которого соединен с информационным входом регистра 3 частного, синхровход которого соединен с входом 14 синхронизации устройства и с синхровходами регистров 1 делимого и 2 делителя и блока 12 управления, первый выход 15 которого соединен с управляющим входом коммутатора 11, второй 16 и третий 17 выходы блока 12 управления соединены с входами разрешения записи регистров 1 делимого и 2 делителя соответственно, управляющий вход второго сумматора-вычитателя

10.соединен с выходом 18 знакового разряд второго вычитателя 8, выходы 23 регистра 2 делителя и выходы 30 второго вычитателя 8 соединены с входами соответственно первой и второй групп второго сумматора-вычитателя 10, выход 20 знакового разряда которого соединен с третьим управляющим входом узла 5 коррекц и частного, первый, второй и третий входы блока 12 управления соединены с выходами 18,19,20 знаковых разрядов соответственно второго вычитателя 8, первого сумматоравычитателя 9 и второго сум.матора-вычитателя 10, выходы 32 которого соединены с информационными входами четвертой труппы коммутатора 11.

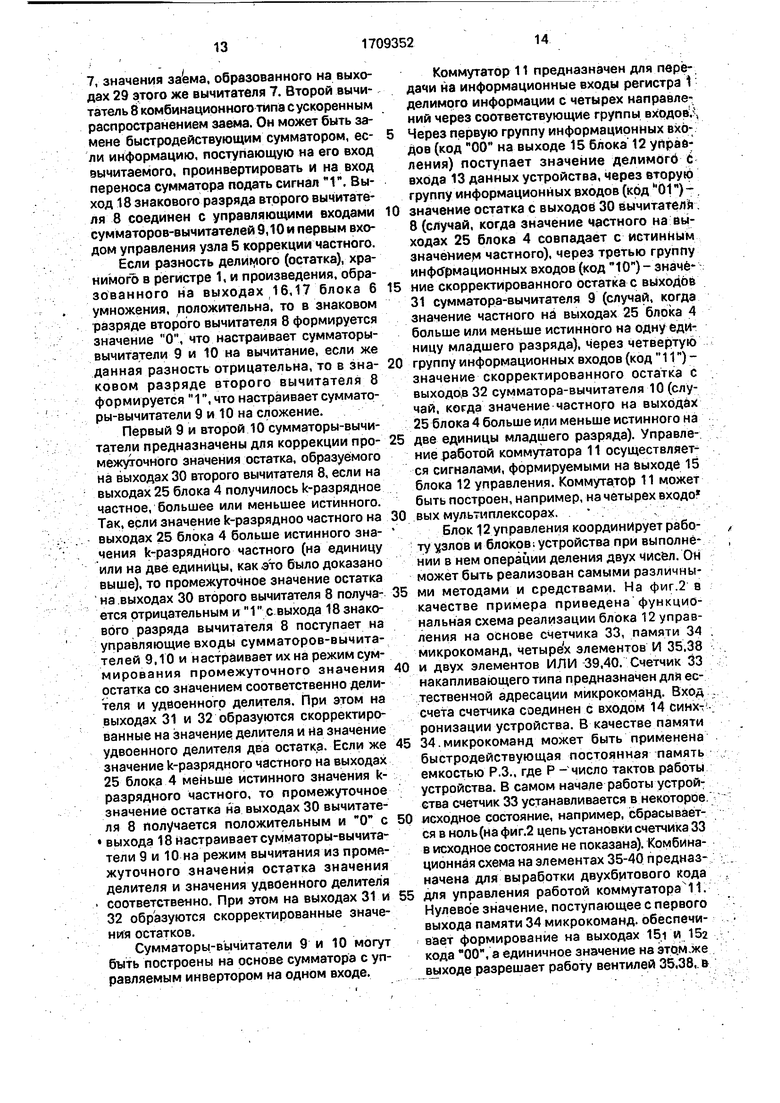

Блок 12 управления содержит (фиг.2) счетчик 33, память 34 микрокоманд, четыре элемента И 35-38 и два элемента ИЛИ 39,40.

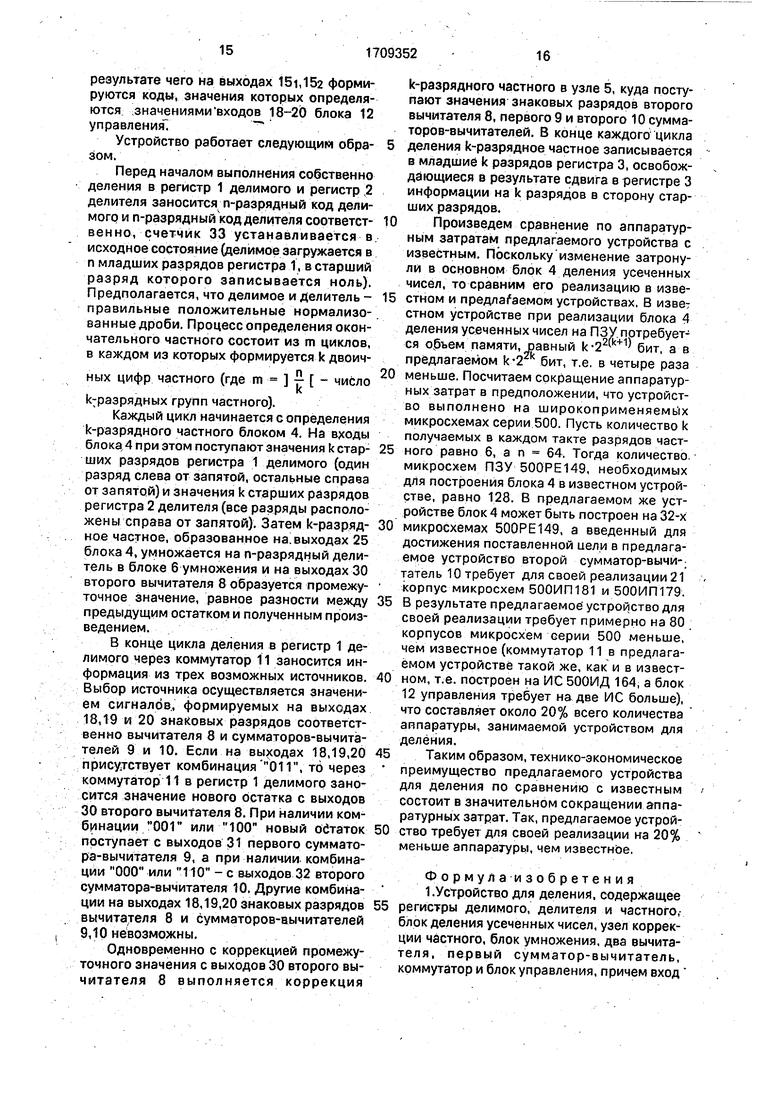

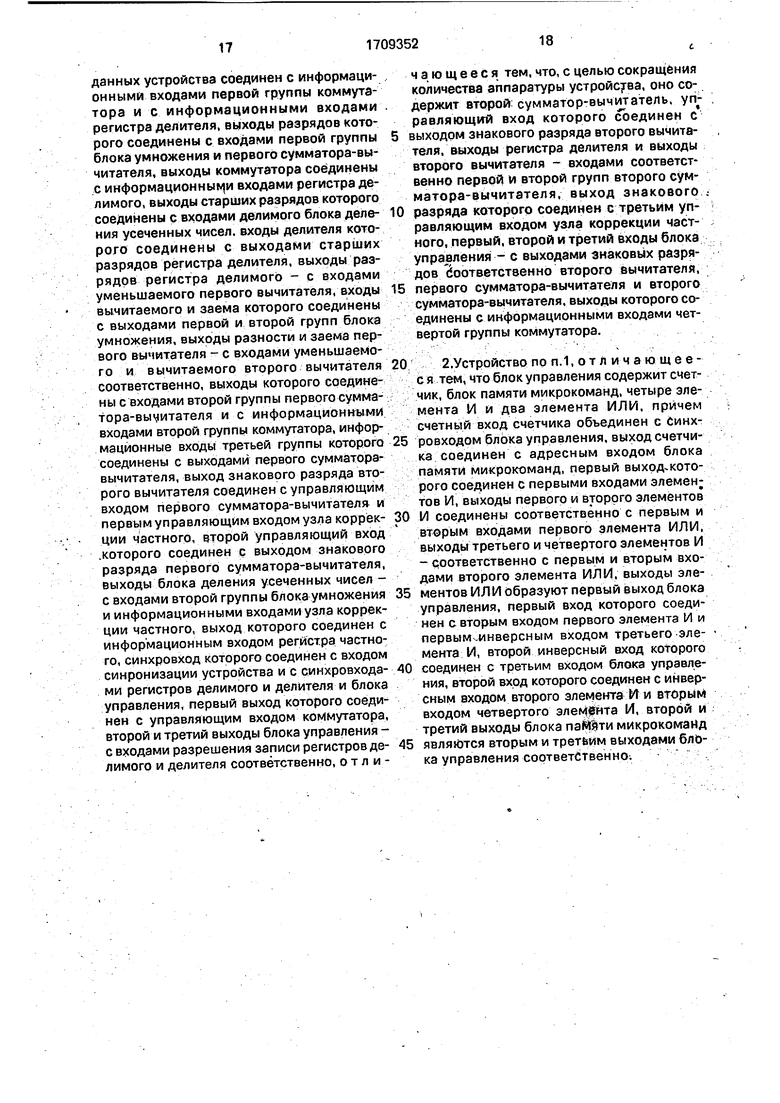

Блок 4 деления усеченных чисел содержит (фиг.З) делительную матрицу 41, корректор 42, выход 43 старшего разряда и выходы 44 младших разрядов делительной матрицы 41.

Делительная матрица 41 содержит {фиг.4) матрицу ячеек 45, вход 46 логической единицы, вход 47 логического нуля.

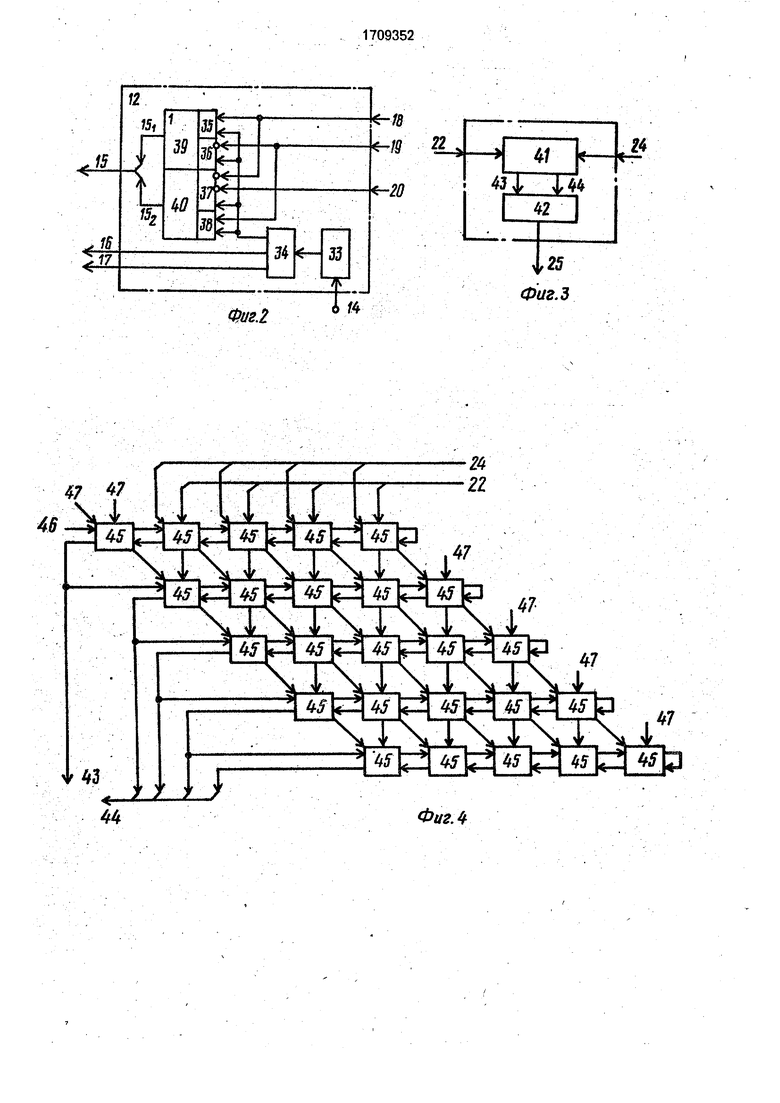

Ячейка 46 содержит (фиг.5) элемент 48

неравнозначности, одноразрядный двоичный сумматор 49, вход 50 разряда делимого (остатка), вход 51 (он же является выходом 55) разряда делителя, управляющий вход 52 (на этот вход подается значение соответствующей цифры частного), который является и выходом 57 ячейки, вход 53 переноса, выходы 54 и 56 соответственно суммы и переноса ячейки.

Корректор 42 содержит (фиг.б) k двух5 входовых элементов Или 58.

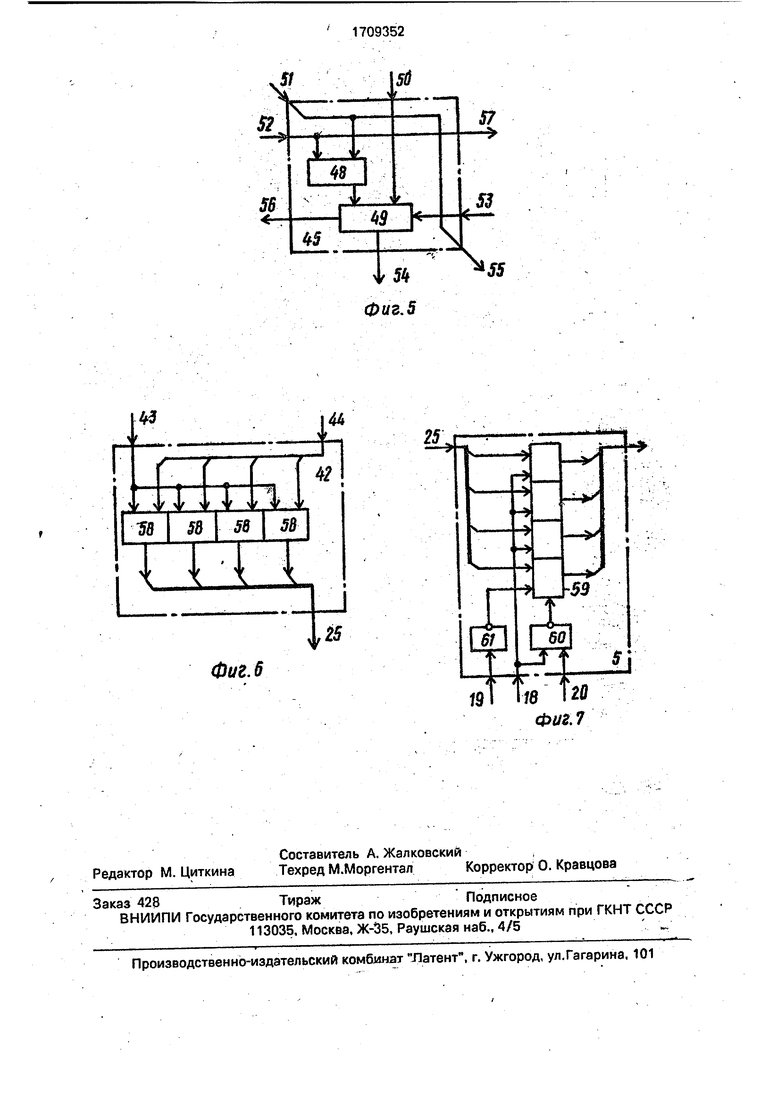

Узел 5 коррекции частного содержит (фиг.7)k-paзpядный сумматор И 59, элемент ИЛИ-НЕ 60, инвертор 61.

Рассмотрим функциональное назначение и реализацию основных узлов и блоков предлагаемого устройства для деления.

Регистры 1 делимого и 2 делителя предназначены для временного хранения двоичных кодов делимого (остатков) и делителя.

5 Регистр 1 делимого (п+1)-разрядный, из ко торых один разряд расположен слева от запятой и п разрядов справа от запятой, Регистр 2 делителя содержит п разрядов, когррые все расположены справа от запятой. В первом такте деления в эти регистры загружаются дроичные коды делимого и делителя, которые являются правильными положительными Дробями. Регистры 1,2 Могут быть реализованы на основе двухтак5 тнЫх синхронных DV-триггеров. Запись информации в регистры 1,2 производится по. синхроимпульсу при наличии разрушающего потенциала на их V-входах. V-входы всех триггеров регистра 1 делимого объединены

0 и подключены к вь1ходу 16, а V-входы всех триггеров регистра 2 делителя объединены и подключены к выходу 17 блока 12 управления.

Регистр 3 частного предназначен для

5 хранения частного и реализован в виде регистра с возможностью однотактного сдвига на k разрядов в сторону старших разрядов. Информационные входы k его младших разрядов соединены с выходами

0 узла 5 коррекции. Регистр 3 может быть построен на основе двухтактных синхронных Ь-триггеров, причем выход i-ro триггера О 1,2,..,(l-k), где I - разрядность частного) соединен с информационным входом (l+k)5 го триггера. Запись информации в регистр 3 производится по синхроимпульсу, поступающему с входа 14 синхронизации устройства.

Блок 4 деления усеченных чисел предназначен для получения k-разрядного частного от деления старших k разрядов делимого, поступающих с выходов 22 регистра 1, и старших k разрядов делителя, поступающих с выходов 24 регистра 2 делителя. При небольших значениях k блок 4 деления усеченных чисел целесообразно разрабатывать по соответствующей таблице истинности либо в виде быстродействующего логического шифратора. Либо в виде быстрой поисковой таблицы, реализованной на ПЗУ. При больших же значениях k может оказаться более предпочтительной реализация блока 4 в виде совокупности быстродействующей однотактной матричной схемы деления, использующей алгоритм с восстановлением или без восстановления остатков и все возможные средства ускоренной реализации этих алгоритмов и корректора (см.фиг.З). Возможн ы и другие варианты реализации блока 4 деления усеченных чисел. На фиг.4 для случая k 4 приведена структурная схема делительной матрицы в виде однотактной матричной схемы деления без восстановления остатков, построенной из однотипных ячеек, функциональная схема которых приведена на фиг.5. Можно сказать, что при делении в блоке 4 значения k старших разрядов делимого X (или остатка) на значение k старших разрядов делителя Y в предположении, что Y - правильная нормализованная дробь, а О X 2Y, разность между истинным значением k разрядов чacтнo o, получаемым при делении полноразрядных чи сел, и значением частного, сформированным в блоке 4, не превышает по абсолютной величине величины, равной двум единицам младшего разряда истинного значения k разрядов частного (вес младшего разряда k старших разрядов частного равенДля этого докажем неравенство ,-....-, где Xt - значение k старших разрядов делимого;YI - значение k старших разрядов делителя;. А - целая часть значения А; 2 - масштабный коэффициент, обеспечивающий представление k старших разрядов истинного и предсказываемого частного в виде целого числа. Значение младших разрядов делимого X и делителя Y равно Х2 X -Xi, Ya Y - Yi соответственно. С учетом этого получаем следующую систему неравенств: .2ic-ll- Xi±.2-0 2 Yt J fXi+Xz ic-i fXi .,; Yit-Yz J YI 2 J-2 Анализ левых частей неравенств системы позволяет заметить, 4to максимальные значения достигаются: для первого неравенбтва - при Х2 X2min 0, для второго неравенства - при Yz Yzmin 0. Следовательно, систему неравенств можно переписать в следующем виде: 2 - 2 - П - Г 2 - Т J Yi-fY2 J - ГХ1+Х2. k-i1 : ГХ1 . L YiJ- iYi Произведем следующие эквивалентные преобразования: ... : В получен ной системе неравенств представим каждую составляющу|р первых членов левых частей неравенств в виде суммы целого и правильного дробк|ого чисел (правильная дробная часть числа А обозначена как {А}). С учетом зтого получим: :{ --14vi 5%- - t Z ls2;r yifft+y) Так как целая часть суммы двух правильных дробей нелревышает величины, равной единице, то для доказательства полученной системы неравенств достаточно доказать следующую систему неравенств; Г XlY2 .olc-l. Yi(Yi+Y2), J -. ; r2k.2-il (LYI J Сначала докажем первое-унеравенство системы.

Во-первых, из условия О X 2Y следует, что :. .. 2 при любых значениях

VI -f- Y2

Y7

Xi,Yi и Y2. Во-вторых, отношение принимает максимальное значение| при Y2

.V-.

2-k . 2- Yamax - и Yi Yimtn 2 При этих

условиях

Ygmax.«k-1 2 -2 .„k-1 -k - -

Yimln

1-2 1.

Xi

и -2- 1, TO целая

Так как

Г XiY2 ..k-l. Ya .v.kчасть выражения |Yi(Yi-J-Y2) J 1,что и требова шось доказать.

Выражение принимает максимальное значение при Х2 Х2тах - 2

- -. х . .

и YI Yimtn 2. При этих условиях гр

I- (с Ч 1 ft-n 2 - 2 2„ т.е.

2-J

2.«k-i

1, что и требовалось докаYI

зать.

Узел 5 предназначен для коррекции частного, сформированного в текущем такте. Как было показано выше, значение k-разрядногб частного, поступающего с выходов 25 блока 4 на информационные входы узла 5, в некоторых случаях может отличаться на единицу или на две единицы младшего разряда от истинного значения k-разрядного частного, тогда в узле 5 осуществляется либо вычитание из k-разрядного частного значения единицы или двух единиц, либо прибавление к k-разрядному частному значения единицы или двух единиц. Управление работой узла 5 коррекции частного осуществляется по значению сигналов с выходов 18,19 и 20 знаковых разрядов соответственно второго вычитателя 8, первого 9 и второго 10 сумматоров-вычитателей. Так, При наличии на выходах 18,19 и 20 комбинации 000 к k-разрядному частному; будут прибавляться две единиць)его младшего разряда; при комбинации 001 будет прибавляться одна единица (см.фиг.7). При наличии на выходах 1 б, 19 и 20 комбинаций 110 и 100 из k-разрядного частного будут вычитаться соответственно две единицы и единица его младшего разряда. При комбинации 011 k-разрядное частное будет передаваться транзитом через узел 5 коррекции. Другие комбинации на выходах , 18,19 и 20 при правильном функционировании устройства невозможны. Вычитание

на сумматоре 59 в узле 5 осуществляется путем прибавления дополнительного кода второго слагаемого. При сложении k-разрядного частного сдвумя единицами младшего разряда используется вход переноса 0 сумматора 59.

В блоке б умножения осуществляется перемножение k-разрядного частного, сформированного на выходах 25 блока 4 и поступающего на вторую группу входов бло5 ка 6, и п-разрядногЪ делителя, хранимого в регистре 2 и поступающего на первую группу входов блока 6 с выходов 23 разрядов регистра 2. На выходах 26 и 27 первой и второй групп блока 6 образуется произведение в двухрядном коде (в виде двух чисел). Блок б умножения комбинационного типа может быть реализован в виде совокупности из k-разрядных двоичных умножителей.

5 G помощью первого вычитателя 7, второго вычитателя 8, первого 9 и второго 10 сумматоров-вычитателей в яредлагаемом устройстве на выходах 30,31,32 формируют ся три возможныхзначения остатка, только

0 одно из них записывается в качестве нового остатка через коммутатор 11 в регистр 1 делимого. Так, если k-разрядное частное, сформированное на выходах 25 блока 4 равно истинному k-разрядному частному,

5 то в регистр 1 делимого в качестве нового остатка заносится значение остатка с выходов 30 второго вычитателя 8, если данное k-разрядное частное больще или меньше, чем истинное k-разрядное частное, на одну единицу его младшего разряда, то новый остаток формируется на выходах 31 первого сумматора-вычитателя 9, если же k-разрядное частное больше или меньше, чем истинное k-разрядное частное,

5 на две единицы его младшего разряда, то . новый остаток формируется на выходах 32 второго сумматора-вычитателя 10.

Первый вычитатель 7 комбинационного типа выполнен по принципу вычитателя

0 без распространения заема. В вычитателе 7 осуществляется вычитание из содержимого регистра 1 делимого произведения, сформированного на выходах 26 и 27 блока 6 умножения в двухрядном коде. Результат

5 -вычитания образуется на выходах 28 и 29, соответственно разности и заема вычитателя 7 в двухрядном коде.

Второй вычитатель 8 предназначен для вычитания из значения разности, сформи- рованной на выходах 28 первого вычитателя

7, значения заема, образованного на выходах 29 этого же вычитателя 7. Второй вычитатель 8 комбинационного типа сускоренным распространением заема. Он может быть замене быстродействующим сумматором, если инУ1 ормацию, поступающую на его вход вычитаемого, проинвертировать и на вход переноса сумматора подать сигнал 1. Выход 18 знакового разряда второго вычитателя 8 соединен с управляющими входами сумматоров-вычитателей 9,10 и первым входом управления узла 5 коррекции частного.

Если разность делй1 ого (остатка), хранимого в регистре 1, и произведения, образованного на выходах 16,17 блока 6 умножения, положительна, то в знаковом разряде второго вычитателя 8 формируется значение О, что настраивает сумматорывычитатели 9 и 10 на вычитание, если же данная разность отрицательна, то в знаковом разряде второго вычитателя 8 формируется 1, что настраиваетсумматоры-вычитатели 9 и 10 на сложение.

Первый 9 и второй 10 сумматоры-вычитатели предназначены для коррекции промежуточного значения остатка, образуемого на выходах 30 второго вычитателя 8, если на выходах 25 блока 4 получилось k-разрядное частное, большее или меньшее истинного. Так, если значение k-разрядноо частного на выходах 25 блока 4 больше истинного значения k-разрядного частного (на единицу или на две единицы, как это было доказано выше), то промежуточное значение остатка на .выходах 30 второго вычитателя 8 получается отрицательным и 1 с выхода 18 знакового разряда вычитателя 8 поступает на управляющие входы сумматоров-вычитателей 9,10 и настраивает их на режим суммирования промежуточного значения остатка со значением соответственно делителя и удвоенного делителя. При этом на выходах 31 и 32 образуются скорректированные на значение делителя и на значение удвоенного делителя два остатк.а. Если же значение k-разрядного частного на выходах 25 блока 4 меньше истинного значения kразрядного частного, то промежуточное значение остатка на выходах 30 вычитателя 8 получается положительным и О с выхода 18 Настраивает сумматоры-вычитатели 9 и 10 на режим вычитания из промежуточного значения остатка значения делителя и значения удвоенного делителя соответственно. При этом на выходах 31 и 32 образуются скорректированные значения остатков.

Сумматоры-вычйтатели 9 и 10 могут бтнть построены на основе сумматора с управляемым инвертором на одном входе.

Коммутатор 11 предназначен для передачи на информационные входы регистра 1 делимого информации с четырех направлений через соответствующие группы входов .-, Через первую группу информационных входов (код 00 на выходе 15 блока 12 управления) поступает значение делимого с входа 13 данных устройства, через BTOpytb группу информационных входов (код 01) значение остатка с выходов 30 вычитател В (случай, когда значение частного на вь|ходах 25 блока 4 совпадает с истинным значение частного), через третью группу информационных входов (код 10) - значё

ние скорректированного остатка q вЫхоДов 31 сумматора-вычитателя 9 (случай, когда значение частного на выходах 25 блока 4 больше или меньше истинного на одну единицу младшего разряда), через четвертую

группу информационных входов (код 11)значение скорректированного остатка с выходов 32 сумматора-вычитателя 10 (случай, когда значение частного на выходах 25 блока 4 больше или меньше истинного на

две единицы младшего разряда). Управление работой коммутатора 11 осуществляет ся сигналами, формируемыми на выходе 15 блока 12 управления. Коммутатор 11 может быть построен, например, на четырех входо

вых мультиплексорах. v,

Блок 12 управления координирует работу узлов и блоков; устройства при выполнё- , НИИ в нем операции деления двух чис&л. Он может быть реализован самыми различными методами и средствами. На фиг.2 в качестве примера приведена функциональная схема реализации блока 12 управления на основе счетчика 33, памяти 34 . микрокоманд, четырех элементов И 35.38

и двух элементов ИЛИ 39,40. Счетчик 33 накапливающего типа предназначен для естественной адресации микрокоманд. Вход , счета счетчика соединен с входом 14 синх- ронизации устройства. В качестве памяти

34.микрокоманд может быть применена быстродействующая постоянная память емкостью Р.З., где Р - число тактов работы устройства. В самом начале работы устройства счетчик 33 устанавливается в некоторое.

исходное состояние, например, сбрасывается в ноль (на фиг.2 цепь установки счетчика 33 в исходное состояние не показана). Комбинационная схема на элементах 35-40 предназ- : . начена для выработки двухбитового кода .

для управления работой коммутатора 1. Нулевое значение, поступающее с первого выхода памяти 34 микрокоманд, обеспечи- вает формирование на выходах 15i и 152 кода 00, а единичное значение на этбм.же выходе разрешает работу вентилей 35,38, в

результате чего на выходах 15i,152 формируются коды, значения которых определяются чзначениямивходов 18-20 блока 12 управления

Устройство работает следующим образом.

Перед началом выполнения собственно деления в регистр 1 делимого и регистр 2 делителя заносится п-разрядный код делимого и п-разрядный код делителя соответственно, счетчик 33 устанавливается в. исходное состояние (делимое загружается в п младших разрядов регистра 1, в старший разряд которого записывается ноль). Предполагается, что делимое и делитель правильные положительные нормализо-. ванные дроби. Процесс определения окончательного частного состоит из m циклов, в каждом из которых формируется k двоичных цифр частного (где m - - число

К

k-разрядных групп частного).

Каждый цикл начинается с определения k-разрядного частного блоком 4. На входы блока,4 при зтом поступают значения k старших разрядов регистра 1 делимого (один разряд слева от запятой, остальные справа от запятой) и значения k старших разрядов регистра 2 делителя (все разряды расположены справа от запятой). Затем k-разрядное частное, образованное на выходах 25 блока 4, умножается на п-разрядный делитель в блоке 6 умножения и на выходах 30 второго вычитателя 8 образуется промежуточное значение, равное разности между предыдущим остатком и полученным пр оизведением,

В конце цикла деления в регистр 1 делимого через коммутатор 11 заносится информация из трех возможных источников. Выбор источника осуществляется значением сигналов., формируемых на выходах 18,19 и 20 знаковых разрядов соответственно вычитателя 8 и сумматоров-вычитателей 9 и 10. Если на вь|ходах 18,19,20 присутствует комбинация 011, то через коммутаторИ в регистр 1 делимого заносится значение нового остатка с выходов 30 второго вычитателя 8. При Наличии комбинации 001 или 100 новый остаток поступаете выходов 31 первого сумматора-вычитателя 9, а при наличии комбинации 000 или 110 - с выходов 32 второго сумматора-вычитателя 10. Другие комбинации на выходах 18,19,20 знаковых разрядов вычитателя В и сумматоров-аычитателей 9,10 невозможны.

Одновременно с коррекцией промежуточного значения с выходов 30 второго вычитателя 8 выполняется коррекция

k-разрядного частного в узле 5, куда поступают значения знаковых разрядов второго вычитателя 8, первого 9 и второго 10 сумматоров-вычитателей, В конце каждого цикла

деления k-разрядное частное записывается в младшие k разрядов регистра 3, освобождающиеся в результате сдвига в регистре 3 информации на k разрядов в сторону старших разрядов.

Произведем сравнение по аппаратурным затратам предлагаемого устройства с известным. Поскольку изменение затронули в основном блок 4 деления усеченных чисел, то срйвним его реализацию в известном и предлагаемом устройствах. В извет стном устройстве при реализации блока 4 деления усеченных чисел на ПЗУ потребуется памяти, равный бит, а в предлагаемом k2 бит, т.е. в четыре раза

меньше. Посчитаем сокращение аппаратурных затрат в предположении, что устройство выполнено на широкоприменяемь1х микросхемах серии 500. Пусть количество k получаемых в каждом такте разрядов частного равно 6, а п 64. Тогда количество, микросхем ПЗУ 500РЕ149, необходимых дЛя построения блока 4 в известном устройстве, равно 128, В предлагаемом же устройстве блок 4 может быть построен на 32-х

микросхемах 500РЕ149, а введенный для достижения поставленной цели в предлагаемое устройство второй сумматор-вычи-; татель 10 требует для своей реализации 21 корпус микросхем 500ИП181 и 500ИП179.

В результате предлагаемое устройство для своей реализации требует примерно на 80 корпусов микросхем серии 500 меньше, чем известное (коммутатор 11 в предлагаемом устройстве такой же, как и в известном, т.е. построен на ИС 500ИД 164, а блок 12 управления требует на две ИС больше), что составляет около 20% всего количества аппаратуры, занимаемой устройством для деления.

Таким образом, технико-экономическое преимущество предлагаемого устройства для деления по сравнению с известным состоит в значительном сокращении аппаратурных затрат. Так, предлагаемое устройство требует для своей реализации на 20% меньше аппаратуры, чем известное.

Формулаизобретения 1 .Устройство для деления, содержащее регистры делимого, делителя и частного,блок деления усеченных чисел, узел коррекции частного, блок умножения, два вычитателя, первый сумматор-вычитатель, коммутатор и блок управления, причем вход

данных устройства соединен с информационными входами первой группы коммутатора и с информационными входами регистра делителя, разрядов которого соединены с входами первой группы блока умножения и первого сумматора-вычитателя, выходы коммутатора соединены с информационныг и входами регистра делимого, выходы старших разрядов которого соединены с входами делимого блока деления усеченных чисел, входы делителя которого соединены с выходами старших разрядов регистра делителя, выходы разрядов регистра делимого - с входами уменьшаемого первого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп блока умножения, выходы разности и заема первого вычитателя - с входами уменьшаемого и вычитаемого второго вычитателя соответственно, выходы которого соединены с входами второй группы первого сумматора-вы итателя и с информационными входами второй группы коммутатора, информационные входы третьей группы которого соединены с выходами первого сумматоравычитателя, выход знакового разряда второго вычитателя соединен с управляющим входом первого сумматора-вычитателя и первым управляющим входом узла коррекции частного, второй управляющий вход .которого соединен с выходом знакового разряда первого сумматора-вычитатеяя, выходы блока деления усеченных чисел - с входами второй группы блока умножения и информационными входами узла коррекции частного, выход которого соединен с информационным входом регистра частного, синхровход которого соединен с входом синронизации устройства и с синхровходами регистров делимого и делителя и блока управления, первый выход которого соединен с управляющим входом коммутатора, второй и третий выходы блока управления с входами разрешения записи регистров делимого и делителя соответственно, отличающееся тем, что, с целью сокращения количества аппаратуры устройС7ва, оно содержит второй: сумматор-вычитатель, yriравляющкй вход которого соединен с

выходом знакового разряда второго вычитателя, выходы регистра делителя и выходы второго вычитателя - входами соответственно первой и второй групп второго сумматора-вычитателя, выход знакового ;

разряда которого соединен с третьим управляющим входом узла коррекции частного, первый, второй и третий входы блока управления - с выходами знаковых разрядов боответственно второго вычитателя,

первого сумматора-вычитателя и второго сумматора-вычитателя, выходы которогосоединены с информационными входами четвертой группы коммутатора.

2.Устройство по П.1, от л и ч а ю щ е еся тем, что блок управления содержит счетчик, блок памяти микрокоманд, четыре элемента И и два злемента ИЛИ, причем счетный вход счетчика объединен с Синхровходом блока управления, выход счетчика соединен с адресным входом блока памяти микрокоманд, первый выхрд-которого соединен с первыми входами элемен; тов И, выходы первого и второго элементов

И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы третьего и четвертого элементов И -соответственно с первым и вторым входами второго элемента ИЛИ, выходы элементов ИЛИ образуют первый выход блока управления, первый вход которого соединен с вторым входом первого элемента И и первымхинверсным входом Третьего эле- мента И, второй инверсный вход которого

соединен с третьим входом блока управления, второй вход которого соединен с инверсным входом второго элемента И и вторым входом четвертого элей|гйта И, второй И третий выходы блока паЙЙти микрокоманд

являются вторым и третьим выходами блока управления соответственно;

22

24

М

43 J, AU4

25 Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления | 1986 |

|

SU1478212A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для построения устройств деления чисел. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит регистры 1-3 делимого, делителя и частного, коммутатор 11. блок 4 деления усеченных чисел, блок 6 умножения, узел 5 коррекции частного, два вычитателя 1,8< первый сумматор-вычитатель 9, блок 12 управления, а также нововведенный второй сумматор-вычитатель 10. 7 ил.

47

45

44

Фиг. 5

i X л

25

.

| Авторское свидетельство СССР по заявке № 4634053/24 | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1990-01-15—Подача