1

Изобретение относится к вычислительной технике, может быть использовано в электронных вычислительных машинах.

Известно устройство для умножения, содержащее регистр множителя, накапливающий регистр, сумматор, регистр множимого с блоком парафазного приема кода 1, которое анализирует триггер -младщего разряда регистра множителя и, если этот триггер находится в состоянии «единица, выполняет сложение и сдвиг регистра множителя вправо, и если он в «нулевом состоянии - только сдвиг регистра множителя. Вторым тактом код накапливающего регистра сдвигается вправо.

Таким образом, указанное устройство выполняет умножение только на один разряд множителя, что не отвечает современным требования к быстродействию ЭВМ.

Известно также устройство для умножения, содержащее сумматор, регистры множимо,го и множителя, переносов и частичных произведений, логический элемент преобразования множимого, а также триггер запоминания, два дополнительных младщих разряда и один дополнительный старший разряд сумматора, два дополнительных младщих разряда регистра переносов и систему связей дополнительного оборудования с основным 2.

В этом устройстве происходит умножение на два разряда множителя, что повышает быстродействие схемы. Однако наличие дополнительного оборудования сумматора и регистров, расширяющее разрядную сетку, специфично только для умножения и не может быть использовано при выполне-нии других операций обработки информащхи. При использовании подобных устройств в процессоре ЭВМ дополнительное оборудование сумматора и регистров нарушает регулярность структуры, затрудняет их реализацию средствами микроэлектроники и снижает коэффициент использования аппаратуры.

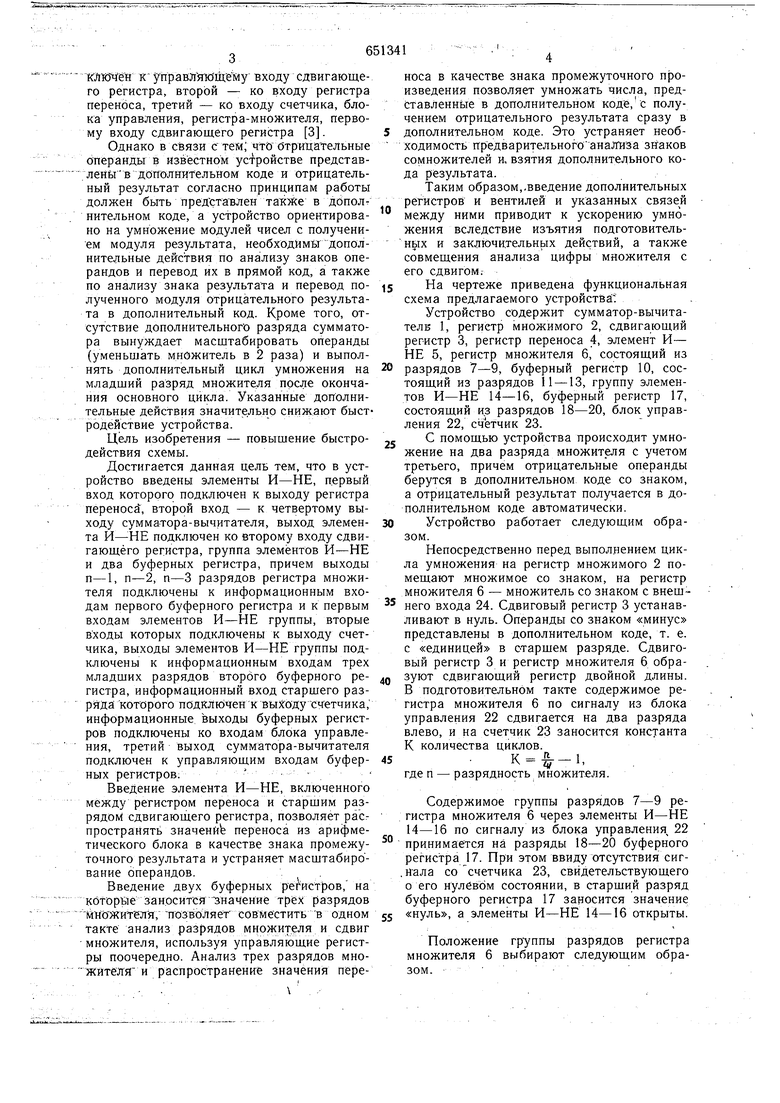

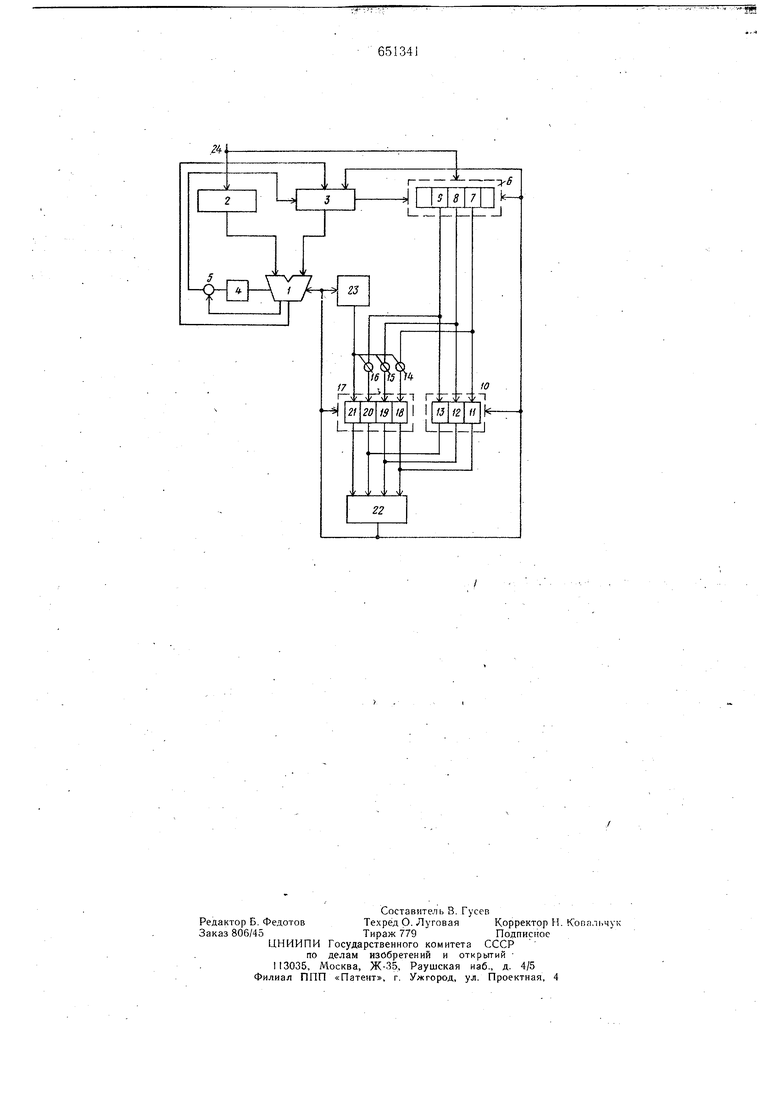

Наиболее близко к предлагаемому устройство для умножения п-разрядных чисел, содержащее регистры множимого и множителя, информационные входы которых соединены со входами устройства, сдвигающий регистр, выход которого подключен ко входу регистра множителя, выходы регистра множимого и сдвигающего регистра подклк)чены к первому и второму входам сумм;атора-вычитателя, первый выход которого (ОЧен К управлягющейу входу сдвигающего регистра, второй - ко входу регистра переноса, третий - ко входу счетчика, блока управления, регистра-множителя, первому входу сдвигающего регистра 3. Однако в связи с тем; чть бтрицательные операнды в известном устройстве представлены в дополнительном коде и отрицательный результат согласно принципам работы должен быть представлен в дЬполт нительном коде, а устройство ориентировано на умножение модулей чисел с получением модуля результата, необходимы дополнительные действия по анализу знаков операндов и перевод их в прямой код, а также по анализу знака результата и перевод полученного модуля отрицательного результата в дополнительный код. Кроме того, отсутствие дополнительного разряда сумматора вынуждает масщтабировать операнды (уменьшать множитель в 2 раза) и выполнять дополнительный цикл умножения на младший разряд множителя после окончания основного цикла. Указанные дополнительные действия значительно снижают быст родействие устройства. Цель изобретения - повышение быстродействия схемы. Достигается данная цель тем, что в устройство введены элементы И-НЕ, первый вход которого подключен к выходу регистра переноса, второй вход - к четвертому выходу сумматора-вычитателя, выход элемента подключен ко второму входу сдвигающего регистра, группа элементов И-НЕ и два буферных регистра, причем выходы п-1, п-2, п-3 разрядов регистра множителя подключены к информационным входам первого буферного регистра и к первым входам элементов И-НЕ группы, вторые входы которых подключены к выходу счетчика, выходы элементов И-НЕ группы подключены к информационным входам трех младших разрядов второго буферного регистра, информационный вход старшего разрйдя которого подклк)Чен к выходу счетчика, информационные выходы буферных регистров подключены ко входам блока управления, третий выход сумматора-вычитателя подключен к управляющим входам буферных регистров: Введение элемента И-НЕ, включенного между регистром переноса и старшим разрядом сдвигающего регистра, позволяет распространять значений переноса из арифметического блока в качестве знака промежуточного результата и устраняет масштабирование операндов. Введение двух буферных регистров, на которые заносится значение трёх разрядов йможитёля, позволяет совместить В одном такте анализ разрядов множит ля и сдвиг множителя, используя управляющие регистры поочередно. Анализ трех разрядов мно жителя и распространение значения пере. . , носа в качестве знака промежуточного произведения позволяет умножать числа, представленные в дополнительном коде,с получением отрицательного результата сразу в дополнительном коде. Это устраняет необходимость предварительного анализа сомножителей и, взятия дополнительного кода результата. Таким образом,.введение дополнительных регистров и вентилей и указанных связей между ними приводит к ускорению умножения вследствие изъятия подготовительньтх и заключительньгх действий, а также совмещения анализа цифры множителя с его сдвигом. На чертеже приведена функциональная схема предлагаемого устройства Устройство содержит сумматор-вычитателн 1, регистр множимого 2, сдвигающий регистр 3, регистр переноса 4, элемент И- НЕ 5, регистр множителя б, состоящий из разрядов 7-9, буферный регистр 10, состоящий из разрядов 11 -13, группу элементов И-НЕ 14-16, буферный регистр 17, состоящий из разрядов 18-20, блок управления 22, счетчик 23. С помощью устройства происходит умножение на два разряда множителя с учетом третьего, причем отрицательные операнды берутся в дополнительном коде со знаком, а отрицательный результат получается в дополнительном коде автоматически. Устройство работает следующим образом. Непосредственно перед выполнением цикла умножения на регистр множимого 2 помещают множимое со знаком, на регистр множителя 6 - множитель со знаком с внеш-него входа 24. Сдвиговый регистр 3 устанавливают в нуль. Операнды со знаком «минус представлены в дополнительном коде, т. е. с «единицей в старшем разряде. Сдвиговый регистр 3 и регистр множителя 6 образуют сдвигающий регистр двойной длины. В подготовительном такте содержимое регистра множителя 6 по сигналу из блока управления 22 сдвигается на два разряда влево, и на счетчик 23 заносится константа К количества циклов. К -1, где п - разрядность множит ля. Содержимое группы разрядов 7-9 регистра множителя 6 через элементы И-НЕ 14-16 по сигналу из блока управления, 22 принимается на разряды 18-20 буферного регистра 17. При этом ввиду отсутствия сигНала со счетчика 23, свидетельствующего о его нулевОм состоянии, в старший разряд буферного регистра 17 заносится значение «нуль, а элементы И-НЕ 14-16 открыты. Положение группы разрядов регистра множителя 6 выбирают следующим образом. . Разряд 7 является п-1-вым, разряд 8 является п-2-м, разряд 9 является п-3-ьим, где п - разрядность регистра множителя 6.

Таким образом, предварительно в разряд 18 буферного регистра 17 заносится «нуль, в разряд 19 - последняя цифра множителя, в разряд 20 - предпоследняя его цифра. Множитель сдвигом на два вправо возвращается в исходное состояние. На этом этап загрузки буферного регистра заканчивается.

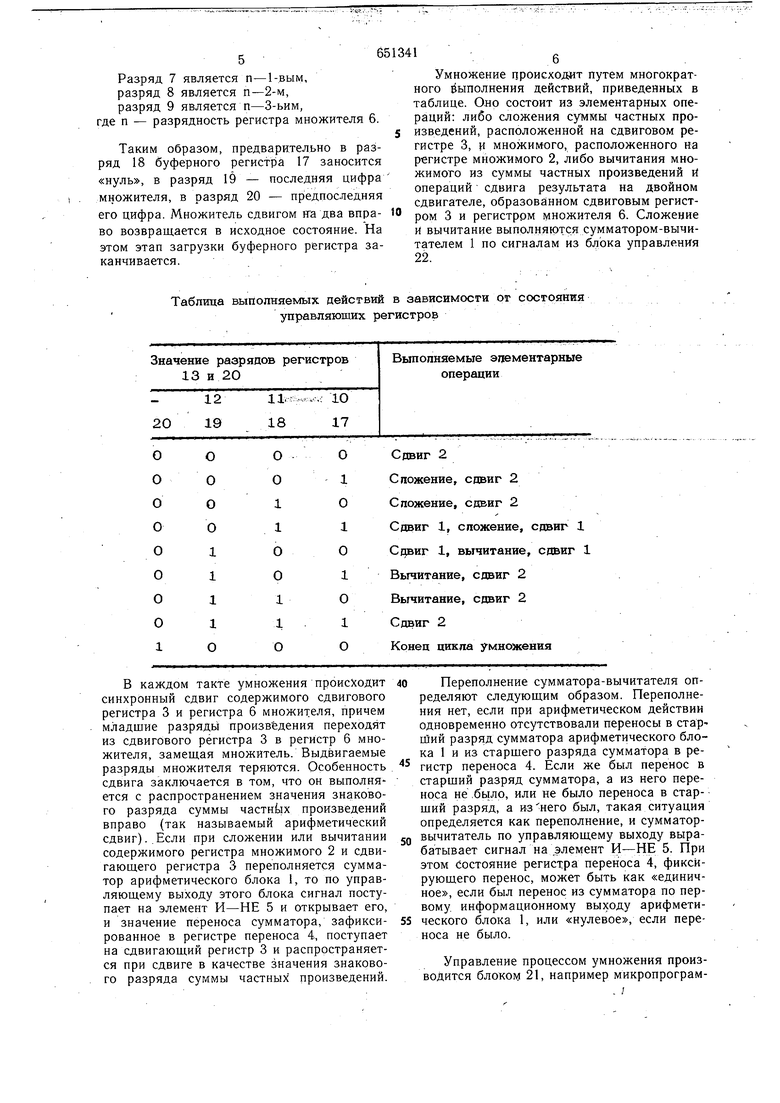

Таблица выполняемых действий в зависимосги ог состояния управляющих регистров

Умножение происходит путем многократного выполнения действий, приведенных в таблице. Оно состоит из элементарных операций: либо сложения суммы частных произведений, расположенной на сдвиговом регистре 3, и MHokHNforo, расположенного на регистре множимого 2, либо вычитания множимого из суммы частных произведений и операций сдвига результата на двойном сдвигателе, образованном сдвиговым регистром 3 и регистром множителя 6. Сложение и вычитание выполнянэтся сумматором-вычитателем 1 по сигналам из блока управления 22.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для деления | 1976 |

|

SU734682A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

В каждом такте умножения происходит синхронный сдвиг содержимого сдвигового регистра 3 и регистра 6 множителя, причем младшие разрядь произведения переходят из сдвигового регистра 3 в регистр 6 множителя, замещая множитель. Выдвигаемые разряды множителя теряются. Особенность сдвига заключается в том, что он выполняется с распространением значения знакового разряда суммы частных произведений вправо (так называемый арифметический сдвиг)..Если при сложении или вычитании содержимого регистра множимого 2 и сдвигающего регистра 3 переполняется сумматор арифметического блока 1, то по управляющему выходу этого блока сигнал поступает на элемент И-НЕ 5 и открывает его, и значение переноса сумматора, зафиксированное в регистре переноса 4, поступает на сдвигающий регистр 3 и распространяется при сдвиге в качестве значения знакового разряда суммы частных произведений. Переполнение сумматора-вычитателя определяют следующим образом. Переполнения нет, если при арифметическом действии одновременно отсутствовали переносы в стар ц5ий разряд сумматора арифметического блока 1 и из старщего разряда сумматора в регистр переноса 4. Если же был перенос в старщий разряд сумматора, а из него переноса не .бь1ло, или не было переноса в старщий разряд, а изнего был, такая ситуация определяется как переполнение, и сумматорвычитатель по управляющему выходу вырабатывает сигнал на элемент И-НЕ 5. При этом Состояние регистра переноса 4, фиксирующего перенос, может быть как «единичное, если был перенос из сумматора по первому, информационному выходу арифметического блока 1, или «нулевое, если переноса не было. Управление процессом умножения производится блоком 21, например микропрограминым, с помощью буферных регистров 10 и 17. В первом такте умножения значение буферного регистра 17 принимается в блок управления 22, и последний вырабатывает последовательность сигналов, реализующих действия по таблице. При этом в младшем разряде 18 второго буферного регистра 17 всегда находится нуль. Одновременно блок управления 22 подает сигнал на буферный регистр 10 для приема значения группы разрядов множителя регистра 6, и в разрядах 12 и 13 буферного регистра 10 фиксируются два очередных разряда множителя, а в разряде 11 старший разряд предыдущей пары разрядов множителя. Во втором цикле умножения блок управления 22 вырабатывает последовательность сигналов, реализующих действия по таблице в соответствии с состоянием буферного регистра 10, причем значение счетчика 23 дополнительно уменьшается на единицу. Одновременно с анализом состояния буферного регистра 10 на буферный регистр 17 принимается следующая пара разрядов множителя и старший разряд предыдушей пары (на которую происходит умножение в .этот самый момент). Таким образом значения очередных разрядов множителя заносятся за такт до умножения на них. Это позволяет сохранить значение старшего разряда пары цифр множителя, не вводя дополнительных разрядов в регистр множителя 6. Умножение продолжается до тех .пор, пока в такте анализа буферного регистра 10 значение счетчика 23 не станет нулевым. Сигнал из счетчика 23 заносит в разряд 21 буферного регистра 17 единицу и запрещает прием через элементы И-НЕ 14-16 в остальные разряды того же регистра содержимого группы разрядов регистра множителя 6. В последнем цикле умножения значение буферного регистра оказывается 1000, и блок управления 22 прекращает умножение. Запрет приема в разряды 18-20 буферного регистра 17 делается в целях экономии ячеек памяти микропрограммнбго блока управления 22. Предлагаемое устройство имеет существенньгё преимущества по сравнению с известными, так как позволяет повысить быстродействие вычислительных машнн путем ускорения выполнения широко распространенной операции умножения. При реализации изобретения в вычислительной машине фактически не возникает

8 НУЖДЫ во внедрении специфической аппаратуры, так как все перечисленные блоки и регистры устройства используются и при выполнении других операций системы команд. Кроме того, ввиду значительного упг рощения управления оборудованием при выполнении операции зна.чительно снижается объем микропрограмм, если используется микропрограммный принцип управления. Формула изобретения Устройство для умножения п-разрядных чисел, содержащее регистры множимого и множителя, информационные входы которых соединены со входами устройства, сдвигающий регистр, выход которого подключен ко входу регист|эа множителя, в.ыходы регистра множимого и сдвигающего регистра подключены к первому и второму входам сумматора-вычитателя, первый выход которого подключен к управляющему входу сдвигающего регистра, второй - ко входу регистра переноса, третий ко входу счетчика, блока управления, регистра множителя, к первому входу сдвигающего регистра, отличающееся тем, что, с целью повышения быстродействия схемы, в нее введены элемент. И-НЕ, первый вход которого подключен к выходу регистра переноса, второй - к четвертому выходу сумматора-вычитателя, выход элемента И-НЕ подключен ко второму входу сдвигающего регистра, группа элементов И-НЕ и два буферных регистра, причем выходы п-1, п-2, п-3 разрядов регистра множителя подключены к информационным входам первого буферного регистра и к первым входам элементов И-НЕ группы, вторые входы которых подключены к выходу счетчика, выходы элементов И-НЕ группы подключены к информационным входам трех младших разрядов второго буферного регистра, информационный вход старшего разряда которого подключен к выходу счетчика, информационные вы-ходы буферных регистров подключены ко входамблока управления, третий выход сумматоравычитателя подключен к управляющим входам буферных регистров. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 318941, G 06 F 7/50, 12.07.68. 2.Авторское свидетельство СССР № 357561, G 06 F 7/30, 23.06.70. 3.Флорес А. Opt-анизация вычислительных машин, М., «Мир, 1972, с. 309-311.

Д

Зпгг:

Авторы

Даты

1979-03-05—Публикация

1976-07-07—Подача