1

Изобретение относится к цифрово вычислительной технике, предназначено для деления чисел, представленных в двоичной системе счисления, и может найти применение в качестве операционного блока в высокпроизводительных вычислительных машинах и системах.

Целью изобретения является повышение быстродействия устройства дл деления чисел.

В устройстве делимое и делитель положительные числа. Диапазон представления делимого о, ij , делителя l/2,l3i, причем делимое меньше делителя .

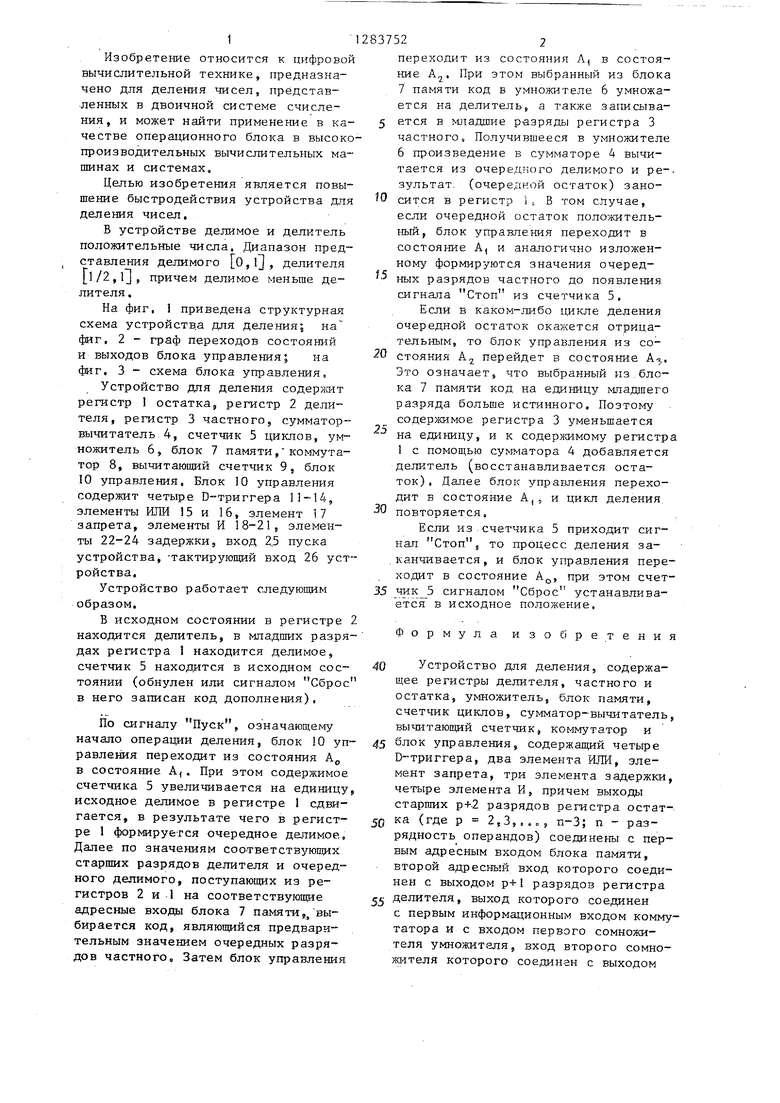

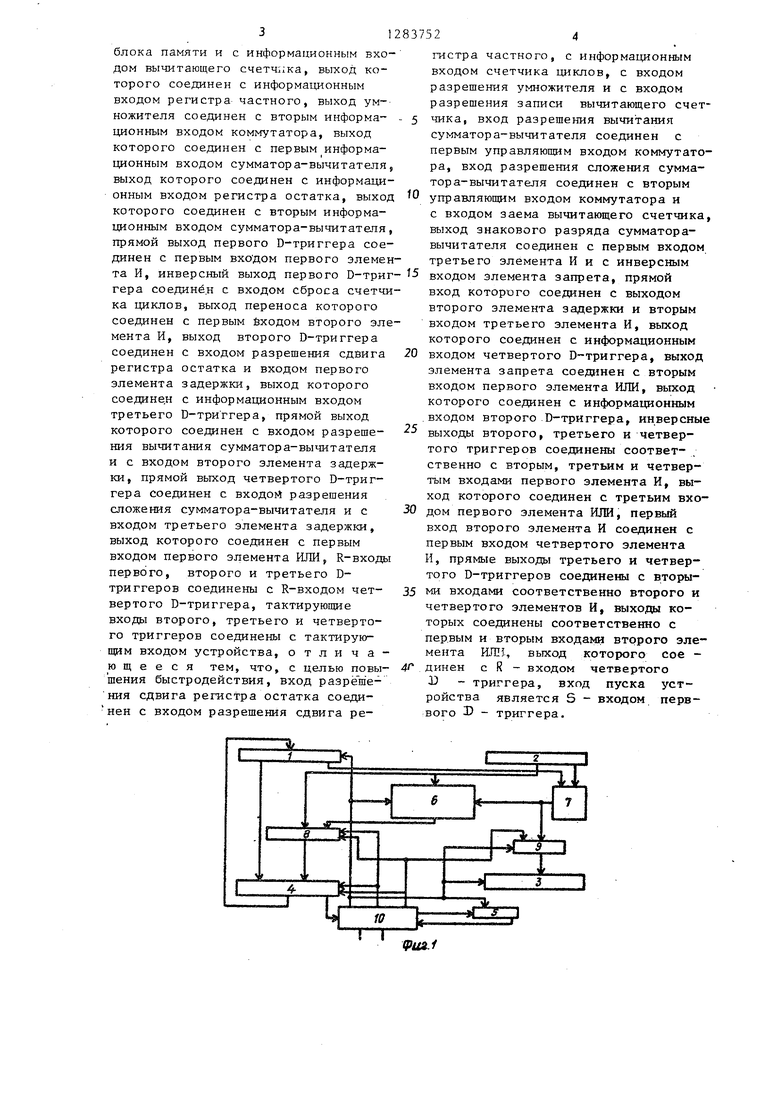

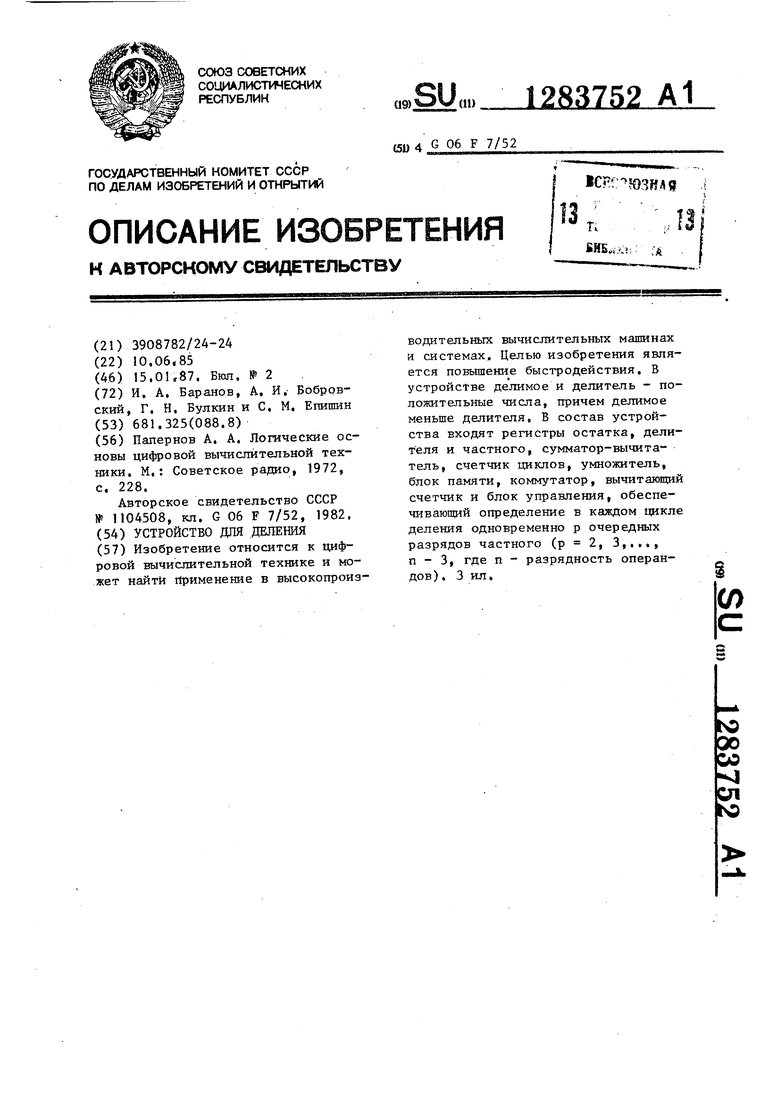

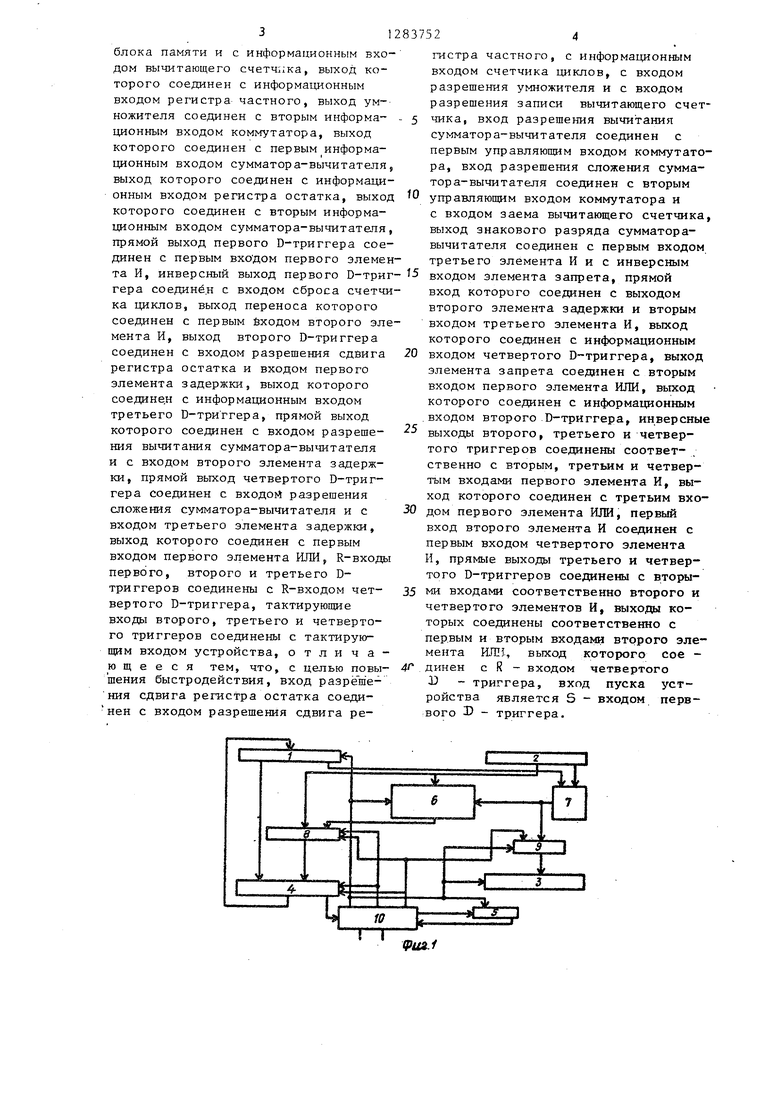

На фиг, приведена структурная схема устройства для деления; на фиг, 2 - граф переходов состояний и выходов блока управления; на фиг. 3 - схема блока управления.

Устройство для деления содержит регистр I остатка, регистр 2 делителя, регистр 3 частного, сумматор вычитатель,4, счетчик 5 циклов, умножитель 6, блок 7 памяти, коммутатор 8, вычитающий счетчик 9, блок 10 управления. Блок 0 управления содержит четыре D-триггера -14, элементы ИЛИ 15 и 16, элемент 17 запрета, элементы И 18-21, элементы 22-24 задержки, вход 2,5 пуска устройства, -тактирующий вход 26 усройства.

Устройство работает следуюшим образом.

В исходном состоянии в регистре находится делитель, в младших разрдах регистра 1 находится делимое, счетчик 5 находится в исходном состоянии (обнулен или сигналом Сбро в него записан код дополнения).

По сигналу означающему начало операции деления, блок 0 управления переходит из состояния А в состояние А,, При этом содержимое счетчика 5 увеличивается на единицу исходное делимое в регистре 1 сдвигается, в результате чего в регистре 1 формируется очередное делимое. Далее по значениям соответствующих старших разрядов делителя и очеред™ ного делимого, поступающих из регистров 2 и 1 на соответствующие адресные входа блока 7 памяти,, выбирается код, являющийся предварительным значением очередных разрядов частного. Затем блок управления

5

752

2

переходит из состояния А( в состояние А. При этом выбранный из блока 7 памяти код в умножителе 6 умножается на делитель, а также записывается в младшие р-азряды регистра 3 частного. Получившееся в умножителе 6 произведение в сумматоре 4 вычитается из очередного делимого и ре-. зультат, (очередной остаток) заносится в регистр 1. В том случае, если очередной остаток положительный блок управления переходит в состояние А, и аналогично изложенному формируются значения очередных разрядов частного до появления сигнала Стоп из счетчика 5,

Если в каком-либо цикле деления очередной остаток окажется отрицательным, то блок управления из со0 стояния А. перейдет в состояние А. Это означает, что выбранный из . блока 7 памяти код на единицу разряда больше истинного. Поэтому содержимое регистра 3 уменьшается на единицу, и к содержимому регистра 1 с помощью сумматора 4 добавляется делитель (восстанавливается остаток) , Далее блок управления переходит в состояние А, ,, и цикл деления, повторяется.

Если из. счетчика 5 приходит сигнал Стоп, то процесс деления за- .канчивается, и блок управления переходит в состояние А, при этом счет5 сигналом Сброс устанавливает cF в исходное положение.

5

0

Формула изобретения

Устройство для деления, содержащее регистры делителя, частного и остатка, умножитель, блок памяти, счетчик циклов, сумматор-вычитатель, вычитаюш11й счетчик, ко1х1мутатор и

блок управления, содержащий четыре D-триггера, два элемента ИЛИ, элемент запрета, три элемента задержки, четыре элемента И, причем выходы старших Р+-2 разрядов регистра остатка (где р 2,3,..., п-3; п - разрядность операндов) соединеьа с первым адресным входом блока памяти, второй адресньгй вход которого соединен с выходом р+I разрядов регистра

делителя, выход которого соединен

с первым информационным входом коммутатора и с входом первого сомножителя умножителя, вход второго сомножителя которого соединен с выходом

блока памяти и с информационным входом вычитающего счетч;;ка, выход которого соединен с информационным входом регистра частного, выход умножителя соединен с вторым информа- - ционным входом коммутатора, выход которого соединен с первым информационным входом сумматора-вычитателя5 выход которого соединен с информационным входом регистра остатка, выход которого соединен с вторым информационным входом сумматора-вычитателя, прямой выход первого D-триггера соединен с первым входом первого элеменfO

гистра частного, с информационны входом счетчика циклов, с входом разрешения умножителя и с входом разрешения записи вычитающего с чика, вход разрешения вычитания сумматора-вычитателя соединен с первым управляюшим входом коммут ра, вход разрешения сложения сум тора-вычитателя соединен с вторы управляющим входом коммутатора и с входом заема вычитающего счетч выход знакового разряда сумматор вычитателя соединен с первым вхо третьего элемента И и с инверсны

та И, инверсный выход первого D-триг- -5 входом элемента запрета, прямой

гера соединён с входом сброса счетчка циклов, выход переноса которого соединен с первым йходом второго элмента И, выход второго D-триггера соединен с входом разрешения сдвига регистра остатка и входом первого элемента задержки, выход которого соединен с информационным входом третьего D-три ггера, прямой выход которого соединен с входом разрешения вычитания сумматора-вычитателя и с входом второго элемента задержки, прямой выход четвертого D-триггера соединен с входой разрешения сложения сумматора-вычитателя и с входом третьего элемента задержки, выход которого соединен с первым входом первого элемента ИЛИ, R-вход первого, второго и третьего D- триггеров соединены с R-входом четвертого D-триггера, тактирующие входы второго, третьего и четвертого триггеров соединены с тактирующим входом устройства, отличающееся тем, что, с целью повышения быстродействия, вход разрешения сдвига регистра остатка соеди- нен с входом разрешения сдвига ре

гистра частного, с информационным входом счетчика циклов, с входом разрешения умножителя и с входом разрешения записи вычитающего счетчика, вход разрешения вычитания сумматора-вычитателя соединен с первым управляюшим входом коммутатора, вход разрешения сложения сумматора-вычитателя соединен с вторым управляющим входом коммутатора и с входом заема вычитающего счетчика, выход знакового разряда сумматора- вычитателя соединен с первым входом третьего элемента И и с инверсным

5

вход которого соединен с выходом второго элемента задержки и вторым входом третьего элемента И, выход которого соединен с информационным 0 входом четвертого D-триггера, выход элемента запрета соединен с вторым входом первого элемента ИЛИ, выход которого соединен с информационным входом второго D-триггера, инверсные выходы второго, третьего и четвертого триггеров соединены соответ- . ственно с вторым, третьим и четвертым входами первого элемента И, выход которого соединен с третьим входом первого элемента ИЛИ, первый вход второго элемента И соединен с первым входом четвертого элемента И, прямые выходы третьего и четвертого D-триггеров соединены с вторыми входами соответственно второго и четвертого элементов И, выходы которых соединены соответственно с первым и вторым входами второго элемента , выход которого сое - динен с R - входом четвертого D - триггера, вход пуска устройства является S - входом перв- вого 33 - триггера.

0

5

1

I

„Cffpoc

„Уин, , Сдвиг . ц

„/7/7

Bbit.

„Спот. :/

JweA

паст.

,

.i w/ .

,Шйг

Стт

(Pu.t.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1986 |

|

SU1325467A1 |

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Делительное устройство | 1983 |

|

SU1168929A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления с самоконтролем | 1987 |

|

SU1559346A2 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

Изобретение относится к цифровой вычислительной технике и может найти йрименение в высокопроизводительных вычислительных машинах и системах. Целью изобретения является повьшение быстродействия. В устройстве делимое и делитель - положительные числа, причем делимое меньше делителя. В состав устройства входят регистры остатка, делителя и частного, сумматор-вычита- тель, счетчик циклов, умножитель, блок памяти, коммутатор, вычитающий счетчик и блок управления, обеспечивающий определение в каждом 1дакле деления одновременно р очередных разрядов частного (р 2, 3,..., п - 3, где п - разрядность операндов) . 3 ил. СЛ С

| Папернов А | |||

| А | |||

| Логические основы цифровой вычислительной техники | |||

| М.: Советское радао, 1972, с | |||

| Приспособление для нагрузки тендеров дровами | 1920 |

|

SU228A1 |

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-06-10—Подача