Изобретение относится к вычислительной технике и может быть использовано при проектировании устройств отображения информации на экране ЭЛТ.

Цель изобретения повышение точности устройства.

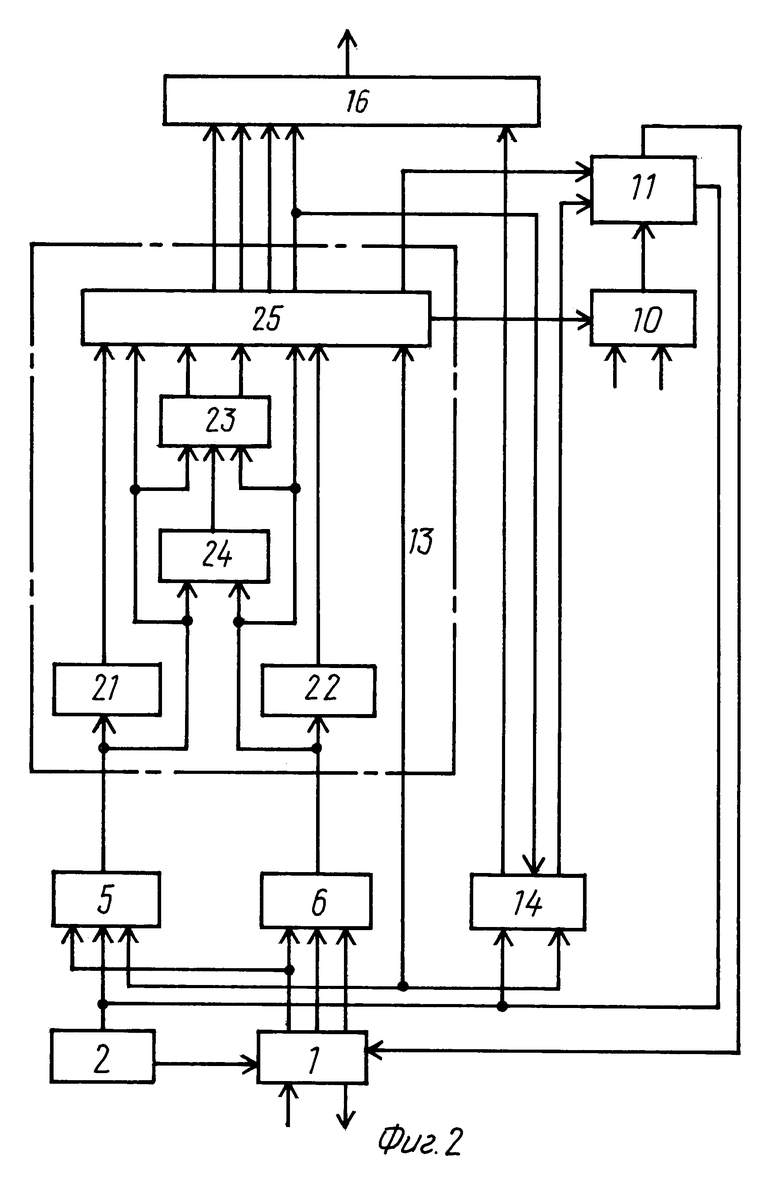

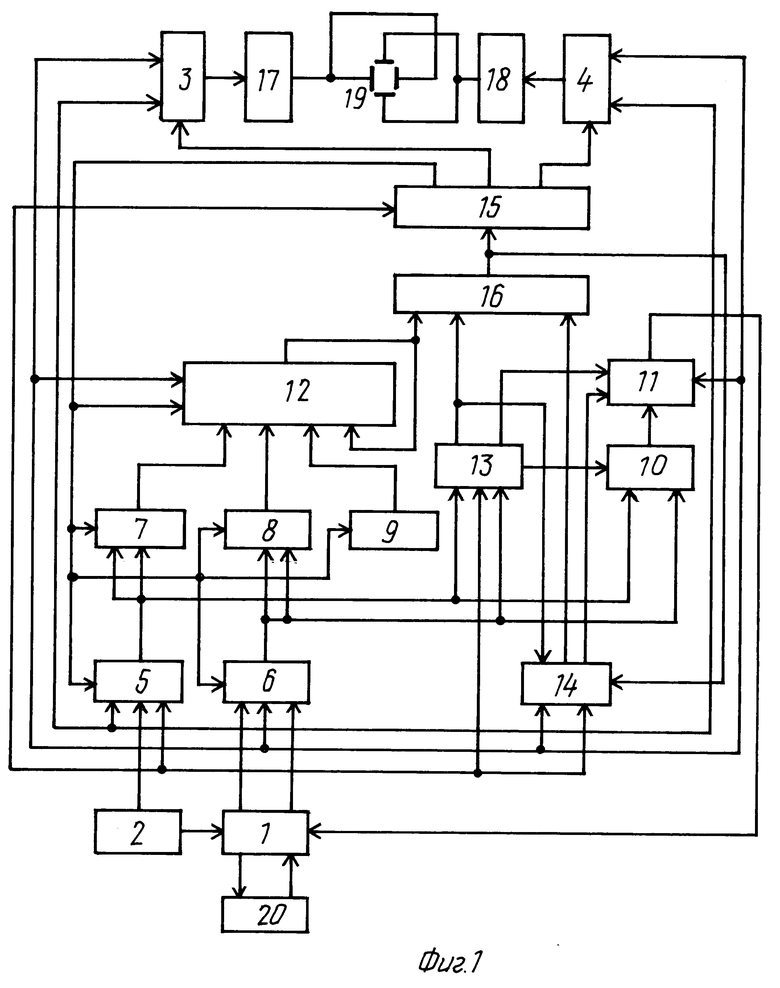

На фиг. 1 представлена блок-схема устройства; на фиг.2 блока дешифрации секторов; на фиг.3 октанты и значения логической функции В для дуги с направлением движения против и по часовой стрелке.

В устройстве реализуется метод формирования векторов и дуг, заключающийся в том, что на каждом шаге по знаку предварительно вычисленной оценочной функции определяется и осуществляется переход на следующую точку вектора или дуги, а так же формируется формула, по которой вычисляется оценочная функция для следующего шага.

Формулы перехода к следующей точке и расчета оценочной функции однозначно определяются тем, что в каком октанте координатной плоскости находится текущая точка вектора или дуги, причем для дуги дополнительным условием является направление движения по дуге.

В случае вектора для всех текущих точек октант определяется компонентами приращений вектора DX и DУ, для дуги октант текущей точки определяется компонентами текущего радиус-вектора DX(i) и DY(i), где i 1 N, а N число точек вектора или дуги.

Расчетные формулы для вектора имеют следующий вид:

D(o) SY˙DY2˙DY + SX˙DX2˙DX (1)

Если D(i-1) < 0, то D(i)

D(i-1) + SDY˙SX˙DX + SDX˙SY˙DY

X(i) X(i-1) + SDX˙SX

Y(i) Y(i 1) + SDY˙SY (2)

Если D(i-1) ≥ 0, то D(i)

D(i-1) + (SDY SDA) ˙SX˙DX +

+ (SDX SDY)˙SY˙DY

X(i) X(i-1) + SX

Y(i) Y(i-1) + SY (3) где D(i-1) и D(i) вычисляемая соответственно на (i-1)-ом и i-ом шаге оценочная функция,

D(0) предварительная оценочная функция для первого шага,

X(i), Y(i) координаты точки, на которую осуществляется переход на i-м шаге,

X(i-1), Y(i-1) координаты точки предыдущего шага

SX, SY, DX2, DY2, SDX, SDY функциональные коэффициенты, определяемые из условий:

SX sign(DX 1, если DX ≥ 0.

-1, если DC < 0 (4)

SY sign (DY 1, если DY ≥ 0

1- если DY < 0

DX2 1, еслиDX<DY|

-1/2, еслиDX| ≥DY|

DY2 -1/2, еслиDX| <DY|

1, еслиDX| ≥DY|

SDX 0, еслиDX| <DY| (5)

1, еслиDX| ≥DY|

SDY 1, если,DX| <DY|

0, еслиDX| ≥DY|

Расчетные формулы для дуги имеют вид

D(O) 3/4 + SDY˙DY2˙DY +

+ SDX˙DX2˙DX (6)

Если D(i-1) ≥ 0 В, то D(i)

D(i-1) + SDY˙DY(i-1) +

+ SDX˙DX(i-1) + 5/2

X(i) X(i-1) + SDX

Y(i) Y(i-1) + SDY (7)

Если D(i-1) < 0 В, то D(i) D(i-1) +

+ ADX˙DX(i-1) + ADY˙DY(i-1) + 3/2

X(i) X(i-1) + ADX

Y(i) Y(i-1) + ADY (8)

Если D(i-1) ≥ 0 В, то D(i)

D(i-1) + ADY ˙DY(i-1) +

+ ADX˙ DX(i-1) + 3/2

X(i) X(i-1) + ADX

Y(i) Y(i-1) + ADX (9)

Если D(i-1) < 0 В, то D(i)

D(i-1) + SDX ˙DX(i-1) +

+ SDY ˙DY(i-1) + 5/2

X(i) X(i-1) + SDX

Y(i) Y(i-1) + SDY (10) где SX sign (DX) 1, если DX ≥ 0

-1, если DX < 0 (11)

1, если DY ≥ 0

SY sign(DY) -1, если DY < 0 (12)

В формулы введены дополнительные логические функции А, В и функциональные коэффициенты ADX и ADY. Значения этих коэффициентов, функций А и В, а также коэффициентов SDX, SDY, DX2, DY2 зависят от направления движения по дуге.

Логическая функция В принимает значение 0 или 1 в зависимости от октанта, в котором находится текущая точка дуги. На фиг.3 показаны октанты и значения функции В для дуги с направлением движения против и по часовой стрелке

При переходе текущей точки из одного октанта в другой (чему соответствует изменение значения функции В) необходимо пересчитать значение оценочной функции по следующим формулам:

B _→ B: D(i-1) D(i-1)

SX ˙DX(i-1)/2 SY˙DY(i-1)/2

B _→ B: D(i-1) D(i-1)

SX˙DX(i-1) SY˙DY(i-1) (13) и только после этого продолжить итерационный процесс.

Устройство содержит блок 1 управления, генератор 2 тактовых импульсов, реверсивные счетчики 3 и 4 координат, реверсивные счетчики 5 и 6 приращений векторов, мультиплексоры 7, 8, блок 9 формирования контакта, мультиплексор 10, счетчик 11 импульсов, сумматор 12, дешифратор 13 (секторов), регистр (флагов условий) 14, блок 15 постоянной памяти, регистр 16 (адреса), цифро-аналоговые преобразователи 17 и 18, электроннолучевую трубку 19 (ЭЛТ).

Устройство работает под управлением процессора 20.

Дешифратор 13 секторов содержит блоки 21 и 22 оси Х и оси У, арифметическо-логический блок 23, блок 24 знака операции, узел 25 постоянной памяти.

Устройство работает следующим образом.

Синхронизация работы блоков осуществляется с помощью выработки генератором 2 тактовых импульсов, которые позволяют выделить начало, середину и конец такта.

При поступлении из процессора 20 команды блок 1 управления запоминает код команды и вырабатывает следующую последовательность управляющих сигналов, синхронизированных тактовыми импульсами.

На первом такте реализации команды вектор или дуга на выходах блока 1 вырабатывается импульсный сигнал приема, поступающего по шине данных на вход реверсивного счетчикам 5 приращения и устанавливаются на все время выполнения команды потенциальные сигналы V/D и направления движения по дуге по/против часовой стрелки DIR, поступающие на два из адресных входов блока 15, а так же на вход дешифратора 13 секторов.

Во втором такте на вход реверсивного счетчика 6 приращения DY поступает с выхода блока 1 импульсный сигнал приема DY.

Принятые значения DX и DY подаются на вход дешифратора 13 секторов, один из выходов которого управляет мультиплексором 10 для выбора большего изDX| и DY|

В третьем такте блок 1 вырабатывает сигнал приема N на счетчик импульсов 11 либо с шины данных в случае дуги, либо с выхода мультиплексора 10.

В начале каждого такта на регистр 16 адреса принимается информация с дешифратора 13 секторов, регистра 14 и со знакового разряда результата сумматора 12. Дешифратор 13 вырабатывает четырехразрядный код, по которому различаются 16-ть секторов (см. фиг.3). В зависимости от выполняемой операции вектор или дуга, в последнем случае и от направления движения, каждые два сектора образуют один октант.

Регистр (флагов условий) 14 формирует два флаговых сигнала, поступающих на адресный вход блока 15 через регистр 16, и фиксирующих такт вычисления начального значения оценочной функции и такт ее пересчета при смене октантов во время выполнения операции дуга.

Флаг начального условия устанавливается во втором такте, сбрасывается после вычисления начального значения оценочной функции в третьем такте.

В первой половине каждого такта блок 15 по входному адресу формирует в соответствии с вышеприведенными формулами управляющие сигналы, поступающие на сумматор 12, мультиплексоры 7 и 8, блок 9 формирования констант, реверсивные счетчики 5 и 6 приращений и счетчики 3 и 4 координат.

Эти сигналы определяют:

на сумматоре 12 количество и знаки операндов, участвующих в вычислении оценочной функции D(i);

на мультиплексорах 7 определяют выбор значения 1 или 1/2 функциональных коэффициентов SX и SY;

на блоке 9 выбор одной из четырех констант 0,3 (4,5) 2, 3/2, формируемых соответствующими потенциалами на информационных входах мультиплексора, собственно и составляющего блок 9;

на счетчиках 5 и 6 приращений и счетчиках 3 и 4 координат наличие и знак соответствующих приращений.

Таким образом, на входы сумматора 12 поступаютSDX|˙|DX|SDY|˙|DY| константа и с выхода этого же сумматора D(i-1).

В середине каждого такта происходит запуск сумматора 12 на вычисление по требуемой из (2, 3, 7-10) формуле значения D(i). В это же время происходит изменение значений на реверсивных счетчиках 3, 4, 5, 6.

В третьем такте описанным выше способом при установленном флаге начального условия вычисляется D(0) по формулам (1) или (6) без изменения значений DX, DY, координат Х, У.

С четвертого такта осуществляется итерационный процесс пошаговой реализации вектора или дуги. В каждом из этих расчетных тактов происходит уменьшение на единицу содержимого счетчика 11 импульсов. При обнулении счетчика он выдает блоку 1 сигнал о завершении текущей операции.

В процессе формирования дуги при смене октанта, т.е. изменении значения функции В, устанавливается флаг пересчета, и в следующем такте производится пересчет значения оценочной функции D(i-1) по формулам (13) без изменения содержимого как счетчиков 5, 6, 3 и 4 приращений и координат, так и счетчика 11 импульсов.

Управляющие сигналы, выделяемые блоком 13 дешифратора формируются на выходе узла 25 постоянной памяти.

Входными сигналами являются значения приращений DX и DY, а так же управляющие сигналы V/D и DIR от блока 1.

Наряду с выработкой 4-х разрядного кода сектора (один из разрядов этого кода имеет значение функции В) и, как указывалось выше, сигнала управления мультиплексором 10, дешифратора 13, исходя из знака принятого на счетчик 11 числа точек значения, формирует управляющий сигнал знака счета счетчика 11.

Блок 13 вырабатывает сигналы равенства нулю соответственно приращений DX и DY, сигнал равенстваDX|DY| и сигнал знака результата сравнения значенийDX| иDY|

Предложенное устройство обеспечивает скорость формирования линий как векторов, так и дуг порядка 125 нс на точку (тактовая частота работы устройства 8 МГц).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ НА ЭКРАНЕ ЭЛЕКТРОННО-ЛУЧЕВОЙ ТРУБКИ | 1992 |

|

RU2049362C1 |

| Генератор векторов | 1988 |

|

SU1596375A2 |

| Линейный интерполятор | 1987 |

|

SU1418751A1 |

| Устройство для отображения информации | 1990 |

|

SU1785035A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Графический интерполятор | 1985 |

|

SU1401509A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Цифровой линейный интерполятор | 1988 |

|

SU1624405A2 |

Использование: автоматика и вычислительная техника, при проектировании устройств отображения информации. Сущность изобретения: устройство содержит блок управления 1, генератор тактовых импульсов 2, четыре реверсивных счетчика 3, 4, 5, 6, три мультиплексора 7, 8, 10, блок формирования констант 9, счетчик импульсов 11, сумматор 12, дешифратор 13, блок постоянной памяти 15, два регистра 14, 16, два цифроаналоговых преобразователя 17, 18, ЭЛТ 19, процессор 20. 3 ил.

УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ВЕКТОРОВ И ДУГ НА ЭКРАНЕ ЭЛЕКТРОННО-ЛУЧЕВОЙ ТРУБКИ (ЭЛТ), содержащее генератор тактовых импульсов, первый выход которого соединен с тактовым входом блока управления, вход-выход которого является входом-выходом устройства, первый выход блока управления соединен с первыми информационными входами реверсивных счетчиков приращения векторов и реверсивных счетчиков координат X и Y, выходы которых подключены к входам цифроаналоговых преобразователей координат X и Y соответственно, выходы которых соединены с отклоняющей системой ЭЛТ, первый, второй и третий мультиплексоры, выход третьего мультиплексора соединен с информационным входом счетчика импульсов, выход которого соединен с управляющим входом блока управления, выходы реверсивных счетчиков приращения векторов подключены к информационным входам соответственно первого и второго мультиплексоров, сумматор, первый регистр и дешифратор, отличающееся тем, что, с целью повышения точности устройства, оно содержит блок постоянной памяти, второй регистр и блок формирования констант, выход первого регистра подключен к управляющему входу второго регистра и адресному входу блока постоянной памяти, управляющий вход которого подключен к второму выходу блока управления, соединенному с входом сброса второго регистра, управляющему входу дешифратора и вторым информационным входам реверсивных счетчиков приращений векторов, счетные входы которых подключены к второму выходу генератора тактовых импульсов, соединенному с тактовым входом второго регистра, счетными входами реверсивных счетчиков координат и счетчика импульсов и тактовым входом сумматора, выход которого подключен к первому управляющему входу первого регистра и входу сброса сумматора, информационные входы сумматора подключены к выходам первого и второго мультиплексоров и блока формирования констант, управляющий вход которого соединен с первым выходом блока постоянной памяти, который подключен к управляющим входам сумматора, первого и второго мультиплексоров и реверсивных счетчиков приращений векторов, второй и третий выходы блока постоянной памяти подключены к управляющим входам реверсивных счетчиков координат, информационные входы дешифратора к выходам реверсивных счетчиков приращений векторов, управляющий вход к второму выходу блока управления, первый выход дешифратора к первому информационному входу второго регистра, второй выход к управляющему входу счетчика импульсов, вход сброса которого соединен с первым выходом второго регистра, второй выход которого подключен ко второму информационному входу первого регистра, третий выход дешифратора соединен с управляющим входом третьего мультиплексора, информационные входы которого подключены к выходам реверсивных счетчиков приращений векторов.

| Устройство для отображения векторов и дуг окружностей на экране электронно-лучевой трубки | 1987 |

|

SU1451760A2 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1995-12-10—Публикация

1990-03-30—Подача