(О

Nj

О

сд

о со

iPuz.

Изобретение относится к вычислительной технике и может быть иснользовано в устройствах отображения и преобразования информации, преимущественно в устройствах отображения графической информации на электронно-лучевых трубах (ЭЛТ).

Цель изобретения - увеличение производительности интерполятора при отображении объектов, содержащих дуги и окружности.

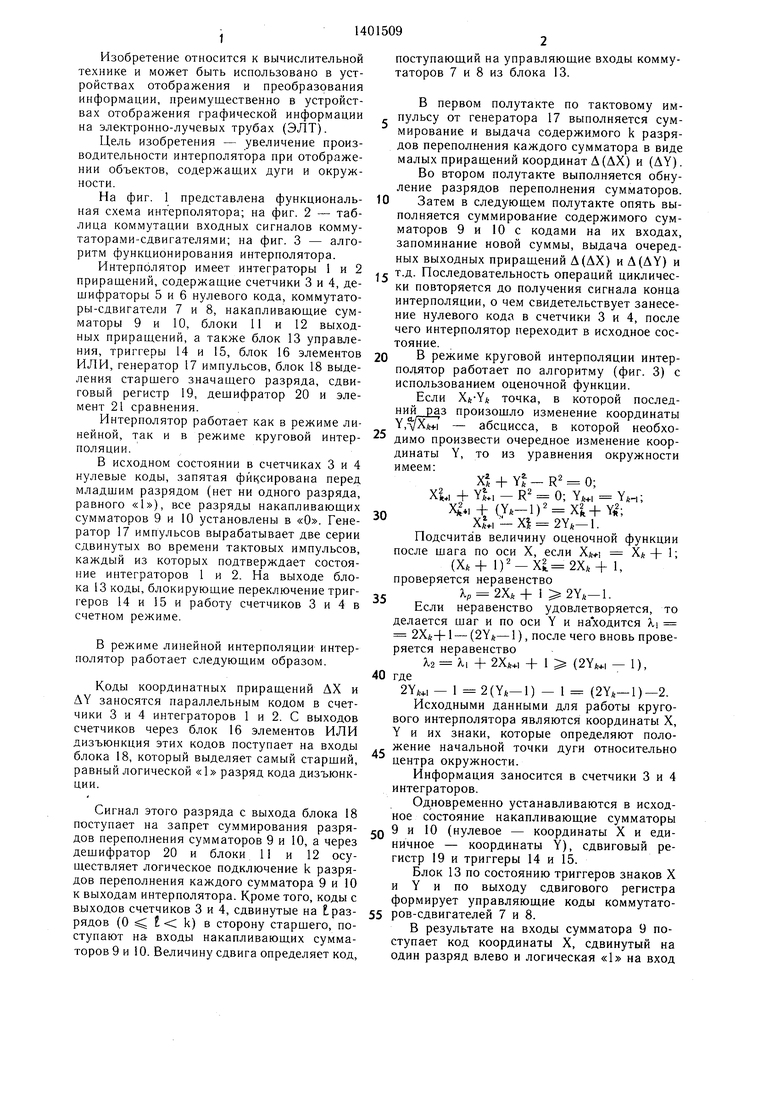

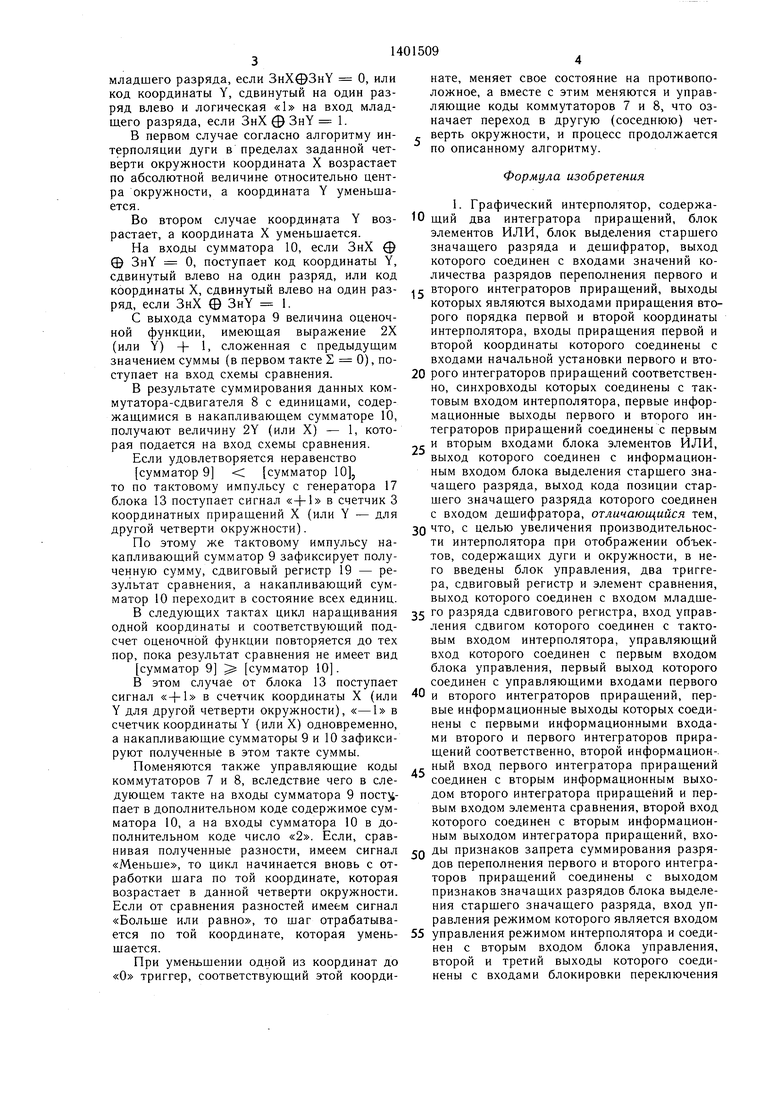

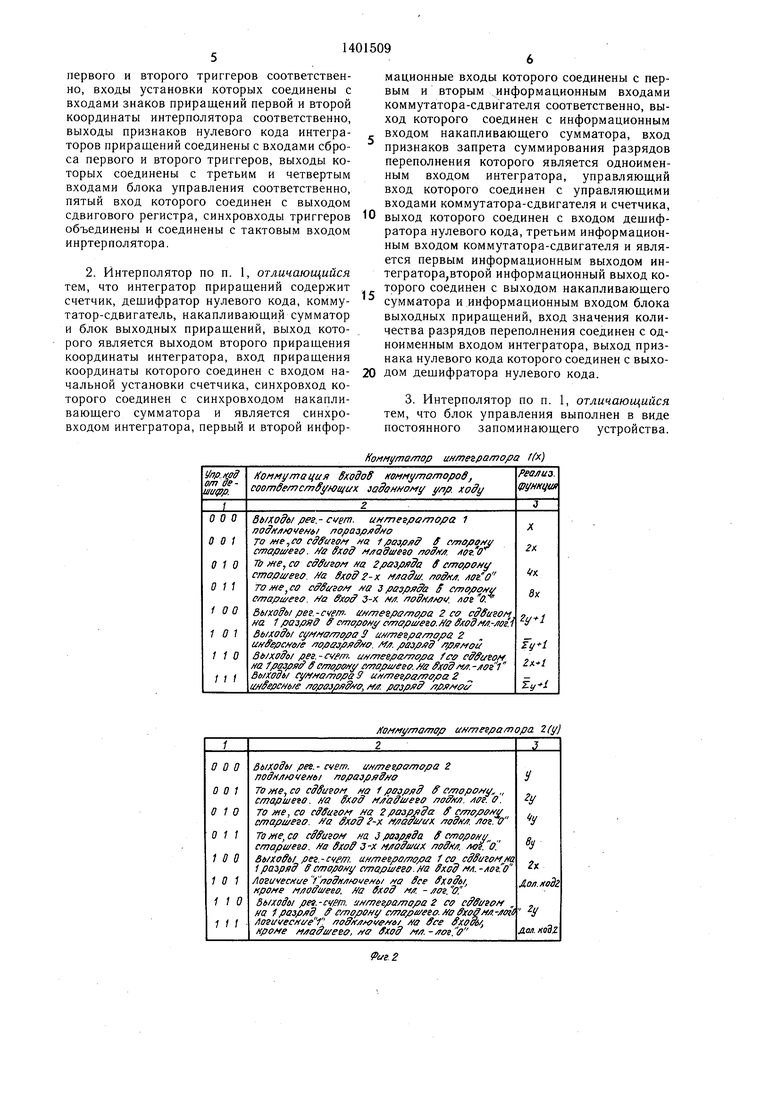

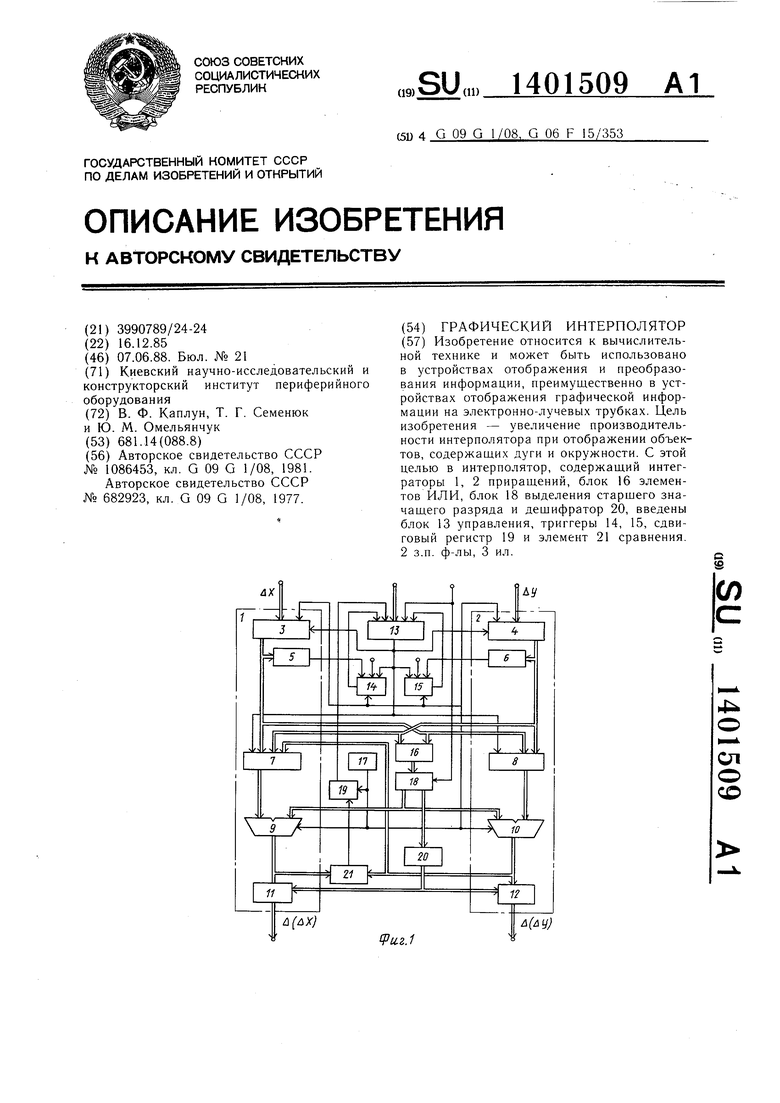

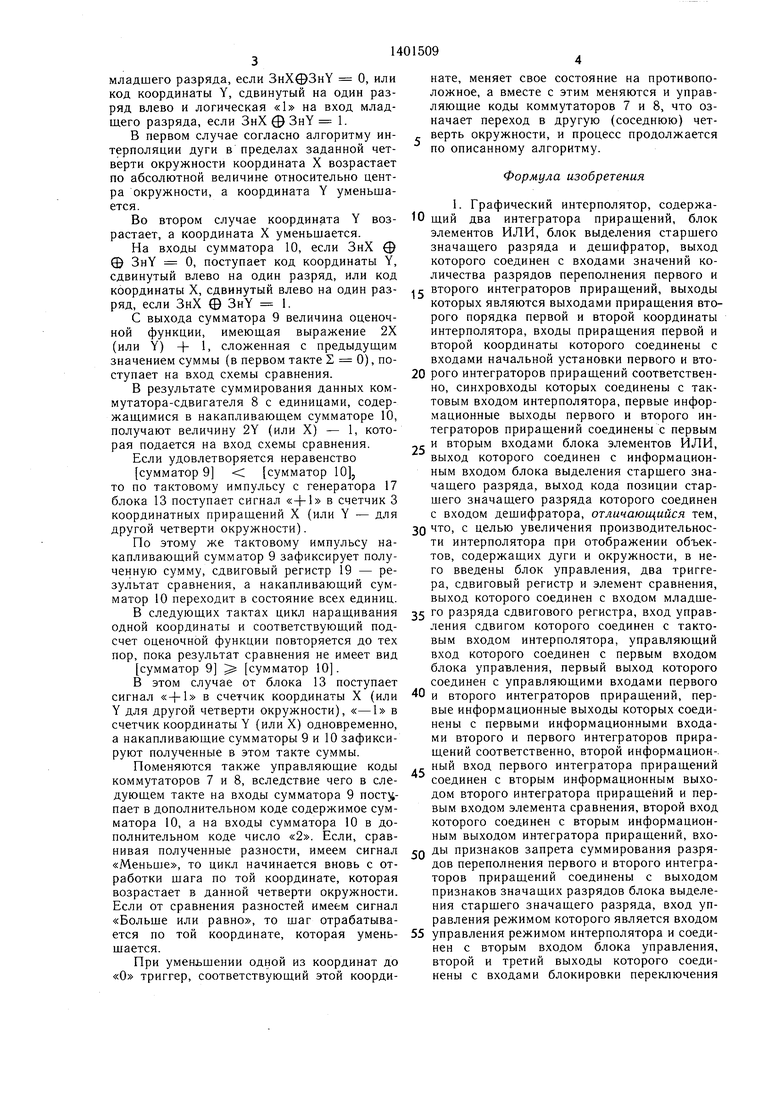

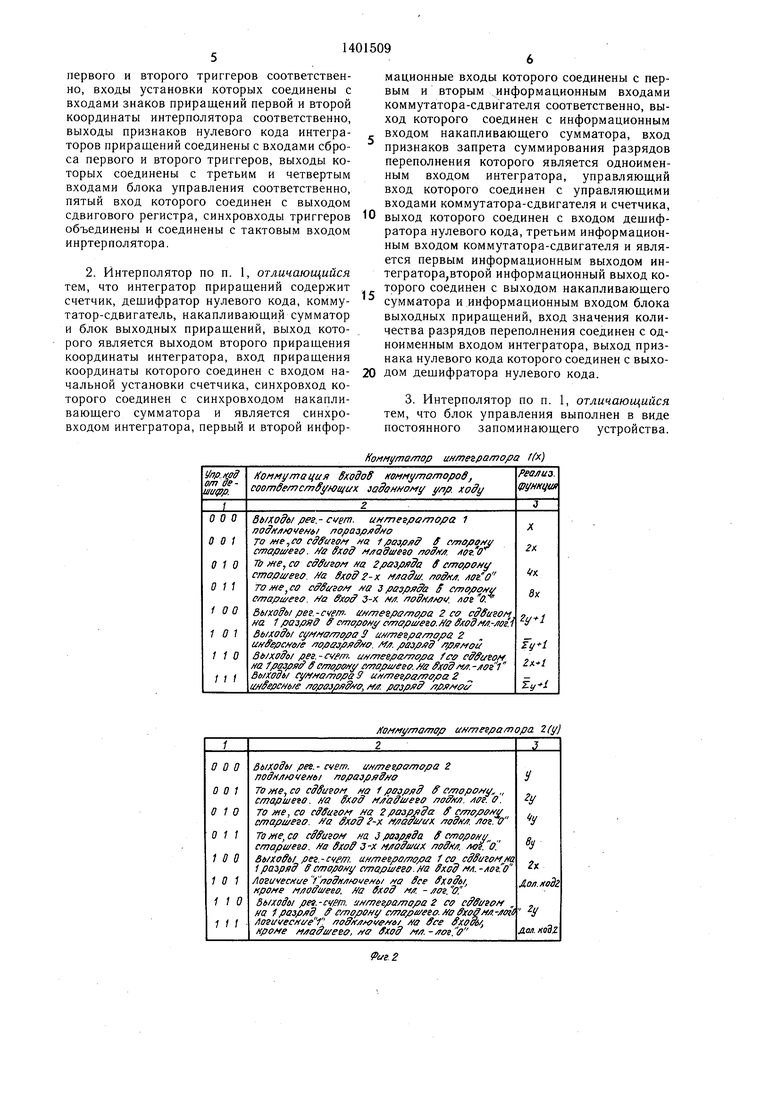

На фиг. 1 представлена функциональная схема интерполятора; на фиг. 2 - таблица коммутации входных сигналов комму- таторами-сдвигателями; на фиг. 3 - алгоритм функционирования интерполятора.

поступающий на управляющие входы коммутаторов 7 и 8 из блока 13.

В первом полутакте по тактовому им- пульсу от генератора 17 выполняется суммирование и выдача содержимого k разрядов переполнения каждого сумматора в виде малых приращений координат А (АХ) и (AY).

Во втором полутакте выполняется обнуление разрядов переполнения сумматоров. 10 Затем в следующем полутакте опять выполняется суммирование содержимого сумматоров 9 и 10 с кодами на их входах, запоминание новой суммы, выдача очередных выходных приращений А (АХ) и A(AY) и

Интерполятор имеет интеграторы 1 и 2 . т.д. Последовательность операций цикличесГГЛОШ/ЛНиЙ М, OllllJjri г rlii T t 1 TllVtjQ 1.1/1ТТЛ ..

приращений, содержащие счетчики 3 и 4, де- щифраторы 5 и 6 нулевого кода, коммутато- ры-сдвигатели 7 и 8, накапливающие сумматоры 9 и 10, блоки 11 и 12 выходных приращений, а также блок 13 управления, триггеры 14 и 15, блок 16 элементов ИЛИ, генератор 17 импульсов, блок 18 выделения старщего значащего разряда, сдвиговый регистр 19, дешифратор 20 и элемент 21 сравнения.

Интерполятор работает как в режиме линейной, так и в режиме круговой интерполяции.

В исходном состоянии в счетчиках 3 и 4 нулевые коды, запятая фиксирована перед младшим разрядом (нет ни одного разряда, равного «1), все разряды накапливающих сумматоров 9 и 10 установлены в «О. Генератор 17 импульсов вырабатывает две серии сдвинутых во времени тактовых импульсов, каждый из которых подтверждает состояние интеграторов 1 и 2. На выходе блока 13 коды, блокирующие переключение триггеров 14 и 15 и работу счетчиков 3 и 4 в счетном режиме.

В режиме линейной интерполяции интерполятор работает следующим образом.

Коды координатных приращений АХ и AY заносятся параллельным кодом в счетчики 3 и 4 интеграторов 1 и 2. С выходов счетчиков через блок 16 элементов ИЛИ дизъюнкция этих кодов поступает на входы блока 18, который выделяет самый старщий, равный логической «1 разряд кода дизъюнкции.

Сигнал этого разряда с выхода блока 18 поступает на запрет суммирования разрядов переполнения сумматоров 9 и 10, а через дещифратор 20 и блоки 11 и 12 осуществляет логическое подключение k разрядов переполнения каждого сумматора 9 и 10 к выходам интерполятора. Кроме того, коды с выходов счетчиков 3 и 4, сдвинутые на t разрядов (О k) в сторону старщего, поступают на входы накапливающих сумматоров 9 и 10. Величину сдвига определяет код.

20

25

30

35

ки повторяется до получения сигнала конца интерполяции, о чем свидетельствует занесение нулевого кода в счетчики 3 и 4, после чего интерполятор переходит в исходное состояние.

В режиме круговой интерполяции интерполятор работает по алгоритму (фиг. 3) с использованием оценочной функции.

Если точка, в которой последний раз произошло изменение координаты У,Л/ХА+| - абсцисса, в которой необходимо произвести очередное изменение координаты У, то из уравнения окружности имеем:

Х + Y - R2 0; Xjt.ji -(- - R 0; Yft+i Y|fe-i;

x., H (,-i) - XI 2Y,- 1.

Подсчитав величину оценочной функции после щага по оси X, если Xk+i Х + 1;

( 1) 1, проверяется неравенство

K, 2Xk+ 1 2Y/,-1.

45

Если неравенство удовлетворяется, то делается щаг и по оси Y и на ходится Ki 2Xk+1 - (2Yft- 1), после чего вновь проверяется неравенство

;.2 .; + 2Х, + 1 (2Y,i - 1), 40 где

2Y,, - 1 2() - 1 ()-2.

Исходными данными для работы кругового интерполятора являются координаты X, Y и их знаки, которые определяют положение начальной точки дуги относительно центра окружности.

Информация заносится в счетчики 3 и 4 интеграторов.

Одновременно устанавливаются в исходное состояние накапливающие сумматоры 9 и 10 (нулевое - координаты X и единичное - координаты Y), сдвиговый регистр 19 и триггеры 14 и 15.

Блок 13 по состоянию триггеров знаков X и Y и по выходу сдвигового регистра формирует управляющие коды коммутато- ров-сдвигателей 7 и 8.

В результате на входы сумматора 9 поступает код координаты X, сдвинутый на один разряд влево и логическая «1 на вход

50

55

поступающий на управляющие входы коммутаторов 7 и 8 из блока 13.

В первом полутакте по тактовому им- пульсу от генератора 17 выполняется суммирование и выдача содержимого k разрядов переполнения каждого сумматора в виде малых приращений координат А (АХ) и (AY).

Во втором полутакте выполняется обнуление разрядов переполнения сумматоров. 0 Затем в следующем полутакте опять выполняется суммирование содержимого сумматоров 9 и 10 с кодами на их входах, запоминание новой суммы, выдача очередных выходных приращений А (АХ) и A(AY) и

т.д. Последовательность операций цикличес ..

0

5

0

5

ки повторяется до получения сигнала конца интерполяции, о чем свидетельствует занесение нулевого кода в счетчики 3 и 4, после чего интерполятор переходит в исходное состояние.

В режиме круговой интерполяции интерполятор работает по алгоритму (фиг. 3) с использованием оценочной функции.

Если точка, в которой последний раз произошло изменение координаты У,Л/ХА+| - абсцисса, в которой необходимо произвести очередное изменение координаты У, то из уравнения окружности имеем:

Х + Y - R2 0; Xjt.ji -(- - R 0; Yft+i Y|fe-i;

x., H (,-i) - XI 2Y,- 1.

Подсчитав величину оценочной функции после щага по оси X, если Xk+i Х + 1;

( 1) 1, проверяется неравенство

K, 2Xk+ 1 2Y/,-1.

5

Если неравенство удовлетворяется, то делается щаг и по оси Y и на ходится Ki 2Xk+1 - (2Yft- 1), после чего вновь проверяется неравенство

;.2 .; + 2Х, + 1 (2Y,i - 1), 0 где

2Y,, - 1 2() - 1 ()-2.

Исходными данными для работы кругового интерполятора являются координаты X, Y и их знаки, которые определяют положение начальной точки дуги относительно центра окружности.

Информация заносится в счетчики 3 и 4 интеграторов.

Одновременно устанавливаются в исходное состояние накапливающие сумматоры 9 и 10 (нулевое - координаты X и единичное - координаты Y), сдвиговый регистр 19 и триггеры 14 и 15.

Блок 13 по состоянию триггеров знаков X и Y и по выходу сдвигового регистра формирует управляющие коды коммутато- ров-сдвигателей 7 и 8.

В результате на входы сумматора 9 поступает код координаты X, сдвинутый на один разряд влево и логическая «1 на вход

0

5

младшего разряда, если ЗнХфЗнУ О, или код координаты Y, сдвинутый на один разряд влево и логическая «1 на вход млад- щего разряда, если ЗнХ ф ЗнУ 1.

В первом случае согласно алгоритму интерполяции дуги в пределах заданной четверти окружности координата X возрастает по абсолютной величине относительно центра окружности, а координата Y уменьшается.

Во втором случае координата Y возрастает, а координата X уменьшается.

На входы сумматора 10, если ЗнХ ф ф 3HY О, поступает код координаты Y, сдвинутый влево на один разряд, или код

нате, меняет свое состояние на противоположное, а вместе с этим меняются и управляющие коды коммутаторов 7 и 8, что означает переход в другую (соседнюю) чет- г верть окружности, и процесс продолжается по описанному алгоритму.

Формула изобретения

1. Графический интерполятор, содержа- 10 щий два интегратора приращений, блок элементов ИЛИ, блок выделения старшего значащего разряда и дешифратор, выход которого соединен с входами значений количества разрядов переполнения первого и

которых являются выходами приращения второго порядка первой и второй координаты интерполятора, входы приращения первой и второй координаты которого соединены с входами начальной установки первого и вто- 20 рого интеграторов приращений соответственно, синхровходы которых соединены с тактовым входом интерполятора, первые информационные выходы первого и второго интеграторов приращений соединены с первым

25

и вторым входами блока элементов ИЛИ,

координаты X, сдвинутый влево на один раз- второго интеграторов приращений, выходы ряд, если ЗнХ © 3HY 1.

С выхода сумматора 9 величина оценочной функции, имеющая выражение 2Х (или Y) + 1, сложенная с предыдущим значением суммы (в первом такте Е 0), поступает на вход схемы сравнения.

В результате суммирования данных ком- мутатора-сдвигателя 8 с единицами, содержащимися в накапливающем сумматоре 10, получают величину 2Y (или X) - 1, которая подается на вход схемы сравнения.

Если удовлетворяется неравенство

сумматор 9 сумматор 10, то по тактовому импульсу с генератора 17 блока 13 поступает сигнал «4-Ь в счетчик 3 координатных приращений X (или Y - для другой четверти окружности).

По этому же тактовому импульсу на- капливаюший сумматор 9 зафиксирует полученную сумму, сдвиговый регистр 19 - результат сравнения, а накапливающий сумматор 10 переходит в состояние всех единиц.

В следующих тактах цикл наращивания одной координаты и соответствующий подсчет оценочной функции повторяется до тех пор, пока результат сравнения не имеет вид

сумматор 9 сумматор 10.

В этом случае от блока 13 поступает сигнал «-J-1 в счетчик координаты X (или Y для другой четверти окружности), «-1 в счетчик координаты Y (или X) одновременно, а накапливающие сумматоры 9 и 10 зафиксируют полученные в этом такте суммы.

Поменяются также управляющие коды коммутаторов 7 и 8, вследствие чего в следующем такте на входы сумматора 9 nocrji- пает в дополнительном коде содержимое сумматора 10, а на входы сумматора 10 в дополнительном коде число «2. Если, сраввыход которого соединен с информационным входом блока выделения старщего значащего разряда, выход кода позиции старшего значащего разряда которого соединен с входом дещифратора, отличающийся тем,

30 что, с целью увеличения производительности интерполятора при отображении объектов, содержащих дуги и окружности, в него введены блок управления, два триггера, сдвиговый регистр и элемент сравнения, выход которого соединен с входом младше35 го разряда сдвигового регистра, вход управления сдвигом которого соединен с тактовым входом интерполятора, управляющий вход которого соединен с первым входом блока управления, первый выход которого соединен с управляющими входами первого

40 и второго интеграторов приращений, первые информационные выходы которых соединены с первыми информационными входами второго и первого интеграторов приращений соответственно, второй информационный вход первого интегратора приращений соединен с вторым информационным выходом второго интегратора приращений и первым входом элемента сравнения, второй вход которого соединен с вторым информационным выходом интегратора приращений, вхонате, меняет свое состояние на противоположное, а вместе с этим меняются и управляющие коды коммутаторов 7 и 8, что означает переход в другую (соседнюю) чет- верть окружности, и процесс продолжается по описанному алгоритму.

Формула изобретения

1. Графический интерполятор, содержа- щий два интегратора приращений, блок элементов ИЛИ, блок выделения старшего значащего разряда и дешифратор, выход которого соединен с входами значений количества разрядов переполнения первого и

которых являются выходами приращения второго порядка первой и второй координаты интерполятора, входы приращения первой и второй координаты которого соединены с входами начальной установки первого и вто- 0 рого интеграторов приращений соответственно, синхровходы которых соединены с тактовым входом интерполятора, первые информационные выходы первого и второго интеграторов приращений соединены с первым

5

и вторым входами блока элементов ИЛИ,

второго интеграторов приращений, выходы

выход которого соединен с информационным входом блока выделения старщего значащего разряда, выход кода позиции старшего значащего разряда которого соединен с входом дещифратора, отличающийся тем,

0 что, с целью увеличения производительности интерполятора при отображении объектов, содержащих дуги и окружности, в него введены блок управления, два триггера, сдвиговый регистр и элемент сравнения, выход которого соединен с входом младше5 го разряда сдвигового регистра, вход управления сдвигом которого соединен с тактовым входом интерполятора, управляющий вход которого соединен с первым входом блока управления, первый выход которого соединен с управляющими входами первого

0 и второго интеграторов приращений, первые информационные выходы которых соединены с первыми информационными входами второго и первого интеграторов приращений соответственно, второй информационный вход первого интегратора приращений соединен с вторым информационным выходом второго интегратора приращений и первым входом элемента сравнения, второй вход которого соединен с вторым информационным выходом интегратора приращений, вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейно-круговой интерполятор | 1978 |

|

SU746431A1 |

| Линейно-круговой интерполятор | 1987 |

|

SU1462250A2 |

| Цифровой линейный интерполятор | 1977 |

|

SU682923A1 |

| Линейно-круговой интерполятор | 1986 |

|

SU1312530A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU658528A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах отображения и преобразования информации, преимущественно в устройствах отображения графической информации на электронно-лучевых трубках. Цель изобретения - увеличение производительности интерполятора при отображении объектов, содержащих дуги и окружности. С этой целью в интерполятор, содержащий интеграторы 1, 2 приращений, блок 16 элементов ИЛИ, блок 18 выделения старшего значащего разряда и дещифратор 20, введены блок 13 управления, триггеры 14, 15, сдвиговый регистр 19 и элемент 21 сравнения. 2 з.п. ф-лы, 3 ил.

нивая полученные разности, имеем сигнал д ды признаков запрета суммирования разря«Меньше, то цикл начинается вновь с отработки щага по той координате, которая возрастает в данной четверти окружности. Если от сравнения разностей имеем сигнал «Больше или равно, то шаг отрабатывадов переполнения первого и второго интеграторов приращений соединены с выходом признаков значащих разрядов блока выделения старщего значащего разряда, вход управления режимом которого является входом

ется по той координате, которая умень- 55 управления режимом интерполятора и соеди- шается.

При уменьшении одной из координат до «О триггер, соответствующий этой координен с вторым входом блока управления, второй и третий выходы которого соединены с входами блокировки переключения

ды признаков запрета суммирования разрядов переполнения первого и второго интеграторов приращений соединены с выходом признаков значащих разрядов блока выделения старщего значащего разряда, вход управления режимом которого является входом

управления режимом интерполятора и соеди-

нен с вторым входом блока управления, второй и третий выходы которого соединены с входами блокировки переключения

первого и второго триггеров соответственно, входы установки которых соединены с входами знаков приращений первой и второй координаты интерполятора соответственно, выходы признаков нулевого кода интеграторов приращений соединены с входами сброса первого и второго триггеров, выходы которых соединены с третьим и четвертым входами блока управления соответственно, пятый вход которого соединен с выходом сдвигового регистра, синхровходы триггеров объединены и соединены с тактовым входом инртерполятора.

Выходы рее. - пет. имтег/эсглюра 2 поднлю ены гго/уазряд о

То ме. со cSSueofi ffo 1 разряд ff с/тгорону, „ старшего, ffa &код м.а а&шеео /7off/(.a. /le. О. Томе, со cffSuio/ на 2/ азряЗа ff cma/yow старшего, //а Sxod /-х waffi t/if. fod/f.a. /юг. О

То , со cffffuso/v на J раэряЗа ff сторону стари/fso. ffa ffxoff 3-х fijfo a/ux noff/ /i. лог. о. Вь/xoffb/ /оег. - cvfm. антеера/ло/уа / со сд&игон/а 1 разряд ff emopOHi/ старшего, ла $ход ли. -лог. О

Логичесхие f f7off/(/ jve//t / See fxofft/, кроме M/roffiaeeo. //a Sxod /w - лог. О 5b/xodtii pet.-cvgm. интегра/пора 2 со cffffi/ioff , на 1 розрлЗ ff с/тгарону са7ара/еео.//о ffxo&ffA-. /losuvec/ft/e f (.af fi/ffff6/ /fa fee fxo№/, нроме M affa/eeo, /fff ffxod м/r.-.ffoг.(

0

мационные входы которого соединены с первым и вторым информационным входами коммутатора-сдвигателя соответственно, выход которого соединен с информационным входом накапливающего сумматора, вход признаков запрета суммирования разрядов переполнения которого является одноименным входом интегратора, управляющий вход которого соединен с управляющими входами коммутатора-сдвигателя и счетчика, выход которого соединен с входом дещиф- ратора нулевого кода, третьим информационным входом коммутатора-сдвигателя и является первым информационным выходом ин- тегратора,второй информационный выход которого соединен с выходом накапливающего сумматора и информационным входом блока выходных приращений, вход значения количества разрядов переполнения соединен с одноименным входом интегратора, выход признака нулевого кода которого соединен с выходом дещифратора нулевого кода.

5

0

HofiMi/mofnop инте&ратора ffx)

(ofiMymamap uf/fnesflamopa 2(i/)

У

y y

8y

ZK

o/j.f/od2

y

дал. Ka3z

4Х 0, ила знх. 0

начало )

, 4Х или @ f

| Устройство для отображения векторов и дуг окружностей на экране электронно-лучевой трубки | 1981 |

|

SU1086453A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Цифровой линейный интерполятор | 1977 |

|

SU682923A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1988-06-07—Публикация

1985-12-16—Подача