Изобретение относится к полупроводниковому устройству неразрушаемой памяти и способу ее программирования, более точно к стираемому и электрически программируемому ПЗУ, имеющему ячейки в виде структур И-НЕ, и способу, дающему возможность оптимизированного программирования данных, использующему вышеуказанное ПЗУ.

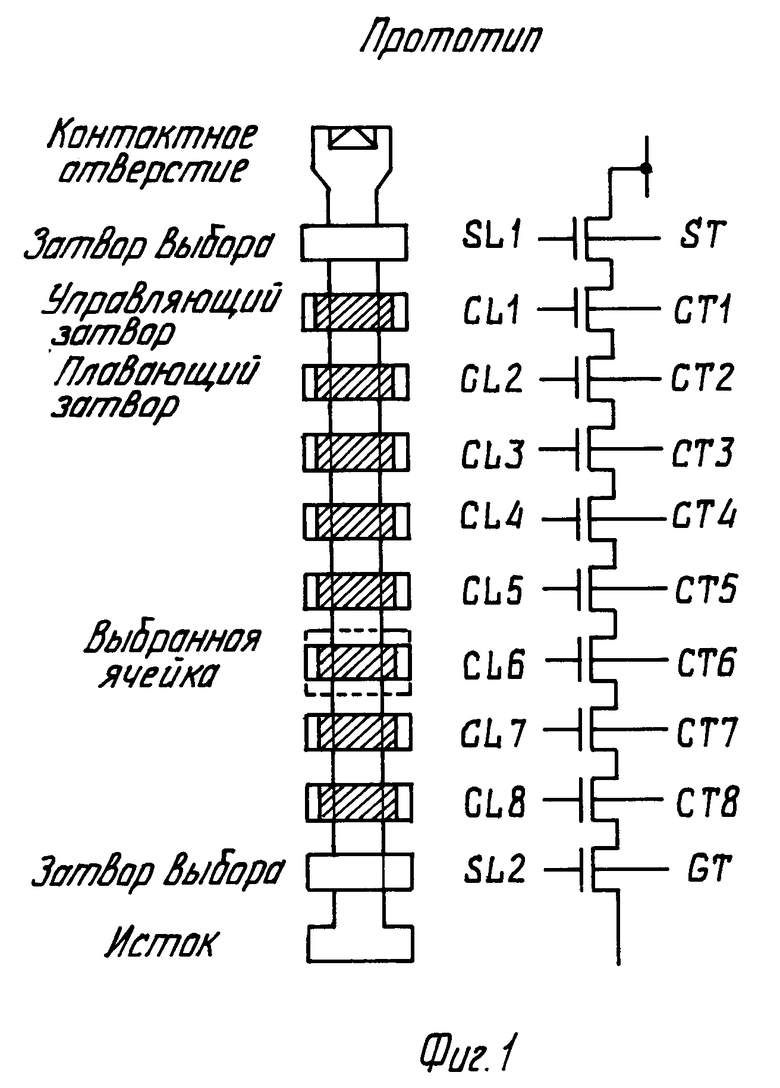

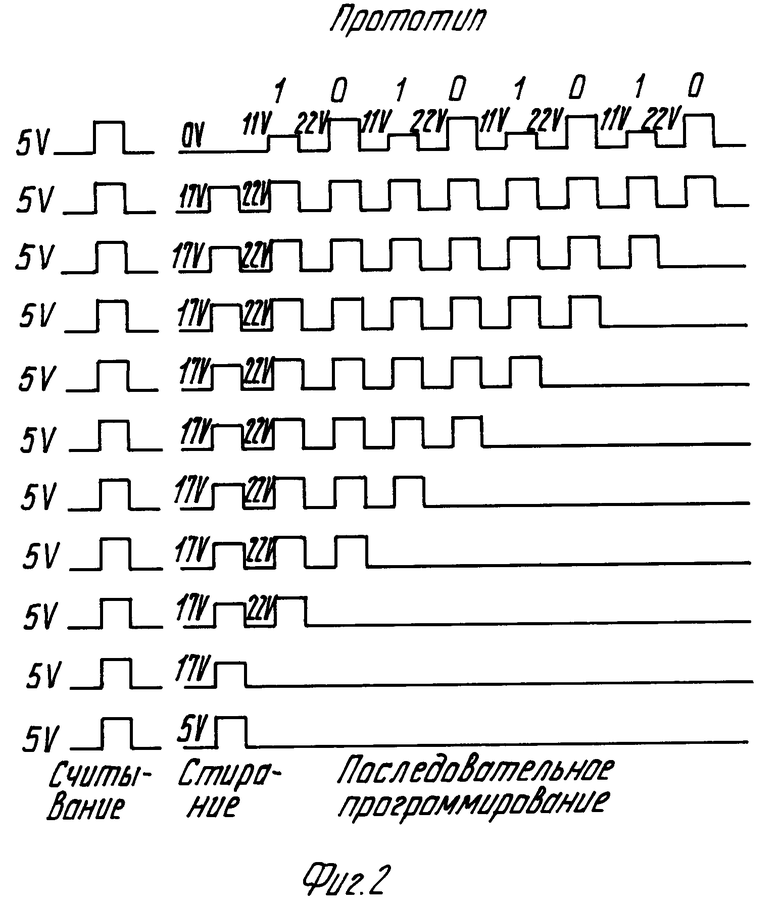

На фиг. 1 показана обычная ячейка структуры НЕ-И первого поколения и ее эквивалентная схема, вид сверху; на фиг. 2 условия управляющих напряжений во время операции считывания и временная диаграмма управляющих напряжении во время операций стирания и программирования стираемой и электрически программируемой памяти, имеющей ячейку структуры И-НЕ первого поколения.

Рабочие условия выбранной ячейки при стирании и программировании в обычной стираемой и электрически программируемой памяти первого поколения следующие. Во-первых, при стирании путем подачи напряжения стирания (17 В) на затвор CL 5 выбранной ячейки CT 5 и напряжения OB на сток ячейки из стока в плавающий затвор за счет F-N туннельного эффекта (Фоулера-Нордхейма) инжектируются электроны, так что пороговое напряжение ячейки становится положительным.

При программировании путем подачи напряжения OB на затвор выбранной ячейки CT 5 и напряжения программирования (22В) на ее сток за счет F-N туннельного эффекта электроны эмиттируются из плавающего затвора в сток ячейки, так что пороговое напряжение ячейки становится отрицательным (см. Журнал по твердотельным схемам института инженеров электриков, октябрь 1989, с. 1238 1243). Следовательно, при стирании и программировании на тонкий оксидный слой для создания туннельного эффекта со стороны стока ячейки непрерывно прикладывается удар, который воздействует на прочность (число циклов записи) и сохранность данных (характеристику сохранения заряда плавающего затвора) ячейки. В частности, если размеры ячейки существенно уменьшаются при достижении более высоких плотностей и емкостей, вышеуказанная характеристика надежности ухудшается еще более.

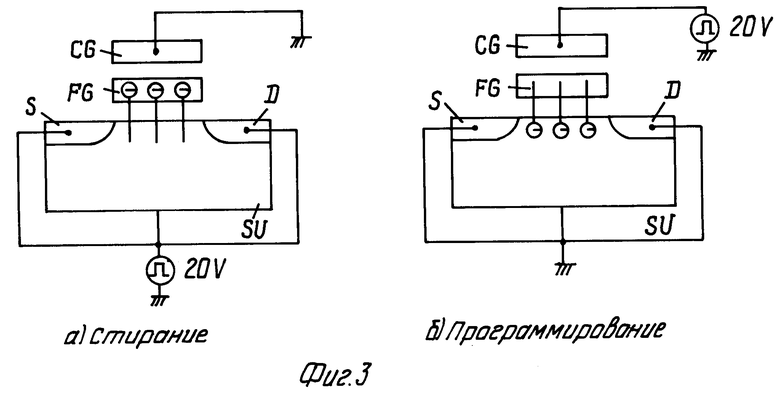

Фиг. 3 (а и б) представляют схематические виды ячейки для иллюстрирования операции стирания и программирования стираемой и электрически программируемой памяти, имеющей обычную ячейку структуры И-НЕ второго поколения.

В стираемой и электрически программируемой памяти второго поколения при стирании (фиг. 3,а) к затвору CG выбранной ячейки прикладывается напряжение OB, а к подложке SU, истоку S и стоку D -напряжение стирания (20В), так что электроны эмиттируются из плавающего затвора FG ячейки в подложку SU, что делает пороговое напряжение ячейки отрицательным. При программировании (фиг. 3,б) к затвору CG выбранной ячейки прикладывается напряжение программирования (18В), а к подложке SU, истоку S и стоку D прикладывается OB, так что электроны инжектируются из подложки SU в плавающий затвор FG ячейки, что делает пороговое напряжение ячейки положительным. То есть эти рабочие условия противоположны рабочим условиям стираемой и электрически программируемой памяти первого поколения, а инжекция и эмиттирование электронов не ограничены до стока ячейки, но возникают через ее плавающий затвор, подложку и сток, так же как и сток. Следовательно, ток утечки через тонкий запорный оксидный слой для создания туннельного эффекта, который вызывает удар при стирании и программировании, может быть уменьшен, тем самым значительно повышая надежность ячейки. В дополнение к этому пороговое напряжение ячейки во время стирания отрицательно и проблема перестирания является решенной (см. Симпозиум по СБИС технологии, 1990, с. 129 и 130).

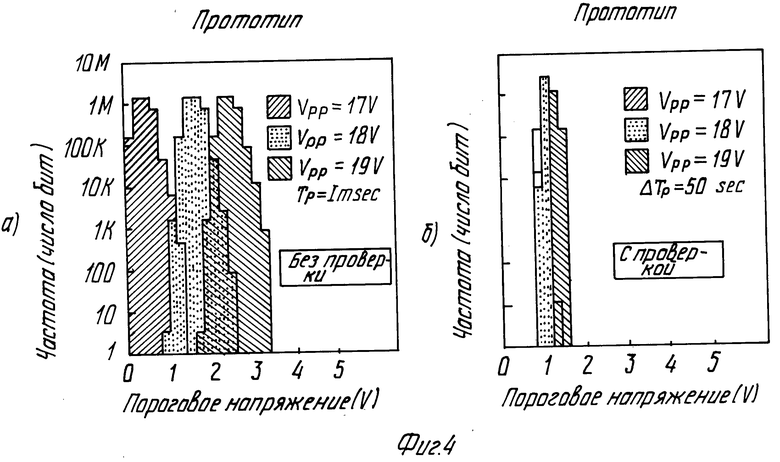

Однако, как показано на фиг. 4,а, поскольку из-за больших изменений напряжения, вызываемых изменениями параметров процесса во время программирования ячейки в стираемой и электрически программируемой памяти второго поколения, характеристика распределения порогового напряжения программируемой ячейки ухудшается, то возникает явление перепрограммирования. Другими словами, даже если в пределах ячеечной цепочки структур НЕ-И стираемой и электрически программируемой памяти перепрограммирована только одна ячейка, то не считывается вся цепочка ячеек. Соответственно, чтобы поддержать оптимальные условия программирования, требуется некоторое устройство для предотвращения перепрограммирования.

Когда, как показано на фиг. 4,б, программирование повторяется при проверке программы, можно заметить, что пороговое напряжение ячейки распределено равномерно.

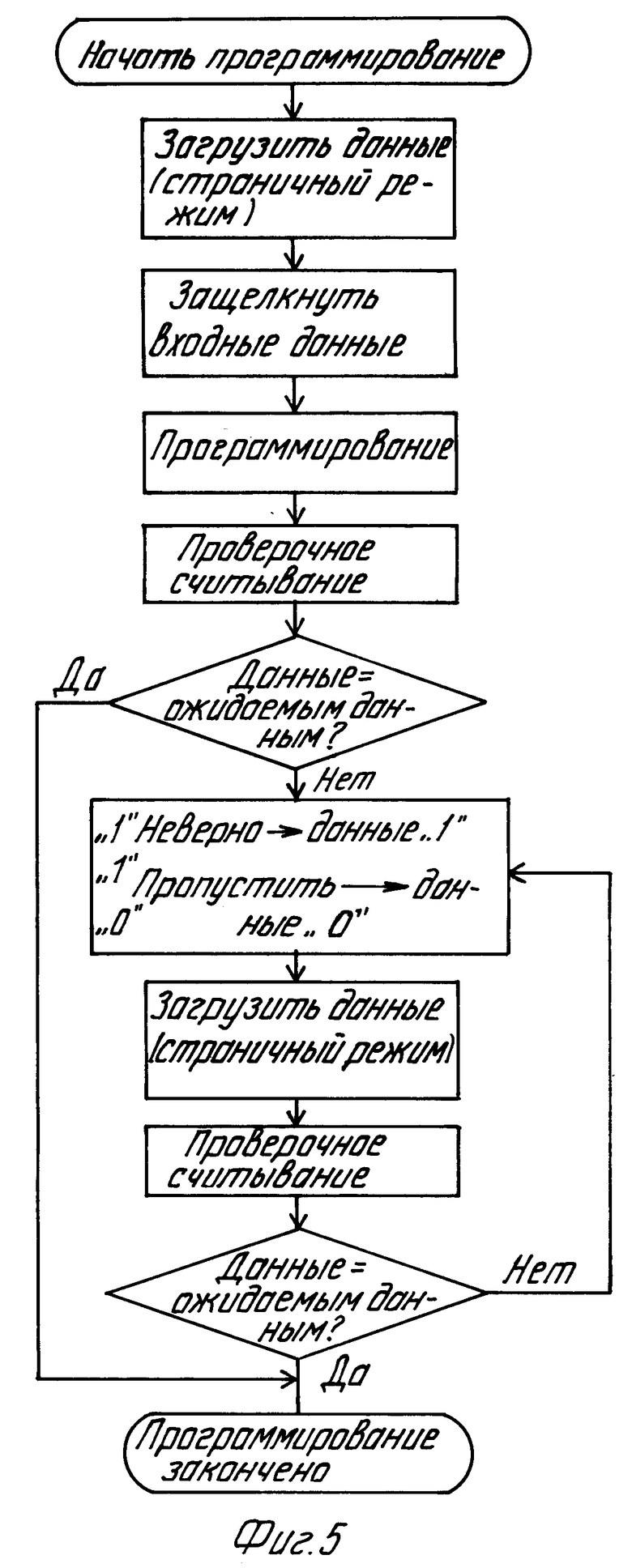

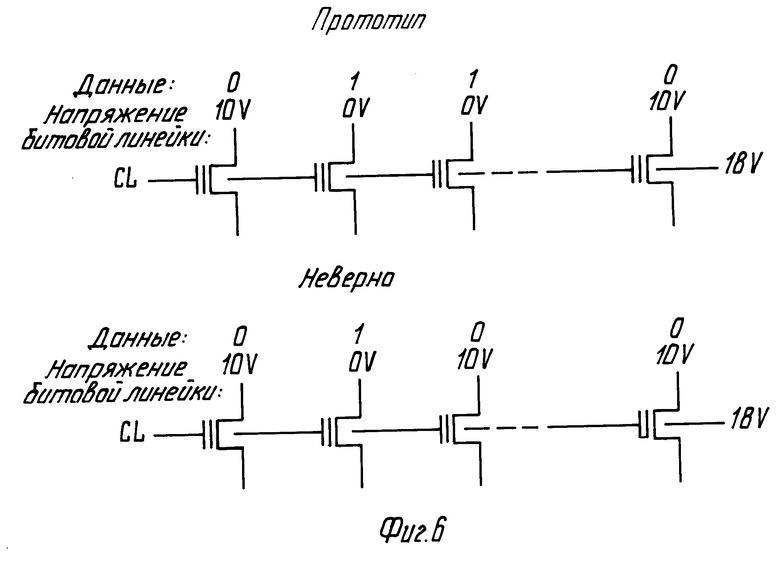

Таким образом, обычно состояния программируемых данных стираемого и электрически программируемого ПЗУ проверяются и внешним контроллером проверки выполняется повторное программирование данных, который выполняет алгоритм, показанный на фиг. 5, чтобы оптимизировать программирование данных. Алгоритм проверки программирования данных загружает данные в режиме страницы и защелкивает вводимые данные. Затем после программирования защелкнутых данных в каждую ячейку выбранной линейки ячеек данные считываются, чтобы проверить состояние программированных данных. Когда считываемые данные такие же, как и ожидаемое значение, программирование завершается. Когда же считываемые данные отличаются от ожидаемого значения, как показано на фиг. 6, биты данных, соответствующие ячейке, программирование на "1" у которой не удалось, удерживаются на "1", а биты данных, соответствующие ячейке, в которой "1" или "О" запрограммировались нормально, устанавливаются на нуль. Данные, обрабатываемые вышеописанным образом, повторно регулируются в режиме страницы и регулируемые данные повторно программируются в каждую ячейку выбранной линейки ячеек. После повторного программирования данные считываются, чтобы проверить запрограммированное состояние каждой ячейки, так что операция программирования заканчивается тогда, когда программирование оказывается в нормальном состоянии. Иными словами, когда программирование оказывается в ненормальном состоянии, циклический процесс считывания данных и программирования скорректированных данных повторяется, как описано выше (см. Журнал по твердотельным схемам института инженеров электриков, апрель 1991, с. 492 496).

Однако в соответствии с вышеописанным обычным алгоритмом проверки должен повторно выполняться процесс, в котором данные, программируемые внешним контроллером, считываются и проверяются, а затем загружаются снова для повторного программирования до тех пор, пока не будет детектировано нормальное запрограммированное состояние каждой ячейки, что ухудшает характеристику всей системы.

Целью изобретения является создание полупроводникового устройства неразрушаемой памяти, которое может автоматически оптимизировать программирование данных посредством одноразовой автоматической загрузки данных.

Другой целью изобретения является создание полупроводникового устройства неразрушаемой памяти, которое может предотвратить явление перепрограммирования данных.

Еще одной целью изобретения является создание оптимального способа программирования полупроводникового устройства неразрушаемой памяти, который может автоматически оптимизировать программирование данных внутри чипа.

Чтобы достичь этих и других целей изобретения, предусмотрено полупроводниковое устройство неразрушаемой памяти, содержащее

сеть ячеек памяти, устроенную в виде матрицы, имеющей ячейки И-НЕ, образованную множеством последовательно соединенных ячеек памяти, каждая из которых образована наложением слоя накопления зарядов и управляющего затвора на полупроводниковую подложку, и имеет возможность электрического стирания посредством взаимного обмена заряда между слоем накопления заряда и подложкой;

схему защелки данных для обеспечения данных программы для битовых линеек сети ячеек памяти;

схему высоковольтного источника питания для подачи предопределенного высокого напряжения к битовым линейкам сети ячеек памяти в соответствии с состоянием данных схемы защелки данных;

схему источника тока для подачи тока проверки к битовым линейкам сети ячеек памяти, для того чтобы подтвердить запрограммированное состояние данных после их программирования в сеть ячеек памяти;

устройство проверки программ для инвертирования состояния данных схемы защелки данных в ответ на то, протекает или нет через ячейку памяти ток проверки, поданный к битовым линейкам, когда этот ток проверки подается к управляющему затвору ячейки памяти, которая должна быть проверена;

схему детектирования состояния программы для генерирования сигнала детектирования состояния программы в ответ на операцию инвертирования состояния данных схемы защелки схемой проверки программы.

Кроме того, изобретение обеспечивает способ для оптимального программирования полупроводникового устройства неразрушаемой памяти, который предусматривает блочно-страничный режим, при котором множество цепочек ячеек структуры И-НЕ стирается блоками, а входные данные, защелкиваемые в буфер страниц, одновременно программируются в ячейки выбранного ряда ячеек, содержащий этапы

проверки программирования, которая подает управляющее напряжение проверки и ток проверки к каждой ячейке выбранной линейки ячеек, проверяет запрограммированное состояние данных в каждой ячейке и инвертирует только данные буфера страниц, соответствующие среди запрограммированных ячеек ячейке, имеющей нормально запрограммированные данные, в ответ на операцию проверки;

повторного программирования, которое повторно программирует данные буфера страниц, скорректированные указанным этапом проверки, в каждую ячейку выбранной линейки ячеек;

автоматического повторения этапов проверки и повторного программирования до тех пор, пока соответствующая инверсия данных буфера страниц не будет полностью выполнена путем нормального программирования данных в каждую из ячеек выбранной линейки ячеек, посредством чего программирование данных длиной в одну страницу может быть оптимизировано только при однократном вводе внешних данных и без перепрограммирования.

На фиг. 1 показана цепочка ячеек структуры И-НЕ обычного стираемого и электрически программируемого ПЗУ первого поколения и его эквивалентная схема, вид сверху; на фиг. 2 осциллограмма напряжений, подаваемых во время операций считывания, стирания и программирования цепочки ячеек структуры И-НЕ первого поколения; на фиг. 3 (а и б) схематические виды для иллюстрирования операций стирания и программирования стираемого и электрически программируемого ПЗУ второго поколения; на фиг. 4 (а и б) графики, изображающие характеристику распределения порогового напряжения запрограммированной ячейки по отношению к изменению напряжения программирования стираемого и электрически программируемого ПЗУ второго поколения с проверкой и без нее соответственно; на фиг. 5 блок-схема, показывающая алгоритм программы проверки стираемого и электрически программируемого ПЗУ второго поколения; на фиг. 6 запрограммированное состояние в соответствии с алгоритмом программы проверки по фиг. 5; на фиг. 7 принципиальная схема сети ячеек и схема детектирования в стираемом и электрически программируемом ПЗУ второго поколения в соответствии с изобретением.

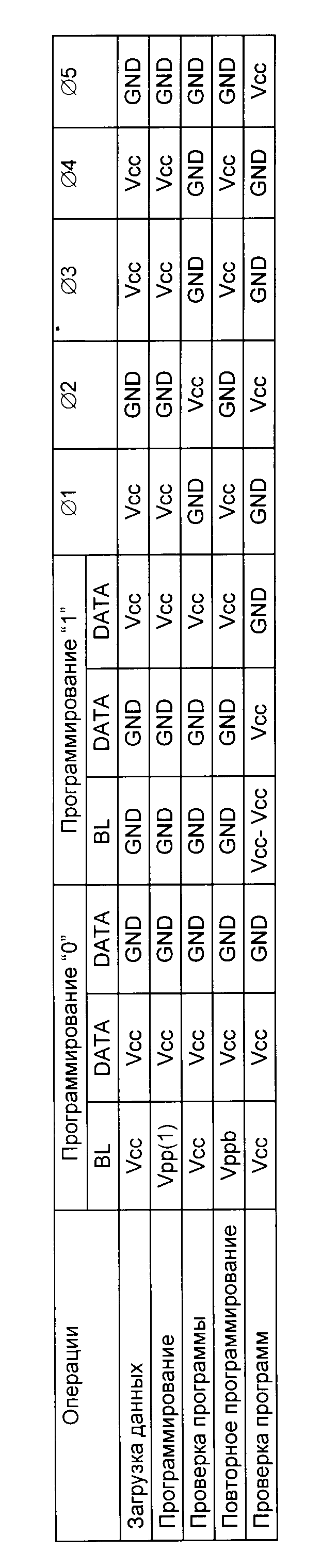

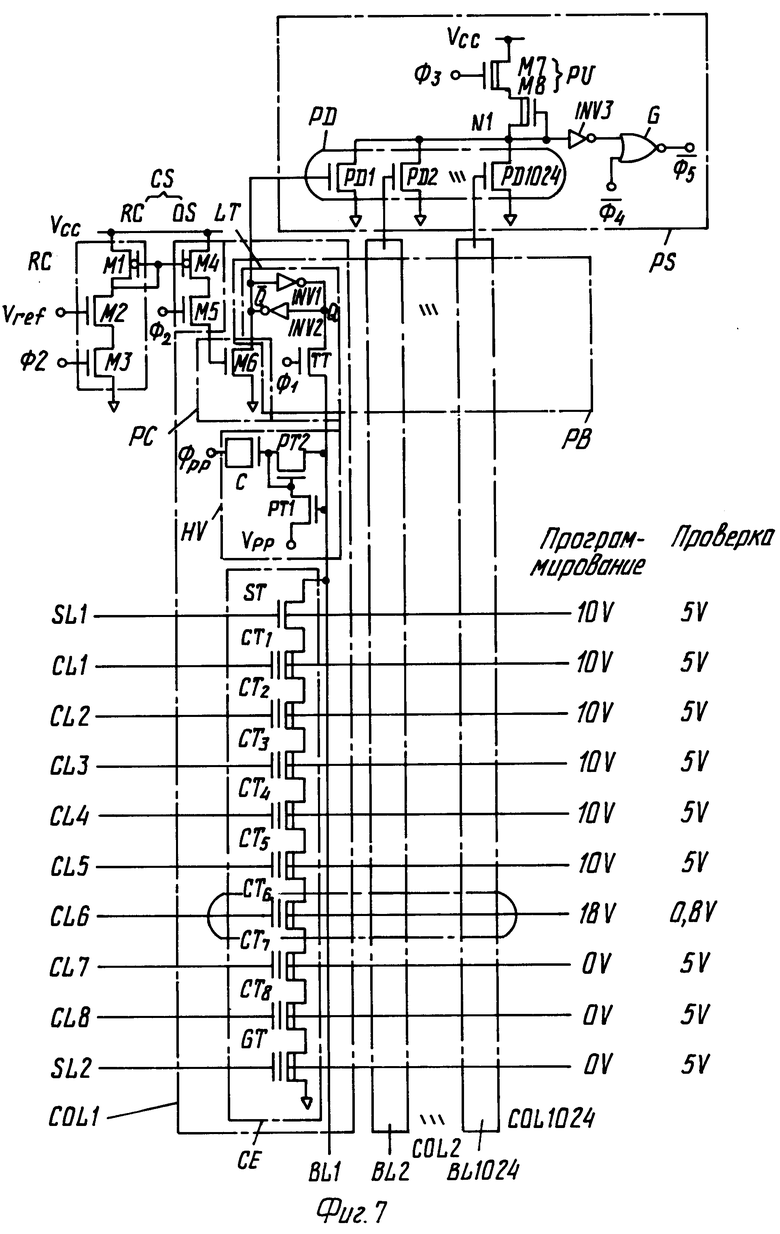

В таблице показано состояние напряжений каждой части фиг. 7 во время программирования данных и проверки запрограммированного состояния.

Обратимся к фиг. 7, которая иллюстрирует сеть ячеек стираемой и электрически программируемой памяти, имеющей ячейки структуры И-НЕ, а также схему детектирования запрограммированного состояния в соответствии с изобретением. Каждая битовая линейка BL1-BL1024 соединена с ячейкой структуры И-НЕ блока цепочки CE, состоящего из транзистора выбора цепочки ST, восьми транзисторов ячейки CT1-CT8 и транзистора выбора земли GT, которые соединены последовательно. Транзистор выбора цепочки ST и транзистор выбора земли GT имеют МОП-структуру и их затворы соответственно соединены с линиями выбора SL1 и SL2. Каждый транзистор ячейки CT1 CT8 имеет истощенную МОП-структуру с плавающим затвором управления и подложкой, а каждый затвор управления соответственно соединен с линиями управления CL1 CL8. Кроме того, каждая битовая линейка BL1 BL1024 соединена с соответствующей схемой высоковольтного источника питания HV для подачи на битовую линейку высоковольтного напряжения программирования во время программирования данных, соответствующей схемой защелки битовой линейки LT, в которую будут загружаться внешние входные данные, схемой источника тока CS для подачи тока проверки во время проверки программы и соответствующим блоком проверки программы PC для инвертирования данных схемы защелки битовой линейки LT в ответ на неудовлетворительное программирование во время проверки программы.

Схема высоковольтного источника питания HV представляет обычную схему высоковольтной накачки, которая составлена из транзисторов PT1 и PT2 и конденсатора накачки C. Сток транзистора PT1 соединен с источником напряжения программирования Vpp, его затвор соединен с битовой линейкой BL1, а его исток соединен с затвором транзистора PT2. Сток транзистора PT2 соединен с его затвором и одной клеммой конденсатора накачки C, его исток также соединен с битовой линейкой BL1. Когда тактовый сигнал ⊘pp, подаваемый на другую клемму конденсатора накачки C, становится высоким, конденсатор накачки C разряжает накопленные в нем заряды через транзистор PT2 на битовую линейку BL1, тем самым подавая напряжение стирания (10В) или напряжение запрещения программирования (10В) на битовую линейку BL1.

Схема защелки битовой линейки LT состоит из двух инверторов INV1 и INV2 и транзистора передачи TT1. Инверторы INV1 и INV2 соединены так, что вход одного инвертора подключен к выходу другого инвертора. Затвор транзистора передачи TT1 соединен с источником тактового сигнала ⊘1, его первая токовая клемма (сток или исток) соединена с битовой линейкой, а его вторая токовая клемма (исток или сток) соединена с входом инвертора INV2. Соответственно, схема защелки битовой линейки LT вводит и защелкивает внешние данные, подаваемые на битовую линейку через транзистор передачи TT1, который отпирается при высоком потенциале тактового сигнала ⊘1.

Схема источника тока CS образована из множества выходных схем OS, подключенных к соответствующим битовым линейкам, и общей схемы установки опорного тока RC, которые соединены друг с другом в виде хорошо известной зеркальной токовой схемы так, чтобы устанавливать опорный ток для всех выходных схем OS. Общий блок установки опорного тока RC составлен из p-канального МОП-транзистора M1 и n-канальных МОП-транзисторов M2 и M3, последовательно включенных между первым источником напряжения Vcc и вторым источником напряжения Vss (землей). Сток и затвор p-канального МОП-транзистора M1 соединены друг с другом. Затвор n-канального МОП-транзистора M2 соединен с источником опорного напряжения Vref, затвор n-канального МОП-транзистора М3 соединен с источником тактового сигнала ⊘2. Каждый выход OS составлен из p-канального МОП-транзистора M4 и n-канального МОП-транзистора M5, последовательно подключенных между первым напряжением питания Vcc и соответствующей битовой линейкой. Затвор p-канального МОП-транзистора M4 соединен с затвором p-канального МОП-транзистора M1, а затвор n-канального МОП-транзистора M5 также подключен к источнику тактового сигнала ⊘2. Следовательно, схема источника тока CS включается, когда тактовый сигнал ⊘2 становится высоким, так что ток стока p-канального МОП-транзистора M4 подается к битовой линейке BL1 в качестве тока проверки, который пропорционален току стока p-канального МОП-транзистора M1, умноженному на отношение токов МОП-транзисторов M1 и M4.

Блок проверки программы PC образован из МОП-транзистора M6, сток которого соединен с входом инвертора INV1 схемы защелки битовой линейки LT, его исток соединен с вторым источником напряжения (Vss или землей), а его затвор соединен с битовой линейкой. Таким образом, когда ток проверки, подаваемый к битовой линейке, не протекает к земле через ячейку структуры И-НЕ, потенциал битовой линейки становится высоким, что МОП-транзистор M6 (блок проверки программы) включается, что, в свою очередь, понижает вход инвертора INV1 схемы защелки LT до низкого потенциала (земли). Следовательно, когда программирование выбранной ячейки неудовлетворительно, блок проверки программы PC проверяет неудовлетворительное программирование, тем самым инвертируя данные схемы защелки битовой линейки LT.

1024 штук вышеописанных ячеек структуры И-НЕ СЕ образуют один блок, и каждый блок имеет 8 страниц информации, т.е. 8 Кбайт данных. Длина одной страницы составляет 1024 бит. Например, стираемая и электрически программируемая память на 4 Мбит включает 512 блоков. Такая стираемая и электрически программируемая память может программировать данные в блочно-страничном режиме. Здесь один блок схем защелок битовых линеек LT составляет буфер страниц PB.

На фиг. 7 символ PS обозначает схему детектирования состояния программирования. Схема детектирования состояния программирования PS выдает нормальный сигнал детектирования, когда все выбранные ячейки запрограммированы оптимально, или ненормальный сигнал детектирования, если неудовлетворительно запрограммирована даже одна какая-либо ячейка. Схема детектирования состояния программирования PS имеет p-канальный МОП-транзистор M7, служащий в качестве устройства прямого смещения PU для прямого смещения узла N 1, и истощенный МОП-транзистор M8, используемый в качестве нагрузки прямого смещения. Исток p-канального МОП-транзистора M7 соединен с источником первого напряжения Vcc, его затвор соединен с источником тактового сигнала ⊘3, а его сток соединен с истоком истощенного МОП-транзистора М8. Затвор и сток истощенного МОП-транзистора M8 соединены друг с другом и также соединены с узлом N 1. Между узлом N 1 и источником второго напряжения Vss (земля) параллельно включено множество n-канальных МОП-транзисторов PD1 PD1024, служащих в качестве устройства обратного смещения PD. Затвор каждого МОП-транзистора соединен с инвертированным выходом  соответствующей схемы защелки битовой линейки LT. Узел N 1 соединен через инвертор INV3 с одной клеммой схемы НЕ-ИЛИ G, которая представляет выходную схему. Другая клемма схемы НЕ-ИЛИ G соединена с источником тактового сигнала ⊘4.

соответствующей схемы защелки битовой линейки LT. Узел N 1 соединен через инвертор INV3 с одной клеммой схемы НЕ-ИЛИ G, которая представляет выходную схему. Другая клемма схемы НЕ-ИЛИ G соединена с источником тактового сигнала ⊘4.

Соответственно, когда в режиме проверки все транзисторы обратного смещения PD1 PD1024 заперты, схема детектирования состояния программирования генерирует тактовый сигнал ⊘5 высокого потенциала. Столбцы CJL2 COL1024 имеют ту же структуру, что и столбец COL1.

Операции программирования и проверки полупроводникового устройства неразрушаемой памяти по изобретению (фиг. 7) будут описаны со ссылкой на таблицу.

Для того чтобы запрограммировать данные внутри сети ячеек, сперва заполняется операция стирания по блокам. Здесь во время стирания, когда к управляющему затвору каждой ячейки прикладывается OB, а к подложке, истоку и стоку прикладывается напряжение стирания 20В, электроны эмиттируются из плавающего затвора ячейки в подложку, так что пороговое напряжение ячейки становится отрицательным. Когда стирание завершается, вводятся внешние данные, которые загружаются в схему защелки битовой линейки LT. В этот момент выполняется загрузка при высоком логическом уровне (уровень Vcc) для загрузки данных "0" (- Vth) и низком логическом уровне (уровне земли) для загрузки данных "1" (+ Vth). Данные загружаются в схему защелки битовой линейки LT, когда тактовый сигнал ⊘1 становится высоким. Если данные, загружаемые в схему защелки битовой линейки LT, представляют высокий логический уровень, то действует схема высоковольтного источника HV, тем самым устанавливая напряжение битовой линейки BL 10B, что представляет напряжение запрета программирования. Следовательно, как пояснено на фиг. 7, поскольку разность потенциалов между затвором и стоком транзистора выбранной ячейки CT6 недостаточна, чтобы возбудить F-N туннельный эффект, транзистор выбранной ячейки CT6 непрерывно сохраняет отрицательное пороговое напряжение (- Vth).

В то же время, если данные, загружаемые в схему защелки битовой линейки LT представляют низкий логический уровень, схема высоковольтного источника HV не действует, тем самым поддерживая напряжение битовой линейки на OB. Таким образом, поскольку F-N туннельный эффект не возбуждается разностью потенциалов между затвором и стоком транзистора выбранной ячейки CT6, электроны инжектируются в плавающий затвор, так что пороговое напряжение ячейки становится положительным (+ Vth). Однако, если бит данных "1" запрограммирован неудовлетворительно, выбранная ячейка CT6 не может получить предопределенное положительное пороговое напряжение. Такая операция программирования одновременно выполняется по страницам в режиме страниц. Соответственно, чтобы запрограммировать один блок (1024 х 8), выполняется восемь операций программирования. Чтобы проверить программирование по окончании операции программирования, в ответ на высокие состояния тактового сигнала ⊘2 действует схема источника тока CS, так что к битовой линейке BL прикладывается ток проверки. В этот момент к линиям управления CL1 CL5, CL7 и CL8 линии выбора SL1 и SL2 и транзисторам не выбранных ячеек CT1 CT5, CT7 и CT8 подается напряжение Vcc, а к линии управления CL6 выбранного ряда ячеек подается предопределенное напряжение проверки, например, 0,8 В. Следовательно, когда пороговое напряжение транзистора выбранной ячейки CT6 отрицательно (данные 0), ток проверки через цепочку ячеек шунтируется на землю. Таким образом, битовая линейка BL1 сохраняет свой уровень OB.

Когда же пороговое напряжение выбранной ячейки положительно (т.е. + Vth > 0, данные 1), битовая линейка BL1 принимает высокий уровень, так как ток проверки не протекает через цепочку ячеек CE. Однако, если ячейка, запрограммированная данными "1", запрограммирована неудовлетворительно, а это означает, что пороговое напряжение ячейки меньше 0,8В, ток проверки шунтируется на землю, позволяя битовой линейке BL1 все еще сохранять свой уровень OB.

Во время такой операции проверки, когда битовая линейка выбранной ячейки, в которой запрограммированы данные "1", сохраняет низкий потенциал, транзистор M6, который является устройством проверки программирования, не может быть отперт, так что данные в схеме защелки битовой линейки LT не инвертируются. Следовательно, данные "0" в первоначальном состоянии загрузки продолжают оставаться на выходе Q. Кроме того, поскольку на инвертированном выходе  схемы защелки битовой линейки LT сохраняются данные "1", транзистор обратного смещения PD1 схемы детектирования состояния программирования PD, затвор которого соединен с выходом

схемы защелки битовой линейки LT сохраняются данные "1", транзистор обратного смещения PD1 схемы детектирования состояния программирования PD, затвор которого соединен с выходом  , непрерывно поддерживается в открытом состоянии. Поэтому нормальное программирование не выполняется, так что тактовый сигнал ⊘5 схемы детектирования состояния программирования PS поддерживается на низком уровне.

, непрерывно поддерживается в открытом состоянии. Поэтому нормальное программирование не выполняется, так что тактовый сигнал ⊘5 схемы детектирования состояния программирования PS поддерживается на низком уровне.

Во время повторного программирования, поскольку данные "0" схемы защелки битовой линейки LT снова подаются к битовой линейке BL1 при высоком уровне тактового сигнала ⊘1, электроны повторно инжектируются в плавающий затвор выбранной ячейки, которая запрограммирована неудовлетворительно. Таким образом, пороговое напряжение ячейки становится более положительным. Если выбранная ячейка не отпирается напряжением проверки (+0,8 В) во время подъема ее порогового напряжения, чтобы стать положительной, за счет последовательного повторения операций программирования, проверки и повторного программирования, то потенциал битовой линейки становится логическим высоким уровнем, тем самым отпирая транзистор M6. Таким образом, данные "0", загружаемые на выходе Q схемы защелки битовой линейки LT, инвертируются в данные "1", а данные "1" инвертированного выхода инвертируются в данные "0", так что транзистор обратного смещения PD1 схемы детектирования состояния программирования PD запирается. За счет этого повторного действия, когда все биты данных буфера страниц PB, т.е. инвертированные выходные сигналы  всех схем защелок битовых линеек, являются данными "0", иными словами, когда все первоначальные входные данные "1" инвертируются в данные "0", тактовый сигнал ⊘5 схемы детектирования состояния программирования PS становится высоким (уровня Vcc). То есть ячейки, выбранные входными данными, запрограммированы.

всех схем защелок битовых линеек, являются данными "0", иными словами, когда все первоначальные входные данные "1" инвертируются в данные "0", тактовый сигнал ⊘5 схемы детектирования состояния программирования PS становится высоким (уровня Vcc). То есть ячейки, выбранные входными данными, запрограммированы.

Как раскрыто выше, операции программирования и проверки повторяются автоматически данными из буфера страниц только при одноразовой операции ввода данных и без внешнего управления до тех пор, пока все ячейки, выбранные буфером страниц, т.е. схемами защелок битовых линеек и схемой источника тока, оптимально не запрограммированы.

В соответствии с изобретением программированное состояние может быть оптимизировано, не подвергаясь влиянию изменения параметров процесса, перепрограммирование предотвращается путем использования потенциала проверки, и оптимальное программирование автоматически выполняется внутренней функцией проверки чипа. В результате характеристика чипа может быть улучшена, и, в свою очередь, поскольку внешнее управление не требуется, улучшается характеристика всей системы, использующей такой чип. Кроме того, изобретение, используя буфер страниц обычной стираемой и электрически программируемой памяти, имеющей функцию страничного режима, применимо для существующих изделий.

Полупроводниковое устройство неразрушаемой памяти относится, в частности, к стираемому и электрически программируемому ПЗУ. Устройство включает сеть ячеек памяти, устроенную в виде матрицы, имеющей ячейки И-НЕ, образованную множеством последовательно соединенных ячеек памяти, каждая из которых выполнена путем наложения слоя накопления зарядов и управляющего затвора на полупроводниковую подложку и имеет возможность электрического стирания посредством взаимного обмена заряда между слоем накопления зарядов и подложкой, схему защелки данных LT, источник высоковольтного напряжения HV, схему источника тока CS, схему проверки программирования PC и схему детектирования состояния программирования PS. Кроме того, используется буфер страниц PB стираемой и электрически программируемой памяти, имеющей функцию страничного режима. 2 з.п. ф-лы, 7 ил.

| Журнал по твердотельным схемам института инженеров электриков, апрель, 1991, v | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1997-11-27—Публикация

1992-04-29—Подача