Предпосылки создания настоящего изобретения

Область техники, к которой относится настоящее изобретение

Настоящее изобретение относится к устройству и способу тестирования трактов передачи дискретных данных на печатной плате при использовании JTAG.

Описание родственной области техники

Хорошо известный способ тестирования схемотехники, например, на печатной плате, описан в стандарте сканирования поверхности раздела 1149.1 IEEE. разработанном JTAG (Международной рабочей группой по испытаниям соединений), включенном в эту заявку ссылкой. Осуществление этого стандарта предусматривает конструирование компонентов (например, интегральных схем для последовательного тестирования сканированием поверхности раздела посредством обеспечения элементов сдвигового регистра в виде цепи для образования тракта по периферии компонента интегральной схемы.

Общая концепция тестирования сканированием поверхности раздела, при использовании JTAG, заключается в смещении последовательных данных через ряд компонентов интегральной схемы для возбуждения схемотехники на печатной плате и для стробирования входных сигналов интегральной схемы из схемотехники печатной платы. Поскольку известны топология межсоединения и логические функции печатной платы (то есть между выходным сигналом JTAG и входом JTAG на печатной плате), задающая тестовая схема может сравнивать данные возврата с ожидаемым результатом (то есть с результатом, который является зависимым от функций известной схемотехники и межсоединения печатной платы). Другими словами, последовательные вводы данных в тестируемую схему генерируют известные выходные сигналы, если межсоединение печатной платы выполнено правильно и схемотехника между источником JTAG и точками стробирования функционирует должным образом. Последовательное тестирование является также тестированием входных и выходных штырьковых выводов и буферных каскадов интегральной схемы, которая содержит JTAG, поскольку они расположены между точками выхода JTAG и точками стробирования входа JTAG.

Если поток данных, возвращаемый в задающую схему тестирования, является не таким, которого ожидают, то соединительный тракт на печатной плате разомкнут или замкнут для другого сигнала, или существует нарушение нормальной работы какой-либо логической схемы вдоль анализируемого тракта от выхода JTAG к входу JTAG. Тщательный компьютерный анализ отклонений в потоке данных может локализовать любое нарушение нормальной работы в печатной плате.

В некоторых случаях желательно тестировать ветвь или часть тракта передачи дискретных данных на печатной плате. Например, при тестировании электрической схемы системы, очень часто представляет важность тестирование замкнутых цепей или разомкнутых цепей на печатной плате. Это важно, поскольку при высокой плотности монтажа штырьковых выводов между смежными штырьковыми выводами могут иметься припойные перемычки. В другом варианте, отсутствующее или неправильно образованное паяное соединение может привести к образованию разомкнутой цепи.

Однако иногда часть тракта передачи дискретных данных, которая должна быть протестирована, заканчивается, например, в гнезде запоминающего устройства, так что отсутствует замкнутая цепь, образуемая трактом. Таким образом, на некоторых частях подлежащего тестированию тракта отсутствует схемотехника JTAG, так что не представляется возможность тестирования JTAG тракта передачи дискретных данных. Например, такая проблема может существовать в тех случаях, где плата памяти не установлена в гнездо запоминающего устройства или где плата памяти, установленная в гнезде, не способна тестироваться JTAG. Например, стандартные модуль памяти с однорядным расположением штырьковых выводов или модуль памяти с двухрядным расположением штырьковых выводов не предусматривают возможности тестирования JTAG.

Одним решением этой проблемы является использование тестеров с матрицей подпружиненных игольчатых контактов, который разрабатывают и изготавливают по особому заказу для тестирования частей тракта (передачи дискретных данных) на печатной плате, которые заканчиваются в незанятых гнездах. Однако такие тестеры с матицей подпружиненных игольчатых контактов могут стоить тысячи долларов, так что во многих случаях применения такой тестер может быть дорогим. Кроме того, испытательная арматура, которая обеспечивает соответствие тестера с матрицей подпружиненных игольчатых контактов и конфигурации специальной печатной платы, требует времени для изготовления и может оказаться недоступной для применения на этапе изготовления прототипа конструкции печатной платы. По этой причине продолжает существовать потребность в недорогом устройстве и способе для тестирования трактов (передачи дискретных данных) в компьютерной или аналогичной системе.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

Система для тестирования соединений от точки к точке на печатной плате при использовании JTAG содержит печатную плату, включающую в себя схемотехнику, которая должна быть протестирована при использовании JTAG. Тракт передачи дискретных данных на печатной плате содержит штырьковые выводы соединения, в то время как множество сменных периферийных или расширительных гнезд (слотов) электрически соединено штырьковыми выводами тракта передачи дискретных данных. Сменная тестовая плата JTAG дополнительно входит в контакт с одним из сменных гнезд для образования с ним электрического соединения. Тестовая плата содержит тестовую схемотехнику JTAG для возбуждения тестовых сигналов на штырьковых выводах тракта (передачи дискретных данных) через сменное гнездо, введенное в контакт с тестовой платой. Наконец, система содержит тестовую схему JTAG, имеющую связь с трактом (передачи дискретных данных) на печатной плате. Выходные тестовые сигналы, формируемые тестовой платой, принимаются тестовой схемой JTAG для тестирования целостности соединений от точки к точке на печатной плате. В предпочтительном варианте осуществления тестовая схема JTAG содержит вторую тестовую плату JTAG, введенную в контакт со вторым сменным гнездом. В другом предпочтительном варианте осуществления тестовая схема JTAG содержит кристалл интегральной схемы, имеющий способность тестирования JTAG на печатной плате.

В другом аспекте настоящее изобретение обеспечивает способ тестирования соединений тракта (передачи дискретных данных) на объединительной плате, которые сопряжены со сменным гнездом. Способ предусматривает обеспечение сменной тестовой платы, имеющей тестовые компоненты JTAG, содержащие регистр сканирования поверхности раздела. Тестовая плата предназначена для установки в сменное гнездо. Этот способ дополнительно предусматривает установку тестовой платы в сменное гнездо; смещение тестового вектора, содержащего биты данных, в регистр сканирования поверхности раздела; вывод битов данных тестового вектора из регистра сканирования поверхности раздела к соединениям тракта передачи дискретных данных через сменное гнездо; прием выходных битов данных тестового вектора через соединения тракта передачи дискретных данных; сбор битов данных тестового вектора через регистр JTAG сканирования поверхности раздела; смещение тестовых данных из регистра сканирования поверхности раздела в тестер JTAG; и сравнение принятых выходных битов данных тестового вектора с предварительно заданной конфигурацией выхода для идентификации нарушения нормальной работы в соединениях тракта передачи дискретных данных. В предпочтительном варианте осуществления способа операции обеспечения, установки, смещения, вывода, приема и сравнения повторяют для каждого набора соединений тракта передачи дискретных данных на объединительной плате.

В еще одном аспекте настоящее изобретение обеспечивает систему, которая тестирует соединения тракта (передачи дискретных данных), которые сопряжены со сменными гнездами на объединительной плате. Система содержит объединительную плату; тракт передачи дискретных данных, имеющий соединения, которые сопряжены со сменными гнездами на объединительной плате; и сменную тестовую плату. Сменная тестовая плата дополнительно содержит регистр сканирования поверхности раздела и часть соединителя, имеющую связь с регистром сканирования поверхности раздела. Часть соединителя предназначена для вхождения в контакт со сменным гнездом для установления связи между соединениями тракта передачи дискретных данных и регистром сканирования поверхности раздела. Сменная тестовая плата содержит также управляющую схемотехнику сканирования поверхности раздела, содержащую контроллер подключения (ТАР-контроллер) и регистр команд.

В дополнительном аспекте настоящее изобретение обеспечивает систему для тестирования множества соединений тракта (передачи дискретных данных), которые сопряжены по меньшей мере с одним сменным гнездом на объединительной плате. Множество соединений тракта передачи дискретных данных не имеет электрической связи с тестовой схемотехникой JTAG на объединительной плате. Система содержит объединительную плату, тракт передачи дискретных данных, имеющий соединения, которые сопряжены по меньшей мере с одним сменным гнездом на объединительной плате, и по меньшей мере одну сменную тестовую плату, которая входит в контакт по меньшей мере с одним сменным гнездом для установления электрической связи между тестовой схемотехникой JTAG на сменной тестовой плате и соединениями тракта передачи дискретных данных. В предпочтительном варианте осуществления схемотехника JTAG на сменной тестовой плате содержит регистр сканирования поверхности раздела, контроллер программы анализа транзисторных схем и регистр команд.

В другом аспекте настоящее изобретение обеспечивает сменную тестовую плату JTAG, предназначенную для применения при тестировании соединений тракта (передачи дискретных данных) на объединительной плате, которые сопряжены со сменными периферийными или расширительными гнездами. Сменная тестовая плата содержит часть соединителя, которая входит в контакт со сменными периферийными или расширительными гнездами, регистр сканирования поверхности раздела и входной тракт передачи дискретных данных, который обеспечивает входной канал, посредством которого сигналы из соединителя обеспечиваются как входы в регистр сканирования поверхности раздела. Сменная плата дополнительно содержит выходной тракт передачи дискретных данных, посредством которого выходные сигналы из соединителя поступают в соединитель и управляющую схемотехнику сканирования поверхности раздела. Управляющая схемотехника сканирования поверхности раздела содержит контроллер программы анализа транзисторных схем и регистр команд.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - упрощенная принципиальная блок-схема компьютерной системы, содержащей тракт передачи дискретных данных, соединяющий сменную плату памяти и гнезда входа/выхода.

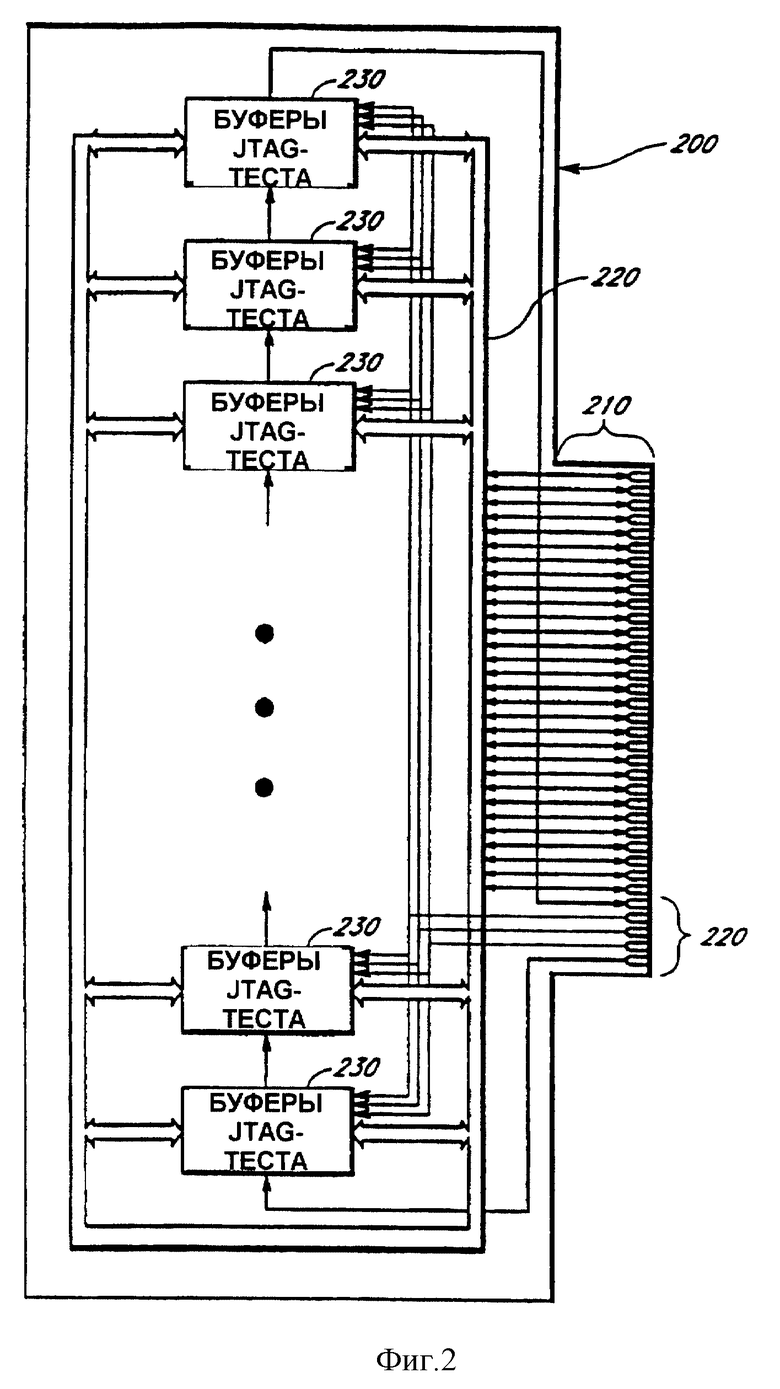

Фиг. 2 - принципиальная схема, на которой показана одна сторона сменной платы модуля памяти с двухрядным расположением штырьковых выводов, выполненная в соответствии с настоящим изобретением для включения только буферной схемотехники JTAG.

Фиг. 3 - принципиальная блок-схема, на которой показан один из тестовых буферных каскадов сканирования поверхности раздела, реализованный на сменной плате модуля памяти с двухрядным расположением штырьковых выводов, показанной на фиг.2.

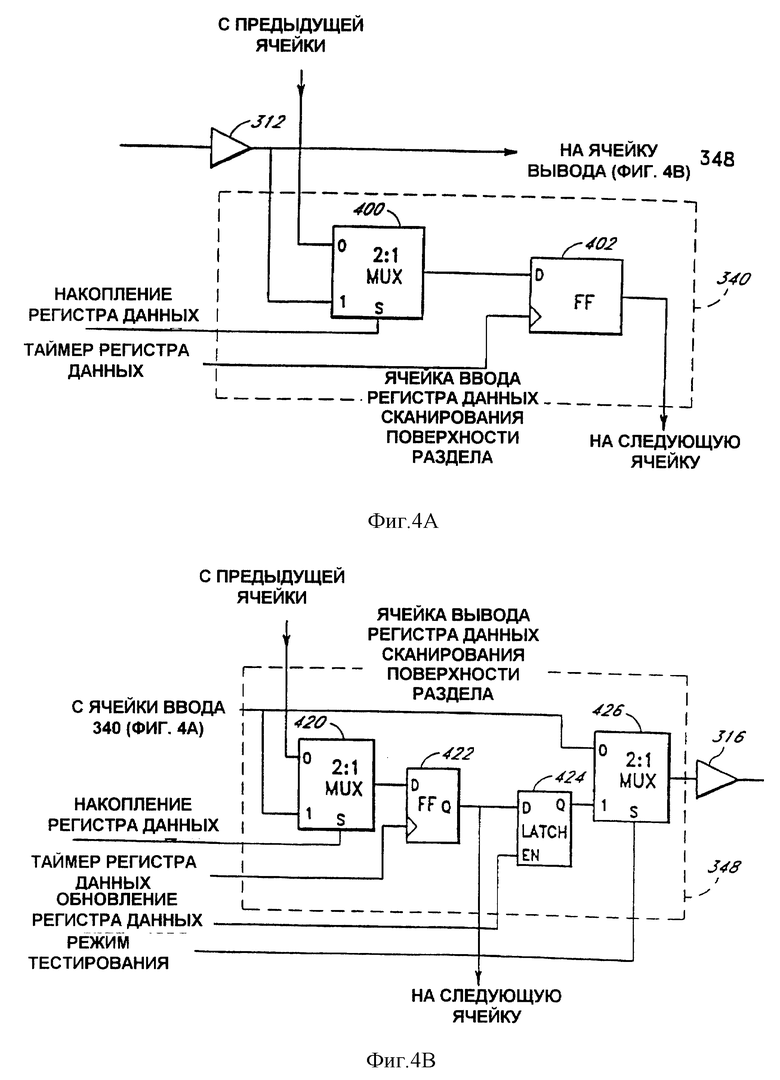

Фиг. 4А и 4В - более подробная иллюстрация внутренних элементов регистра сканирования поверхности раздела, показанного на фиг.3.

Фиг. 5 - схематическая иллюстрация варианта воплощения сменной платы, в которой соединения JTAG образованы на тыльной стороне платы напротив соединений тракта передачи дискретных данных.

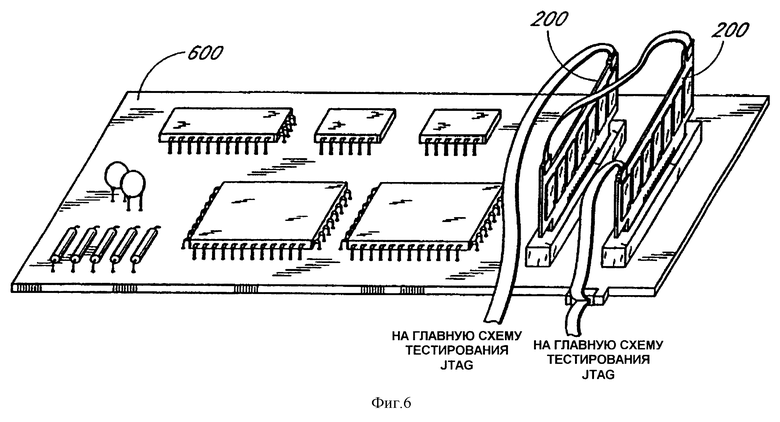

Фиг.6 - иллюстрация системы с несколькими сменными платами, соединенными в процессе тестирования объединительной платы.

Фиг.7 - иллюстрация тестовой системы в соответствии с настоящим изобретением.

ПОДРОБНОЕ ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНОГО ВАРИАНТА ОСУЩЕСТВЛЕНИЯ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

На фиг. 1 показана упрощенная принципиальная блок-схема, иллюстрирующая компьютерную систему 100. Компьютерная система 100 содержит микропроцессор 110, который устанавливает связь с устройством сопряжения 120 тракта передачи дискретных данных и с контроллером 140 динамического запоминающего устройства с произвольной выборкой через тракт 130 передачи дискретных данных системы. В одном предпочтительном варианте осуществления, микропроцессор 110 содержит микропроцессор Р6, а устройство сопряжения 120 тракта передачи дискретных данных содержит устройство сопряжения микропроцессора Р6 с PCI (периферийным межсоединением компонента). Устройство сопряжения 120 микропроцессора Р6 с PCI устанавливает связь с дисководом 150 и сменным гнездом 160 входа/выхода через тракт 170 передачи дискретных данных PCI. Контроллер 140 динамического запоминающего устройства с произвольной выборкой соединен с первым сменным гнездом 180 модуля памяти с двухрядным расположением штырьковых выводов и вторым сменным гнездом 190 модуля памяти с двухрядным расположением штырьковых выводов через тракт 195 передачи дискретных данных памяти. При работе компьютерной системы 100, модули памяти с двухрядным расположением штырьковых выводов (эти модули на фиг.1 не показаны), имеющие, установленные на них, динамические запоминающие устройства с произвольной выборкой, вставлены в гнезда 180, 190, Хотя в варианте осуществления, показанном на фиг.1, использованы сменные платы модуля памяти с двухрядным расположением штырьковых выводов, в соответствии с настоящим изобретением могут быть также использованы модули памяти с однорядным расположением штырьковых выводов.

Желательно, чтобы на стадии производства была возможность протестировать каждый из компонентов интегральной схемы, а также каждое соединение от точки к точке кристаллов интегральных схем и вдоль всех трактов передачи дискретных данных при использовании тестирования JTAG сканирование поверхности раздела. Однако в некоторых случаях может оказаться трудным протестировать многие из соединений от точки к точке вдоль некоторых каналов связи, поскольку одно сменное гнездо или более сменных гнезд оказываются незанятыми или не содержат модуля с совместимостью JTAG.

В характерном случае, как показано на фиг.1, сменное гнездо 160 входа/выхода в сменные гнезда 180 и 190 модулей памяти с двухрядным расположением штырьковых выводов могут быть незанятыми, так что тракт 170 передачи дискретных данных PCI и тракт 195 передачи дискретных данных памяти закончатся у незамкнутого соединения. Следовательно, нет замкнутой цепи для тестирования шин тракта 170 передачи дискретных данных PCI или тракта 195 передачи дискретных данных памяти при использовании JTAG. Кроме того, в альтернативном варианте осуществления сменные гнезда 160, 180 и 190 могут содержать модули, которые несовместимы с JTAG, так что гнезда 160, 180 и 190, а также части трактов 170, 195 передачи дискретных данных не будут тестируемыми при использовании JTAG.

Таким образом, для обеспечения недорогих и эффективных системы и способа тестирования каждого из соединений на тракте 170 передачи дискретных данных PCI и тестирования гнезд 180, 190 модуля памяти с двухрядным расположением штырьковых выводов, специально разработанный сменный модуль 200 (смотри фиг. 2) вставляют в каждое из гнезд, которые для тестирования требуют совместимости с JTAG.

Как показано на фиг.2, сменная тестовая плата 200 JTAG содержит сменный соединитель 210, который обеспечивает, например, многоштырьковое соединение с трактом 195 передачи дискретных данных памяти (или в альтернативном варианте с трактом 170 передачи дискретных данных PCI. Соответствующая тестовая плата JTAG для каждого из гнезд 160, 180, 190 имеет соответствующий соединитель для каждого из гнезд 160, 180, 190. Сменная тестовая плата 200 JTAG дополнительно содержит тестовый интерфейс 220 JTAG для большого числа тестовых буферных каскадов 230 JTAG. Как показано на фиг.2, тестовые буферные каскады 230 JTAG используют для соединения с каждым сигнальным штырьком предназначенного для тестирования тракта передачи дискретных данных (например, тракта 195 передачи дискретных данных памяти или тракта 170 передачи дискретных данных PCI). В одном предпочтительном варианте осуществления тестовые буферные каскады 230 JTAG содержат логическую схему JTAG сканирования поверхности раздела, образованную в октальных приемопередатчиках тракта (передачи дискретных данных), выпускаемых на промышленной основе компанией Texas Instrument и продаваемых под индексом SN74ABT8245. Этот октальный приемопередатчик тракта передачи дискретных данных содержит две группы из восьми двунаправленных тестовых буферных каскадов JTAG, причем каждая группа совместно использует выходной разрешающий сигнал.

Необходимо отметить, что сменная плата 200 не содержит запоминающего устройства, хотя запоминающее устройство или другая схемотехника может быть выполнена на плате 200 в соответствии с требованиями в конкретных случаях применения. Сменную плату 200 предпочтительнее используют только для завершения тестовой схемы JTAG, так что плата 200 предназначена только для применения в тестовой схеме JTAG. Таким образом, путем вставления сменной платы 200 в одно или более вставных гнезд 160, 180 и 190, могут быть недорого протестированы тракты 175, 190 передачи дискретных данных. Кроме того, настоящее изобретение стоит значительно меньше тестеров (с матрицей подпружиненных игольчатых контактов), которые должны быть разработаны и изготовлены по специальному заказу за тысячи долларов.

В процессе тестирования одна или более сменных плат 200 могут быть вставлены в соответствующие сменные гнезда снова и снова и использованы в качестве тестовой схемы для трактов передачи дискретных данных на многокомпьютерных системах, подлежащих тестированию.

Если вставные платы 200 используют для тестирования соединений тракта передачи дискретных данных для трактов уже оборудованных для тестирования JTAG (например, тракт 170 передачи дискретных данных PCI, показанный на фиг. 1), уже предусмотрены соответствующие шины для смещения данных и команд JTAG в байпасный регистр, регистр контроля поверхности раздела и регистр команд (смотри фиг. 3 и 4) в тестовых схемах JTAG. Однако, если сменная тестовая плата 200 JTAG соединена для тестирования с трактом передачи дискретных данных, который нормально не оборудован для JTAG (например, тракт ISA передачи дискретных данных, обычный тракт передачи дискретных данных памяти или тракт передачи дискретных данных PCI без соответствующего интерфейса JTAG), то специальные шины JTAG должны быть соединены с платами 200 специальными соединителями, как показано на фиг.5 и 6, так, чтобы данные и команды могли быть смещены в сдвиговые регистры данных и команд JTAG.

На фиг.5 схематически иллюстрируется вариант осуществления сменной платы 200, в которой соединения JTAG образованы на краю платы напротив соединений тракта передачи дискретных данных. Четыре шины JTAG, включающие в себя шину 240 выбора режима тестирования (TMS), шину 242 передачи синхронизирующего сигнала тестирования (ТСК), шину 244 ввода данных тестирования (TDI) и необязательная шина 246 возврата в исходное состояние (TRST*), соединены с тестовыми буферными каскадами 230 JTAG. Шины 240, 242, 246 TMS, TCK, TRST* соединены параллельно каждому из буферных каскадов 230, в то время как шина 244 TDI соединена последовательно через тестовые буферные каскады 230, как хорошо известно из предшествующего уровня техники. Пятая шина 248 выхода данных тестирования (ТDО) JTAG возвращает выходные данные из последнего буферного каскада 230. Входные шины 240, 242, 244, 246 соединены с платой 200, показанной на фиг. 5, через входной соединитель 250 JTAG. Входные шины 240, 242, 246 TMS, TCK, TRST*, соответственно, также соединены с выходным соединителем 252 JTAG, причем с выходным соединителем 252 также соединена шина 248 TDO. Параллельный тракт 254 передачи дискретных данных обеспечивает межсоединения между соединителем 256 тракта передачи дискретных данных и штырьковыми выводами вход/выход тестовых буферных каскадов 230 JTAG.

На фиг. 6 иллюстрируется несколько сменных плат, соединенных в процессе тестирования объединительной платы 600. Как показано на фиг.6, тестовые шины JTAG соединяются на тыльной стороне плат 200, а не через соединение тракта передачи дискретных данных, поскольку в приведенном случае применения либо тракт передачи дискретных данных не содержит тестовых шин JTAG, либо тракт передачи дискретных данных содержит тестовые шины JTAG, которые последовательно не соединены с системой сканирования объединительной платы.

На фиг. 3 приведена функциональная блок-схема интегральной схемы SN74ABT8245. На фиг.3 показана внутренняя схемотехника интегральной схемы, выпускаемой на промышленной основе, которая может быть использована для обеспечения тестовых буферных каскадов 230 для обеспечения сканирования, иллюстрируемых на фиг.2. Как показано на фиг.3, буферные каскады 230 включают в себя регистр 300 сканирования поверхности раздела и восемь двунаправленных буферных каналов 310 (на фиг.3 показан только один буферный канал 310). Каждый двунаправленный буферный канал 310 ((прим.пер.) в оригинале текста описания на английском языке, вероятно, ошибочно написано "канальный буфер 310") обеспечивает межсоединение между одним отрезком А-тракта передачи дискретных данных (показанным на фиг.3, слева) и соответствующим отрезком В-тракта передачи дискретных данных (показанным на фиг.3, справа). На фиг.3 показан только двунаправленный буферный канал 310, предназначенный для образования межсоединения между первым отрезком (А1) А-тракта передачи дискретных данных и первым отрезком (В1) В-тракта передачи дискретных данных. Другие семь буферных каналов (не показаны) образуют межсоединения отрезков А2 и В2, отрезков A3 в В3, отрезков А4 и В4, отрезков А5 и В5, отрезков А6 и В6, отрезков А7 и В7, отрезков А8 и В8. Каждый буферный канал 310 содержит соответствующие входные буферы 312, 318 и соответствующие выходные буферы 314, 316. Выходные буферы 314, 316 являются буферами, имеющими три состояния, причем состояние высокого импеданса управляется выходным разрешающим сигналом А (ОЕА) и выходными разрешающими сигналами В (ОЕВ) логического элемента И 320 и логического элемента И 322, соответственно, в нормальном режиме, и контролируются выходными ячейками (OUT CELL) 324, 326 сканирования поверхности раздела JTAG, соответственно, в режиме тестирования JTAG.

Логический элемент И 320 принимает первый инвертирующий вход из шины 328 активного низкого выходного разрешающего сигнала через буфер 330. Входная ячейка (IN CELL) 332 сканирования поверхности раздела JTAG в регистре 300 сканирования поверхности раздела соединена с выходом буфера 330 для текущего контроля состояния шины 328 выходного разрешающего сигнала. Второй не инвертирующий вход к логическому элементу И 320 обеспечивается шиной 334 направления (DIR) через буфер 336. Входная ячейка 338 сканирования поверхности раздела JTAG в регистре 300 сканирования поверхности раздела соединена с выходом буфера 336 для разрешения текущего контроля состояния шины 334 направления. Логический элемент И 322 принимает инвертированный вход из шины 328 выходного разрешающего сигнала и принимает инвертированный вход из шины 334 направления через буферы 330, 336, соответственно. Таким образом, можно видеть, что для первоначально предназначенного применения буферного каскада 230 только один из сигналов ОЕА и ОЕВ из логических элементов И 320, 322 может быть одновременно возбужден в соответствии с состоянием сигнала DIR на шине 334. В предпочтительном варианте осуществления шины 328, 334 выходного разрешающего сигнала и направления, соответственно, связаны так, что, если тестовые буферные каскады 230 сканирования не находятся в режиме тестирования JTAG, шестнадцать штырьковых выводов вход/выход октального буферного каскада находятся в состоянии высокого импеданса и не оказывают воздействия на, подвергаемый тестированию, каскад передачи дискретных данных. В описываемом в этой заявке режиме тестирования JTAG, шина 328 выходного разрешающего сигнала, шина 334 направления и логические элементы И 320, 322 не используются, а буферы контролируются только выходными ячейками 324, 326 JTAG.

Каждый из восьми каналов дополнительно контролируются входной ячейкой 340 JTAG стороны А-тракта передачи дискретных данных, выходной ячейкой 342 JTAG стороны А-тракта передачи дискретных данных, входной ячейкой 346 JTAG стороны В-тракта передачи дискретных данных и выходной ячейкой 348 стороны В-тракта передачи дискретных данных в регистре 300 сканирования поверхности раздела, как более подробно описано ниже со ссылкой на фиг.4А и 4В.

Регистр 300 сканирования поверхности раздела принимает биты данных и команды, которые могут быть смещены в регистр 300 сканирования поверхности раздела под контролем стандартной тестовой схемотехники JTAG. Конкретно, тестовая схемотехника JTAG, которая управляет регистром 300 сканирования поверхности раздела содержит байпасный (параллельный) регистр 350, регистр 355 контроля поверхности раздела, регистр 360 команд и контроллер 365 программы анализа транзисторных схем. Регистры 350-360 принимают сигнал входа данных тестирования (TDI) на шине 370 через буфер 371. Контроллер 365 программы анализа транзисторных схем принимает сигнал выбора режима тестирования (TMS) на шине 372 через буфер 373 и принимает синхронизирующий сигнал тестирования (ТСК) на шине 374 через буфер 375. Контроллер 365 программы анализа транзисторных схем обеспечивает управление выходными сигналами в регистр 360 команд, регистр 355 контроля поверхности раздела и в байпасный (параллельный) регистр 350.

Выход регистра 300 сканирования поверхности раздела предусмотрен как первый вход в мультиплексор 380, имеющий три входа, в то время как выходы байпасного регистра 350 и регистра 355 контроля поверхности раздела служат вторым и третьим входами, соответственно, в мультиплексор 380. Выход мультиплексора 380 служит первым входом в мультиплексор 385, имеющий два входа и один выход, в то время как выход регистра 360 команд служит вторым входом в мультиплексор 385. Контроллер программы анализа транзисторных схем обеспечивает вход выбора (режима тестирования) в мультиплексор 385, а также обеспечивает вход в буфер 390 выхода данных тестирования, который соединен с выходом мультиплексора 385. Выход выходного буфера 390 представляет собой сигнал TDO на шине 392.

Способ осуществления тестирования JTAG при использовании схемы, иллюстрируемой на фиг.3, хорошо известен квалифицированным в этой области техники специалистам. Например, описание этого способа, используемого для смещения соответствующих тестовых векторов и так далее, смотри в указанной выше ссылке на стандарт JTAG IEEE 1149.1 JTAG, относящийся к сканированию поверхности раздела.

Фиг. 4А и 4В иллюстрируются более подробные функциональные блок-схемы входных ячеек и выходных ячеек регистра 300 сканирования поверхности раздела. В частности, на фиг.4А иллюстрируется входная ячейка 340, а на фиг.4В иллюстрируется выходная ячейка 348. Другие входные ячейки и выходные ячейки имеют аналогичные конфигурации.

Как показано на фиг.4А, приведенная в качестве примера, входная ячейка 340 содержит мультиплексор 400 2:1, который имеет первый вход (0) из цепи сканирования поверхности раздела. То есть первый вход соединен для приема выхода предшествующей входной ячейки или выходной ячейки в регистре 300 сканирования поверхности раздела или для приема входа TDI из буфера 371, показанного на фиг.3. Мультиплексор 400 имеет второй вход (1), который принимает выходной сигнал из входного буфера 312. Другие входные ячейки (не показаны) принимают соответствующие входные сигналы из цепи сканирования поверхности раздела и из соответствующих входных буферов.

Мультиплексор 400 имеет вход (S) выбора, который управляется сигналом CAPTURE_ DR, генерируемым контроллером 365 программы анализа транзисторных схем, показанным на фиг.3. Если сигнал CAPTURE_DR активен, мультиплексор 400 выбирает выход входного буфера 312. Если сигнал CAPTURE_DR неактивен, мультиплексор 400 выбирает вход из цепи сканирования поверхности раздела.

Выход мультиплексора 400 предусмотрен как вход (D) данных триггера 400, который синхронизируется сигналом (DR_CLK) синхронизатора регистра данных, генерируемым контроллером 365 программы анализа транзисторных схем (фиг.3). Выход (Q) триггера 402 обеспечен как выход сдвига входной ячейки 340, который обеспечен как вход сдвига в следующую ячейку в цепи сканирования поверхности раздела или, если конкретная входная ячейка является последней ячейкой в цепи сканирования поверхности раздела, как выход данных регистра 300 сканирования 300 в мультиплексор 380 на фиг.3. В процессе операций сдвига сканирования поверхности раздела, сигнал CAPTURE_DR к входу выбора мультиплексора 400 является неактивным, так что триггер 402 соединен как часть сдвигового регистра сканирования поверхности раздела, содержащего другие входные ячейки и выходные ячейки.

Как дополнительно иллюстрируется на фиг.4А, выход входного буфера 312 обеспечен как вход в выходную ячейку 348, описываемую ниже со ссылкой на фиг.4В.

Как иллюстрируется на фиг.4В, показанная в качестве примера, выходная ячейка 348 содержит входной мультиплексор 420, имеющий первый вход (0), второй вход (1), вход (S) выбора и выход. Первый вход соединен для приема выхода из предшествующей входной ячейки или выходной ячейки в регистре 300 сканирования поверхности раздела или для приема входа TDI из буфера 371 на фиг.3. Второй вход принимает выход входного буфера 312 (фиг.4А). Вход выбора управляется сигналом CAPTURE_DR, описанным выше.

Выход входного мультиплексора 420 обеспечен как вход (D) данных триггера 422, который также синхронизируется сигналом DR_CLK, описанным выше. Выход (Q) данных триггера 422 обеспечен как вход данных в триггер-защелку 424, который имеет управляющий вход отпирания триггера-защелки, который управляется сигналом UPDATE_ DR, генерируемым контроллером 365 программы анализа транзисторных схем, показанным на фиг.3. Сигнал UPDATE_DR возбуждается контроллером 365 программы анализа транзисторных схем в ответ на самые последние команды, получаемые через сигнальную шину 372 TMS (фиг.3).

Выход данных триггера 422 также обеспечен как сдвиговый выход выходной ячейки 348, который обеспечен как сдвиговый вход в следующую ячейку в цепи сканирования поверхности раздела или, если конкретная выходная ячейка является последней ячейкой в цепи сканирования поверхности раздела, как выход данных регистра 300 сканирования поверхности раздела к мультиплексору 380, показанному на фиг.3.

Выходная ячейка 348 дополнительно содержит выходной мультиплексор 426, который имеет первый вход (0), второй вход (1), вход (S) выбора и выход. Первый вход выходного мультиплексора 426 принимает выход входного буфера 312 (фиг. 4А). Второй вход выходного мультиплексора 426 принимает выход данных триггера-защелки 424. Вход выбора принимает сигнал TEST_MODE, которые генерируются контроллером 365 программы анализа транзисторных схем в ответ на прием команды режима тестирования по шине 372 TMS. Если сигнал TEST_MODE неактивен, то выход буфера 312 (фиг.4А) обеспечен как выход выходного мультиплексора 426, который обеспечен как вход в выходной буфер 316 (показанный так же на фиг.3 и 4В). Если сигнал TEST_MODE активен, то выход триггера-защелки 424 обеспечен как выход выходного мультиплексора 426 в выходной буфер 316.

Выходные буферы 314 и 316, показанные на фиг.3, отпираются сигналами из выходных ячеек 326 и 324, соответственно. Выходные ячейки 326, 324 аналогичны ячейкам, описанным на фиг.3 за исключением того, что выходы ячеек 324, 326 соединены с управляющим входом высокого импеданса их соответствующих выходных буферов 316, 314. Кроме того, входы ячеек 326, 324 приходят из ОЕА и ОЕВ (выходной разрешающий сигнал А и выходной разрешающий сигнал В), соответственно.

В буферном каскаде 230 интегральной схемы SN74ABT8245 (в предпочтительном варианте осуществления настоящего изобретения) входные ячейки 340 и выходные ячейки 348 соединены в сдвиговом регистре сканирования поверхности раздела так, как описано ниже. Сигнал 370 входа данных тестирования (TDI) обеспечен из входного буфера 371 к выходной ячейке 324 ОЕВ, затем к выходной ячейке 326 ОЕА, затем к входной ячейке 338 DIR, затем к входной ячейке 332 ОЕ (разрешающего сигнала), затем к входным ячейкам (В8, В7, В6, В5, В4, В3, В2, В1) стороны В-тракта передачи дискретных данных, затем к выходным ячейкам (В8, В7, В6, В5, В4, В3, В2, В1) стороны В-тракта передачи дискретных данных, затем к входным ячейкам (А8, А7, А6, А5, А4, A3, А2, А1) стороны А-тракта передачи дискретных данных, затем к выходным ячейкам (А8, А7, А6, А5, А4, A3, А2, А1) стороны А-тракта передачи дискретных данных и затем к сигналу выхода данных тестирования (ТDО) через мультиплексор 380, мультиплексор 385 и выходной буфер 390.

Необходимо отметить, что логическая схема тестирования JTAG в интегральной схеме SN74ABT8245 является более сложной, чем иллюстрируется на фиг.4А и 4В. Для простоты показаны только функции, требуемые для тестирования. Интегральная схема SN74ABT8245 содержит также логику для поддержания других функций JTAG, которые также могут быть использованы, но которые не требуются для осуществления настоящего изобретения, описываемого в этой заявке.

В операции тестирования, предусматриваемой в соответствии с настоящим изобретением, данные, смещаемые в регистр 300 сканирования поверхности раздела, фиксируются в триггерах-защелках 424 в каждой из выходных ячеек 342, 348, 326 и 324, соединенной с А-трактом передачи дискретных данных и с В-трактом передачи дискретных данных, выходных мультиплексорах 426, управляемых для выбора второго входа (1), и выходных буферах 314 и 316, соединенных с каждой выходной ячейкой 342, 348, и отпираются выходными ячейками 326, 324 так, чтобы тестируемый тракт передачи дискретных данных, соединенный со штырьковыми выводами буферных каскадов 230 возбуждался выбранными данными из буферных каскадов 230. Данные на тракте принимаются другой логической схемой, соединенной с тестируемым трактом, и сравниваются с ожидаемыми данными для определения, каждый ли штырьковый вывод на тестируемом тракте передачи дискретных данных возбужден должным образом.

Наоборот, тестируемый тракт передачи дискретных данных может возбуждаться другой логической схемой, если выходные буферы 314, 316 являются недееспособными. Затем данные на тестируемом тракте принимаются через входные буферы 312, 318 и собираются в соответствующих триггерах 402. После этого, принятые данные смещаются из регистра 300 сканирования поверхности раздела в шину ТDО. Последовательные выходные данные на TDO принимаются задающей схемой тестирования JTAG (смотри фиг.7) и сравниваются с ожидаемыми данными для определения должным ли образом функционирует тестируемый тракт передачи дискретных данных.

Таким образом, сменные платы 200, содержащие схемотехнику JTAG в регистре 300 сканирования поверхности раздела, обеспечивают недорогие и эффективные систему и способ тестирования частей тракта 170 передачи дискретных данных PCI и тракта 195 передачи дискретных данных памяти, которые иначе не были бы тестируемыми в условиях испытаний JTAG.

В процессе работы, как схематически показано на фиг.7, команды и данные JTAG смещаются в регистры команд и данных в схемотехнике JTAG (на фиг.7 не показана) на объединительной плате 600 и в схемотехнике JTAG (на фиг.7 также не показана) на первой и второй платах 200 модуля памяти с двухрядным расположением штырьковых выводов из задающей схемы 700 тестирования JTAG. Данные и команды смещаются в их соответствующие регистры через соединитель 705, кабель 710, соединитель 715, соединитель 740, соединитель 745 и кабель 750. Соединитель 715 входит в контакт с сопрягающимся соединителем 420 на краю объединительной платы 600, как показано на фиг.7, в то время как соединители 725, 730, 740 и 745 входят в контакт с соответствующими сопрягающимися соединителями на краях сменных плат 200. В одном предпочтительном варианте осуществления настоящего изобретения, соединители 725, 730, 740 и 745, соответственно через один, являются соединителями вилочного и розеточного типа (например, соединитель 725 кабеля 720 является вилочным соединителем, соединитель 730 кабеля 735 является розеточным соединителем и так далее), так что одна или более сменных плат 200 могут быть шунтированы (если, например, имеется незанятое гнездо). Таким образом, например, если гнезда 180, 190 не заняты оба, соединитель 725 кабеля 720 может входить в контакт непосредственно с соединителем 745 кабеля 750 так, чтобы задающая схема тестирования JTAG могла быть просто соединена для тестирования со схемами для тестирования JTAG.

Как только соответствующие данные смещены в регистры JTAG, эти данные поступают к точкам соединения и принимаются схемотехникой JTAG в другом месте, имеющем связь с точками соединения. Например, первая сменная плата 200 (входящая в контакт с гнездом 180) может выдавать данные в тракт 195 передачи дискретных данных (смотри фиг.1), которые принимаются, например, контроллером 140 динамического запоминающего устройства с произвольной выборкой. Схемотехника JTAG в контроллере 140 динамического запоминающего устройства с произвольной выборкой (не показана) считывает данные в тракте 195 передачи дискретных данных и передает их назад в задающую схему 700 тестирования JTAG через соединитель 715.

Хотя выше был подробно описан предпочтительный вариант осуществления настоящего изобретения, квалифицированному в этой области техники специалисту будет очевидно, что без отклонения от существа и объема изобретения могут быть сделаны некоторые модификации. Например, недорогие тестовые схемы другие, чем описанная в этой заявке интегральная схема SN74ABT8245, могут быть применены для выполнения сменной тестовой платы 200 JTAG. Пo этой причине, приведенное выше описание должно восприниматься как иллюстративное, а не как ограничительное. В соответствии с вышесказанным, объем настоящего изобретения должен интерпретироваться только в объеме приведенной ниже формулы изобретения.

Изобретение относится к области тестирования трактов передачи дискретных данных на печатной плате и может быть использовано для тестирования целостности двухточечных соединений на монтажной плате с использованием стандарта Международной объединенной группы по автоматизации тестирования (JTAG). Техническим результатом является возможность тестирования отдельно взятых цепей на печатной плате и соединений, сопряженных со сменными гнездами (слотами). Одна из систем содержит монтажную плату со схемой, подлежащей тестированию, шины, не менее одного периферийного слота или слота расширения, съемные платы тестирования, по стандарту JTAG. Другие варианты систем содержат также регистр поверхности раздела, соединительные участки, схему контроля процесса сканирования поверхности раздела, регистр команд, контроллер подключения (ТАР-контроллер). Съемная плата тестирования содержит соединительный участок, буферную схему, шины. Другой вариант съемной платы содержит два соединительных участка, интегральную схему с множеством приемопередатчиков шины. Способы описывают работу систем. 7 с. и 7 з.п. ф-лы, 8 ил.

| US 5331274 А, 19.07.1994 | |||

| СПОСОБ ОБНАРУЖЕНИЯ ОБРЫВОВ И КОРОТКИХ ЗАМЫКАНИЙ В ЭЛЕКТРИЧЕСКОМ МОНТАЖЕ | 1991 |

|

RU2020499C1 |

| US 5198759 А, 30.03.1993 | |||

| US 5416409, 16.05.1995. | |||

Авторы

Даты

2002-05-20—Публикация

1996-11-13—Подача