/5

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1994 |

|

RU2092891C1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Суммирующее устройство | 1990 |

|

SU1775722A1 |

| Суммирующее устройство | 1991 |

|

SU1803912A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации при реализации технических средств цифровых вычислительных машин и дискретной автоматики. Цель изобретения - сокращение аппаратурных затрат. Устройство содержит ассоциативный запоминающий блок 1, группы элементов И 2, 3, группы элементов задержки 4, 5, преобразователи 6, 7 двоичного кода в уплотненный код, блок 8 деления на два в уплотненном коде, содержащий группу элементов И 9, группу элементов ЗАПРЕТ 10 и элемент ИЛИ 11, входы 12 слагаемых, входы 13, 14 синхронизации и выход 15 результата. 1 ил.

Ij ш Plm 13

l«J«

13

V f

№

CO СЛ

00 4

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации при реализации техни- ческих средств цифровых вычислитель- Hiiix машин и дискретной автоматики.

Цель изобретения - сокращение аппаратурных затрат.

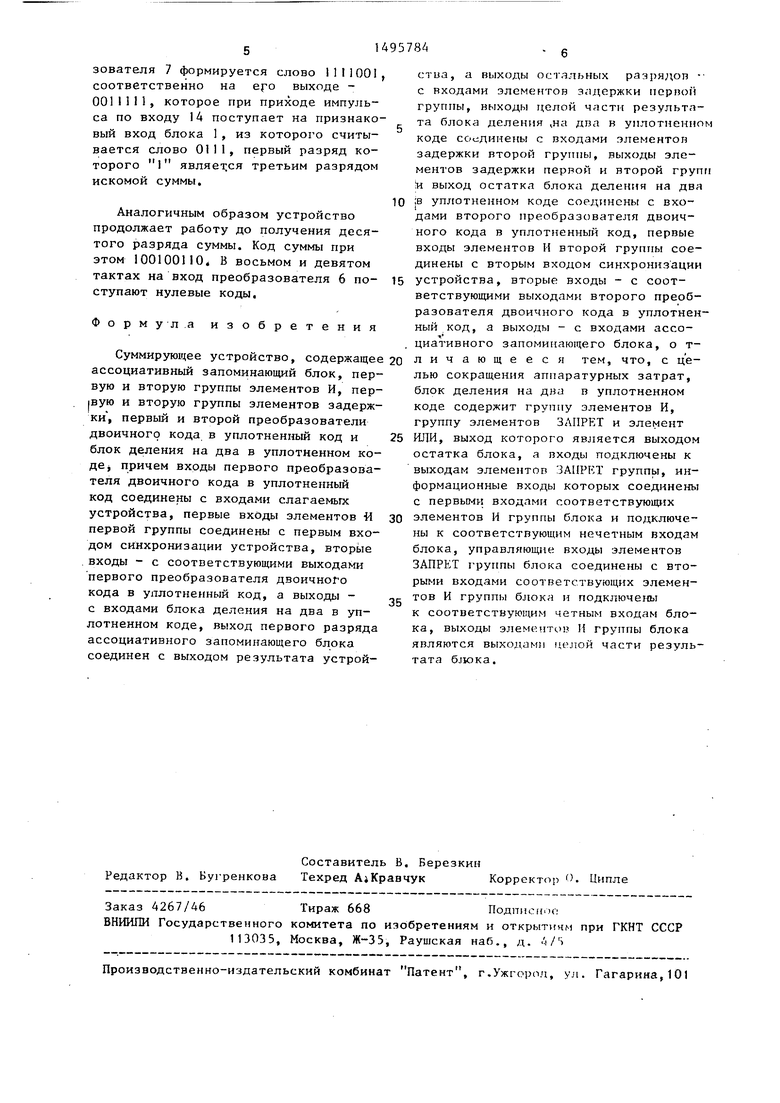

На чертеже представлена структур- ная схема устройства.

Устройство содержит ассоциативный запоминающий блок 1, группы элементов И 2 и 3, группы элементов 4 и 5 задержки, преобразователи 6 и 7 дво- ичного кода в уплотненный код, блок 8 деления на два в уплотненном коде, содержащий группу элементов И 9, группу элементов ЗАПРЕТ 10 и элемент ИЛИ 11, входы 12 слагаемых, входы 13 и 14 синхронизации и выход 15 результата.

Устройство работает следующим образом.

На входы 12 поступают одноименные разряды всех слагаемых, начиная с младших разрядов. Преобразователь 6 преобразует поступающий на его входы двоичный код в уплотненный код, который через элементы И 2 поступает на входы блока В в течение тактового импульса по входу 13. Полученное в результате деления слово является частью ассоциативного признака для ассоциативного запоминающего блока 1. Второй частью признака являются все, кроме первого, разряды кода, считан- ного из 6jroKa 1. Обе части признака поступают на преобразователь 7 дв9ич ного кода в уплотненный код через элементы 5 и 4 задержки, причем сигнал с выхода остатка блока .8, сфор- мированнь1Й дизъюнкцией элементов ЗАПРЕТ 10 на элементе ИЛИ 11, поступае на преобразователь 7 без задержки, а сигналы с выходов целой части результата блока 8 элементами И 9 на входы элементов 5 задержки. Сформированный на -выходе преобразователя 7 признак дополнительно синхронизирует ся импульсом по входу 14 с помощью элементов И 3. Такая синхронизация исключает влияние неидеальности элементов 4 и 5 задержки. На выходе 15 формируется очередной разряд суммы. Общее число тактов вычисления равно m n+Clog2N J,

где п - разрядность слагаемых; N - количество слагаемых.

Пусть необходимо просуммировать следующие семь слагаемых: 010110; 101011; 011011; 111111; 101110; 110011; 101010.

Обрабатываемые срезы на входе преобразователя 6 имеют вид: 0111010; 1111111; 1001100; 0111101; 1011010; 0101111.

На выходе преобразователя 6 обрабатываемые срезы имеют вид: 0001111; 1111111; 0000111; 0011111; 0001111; 0011111.

В течение первого тактового импульса, поданного на вход 13 синхронизации, на вход блока 8 подаются младшие разряды слагаемых, т.е. 0001111.

В результате преобразования этого кода блоком 8 порождается слово 001I первый разряд которого О без задержки подается на первый вход преобразователя 7, а остальные через элементы 5 задержки - на соответствующие входы того же преобразователя. Так как в первом такте из блока 1 ничего не считывается, то к приходу первого импульса по входу 14 синхронизации на все входы преобразователя 7 подаются нули.

Сформированный признак с выхода преобразователя 7 кода - 0000000, с приходом тактового импульса по входу 14 поступает на признаковые входы блока 1. Следовательно, в первом такте из блока 1 считывается слово 0000, первый разряд которого О является младшим разрядом искомой суммы.

В течение второго, импульса, подан ;Ного на вход 13 синхронизации, на вход блока 8 с выхода преобразователя 6 подается второй разряд} ый срез слагаемых, т.е. код 1111111.

Он преобразуется в код 1 1 J 1 . На входе преобразователя 7 формируется слово 1011000 соответственно на его выходе 0000111, которое по приходу импульса по входу 14 поступает на признаковые входы блока 1, из которого считывается слово ООП, первый разряд которого 1 является вторым разрядом искомой суммы. .

В течение третьего импульса, поданного на вход 13 синхронизации, на вход блока 8 с выхода преобразователя 6 подается третий обрабатываемый срез 0000111. Блок 8 преобразовывает его в слово 1001. На входе преобразователя 7 формируется слово 111100I соответственно на его выходе - 00111I1, которое при приходе импульса по входу 14 поступает на признаковый вход блока 1, из которого считывается слово 0111, первый разряд которого I являет.ся третьим разрядом искомой суммы.

Аналогичным образом устройство продолжает работу до получения десятого разряда суммы. Код суммы при этом 100100110, В восьмом и девятом тактах на вход преобразователя 6 поступают нулевые коды.

Форм у л .а изобретения

25

диативного запоминающего блока, о т-

Суммирующее устройство, содержащее 20 личающееся тем, что, с целью сокращения аппаратурных затрат, блок деления на два в уплотненном коде содержит группу элементов И, группу элементов ЗАПРЕТ и элемент ИЛИ, выход которого является выходом остатка блока, а входы подключены к выходам элементов ЗАПРЕТ группы, информационные входы которых соединены с первыми входами соответствующих элементов И группы блока и подключены к соответствующим нечетным входам блока, управляю11у1е входы элементов ЗАПРЕТ г руппы блока соединены с вторыми входами соответствующих элементов И группы блока и подключегш к соответствующим четным входам блоассоциативный запоминающий блок, первую и вторую группы элементов И, пер- 1вую и вторую группы элементов задержки, первый и второй преобразователи двоичного кода в уплотненный код и блок деления на два в уплотненном коде j причем входы первого преобразователя двоичного кода в уплотненный код соединены с входами слагаемых устройства, первые входы элементов И первой группы соединены с первым входом синхронизации устройства, вторые . входы - с соответствующими выходами первого преобразователя двоичного кода в уплотненный код, а выходы - с входами блока деления на два в уплотненном коде, выход первого разряда ассоциативного запоминающего блока соединен с выходом результата устрой30

35

ка, выходы элементов И группы блока

являются выходам) тата блока.

целой части резульстиа, а выходы остальных разрядов с входами элементов задержки первой группы, выходы целой части результата блока деления ,на два в уплотненном

коде соединены с входами элементов

задержки второй гругтпы, выходы элементов задержки первой и второй групп и выход остатка блока деле({ия на два

в уп/готненном коде соединены с входами второго преобразователя двоичного кода в уплотненный код, первые входы элементов И второй группы соединены с вторым входом синхронизации

устройства, вторые входы - с соответствующими выходами второго преобразователя двоичного кода в уплотненный код, а выходы - с входами ассо25

20

20

30

20

35

ка, выходы элементов И группы блока

являются выходам) тата блока.

целой части резуль

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-08—Подача