| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1987 |

|

SU1444752A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1994 |

|

RU2092891C1 |

| Суммирующее устройство | 1986 |

|

SU1396139A1 |

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| Суммирующее устройство | 1987 |

|

SU1495784A1 |

| Устройство для суммирования @ @ -разрядных двоичных чисел | 1984 |

|

SU1277095A1 |

| Ассоциативное устройство для суммирования массива чисел | 1988 |

|

SU1564615A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

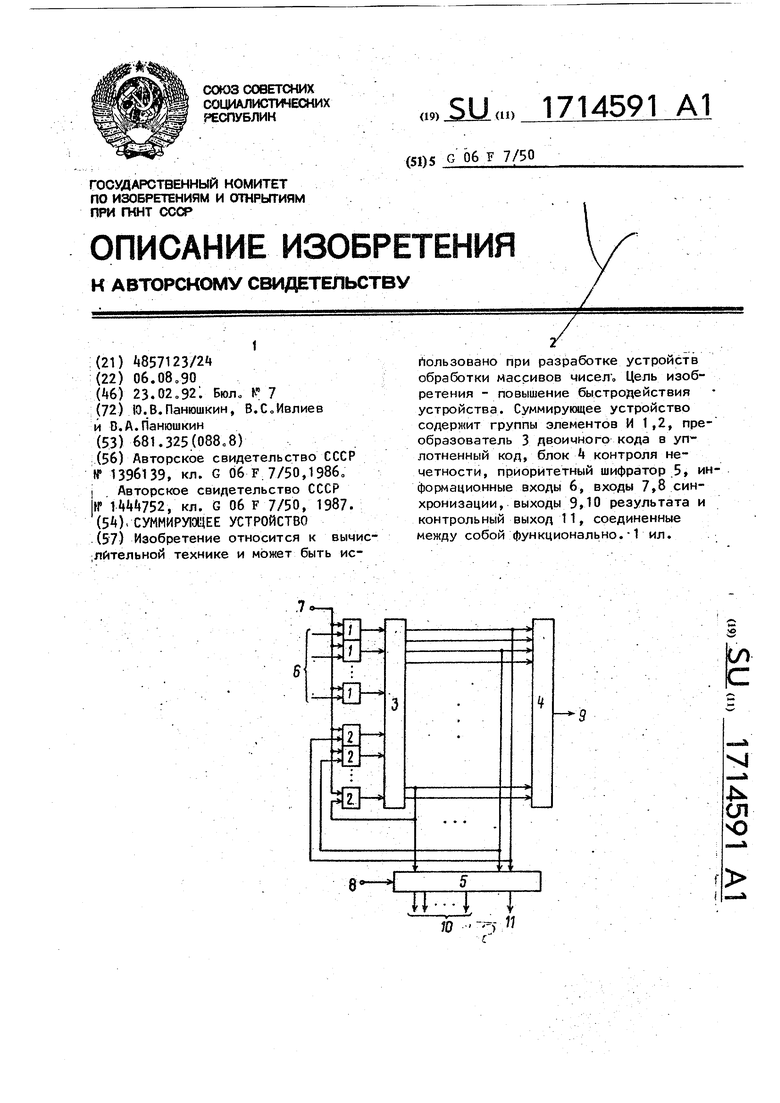

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств обработки массивов чисел'. Цель изобретения - повышение быстродействия устройства. Суммирующее устройство содержит группы элементов И 1,2, пре" образователь 3 двоичного кода в уплотненный код, блок *» контроля нечетности, приоритетный шифратор 5, информационные входы 6, входы 7,8 синхронизации, выходы 9» 10 результата и контрольный выход 11, соединенные между собой функционально.•1 ил.

ь. ел

Ю

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств обработки цифровой информации, осуществляющих обработку массивов чисел.

Известно суммирующее устройство, содержащее постоянный запоминающий блок,первую и вторую группы элементов И, группу элементов задержки, преобразователь двоичного кода в уплотненный кол, группу элементов НЕ, информационный вход, вход синхронизации устройства, выход результата устройства.

Недостатком этого устройства является большая сложность и низкое быстродействие.

Наиболее близким к предлагаемому является суммирующее устройство, содержащее две группы элементов И, преобразователь двоичного кода в уплотненный код, группу элементов ИЛИ блок контроля нечетности, причем циф ра результата формируется на выходе блока контроля нечетности, а группа элемектор ИПЛ формирует сдвинутый на один разряд код количества единиц для осуществления последовательного по разрядам параллельного по словам ме:тода суммирования,

Недостатком известного устройства является .низкое быстродействие

Технические средства прототипа ориентированы на вычисление суммы по тактам, количество которых зависит не только от разрядности слагаемых, но и от количества слагаемых Длительность тактэ определяется задержками сигнала на элементах И ИЛИ и преобразователе двоичного кода в уплотненный код

Однако яри суммировании разрядных срезов в суммирующем устройстве к моменту суммирования последнего раз рядного среза имеется вся информация об общей сумме, что позволяет отказаться от дополнительных тактов, определяемых количеством слагаемых Кроме того, -дпительность каждого такта может быть уменьшена за счет исключения из схемы элементов ИЛИ так как для анализа признаков переноса достаточно информации содержащейся на четных выходах преобразователя двоичного кода в уплотненный код. Все это снижает быстродействие прототипа.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в суммирующее устройство, содержащее первую и вторую группы элементов И, преобразователь двоичного кода в уплотненный код и блок контроля нечетности, причем первые входы элементов И первой и второй групп подключены к первому входу синхронизации устройства, вторые входы элементов И первой группы соединены с информационными входами устройства, выходы элементов И первой группы подключены к соответствующим входам первой группы преобразователя двоичного кода в уплотненный, выходы элементов И второй группы подключены к входам второй группы преобразователя двоичного кода в уплотненный код, выходы

которого соединены с входами блока контроля нечетности, выход которого подключен к первому выходу результата устройства, введены приоритетный шифратор, второй вход синхронизации

устройства, второй выход результата, контрольный выход устройства, причем четные выходы преобразователя двоичного кода в уплотненный код соединены с вторыми входами соответствующих элементов И второй группы и информационными входами приоритетного шифратора, управляющий вход которого соединен с вторым входом синхронизации устройства,выход кода приоритетного шифратора соединен с вторым выходом результата устройства,а его контрольный выход соединен с конт- , рольным выходом устройства.

На чертеже изображена функциональная схема предлагаемого устройства.

Суммирующее устройство содержит группы элементов И 1 и 2, преобразо-: ватель 3 двоичного кода в уплотненный 5 код (ПДУ), блок контроля нечетности (БКН), приоритетный шифратор 5, информационные входы 6, первый 7 и второй 8 входы синхронизации, первый 9 и второй 10 выходы результата, контрольный выход 11 устройства.

Первые входы элементов И первой 1 и второй 2 групп подключены к первому входу 7 синхронизации устройства Вторые входы элементов И первой группы 1 соединены с информационными входами 6 устройства. Выходы элементов И первой группы 1 подключены к соответствующим входам первой группы ПДУ 3. S Выходы элементов И второй группы подключены к входам второй группы ПДУ 3. Выходы последнего соединены с входами БКН , выход которого подключен к первому выходу 9 результата устройства. Четные выходы ПДУ 3 соединены с вторыми выходами соответствующих элементов И второй группы 2 и информационными входами приоритетного шифратора 5, управляющий вход которого соединен с вторым входом 8 синхронизации устройства, В качестве ПДУ .3 может быть использован типовой преобразователь двоичного кода в уплотненный. Выход кода приоритетного шифратора 5 соединен с вторым выходом 10 результата устройства, а контрольный выход соединен с контрольным выходом 11 устройства, : Первая группа 1 элементов И предназначена для пересылки по синхроимпульсу, поступающему по первому входу 7 синхронизации на первую г|эуп пу входов ПДУ 3, разрядных срезов, слагаемых с информационного входа 6 устройства. Вторая группа 2 элементов И пред назначена для пересылки по синхроимпульсу,- поступающему по первому входу 7 синхронизации, признаков переноса с четных выходов ПДУ 3 на вт рую группу входов ПДУ 3. ПДУ 3 предназначен для преобразования двоичных кодов, поступающих по первой и второй группе входов в уплотненный код. БКН предназначен для контроля нечетности кода на выходе ПДУ 3 и формирования выходного кода на первый выход 9 результата. В качестве БКН может быть использован типовой блок контроля нечетности. Приоритетный шифратор 5 предназна чен для формирования по синхроимпуль су, поступающему по второму входу. 8 синхронизации, двоичного кода номера старшей единицы на четных выходах ПДУ ЗИ выдачи этого кода на второй выход 10 результата, а также для выдачи на контрольный выход 11 устройства информации о входном коде. Устройство работает следующим образом. На входы 6 устройства поступают одноименные разряды всех слагаемых, начиная с младших разрядов, которые через элементы И 1 поступают на пер91вую группу входов ПДУ 3 в течение тактового импульса по первому входу 7 синхронизации. Данный тактовый импульс также пропускает на вторую группу входов ПДУ 3 признак перенез са, сформированный на четных выходах ПДУ 3 в предыдущем такте суммирования На входе ПДУ 3 уплотненный код, соответствующий количеству логических 1 в кодах, которые поступили по первой и второй группам входов. В случае, если количество логических 1 в уплотненном коде будет нечетно, то на выходе БКН k, сформировано значение результата, равное логической 1, в противоположном случае - логический Информация с четных выходов ПДУ 3 также поступает на входы приоритетного шифратора 5, однако на его выход информация не-выдается, так как отсутствует тактовый импульс на втором входе 8 синхронизации. Таким образом, осуществляется суммирование разрядных срезов слагаемых в течение N тактов, где N - разрядность слагаемых. Длительность одного такта суммирования t. определяется задержками сигналов на элементах И (t) и пду.,. Чс и Подача следующего разрядного среза на информационные входы 6 и тактового сигнала на первый вход 7 синхронизации возможна с периодом t .. Подача тактового сигнала по .второму входу 8 синхронизации привязывается к моменту формирования на выходе ПДУ 3 уплотненного кода в N-M такте суммирования. При этом включается в работу приоритетный шифратор 5 и формирует на второй выход 10 резуль тата двоичный код старшей единицы на выходе ПДУ 3, соответствующий старим (N+1), (N+2), ,. .jjlog n разрядам суммы слагаемых, где п - количество слагаемых, - ближайее целое число, превышающее log,-п, сли - не целое. Входная раз- ядность приоритетного шифратора 5 пределяется количеством четных выхоов ПДУ 3, а количество выходов еличиной И 1о§2п . Пример, Пусть необходимо проуммировать следующие пять слагаемых: 101101, 110110, 011101, 110111, 100101. Обрабатываемые срезы на вы ходах элементов И 1 имеют вид: 10111 01010, 11ГП, 10100, 01110, 11.011, В течение первого тактового импуль са поданного на первый вход 7 синхронизации, на вход ПДУ 3 подается разрядный срез младших разрядов сла гаемых 10111 и признак переноса 0000, так как в исходном состоянии на всех выходах ПДУ 3 присутствуют логические О ., На выходе ПДУ 3 формируется код 000001111. Настоящий код четный, поэтому с выхода БКН на первый выход 9 результата поступает логический О, а признак переноса равен 0011, так как только на двух четных выходах ПДУ 3 сформирован код 1, Приоритетный шифратор 5 не работает, на.второй выход 10 результата поступает код 0000. Через время .no первому входу 7 синхросигна.па подается тактовый импульс, а ка информационные входы 6второй разрядный срез 01010. Этот код поступает на первую группу входов ПДУ 3. На вторую группу входов ПДУ 3 поступает через вторую группу 2 элементов И признак переноса 0011. На выходе ПДУ 3 формируется, код 000001111 о Данный код четный,поэтому значение результата равно О, а признак переноса 0011. В третьем такте работы устройства на входы ПДУ 3 поступают коды 11111 и 0011. На выходе ПДУ 3 формируется код 001111111. Данный код нечетный, поэтому БКН k форм1фует значение результата 1 а признак переноса равен 0111о Анал.гичным образом устройство продолжает работу в четвертом и пятом тактах, В шестом такте на входы ПДУ 3 поступают коды 11011 и 0011 о На выходе ПДУ 3 формируется уплотненный код 000111111 о Данный код четный, поэтому БКН формирует значение результа та Одновременно с этим по второ му входу 8 синх,ронизации подается тактовый импульс и на выходе приори тетного шифратора 5 формируется двоичный ютд 011,так как на его вход поступают коды 1.с второго, четвер того и liiecToro выходов ПДУ 3 Двоичный код 011 подается на вторый выход 10 результата о Таким образом,полученный результат равен 011011100. Технико-экономическуюэффективность изобретения можно оценить вели чиной относительного увеличения быстродействия. В известном устройстве общее число тактов вычисления суммы равно m N + 3log2n , Длительность одного такта определяется величиной - Л л. A. -ТС и ИДУ - ИЛИ. где , , пд,у - соответственно задержки сигналов на элементах И, ИЛИ и ПДУ, В предлагаемом устройстве длительность такта уменьшена на величи У или кроме того, сокращено количество тактов вычисления суммы до величины N. Таким образом, выигрыш времени составляет At к иАи- 1°8г сФормула изобретения Суммирующее устройство, содержащее первую и вторую группы элементов И, преобразователь двоичного кода в уплотненный код и блок контроля нечетности, причем первые входы элементов И первой и второй групп соеди-: нены с первым входом синхронизации устройства, вторые входы элементов И первой группы соединены соответственно с информационными входами устройства, выходы элементов И первой группы соединены соответственно с входами первой группы преобразователя двоичного кода в уплотненный код, входы второй группы которого соединены соответственно с выходами элементов И второй группы, разрядные выходы преобразователя двоичного кода в уплотненный код соединены соответственно с входами блока контроля нечетности, выход которого соединен с первым выходом результата устройства, отличающееся тем, что, с целью повышения быстродействия, в него введен приоритетный шифратор,информационные входы которого соединены соответственно с вторыми входами элементов И второй группы и четными вы- I ходами преобразователя двоичного кода в уплотненный код, выход кода приоритетного шифратора является вторым

17Й59110

выходом результата устройства,второйшифратора, контрольный выход которовход синхрйнизации которого соединенго является контрольным выходом устс управля1о цим входом приоритетного.ройства.

| Суммирующее устройство | 1986 |

|

SU1396139A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-23—Публикация

1990-08-06—Подача