Изобретение относится к области сокращения информационной избыточности и, в первую очередь, сжатия данных, представляющих многомерные сигналы, в частности изображения.

Известны устройства (например, [1]) для сжатия данных без потерь информации, содержащие блок неравномерного кодирования комбинаций данных соответственно частоте (вероятности) этих комбинаций. Такие устройства имеют небольшой и негарантированный коэффициент сжатия данных из-за обычно низкой достоверности сведений о статистических характеристиках источника данных.

Известны устройства [2] для сжатия данных в пространстве преобразований, содержащие последовательно соединенные блоки дискретного преобразования (косинусного, Уолша и т.д.), квантования и неравномерного кодирования. Недостатком этих устройств являются негарантированное воспроизведение низкоэнергетичных элементов сигнала и высокая сложность.

От этого недостатка свободны устройства [3, 4] для сжатия данных методом дифференциальной импульсно-кодовой модуляции (ДИКМ), содержащие вычитатель, вход уменьшаемого которого является информационным входом устройства, квантователь, выход которого является выходом устройства, а также предсказатель значения текущего отсчета, выход и один вход которого соединены со входом вычитаемого вычитателя, а другой вход с выходом квантователя, вход которого соединен с выходом вычитателя.

Однако и эти устройства имеют недостаток, состоящий в низком быстродействии и недостаточно высоком коэффициенте сжатия данных. Низкое быстродействие обусловлено использованием предсказателя, задерживающего действия по текущему отсчету сигнала до выполнения действий по предыдущему отсчету. Недостаточно высокий коэффициент сжатия обусловлен отсутствием в нем декорреляции отсчетов сигнала посредством адаптивной дискретизации, при которой соответственно соотношению значений разностей в группе назначался бы для этой группы шаг дискретизации, совпадающий с исходным шагом дискретизации или отличающийся от него (адаптивная регулярная дискретизация), или одинаковые по некоторому критерию разности независимо от их местоположения в группе объединялись бы в серии (адаптивная нерегулярная дискретизация).

Заявляемое изобретение направлено на исключение предсказателя и повышение степени декорреляции отсчетов сигналов.

Решение этой задачи дает повышение быстродействия и коэффициента сжатия данных, обеспечиваемых устройством.

Для этого (в первом варианте предлагаемого устройства) в устройство для сжатия данных, содержащее вычитатель, вход уменьшаемого которого является информационным входом устройства, и квантователь, выход которого является информационным выходом устройства, дополнительно введены формирователь локальных центров, информационный вход которого соединен с одноименным входом устройства, вход идентификации локальных центров является одноименным входом устройства, а выход является выходом локальных центров устройства и соединен со входом вычитаемого вычитателя, а также блок адаптивной нерегулярной пороговой дискретизации, информационные вход и выход которого соединены соответственно с выходом вычитателя и входом квантователя, вход идентификации локальных центров соединен с одноименным входом устройства, а вход идентификации разностей, вход порога нерегулярной дискретизации, выход среднего значения разностей и выход кода конфигурации являются одноименными входами и выходами устройства. Это позволяет запоминать в формирователе оценок локальных центров один из группы отсчетов сигнала и вычислять в вычитателе разность между этим отсчетом (локальным центром) и остальными отсчетами группы, то есть производить частичную декорреляцию отсчетов сигналов без предсказателя, а также выявлять в группе разностей, поступающих с выхода вычитателя, серии разностей, различие между которыми не превышает порога; усреднять значения входящих в серии разностей, в том числе определять среднее значение разностей группы как коррективу локального центра; идентифицировать совокупность получающихся серий различной длины и одиночных (уникальных) разностей соответствующим кодом конфигурации и, в итоге, повышать быстродействие и коэффициент сжатия данных. Кроме того, изменением порога нерегулярной дискретизации можно управлять коэффициентом сжатия данных, например, в зависимости от заполненности уравнивающего буфера в системах, использующих предлагаемое устройство.

Второй вариант предлагаемого устройства состоит в том, что в устройство для сжатия данных, содержащее вычитатель, вход уменьшаемого которого является информационным входом устройства, и квантователь, выход которого является информационным выходом устройства, а вход соединен с выходом вычитателя, дополнительно введены формирователь локальных центров, информационный вход которого соединен с одноименным входом устройства, вход идентификации локальных центров является одноименным входом устройства, а выход является выходом локальных центров устройства и соединен со входом вычитаемого вычитателя, а также блок адаптивной нерегулярной беспороговой дискретизации, информационный вход которого соединен с выходом квантователя, а вход идентификации разностей и выход кода конфигурации являются одноименными входом и выходом устройства. Это позволяет выявлять в группе разностей, поступающих с выхода вычитателя и преобразованных квантователем, серии одинаковых кодов разностей, идентифицировать совокупность получающихся серий и уникальных кодов разностей соответствующим кодом конфигурации и, в итоге, повышать быстродействие и коэффициент сжатия данных.

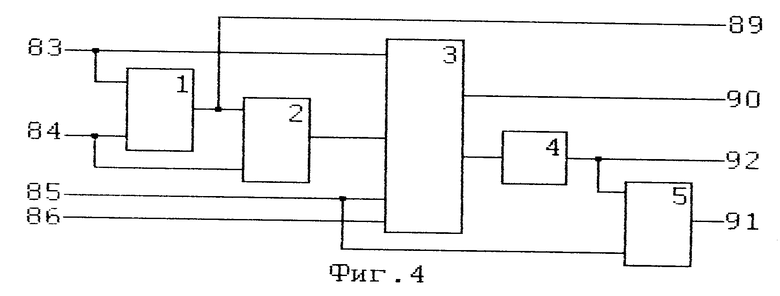

Третий вариант предлагаемого устройства состоит в том, что в устройство для сжатия данных, содержащее вычитатель, вход уменьшаемого которого является информационным входом устройства, и квантователь, выход которого является информационным выходом устройства, дополнительно введены формирователь локальных центров, информационный вход которого соединен с одноименным входом устройства, вход идентификации локальных центров является одноименным входом устройства, а выход является выходом локальных центров устройства и соединен со входом вычитаемого вычитателя, а также блок адаптивной регулярной дискретизации, информационные вход и выход которого соединены соответственно с выходом вычитателя и выходом квантователя, вход идентификации локальных центров соединен с одноименным входом устройства, а вход идентификации разностей, вход порога регулярной дискретизации и выход признака децимации являются одноименными входами и выходами устройства. Это позволяет повысить быстродействие и вычислять некоторый показатель детальности фрагмента изображения, представленного отсчетами группы и, (если этот показатель не превосходит порога регулярной дискретизации) производить регулярную дискретизацию изображения с пониженной частотой (например, прореживание отсчетов с постоянным в пределах группы коэффициентом) и, в итоге, повышать коэффициент сжатия данных. Существенным фактором эффективности этого варианта устройства является возможность передискретизации отсчетов группы по замкнутому контуру, что исключает обычно присущие пофрагментной передискретизации краевые эффекты, а также позволяет получить "шахматную" структуру прореженных отсчетов, благоприятную для улучшения качества восстановленного сигнала.

Четвертый вариант предлагаемого устройства состоит в том, что в устройство для сжатия данных, содержащее вычитатель, вход уменьшаемого которого является информационным входом устройства, и квантователь, выход которого является информационным выходом устройства, дополнительно введены формирователь локальных центров, информационный вход которого соединен с одноименным входом устройства, вход идентификации локальных центров является одноименным входом устройства, а выход является выходом локальных центров устройства и соединен со входом вычитаемого вычитателя, а также блок адаптивной нерегулярной пороговой дискретизации и блок адаптивной нерегулярной беспороговой дискретизации, причем вход идентификации локальных центров, информационные вход, выход блоков пороговой дискретизации и информационный вход блока беспороговой дискретизации соединены соответственно со входом идентификации локальных центров устройства, выходом вычитателя, входом и выходом квантователя, вход идентификации разностей, вход порога нерегулярной дискретизации, выход среднего значения разностей блока пороговой дискретизации и выход кода конфигурации блока беспороговой дискретизации являются одноименными входами и выходами устройства, а вход идентификации разностей блока беспороговой дискретизации соединен с одноименным входом устройства. Это позволяет повысить быстродействие, а выбором порога нерегулярной пороговой дискретизации и нелинейной шкалы преобразования сигнала в квантователе эффективно управлять образованием серий одинаковых кодов разностей как в области низких (околопороговых) их значений, так и в области средних и больших значений разностей и, в итоге, получать повышенное увеличение коэффициента сжатия данных.

Пятый вариант предлагаемого устройства состоит в том, что устройство для сжатия данных, содержащее вычитатель, вход уменьшаемого которого является информационным входом устройства, и квантователь, выход которого является информационным выходом устройства, дополнительно введены формирователь локальных центров, информационный вход которого соединен с одноименным входом устройства, вход идентификации локальных центров является одноименным входом устройства, а выход является выходом локальных центров устройства и соединен со входом вычитаемого вычитателя, а также блок адаптивной регулярной дискретизации и блок адаптивной нерегулярной пороговой дискретизации, причем вход идентификации разностей, вход порога регулярной дискретизации и выход признака децимации блока регулярной дискретизации, вход порога нерегулярной дискретизации, выход среднего значения разностей и выход кода конфигурации блока нерегулярной дискретизации являются одноименными входами и выходами устройства, а вход идентификации локальных центров, информационные вход, выход блока регулярной дискретизации, вход идентификации разностей, информационный выход, вход идентификации локальных центров, вход признака децимации блока нерегулярной дискретизации соединены соответственно со входом идентификации локальных центров устройства, выходом вычитателя, информационным входом блока нерегулярной дискретизации, входом идентификации разностей устройства, входом квантователя, входом идентификации локальных центров устройства, выходом признака децимации блока регулярной дискретизации. Это позволяет повысить быстродействие и благодаря сочетанию эффектов адаптивной регулярной дискретизации и адаптивной нерегулярной пороговой дискретизации получать повышенное увеличение коэффициента сжатия данных.

Шестой вариант предлагаемого устройства состоит в том, что в устройство для сжатия данных, содержащее вычитатель, вход уменьшаемого которого является информационным входом устройства, и квантователь, выход которого является информационным выходом устройства, дополнительно введены формирователь локальных центров, информационный вход которого соединен с одноименным входом устройства, вход идентификации локальных центров является одноименным входом устройства, а выход является выходом локальных центров устройства и соединен со входом вычитаемого вычитателя, а также блок адаптивной регулярной дискретизации и блок адаптивной нерегулярной беспороговой дискретизации, причем вход идентификации разностей, вход порога регулярной дискретизации, выход признака децимации блока регулярной дискретизации, выход кода конфигурации блока нерегулярной дискретизации являются одноименными входами и выходами устройства, а вход идентификации локальных центров, информационные вход и вход блока регулярной дискретизации, информационный вход, вход идентификации разностей и вход признака децимации блока нерегулярной дискретизации соединены соответственно со входом идентификации локальных центров устройства, выходом вычитателя, входом квантователя, выходом квантователя, входом идентификации разностей устройства и выходом признака децимации блока регулярной дискретизации. Это позволяет повысить быстродействие и, благодаря сочетанию эффектов адаптивной регулярной и адаптивной нерегулярной беспороговой дискретизации получать повышенное увеличение коэффициента сжатия данных.

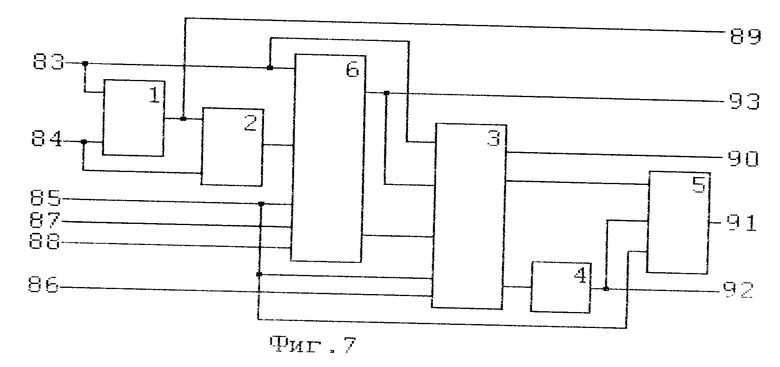

Седьмой вариант предлагаемого устройства состоит в том, что в устройство для сжатия данных, содержащее вычитатель, вход уменьшаемого которого является информационным входом устройства, и квантователь, выход которого является информационным выходом устройства, дополнительно введены формирователь локальных центров, информационный вход которого соединен с одноименным входом устройства, вход идентификации локальных центров является одноименным входом устройства, а выход является выходом локальных центров устройства и соединен со входом вычитаемого вычитателя, а также блок адаптивной регулярной дискретизации, блок адаптивной нерегулярной пороговой дискретизации и блок адаптивной нерегулярной беспороговой дискретизации, причем вход идентификации разностей, вход порога регулярной дискретизации, выход признака децимации блока регулярной дискретизации, выход среднего значения разностей блока нерегулярной пороговой дискретизации, выход кода конфигурации блока нерегулярной беспороговой дискретизации являются одноименными входами и выходами устройства, вход идентификации локальных центров и вход идентификации разностей блока нерегулярной пороговой дискретизации, вход идентификации разностей блока нерегулярной беспороговой дискретизации соединены с одноименными входами устройства, а информационные вход, выход блока регулярной дискретизации, информационный выход блока нерегулярной пороговой дискретизации и информационный вход блока нерегулярной беспороговой дискретизации, вход признака децимации блока нерегулярной пороговой дискретизации, а также вход признака децимации блока нерегулярной беспороговой дискретизации соединены соответственно с выходом вычитателя, информационным входом блока нерегулярной дискретизации, входом и выходом квантователя, с выходом признака децимации блока регулярной дискретизации, а также с выходом признака децимации блока нерегулярной пороговой дискретизации. Это позволяет повысить быстродействие и благодаря сочетанию эффектов адаптивной регулярной, адаптивной нерегулярной пороговой и адаптивной нерегулярной беспороговой дискретизации получать максимальное (среди предлагаемых вариантов устройства) повышение коэффициента сжатия данных.

Действия, выполняемые вариантами предлагаемого устройства, являются гибридом (сочетанием) той или иной разновидности адаптивной дискретизации (АД) и локального дифференциального кодирования (ЛДК) и поэтому далее именуются термином АД-ЛДК.

Во всех вариантах устройства функцию формирователя локальных центров может выполнять запоминающий регистр, причем вышеназванные два входа и выход формирователя являются одноименными входами и выходом этого регистра.

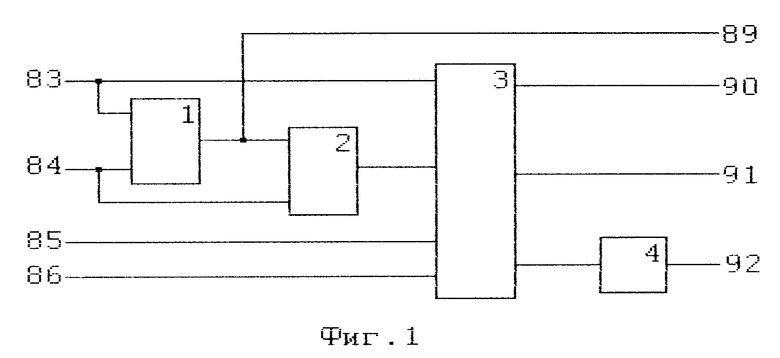

На фиг. 1 7 представлены блок-схемы первого-седьмого вариантов предлагаемого устройства для сжатия данных. на фиг. 8 10 представлены примеры блок-схем блоков адаптивной соответственно нерегулярной пороговой, нерегулярной беспороговой, регулярной дискретизации. на фиг. 11 12 представлены примеры блок-схем узла определения показателя детальности и узла выявления неполных серий.

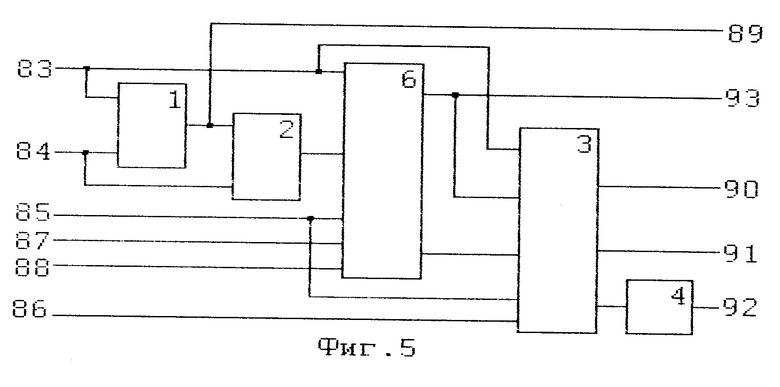

Первый вариант устройства для сжатия данных содержит формирователь 1 локальных центров, вычитатель 2, блок 3 адаптивной нерегулярной пороговой дискретизации, квантователь 4.

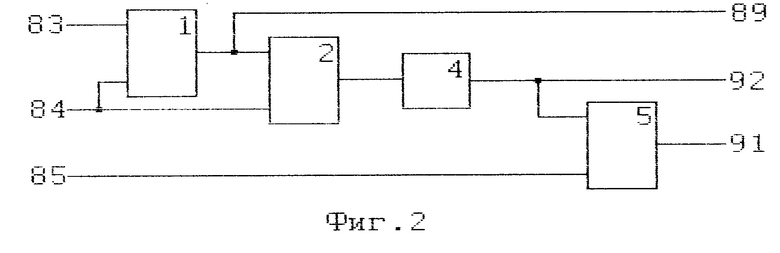

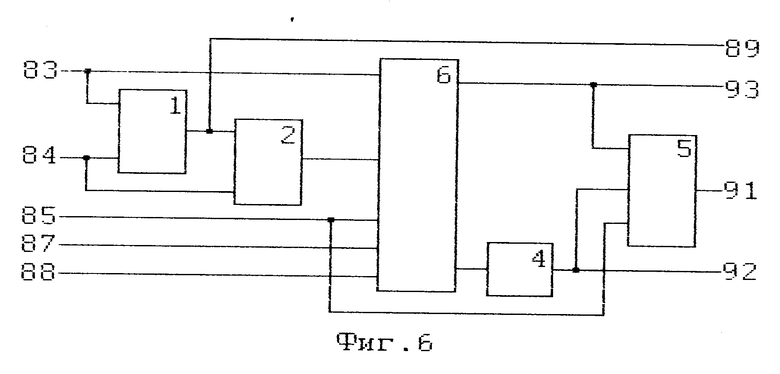

Второй вариант устройства содержит формирователь 1 локальных центров, вычитатель 2, квантователь 4, блок 5 адаптивной нерегулярной беспороговой дискретизации.

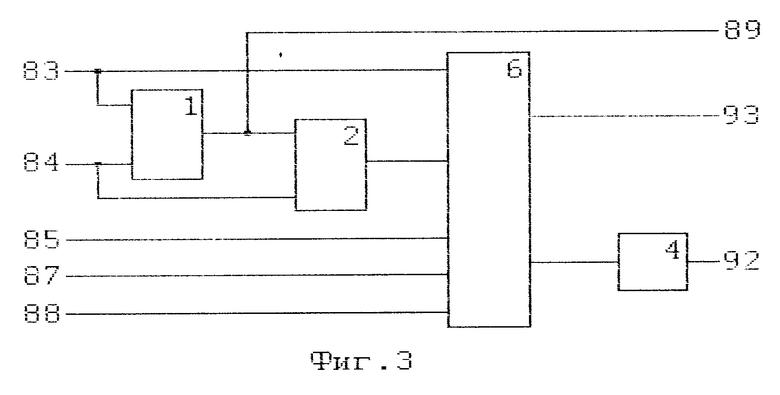

Третий вариант устройства содержит формирователь 1 локальных центров, вычитатель 2, квантователь 4, блок 6 адаптивной регулярной дискретизации.

Четвертый вариант устройства содержит формирователь 1 локальных центров, вычитатель 2, блок 3 адаптивной нерегулярной пороговой дискретизации, квантователь 4, блок 5 адаптивной нерегулярной беспороговой дискретизации.

Пятый вариант устройства содержит формирователь 1 локальных центров, вычитатель 2, блок 3 адаптивной нерегулярной пороговой дискретизации, квантователь 4, блок 6 адаптивной регулярной дискретизации.

Шестой вариант устройства содержит формирователь 1 локальных центров, вычитатель 2, квантователь 4, блок 5 адаптивной нерегулярной беспороговой дискретизации, блок 6 адаптивной регулярной дискретизации.

Седьмой вариант устройства содержит формирователь 1 локальных центров, вычитатель 2, блок 3 адаптивной нерегулярной пороговой дискретизации, квантователь 4, блок 5 адаптивной нерегулярной беспороговой дискретизации, блок 6 адаптивной регулярной дискретизации.

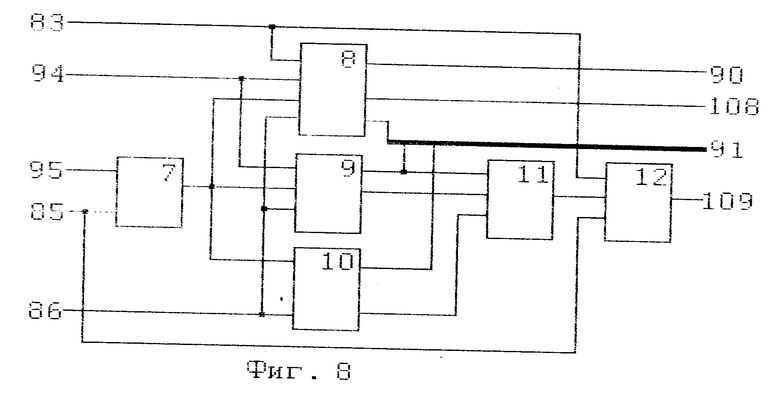

Блок 3 адаптивной нерегулярной пороговой дискретизации содержит, например, сдвиговый регистр 7, узел 8 выявления полной серии, узел 9 выявления предполной серии, узел 10 выявления неполных серий, коммутатор 11, сдвиговый регистр 12. В четвертом и седьмом вариантах устройства выход кода конфигурации блока 3 не используется, вход признака децимации блока 3 используется только в пятом и седьмом вариантах устройства, вход идентификации локальных центров узла 8 и выход признака децимации узла 8 и блока 3 используется только в седьмом варианте устройства.

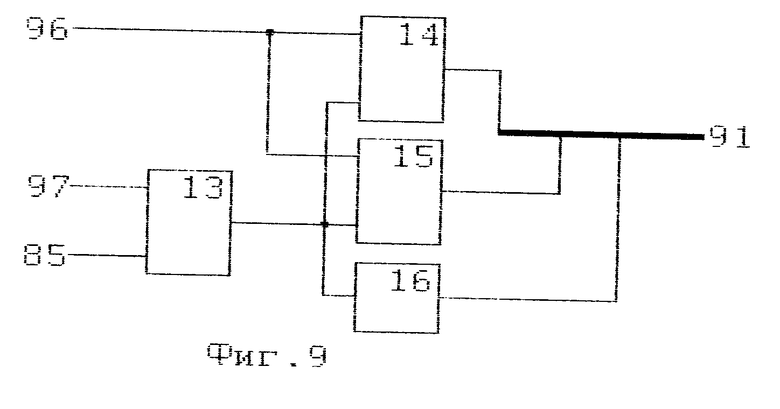

Блок 5 адаптивной нерегулярной беспороговой дискретизации содержит, например, сдвиговый регистр 13, узел 14 выявления полной серии, узел 15 выявления предполной серии, узел 16 выявления неполных серий. Вход признака децимации используется только в седьмом варианте устройства.

Блок 6 адаптивной регулярной дискретизации содержит, например, сдвиговый регистр 18, узел 19 определения показателя детальности, триггер 20, узел 21 децимации идентификаторов, сдвиговый регистр 22. Вход начальной установки блока 6 не является принципиально необходимым и может быть заменен, например, внутренней схемой выработки сигнала начальной установки триггера 21 по включению питающего напряжения.

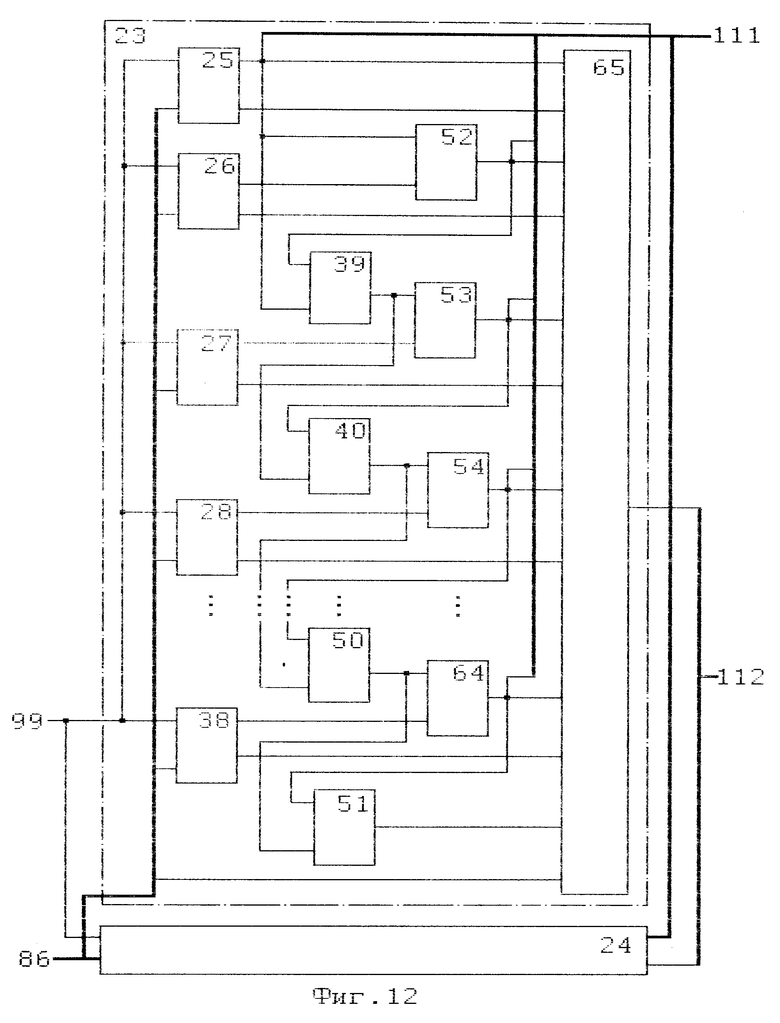

Узел 10 выявления неполных серий содержит, например, два модуля 23 и 24 определения конфигураций серий на четырех точках группы, каждый из которых содержит, например, схему 25 выявления серии из четырех разностей, схемы 26

29 выявления трехточечных серий, схемы 30 32 выявления двух двухточечных серий, схемы 33 38 выявления двухточечной серии и двух уникальных отсчетов, элементы 39 51 ИЛИ, элементы 52 64 запрета ("конъюнкция с одним запретом"), коммутатор 65. При этом модуль 25 соединен с разрядами 1 4 регистра 7, то есть оперирует с четырьмя разностями группы, модуль 26 соединен с разрядами 5 8 регистра 7, то есть оперирует с четырьмя другими разностями группы.

Узел 16 выявления неполных серий в отличие от узла 10 не имеет входа порога и оперирует с квантованными разностями, то есть с числами меньшей разрядности.

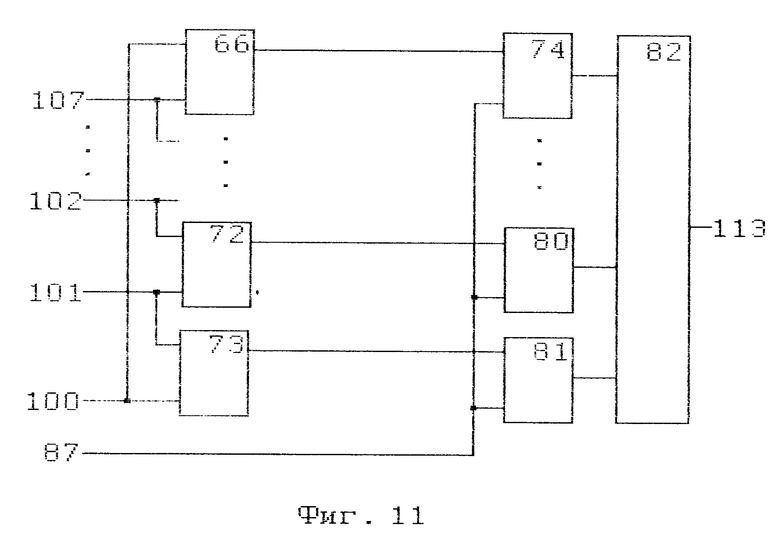

Узел 19 определения показателя детальности содержит, например, вычитатели 66 73, вычитатели 74 81, элемент 82 ИЛИ.

Узлы 8, 9, 14, 15 и схемы 25 38 выявления серий могут быть выполнены на основе сумматоров, вычитателей и элементов поразрядного сравнения типа содержащихся в интегральной микросхеме К 531 ЛП 5 П [5]

Входы устройства:

83 вход идентификации локальных центров,

84 информационный вход,

85 вход идентификации разностей,

86 вход порога нерегулярной дискретизации,

87 вход порога регулярной дискретизации,

88 вход начальной установки.

Выходы устройства:

89 выход локальных центров,

90 выход среднего значения разностей,

91 выход кода конфигурации,

92 информационный выход,

93 выход признака децимации.

Входы и выходы блоков, узлов, схем, являющиеся входами и выходами устройства, имеют номера входов и выходов устройства.

Остальные входы блоков 3, 5, 6 и узлов 10, 19:

94 вход признака децимации блока 3,

95 информационный вход блока 3,

96 вход признака децимации блока 5,

97 информационный вход блока 5,

98 информационный вход блока 6,

99 информационный вход узла 10,

100-107 информационные входы узла 19.

Остальные выходы блоков 3, 5, 6 и узлов 10, 19:

108 выход признака децимации блока 3,

109 информационный выход блока 3,

110 информационный выход блока 6,

111 выход кода конфигурации узла 10,

112 информационный выход узла 10,

113 выход узла 19.

Для конкретности работа устройства для сжатия данных рассматривается на примере двумерного сигнала с группами из 3x3 отсчетов, при этом сдвиговые регистры 7, 12, 13, 18, 24 содержат по восемь каскадов (групповых выходов).

Входные для устройства сигналы меняются по тактам (периодам времени) длительностью T.

В исходном состоянии всех вариантов устройства на их информационном входе 84, на входе 83 идентификации локальных центров, на входе 85 идентификации разностей и входе 88 начальной установки действуют сигналы логического "0", на входе 86 порога нерегулярной дискретизации и входе 87 порога регулярной дискретизации действуют коды заданных порогов, состояние выходов 89 92 может быть произвольным.

Первый вариант устройства для сжатия данных работает следующим образом.

В первом такте на информационный вход 84 устройства приходит (например, восьмиразрядный) код первого отсчета (локального центра группы) сигнала, поступающий далее на информационный вход формирователя 1 локальных центров. В это же время на вход 83 идентификации локальных центров устройства приходит импульс-идентификатор, который своим задним фронтом заносит в формирователь 1, действующий в это время на его информационном входе, код локального центра. С выхода формирователя 1 код локального центра поступает на вход вычитаемого вычитателя 2 и на выход 89 локальных центров устройства.

Во втором такте на информационный вход 84 устройства и вход уменьшаемого вычитателя 2 приходит код второго отсчета группы. Из кода второго отсчета вычитатель 2 вычитает код локального центра, действующий на его входе вычитаемого. С выхода вычитателя 2 девятиразрядный код полученной разности поступает на информационный вход блока 3 адаптивной нерегулярной пороговой дискретизации. Приходящий в этом же такте на вход 85 устройства импульс-идентификатор разностей поступает на одноименный вход блока 3 и заносит в него своим задним фронтом названный код разности.

В третьем-девятом тактах вышеописанным образом вычисляются и заносятся (накапливаются) в блок 3 разности между третьим-девятым отсчетами группы и ее локальным центром. Над восемью накопленными разностями группы блок 3 нерегулярной пороговой дискретизации выполняет в девятом такте следующие действия:

вычисляет среднее для группы значение разностей и выдает его на одноименные свой выход и выход 90 устройства;

определяет максимальные модули различий между разностями, входящими в различные их сочетания;

сравнивает максимальные модули различий с действующим на входе 86 устройства и соответствующем входе блока 3 порогом нерегулярной дискретизации: если эти модули не превышают порога, соответствующие сочетания разностей идентифицируется как серии одинаковых значений, равных среднему значению входящих в серию разностей; при этом разности, не вошедшие в серии, представляются своими исходными индивидуальными (уникальными) значениями;

выбирает из возможных серий и индивидуальных значений разностей такую их совокупность (конфигурацию), которая минимизирует объем данных, представляющих группу отсчетов, и по импульсу-идентификатору локальных центров следующей группы, приходящему на вход 83 устройства в десятом такте, начинает выдачу на свой информационный выход кодов разностей соответственно принятой конфигурации;

формирует код выбранной конфигурации, например унитарный в виде набора признаков серий, образующих конфигурацию, и выдает этот код на свой выход кода конфигурации и выход 91 устройства.

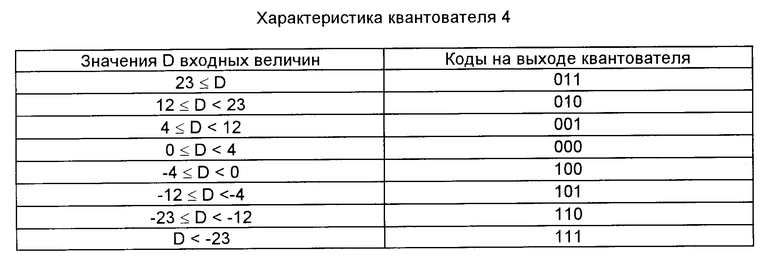

С информационного выхода блока 3 в следующих восьми тактах коды разностей поступают на вход квантователя 4 с нелинейной амплитудной характеристикой и преобразовываются в нем, например, соответственно таблице.

С выхода квантователя трехразрядные коды разностей поступают на информационный выход 92 устройства.

В десятом восемнадцатом тактах производится обработка второй группы из девяти отсчетов, совпадающая с вышеописанной обработкой отсчетов первой группы.

Такая обработка групп отсчетов продолжается, пока на информационный вход 34 и входы 83, 85 идентификации поступают вышеописанные последовательности кодов отсчетов сигнала и импульсов идентификации локальных центров и разностей. С прекращением этих последовательностей устройство переходит в исходное состояние.

Во втором седьмом вариантах устройства формирование и выдача локальных центров на выход 89 устройства, формирование разностей на выходе вычитателя 2, переход устройства в исходное состояние происходят вышеописанным образом.

Во втором варианте устройства получаемые во втором-девятом тактах на выходе вычитателя 2 девятиразрядные разности поступают на вход квантователя 4 и после вышеописанного преобразования в нем в виде трехразрядных кодов поступают на информационные выход 92 устройства и вход блока 5 адаптивной нерегулярной беспороговой дискретизации и заносятся (накапливаются) в него импульсами идентификации разностей, поступающими со входа 85 устройства на вход идентификации разностей блока 3.

Над восемью накопленными разностями блок 5 нерегулярной беспороговой дискретизации выполняет в девятом, восемнадцатом, тактах следующие действия:

выявляет различные сочетания одинаковых значений (кодов) разностей и идентифицирует их как серии определенной длины;

выбирает из возможных серий и индивидуальных значений разностей такую их совокупность (конфигурацию), которая минимизирует объем данных, представляющих группу отсчетов, формирует код выбранной конфигурации, например унитарный в виде набора признаков серий, образующих конфигурацию, и выдает этот код на свой выход кода конфигурации и выход 91 устройства.

В третьем варианте устройства получаемые во втором-девятом тактах на выходе вычитателя 2 разности поступают на информационный вход блока 6 адаптивной регулярной дискретизации и заносятся (накапливаются) в него импульсами-идентификаторами разностей, поступающими со входа 85 устройства на вход идентификации разностей блока 6.

Над восемью накопленными разностями блок 6 адаптивной регулярной дискретизации выполняет в девятом, восемнадцатом, тактах следующие действия:

определяет модуль скорости изменения сигнала посредством вычисления модулей разностей между соседними отсчетами группы, окружающими ее локальный центр;

сравнением модулей разности с порогом адаптивной регулярной дискретизации, поступающим на вход порога блока 6 со входа 87 устройства, определяет показатель детальности сигнала (признак детальности принимается равным логической "1", если хотя бы один модуль разности превышает порог, и равным логическому "0" в противном случае).

По импульсу идентификации локальных центров следующей группы (в десятом, девятнадцатом, тактах) блок 6 выдает признак детальности в инверсном виде (как признак децимации) через одноименный свой выход на выход 93 устройства, а также подготавливает разности к выдаче на свой информационный выход.

В одиннадцатом-восемнадцатом, двадцатом-двадцать седьмом, тактах (то есть в тактах следующей группы по отношению к накапливаемым в блоке 6 разностям) блок 6 по импульсам идентификации разностей, поступающим со входа 85 устройства, производит выдачу накопленных разностей предыдущей группы в соответствии с выданным ранее на выход 93 устройства признаком децимации: при "нулевом" признаке децимации все восемь полученных блоком 6 разностей выдаются на информационный выход блока 6, при "единичном" признаке децимации на этот выход выдаются четыре из восьми полученных блоком 6 разностей, причем по первой, третьей, пятой, группам (после сигнала начальной установки, приходящего на вход 88 устройства и одноименный вход блока 6 в первом такте) выдаются первая, третья, пятая, седьмая разности, а по четным группам - вторая, четвертая, шестая, восьмая разности, что дает "шахматную" структуру прореженных отсчетов. Одновременно с выдачей разностей на информационный выход блока 6 производятся прием и накопление в нем разностей следующей группы.

С информационного выхода блока 6 коды разностей поступают на вход квантователя 4 и после вышеописанного преобразования в виде трехразрядных кодов поступают с его выхода на информационный выход 92 устройства.

В четвертом варианте устройства разности с выхода вычитателя 2 вышеописанным образом накапливаются в блоке 3 адаптивной нерегулярной пороговой дискретизации и после обработки в нем и в квантователе 4 поступают на информационный вход блока 5, среднее значение разностей выдается на выход 90 устройства. Получаемые с выхода квантователя 4 разности по импульсам идентификации со входа 85 устройства вышеописанным образом накапливаются и обрабатываются в блоке 5 адаптивной нерегулярной беспороговой дискретизации, в результате чего с выхода блока 5 на выход 91 устройства выдается код конфигурации.

В пятом варианте устройства разности с выхода вычитателя 2 вышеописанным образом накапливаются в блоке 6 адаптивной регулярной дискретизации и после обработки в нем задают значение признака децимации на выходе 93 устройства и преобразованные разности на информационном входе блока 3 адаптивной нерегулярной пороговой дискретизации. С информационного входа блока 3 разности вышеописанным образом накапливаются в нем и после обработки дают на выходах 90 и 91 устройства соответственно среднее значение разностей и код конфигурации, а на входе квантователя 4 преобразованные значения разностей, которые после вышеописанного квантования поступают на информационный выход 92 устройства.

В шестом варианте устройства разности с выхода вычитателя 2 последовательно поступают в блок 6 адаптивной регулярной дискретизации, квантователь 4, блок 5 адаптивной нерегулярной беспороговой дискретизации и после вышеописанной обработки в них дают признак децимации, код конфигурации и трехразрядные коды разностей соответственно на выходах 93, 91, 92 устройства.

В пятом и шестом вариантах устройства для обработки разностей в блоках 3 и 5 согласованно с выполнением или невыполнением децимации в блоке 6 признак децимации с одноименного выхода блока 6 выдается на входы признака децимации блоков 3 и 5.

В седьмом варианте устройства разности с выхода вычитателя 2 последовательно поступают в блок 6 адаптивной регулярной децимации, блок 3 адаптивной нерегулярной пороговой дискретизации, квантователь 4, блок 5 адаптивной нерегулярной беспороговой дискретизации и после вышеописанной обработки в них дают признак децимации, среднее значение разностей, код конфигурации и трехразрядные коды разностей соответственно на выходах 93, 90, 91, 92 устройства. При этом признак децимации, задержанный в блоке 3 соответственно задержке в нем обработанных разностей, с выхода признака децимации блока 3 выдается на одноименный вход блока 5. Это обеспечивает обработку разностей в блоке 5, согласованную с их обработкой в блоке 3.

Блок 3 адаптивной нерегулярной пороговой дискретизации работает следующим образом.

Девятиразрядные коды разностей с информационного входа 95 блока 3 поступают на информационный вход сдвигового регистра 7 и заносятся в него по задним фронтам импульсов идентификации, поступающих на синхровход регистра 7 со входа 85 блока. После окончания импульса-идентификатора девятого в группе такта в регистре 7 накоплены восемь кодов разностей. С выхода регистра 7 эти коды параллельно поступают на информационные входы узлов 8, 9 и 10 выявления соответственно полной, предполной и неполных серий, на входах порога которых действуют поступающий со входа 86 порога блока 3 порог адаптивной нерегулярной пороговой дискретизации, а на управляющих входах узлов 8, 9 признак децимации, приходящий с одноименного входа 94 блока 3.

Узел 8 при "нулевом" значении признака децимации вычисляет среднее по группе значение разностей и выдает его на одноименные свой выход и выход 90 блока 3, по переднему фронту импульса идентификации локальных центров запоминает признак децимации на время до следующего импульса идентификации локальных центров и выдает этот запомненный признак на одноименные свой выход и выход 108 блока 3, а также вырабатывает признак полной серии (серии из девяти точек группы): если модули разностей между максимальным и минимальным значениями восьми накопленных разностей, а также нулем (нуль соответствует локальному центру) не превышает порога, признак полной серии принимается равным логической "1", в противном случае равным логическому "0". Признак полной серии с одноименного выхода узла 8 поступает на групповой (векторный) выход 91 конфигурации блока 3 (по отдельной линии). При "единичном" значении признака децимации признак полной серии и среднее по группе значение разностей вычисляются по четырем разностям, пришедшим в регистр 7 первыми.

Узел 9 при "нулевом" значении признака децимации вычисляет среднее значение восьми накопленных разностей и через свой одноименный выход выдает его на первый вход коммутатора 11, а также вырабатывает признак предполной серии (серии из восьми точек, окружающих локальный центр группы): если модуль разности между максимальным и минимальным значениями восьми накопленных разностей не превышает порога, признак предполной серии принимается равным логической "1", в противном случае равным логическому "0". Признак предполной серии с одноименного выхода узла 9 поступает на выход 91 конфигурации блока 3 (по отдельной линии) и на второй вход коммутатора 11. При "единичном" значении признака децимации признак предполной серии и среднее значение разностей определяются по четырем разностям, пришедшим в регистр 7 первыми.

Узел 10 выявления неполных серий аналогично вышеописанному выявляет на совокупности из восьми разностей неполные серии (включающие в себя меньше восьми разностей), формирует признаки соответственно выявленным сериям и для каждой серии вычисляет среднее значение входящих в нее отсчетов. Коды средних значений входящих в серии отсчетов и коды уникальных разностей (не вошедших в серии) из узла 10 через его информационный выход поступают на третий вход коммутатора 11, а признаки неполных серий по группе линий поступают на выход 91 кода конфигурации блока 3. Более подробно работа узла 10 выявления неполных серий описывается ниже.

Коммутатор 11 при сигнале логической "1" на его втором входе передает на свой выход код среднего значения с первого входа, а при сигнале логического "0" коды средних значений для неполных серий и/или коды уникальных разностей (при отсутствии серий общее число кодов разностей равно восьми).

С выхода коммутатора 11 коды разностей поступают на информационный вход сдвигового регистра 12 и заносятся в него задним фронтом первого Б следующей группе импульса-идентификатора разностей, поступающего на синхровход регистра 12 со входа идентификации разностей блока 3. Занесение в регистр 12 при этом происходит благодаря действию в это время импульса-идентификатора локальных центров, поступающего с одноименного входа 83 блока 3. Следующие восемь идентификаторов разностей благодаря отсутствию в это время идентификаторов локальных центров по своим задним фронтам производят сдвиг кодов разностей в регистре 12, при этом с выхода регистра 12 эти коды последовательно выдаются на информационный выход 109 блока 3.

Блок 5 адаптивной нерегулярной беспороговой дискретизации работает следующим образом.

Трехразрядные коды разностей с информационного входа 97 блока 5 поступают на информационный вход сдвигового регистра 13 и заносятся в него по задним фронтам импульсов идентификации разностей, поступающих на синхровход регистра 13 со входа 85 блока 5. После окончания импульса-идентификатора девятого в группе такта в регистре 13 накоплены восемь кодов разностей. С выхода регистра 13 эти коды параллельно поступают на информационные входы узлов 14, 15, 16 выявления соответственно полной, предполной и неполных серий, на управляющих входах узлов 14 и 15 при этом действует признак децимации, приходящий с одноименного входа 96 блока 5.

Узел 14 вырабатывает (сравнением разностей) признак полной серии: если коды всех анализируемых разностей равны нулю, признаку присваивается значение логической "1", в противном случае значение логического "0". При этом, если признак децимации равен логическому "0", анализируются все восемь разностей, в противном случае четыре разности, которые приходят в регистр 13 первыми.

Узел 15 вырабатывает (сравнением разностей) признак предполной серии: если коды всех анализируемых разностей одинаковы, признаку присваивается значение логической "1", в противном случае значение логического "0". При этом, если признак децимации равен логическому "0", анализируются все восемь разностей, в противном случае четыре разности, пришедшие в регистр 13 первыми.

Узел 16 выявления неполных серий аналогично вышеописанному (сравнением разностей) формирует признаки выявленных неполных серий. Работа узла 16 выявления неполной серий описана ниже.

Признаки полной, предполной и неполных серий с выходов соответственно узлов 14, 15 и 16 выдаются по отдельным линиям на (групповой) выход 91 кода конфигурации блока 5.

В первом, втором, четвертом вариантах устройства блоки 3 и 5 нерегулярной дискретизации не имеют входа признака децимации и их работа соответствует вышеописанной при "нулевом" значении этого признака.

Блок 6 адаптивной регулярной дискретизации работает следующим образом.

Девятиразрядные коды разностей с информационного входа 98 блока 6 поступают на информационный вход сдвигового регистра 18 и заносятся в него задними фронтами импульсов идентификации разностей, поступающих с одноименного входа 85 блока 6 на синхровход регистра 18. После окончания девятого в группе такта в регистре 18 накоплены восемь кодов разностей, которые с восьми его выходов поступают на восемь входов узла 19 определения показателя детальности, а с восьмого выхода (выхода, на который накапливаемые разности проходят с максимальной задержкой) также на информационный вход сдвигового регистра 22. При этом на девятом входе узла 19 действует порог регулярной дискретизации, приходящий с одноименного входа 87 блока 6.

Узел 19 определяет показатель детальности и через свой выход выдает его на информационный вход триггера 20. В первом такте следующей группы идентификатор локальных центров, поступающий с одноименного входа 83 блока 6 на синхровход триггера 20, своим задним фронтом заносит в него показатель детальности, который с выхода триггера 20 в инверсном виде как признак децимации выдается на одноименный выход 93 блока 6, на управляющий вход регистра 22 и на первый вход узла 21 децимации идентификаторов.

Признак децимации, поступающий на управляющий вход регистра 22, задает прохождение через него кодов разностей с информационного входа: при "нулевом" значении признака децимации разности поступают на вход первой половины регистра 22, что обеспечивает их прохождение на выход регистра 22 и информационный выход 110 блока 6 через восемь импульсов на его синхровходе; при "единичном" значении признака децимации разности поступают на вход второй половины регистра 22, что обеспечивает их прохождение на выход регистра 22 и информационный выход 110 блока 6 через четыре импульса на его синхровходе.

На второй, третий и четвертый входы узла 21 приходят с соответствующих входов 83, 85, 88 блока 6 идентификатор локальных центров, идентификатор разностей и сигнал начальной установки. При "нулевом" значении признака децимации на выход узла 21, а с него на синхровход сдвигового регистра 22 проходят второй девятый задержанные импульсы идентификации группы (прохождение первого блокируется идентификатором локальных центров). При "единичном" значении признака децимации на выход узла 21 проходят поочередно (на последовательности групп отсчетов сигнала) то четные, то нечетные (начиная со второго) импульсы-идентификаторы разностей. Сигнал начальной установки, приходящий в первом такте первой группы (после исходного состояния) задает начало работы с прохождения на выход узла 21 в первой группе четных импульсов-идентификаторов. Эти импульсы своими задними фронтами заносят (сдвигают) в регистр 22 разности, приходящие на его информационный вход с восьмого выхода регистра 18 в процессе его загрузки разностями следующей группы. Таким образом, в регистр 22 загружаются, а в тактах следующей группы и выдаются с его выхода на информационный выход 110 блока 6:

восемь разностей группы при "нулевом" признаке децимации;

четыре четные (по номеру в группе) или четыре нечетные разности при "единичном" признаке децимации.

Узел 19 определения детальности работает следующим образом.

Коды разностей с восьмого, седьмого, первого входов 107, 106, 100 узла 19 поступают на входы вычитаемого вычитателей соответственного 66, 67,73 и на входы уменьшаемого вычитателей соответственно 67, 68,73, 66. С выхода вычитателей 66 73 модули полученных разностей поступают на входы вычитаемого вычитателей соответственно 74 81, на входах уменьшаемого которых действует порог адаптивной регулярной децимации, приходящий с одноименного входа 87 узла 19. Знаки полученных разностей поступают на входы элемента 82 ИЛИ, причем знак разностей равен логической "1", если модуль разности больше порога. В итоге, признак детальности на выходе элемента 82 и выходе 113 узла 19 равен логической "1", если хотя бы одна разность между соседними разностями группы по модулю превосходит порог, и логическому "0" в противном случае.

Узел 10 выявления неполных серий работает следующим образом.

Четыре соседних разности (из восьми) с информационного входа 99 узла 10 поступают на информационный вход модуля 23; другие четыре на информационный вход модуля 24. Код порога с соответствующего входа 86 узла 10 поступает на входы порога обоих модулей 23 и 24.

Со входа каждого модуля код порога поступает одновременно на входы порога всех схем 25 38 выявления различных серий. Коды разностей со входа модуля поступают:

все четыре на первый вход коммутатора 65, на информационный вход схемы 25 выявления четырехточечной серии и на информационные входы схем 30 32 выявления двух двухточечных серий;

в различных сочетаниях на информационные входы схем 26 29 и 33 38 выявления остальных серий.

Соответственно сочетаниям из четырех по три разности поступают на информационные входы схем 26 29 выявления трехточечных серий и сочетаниям из четырех по два на информационные входы схем 33 38 выявления одиночных двухточечных серий.

Каждая из схем 25 38 вышеописанным образом проверяет наличие серии одного вида и со своего выхода признака серии через систему элементов 39 64 (схема 25 непосредственно) выдает признак серии на выход конфигурации модуля (по отдельной линии) и соответствующий управляющий вход коммутатора 65, а со своего информационного выхода непосредственно на соответствующий информационный вход коммутатора 65 среднее значение входящих в серию разностей.

Нумерация схем 25 38 произведена в порядке невозрастания предпочтительности соответствующих серий или, что то же самое, неубывания затрат на кодирование конфигураций (адаптивную нерегулярную дискретизацию) четырех разностей. Поэтому каждый признак серии (при его "единичном" значении) с выхода схемы из 25 38 с меньшим номером запрещает прохождение признаков серий с выходов этих элементов с большими номерами для чего признаки серий с выходов схем 26 38 подаются на информационные входы элементов 52 64 запрета, а запрещающие сигналы последовательно собираются на цепочке элементов 39 51 ИЛИ, с выходов которых накопленные признаки наличия серий поступают на входы запрета элементов 53 64. В результате при любых значениях четырех разностей сигнал логической "1" присутствует только на одном управляющем входе коммутатора 65. При этом сигнал логической "1" на управляющем входе, соединенном с выходом элемента 51 ИЛИ, означает отсутствие каких-либо серий в четырех разностях.

Коммутатор 65 пропускает на свой выход и информационный выход модуля коды с того информационного входа, на соответствующем управляющем входе которого действует сигнал логической "1": при логической "1" на выходе элемента 51 коммутатор 65 пропускает на свой информационный выход коды со своего первого информационного входа, то есть коды всех четырех разностей; при логической "1" на другом управляющем входе коммутатора 65 через него проходят исходные коды уникальных (не входящих в серии) разностей, а коды разностей, входящих в серии, заменяются их средними значениями, поступающими на соответствующий информационный вход с информационного выхода соответствующей схемы из 25 38.

Сигналы с информационных выходов и выходов кодов конфигурации модулей 23 и 24 объединяются на одноименных групповых выходах 112 и 111 узла выявления неполных серий.

Узел 16 выявления неполных серий оперирует с трехразрядными кодами разностей, выявляет наличие серий сравнением разностей на совпадение (равенство). В остальном работа узла 16 совпадает с работой узла 10 выявления неполных серий.

Согласно групповому характеру сжатия данных вариантами предлагаемого устройства, кратковременные нарушения структуры входных для устройства сигналов или работоспособности устройства приводят к потере только тех участков сигнала, которым соответствуют группы отсчетов, приходящиеся по времени на эти аномалии.

Работоспособность каждого варианта устройства обеспечивается при Топ < Т + Т 1 Т 2, где Т длительность такта, Т 1 длительность импульса идентификатора локальных центров, Т 2 длительность импульсов идентификации разностей. Топ суммарная задержка (время выполнения операций) в каждом использованном в варианте устройства блоке из 3, 5, 6 адаптивной дискретизации и соединенном с его информационным выходом квантователе 4 (если такое соединение есть). Для повышения быстродействия устройства продолжительность девятого такта каждой группы может быть больше продолжительности остальных тактов.

Сущность изобретения не изменяется при перераспределении функций между блоками устройства, при включении в его состав средств упаковки данных, средств энтропийного кодирования, средств синхронизации (например, привязки данных к началу строки изображения), средств деления отсчетов сигнала на группы, уравнивающего (сглаживающего) буфера, при включении признака децимации в состав кода конфигурации.

Передаче и/или хранению подлежат следующие данные с выхода устройства (если они формируются в данном его варианте): код конфигурации, признак децимации, код локального центра, выход среднего значения разностей (при "единичном" значении признака полной серии), коды разностей с информационного выхода устройства (в составе, соответствующем набору признаков серий в коде конфигурации).

Восстановление отсчетов по "сжатым" данным определяется вышеописанной процедурой их формирования.

Наибольший эффект предлагаемое устройство для сжатия данных методом АД-ЛДК дает при его применении в системах передачи и/или хранения данных для сжатия многомерных сигналов, когда каждая обрабатываемая группа отсчетов является, например, гиперкубом с центром в качестве первого отсчета группы.

Благодаря устранению предсказателя варианты предлагаемого устройства характеризуются примерно двукратным повышением быстродействия по сравнению с прототипом.

При сжатии уже двумерных сигналов (изображений) группами из 3x3 9 отсчетов предлагаемое устройство позволяет достигать сжатия данных с расходом от 1,2 1,4 бит на отсчет в первых трех вариантах устройства до 0,9 1,1 бит на отсчет в седьмом варианте устройства, что соответствует увеличению коэффициента сжатия в 1,4 1,8 раза по сравнению с прототипом.

Использованная литература

1. Тарасенко Ф.П. Введение в курс теории информации. Томск: Изд. Томского университета, 1963, с. 182.

2. Милт Леонард. Схема, реализующая алгоритм сжатия неподвижных объектов. "Электроника", N 10; 1991, с. 20.

3. Патент США N 4. 179. 710, кл. 358 135 (H 04 N 5/40), 1979.

4. Патент США N 4. 481. 644, кл. 375 27 (H 04 N 7/12), 1984.

5. Тарабрин Б.В. Лукин Л.Ф. Смирнов Ю.Н. и.др. Интегральные микросхемы. Справочник. Под ред. Б.В. Тарабарина. М. "Радио и связь", 1984, с. 253.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЖАТИЯ ДАННЫХ (ВАРИАНТЫ) | 1994 |

|

RU2093957C1 |

| УСТРОЙСТВО ДЛЯ СЖАТИЯ ДАННЫХ | 1993 |

|

RU2057396C1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1998 |

|

RU2141737C1 |

| Цифровая многоканальная сейсмостанция | 1980 |

|

SU1000972A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Способ адаптивной временной дискретизации и устройство для его осуществления | 1983 |

|

SU1095390A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2586605C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| Устройство для многоуровневой дельта - модуляции | 1988 |

|

SU1674377A1 |

Использование: изобретение относится к области сокращения информационной избыточности, а именно, для сжатия данных, представлявших многомерные сигналы. Сущность изобретения: устройство для сжатия данных ( варианты) содержит формирователь кодов 1 локальных центров, вычитатель 2, блок 3 адаптивной нерегулярной пороговой дискретизации, квантователь 4, блок 5 адаптивной регулярной дискретизации, блок адаптивной нерегулярной дискретизации. Изобретение позволяет повысить быстродействие и коэффициент сжатия данных. 7 с.п. ф-лы, 1 табл., 12 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| US, патент, 4179710, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| US, патент, 4481644, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1997-10-20—Публикация

1994-09-20—Подача