Предлагаемое устройство относится к области дискретной обработки сигналов и, в первую очередь, к области обработки сигналов с целью повышения разрешения их элементов, в том числе в случаях экономных хранения и передачи дискретных данных.

Известны [1] устройства для дискретной обработки сигналов, содержащие последовательно соединенные фильтр низких частот (ФНЧ), дискретизатор и блок реставрации сигналов методом Монте-Карло, обеспечивающие не ограниченные полосой частот крутизну перепадов и расстояние разрешения. Недостатком таких устройств является низкая вероятность соответствия реставрированного сигнала входному, поскольку принцип их действия базируется на интегральной информации о сигнале (энергия), причем не входном для устройства, а входном для блока реставрации.

Известны [2] устройства для дискретной обработки сигналов, содержащие последовательно соединенные ФНЧ, дискретизатор и оптимальный восстанавливающий фильтр, обеспечивающие при гауссовом шуме минимальную среднеквадратичную ошибку восстановления. Недостатком этих устройств является недостаточное разрешение элементов сигналов.

От этого недостатка свободны устройства [3] для дискретной обработки сигналов, содержащие последовательно соединенные ФНЧ, дискретизатор и интерполятор и обеспечивающие разрешение сигнала, близкое к максимально возможному при данной ширине частотной полосы пропускания ФНЧ.

Однако и эти устройства имеют недостаток, состоящий в высоком уровне осцилляций (паразитных осцилляций, "хвостов", боковых лепестков) за пределами подлежащих разрешению элементов входного сигнала и пониженном контрасте элементов и групп элементов малой протяженности, что обусловлено восстановлением элементов малой протяженности по их спектру в предельно узкой полосе частот.

С другой стороны, известны (например, [4]) устройства для дискретной обработки сигналов, содержащие последовательно соединенные ФНЧ, дискретизатор и интерполятор, в которых, благодаря представлению сигналов в базисе сфероидальных волновых функций, верхняя частота гармонического спектра сигнала может превышать половину частоты дискретизации, что позволяет использовать этот дополнительный ресурс для некоторого понижения уровня паразитных осцилляций и повышения разрешения. Однако и эти устройства имеют недостаток, состоящий в недостаточно пониженном уровне паразитных осцилляций и в низком контрасте малопротяженных элементов сигнала.

Заявляемое изобретение направлено на уменьшение уровня паразитных осцилляций и на повышение контраста элементов сигнала.

Решение этой задачи обеспечивает:

повышение разрешения, при котором обеспечивается практическая возможность анализа на выходе устройства сигналов, являющихся суперпозицией множества элементов, в том числе предельно разрешаемых;

уменьшение объема данных, подлежащих хранению и/или передаче с последующим обеспечением заданного разрешения.

Для этого (в первом варианте предлагаемого устройства) в устройство для дискретной обработки сигналов, содержащее последовательно соединенные ФНЧ, вход которого является входом устройства, и дискретизатор, дополнительно вводится блок редукции устройства к квазисовершенному, вход которого соединен с выходом дискретизатора, а выход является выходом устройства. Это позволяет выполнять квазисовершенное восстановление элементов сигнала вплоть до предельно разрешаемых, в результате чего сигнал на выходе устройства является суммой двух компонент:

компоненты, являющиеся реакцией существенно более широкополосной системы (вплоть до совершенной [4]) на разрешаемые элементы входного сигнала; компоненты из неразрешаемых предлагаемым устройством групп элементов входного сигнала. Такие группы элементов при анализе выходного сигнала воспринимаются как более протяженные одиночные сигналы.

В известных устройствах первая компонента выходного сигнала отсутствует, а свойственные им реакции на соответствующие элементы входного сигнала относятся частично к группе дающих затянутые фронты и большие осцилляции, частично - к группе неразрешаемых этими устройствами элементов (последнее обусловливает более низкое разрешение известных устройств).

Наличие второй компоненты в выходном сигнале предлагаемого устройства обусловлено, как и всегда, ограниченностью частотной полосы пропускания ФНЧ и наличием шумов.

Далее устройства, имеющие такой двухкомпонентный состав выходного сигнала, будем называть квазисовершенными (по аналогии с совершенными системами [4] ), а использование в их составе и работе блока, обеспечивающего такой состав выходного сигнала, - редукцией устройства к квазисовершенному.

Второй вариант предлагаемого устройства состоит в том, что в устройство для дискретной обработки сигналов, содержащее последовательно соединенные фильтр низких частот, вход которого является входом устройства, и дискретизатор, дополнительно вводится блок редукции устройства к квазисовершенному, вход которого соединен с выходом дискретизатора, а выход является выходом устройства, причем блок редукции устройства к квазисовершенному содержит последовательно соединенные интерполирующий узел, вход которого является входом блока редукции устройства к квазисовершенному, синтезатор сокращенного описания сигнала и квазисовершенный корректор, второй вход которого соединен с выходом интерполирующего узла, а выход является выходом блока редукции устройства к квазисовершенному.

Это позволяет (благодаря интерполирующему узлу) формировать детальное представление обрабатываемого сигнала вплоть до мельчайших подлежащих разрешению элементов, посредством синтезатора сокращенного описания определять по сигналу на его входе примерное положение перепадов во входном для устройства сигнале и уровни этого сигнала после каждого перепада и на этой основе формировать начальное сокращенное описание входного сигнала, а посредством квазисовершенного корректора на основе сравнения выходных реакций одинаковых ФНЧ на входной и на синтезированный сигналы производить коррекцию местоположения перепадов, крутизны перепадов и уровней после каждого перепада, приближая синтезированный сигнал к реальному входному и тем самым получая квазисовершенную реакцию устройства на входной сигнал.

Третий вариант предлагаемого устройства состоит в том, что в устройство для дискретной обработки сигналов, содержащее последовательно соединенные фильтр низких частот, вход которого является входом устройства, и дискретизатор, дополнительно введен блок редукции устройства к квазисовершенному, вход которого соединен с выходом дискретизатора, а выход является выходом устройства, причем блок редукции устройства к квазисовершенному содержит последовательно соединенные интерполирующий узел, вход которого является входом блока редукции устройства к квазисовершенному, синтезатор сокращенного описания сигнала и квазисовершенный корректор, второй вход которого соединен с выходом интерполирующего узла, а выход является выходом блока редукции устройства к квазисовершенному, синтезатор сокращенного описания сигнала содержит последовательно соединенные определитель местоположения перепада и узел памяти, второй вход которого соединен со вторым выходом и со входом определителя местоположения перепада, который является входом синтезатора сокращенного описания сигнала, выходом которого является выход узла памяти, а квазисовершенный корректор содержит последовательно соединенные коммутатор, вход которого является первым входом квазисовершенного корректора, формирователь сигнала по сокращенному описанию, второй фильтр низких частот, вычитатель и корректор сокращенного описания, выход которого соединен со вторым входом коммутатора и является выходом квазисовершенного корректора, при этом второй вход корректора сокращенного описания соединен с выходом коммутатора, а второй вход вычитателя является вторым входом квазисовершенного корректора.

Это позволяет по характерным участкам сигнала на выходе интерполирующего узла определять координату перепада, а задержав относительно момента перепада подачу импульса записи на синхровход (первый вход) узла памяти, указывать для записи в узел памяти (вместе с координатой перепада) уровень сигнала на втором его входе, соответствующий моменту достаточного завершения переходного процесса после перепада и тем самым формировать в синтезаторе начальное сокращенное описание сигнала, а в квазисовершенном корректоре формировать полный (поточечный) сигнал по сокращенному описанию, пропускать этот сигнал через второй ФНЧ, получать на выходе вычитателя разность реакций одинаковых ФНЧ на реальный входной и синтезированный сигналы, корректировать на основе этого разностного сигнала начальное сокращенное описание и (благодаря наличию коммутатора в составе квазисовершенного корректора) повторять коррекцию сокращенного описания необходимое число раз до получения достаточного приближения синтезированного сигнала к реальному входному.

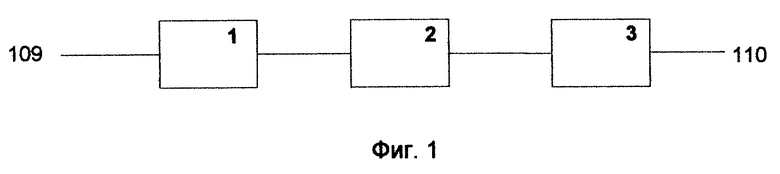

На фиг. 1, представлена блок-схема предлагаемого устройства для дискретной обработки сигналов по п.1 формулы изобретения.

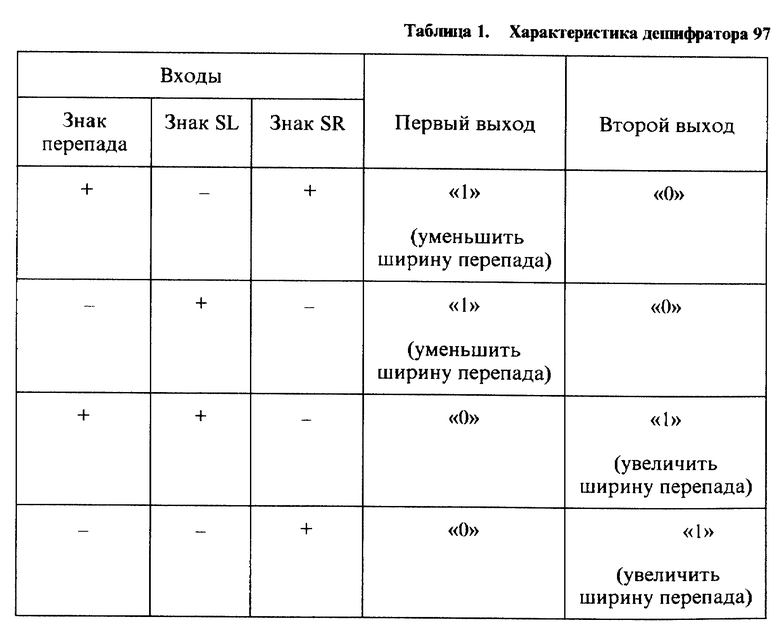

На фиг. 2 представлена блок-схема блока редукции устройства к квазисовершенному в составе устройства для дискретной обработки сигнала по п. 2 формулы изобретения.

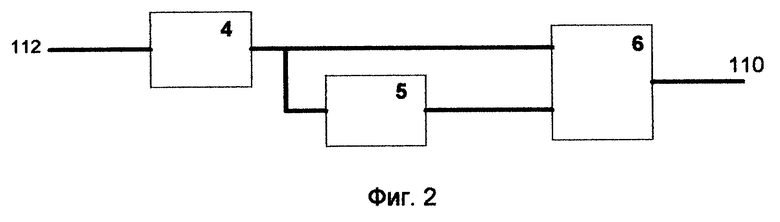

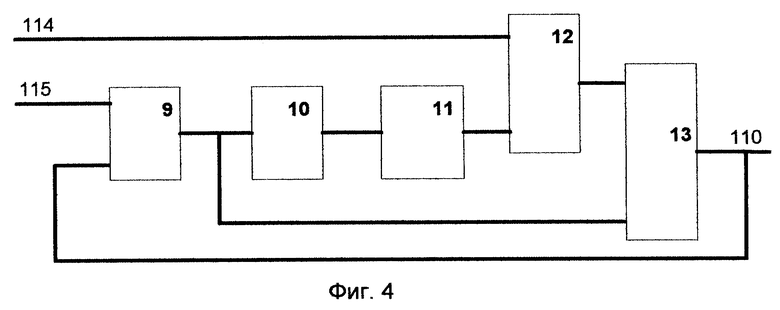

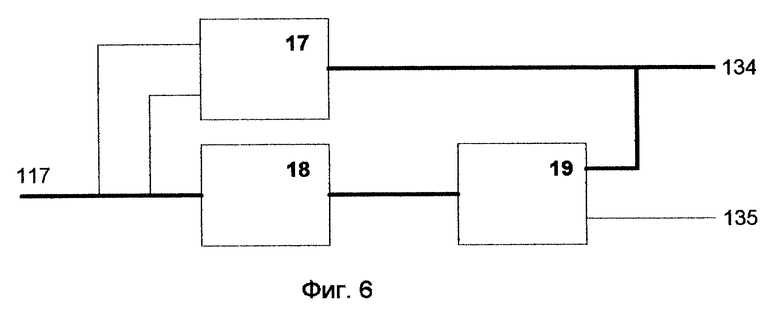

На фиг. 3 и фиг. 4 представлены блок-схемы соответственно синтезатора сокращенного описания сигнала и квазисовершенного корректора в устройстве для дискретной обработки сигналов по п. 3 формулы изобретения.

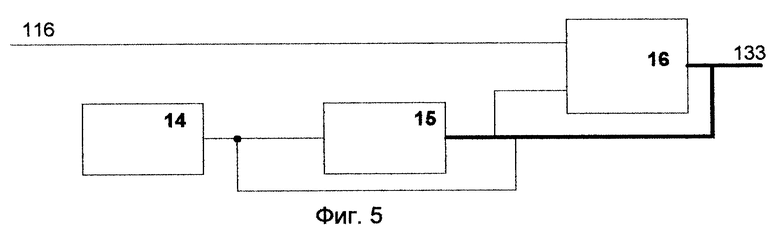

На фиг. 5 представлен пример блок-схемы дискретизатора.

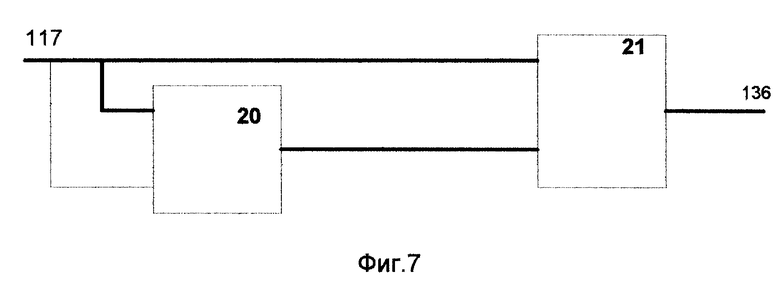

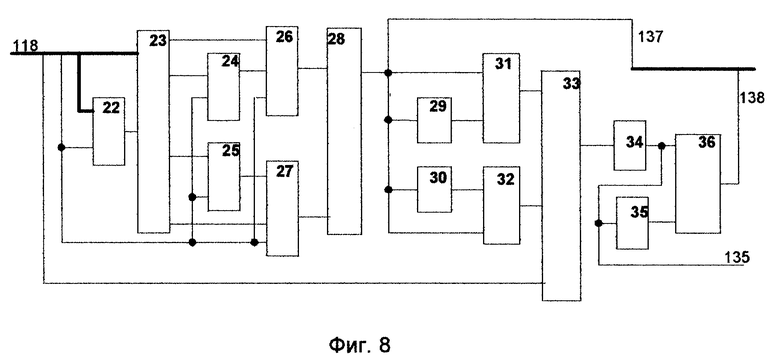

На фиг. 6, фиг. 7, фиг. 8 представлены примеры блок-схем соответственно определителя местоположения перепада, вычислителя производной, определителя местоположения экстремумов.

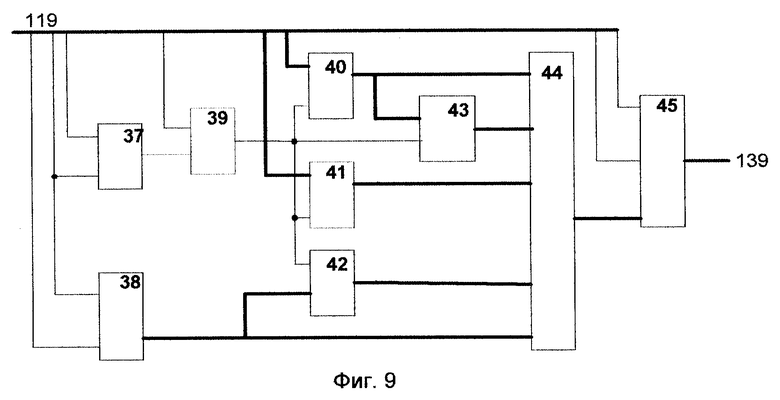

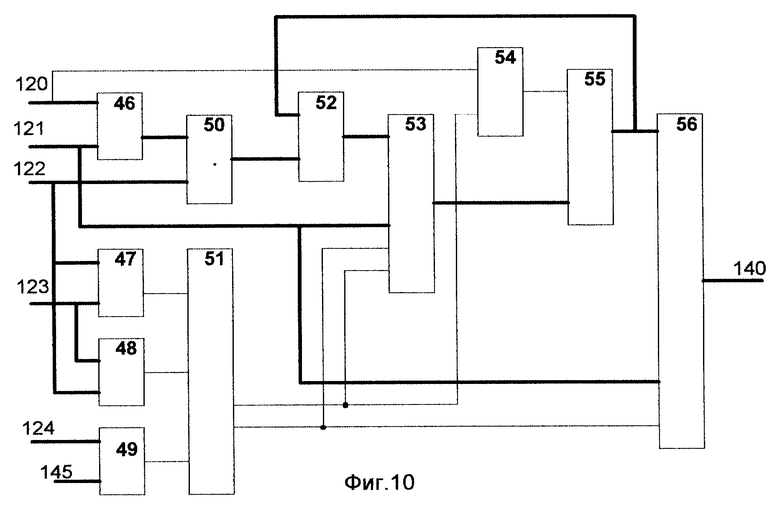

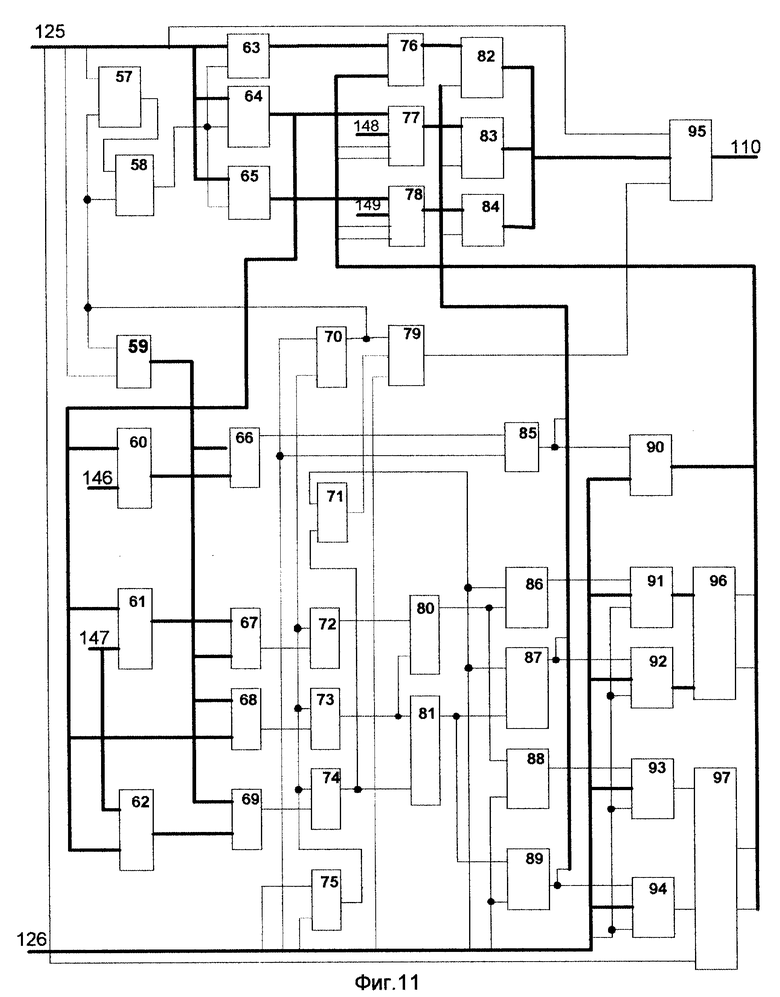

На фиг. 9, фиг. 10, фиг. 11 представлены примеры блок-схем соответственно формирователя сигнала по сокращенному описанию, интерполятора, корректора сокращенного описания.

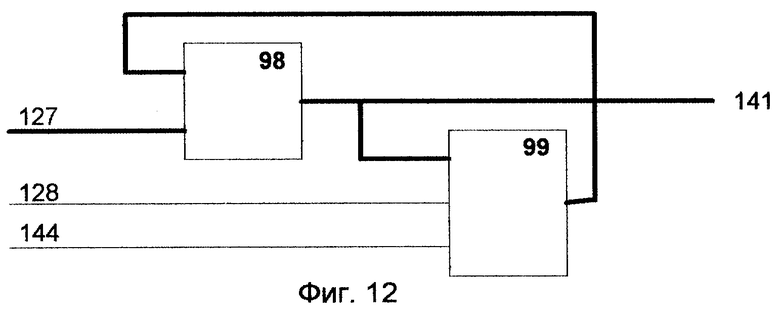

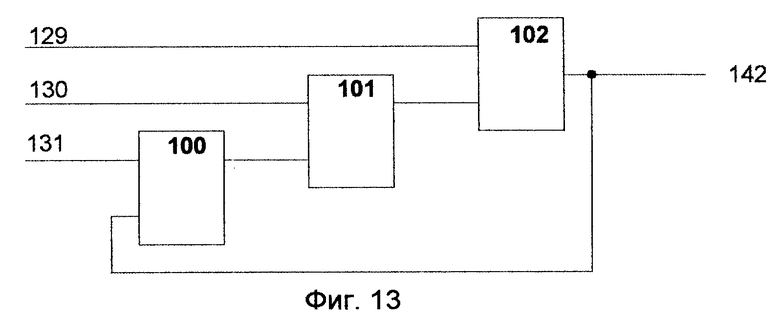

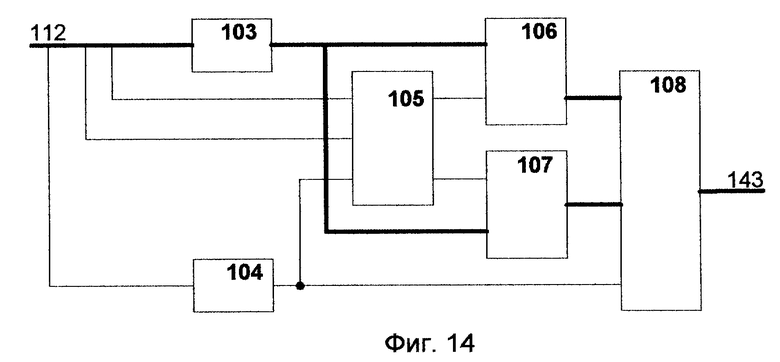

На фиг. 12, фиг. 13, фиг 14 представлены примеры блок-схем накапливающего сумматора, схемы выделения следующего импульса, интерполирующего узла.

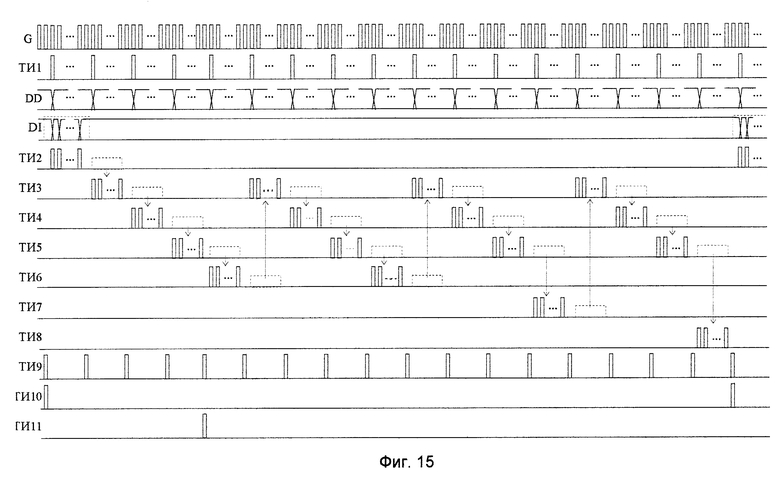

На фиг. 15 представлен пример временной диаграммы, описывающей работу дискретизатора и формирователя сетки частот.

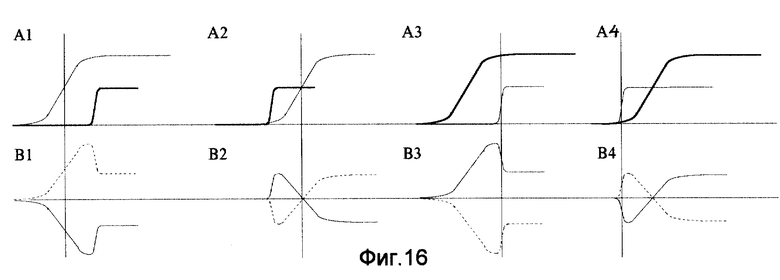

На фиг. 16 представлен пример вариантов сигналов на входах вычитателя (A1, A2, A3, A4), обусловленных перепадами в реальном входном и в синтезированном сигналах, и соответствующие разностные сигналы на выходе вычитателя в квазисовершенном корректоре (B1, B2, B3, B4), иллюстрирующие корректирование уровня синтезированного сигнала после перепада.

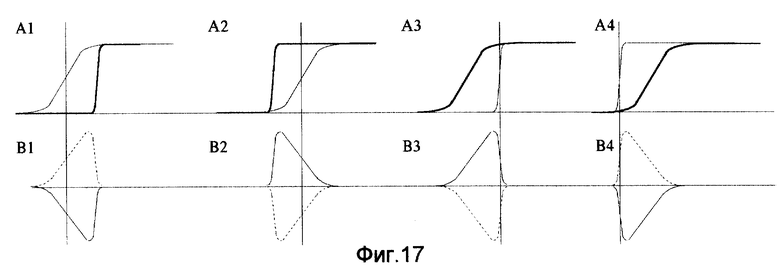

На фиг. 17 представлен пример вариантов сигналов на входах вычитателя (A1, A2, A3, A4), обусловленных перепадами в реальном входном и в синтезированном сигналах, и соответствующие разностные сигналы на выходе вычитателя в квазисовершенном корректоре (B1, B2, B3, B4), иллюстрирующие корректирование положения перепадов синтезированного сигнала.

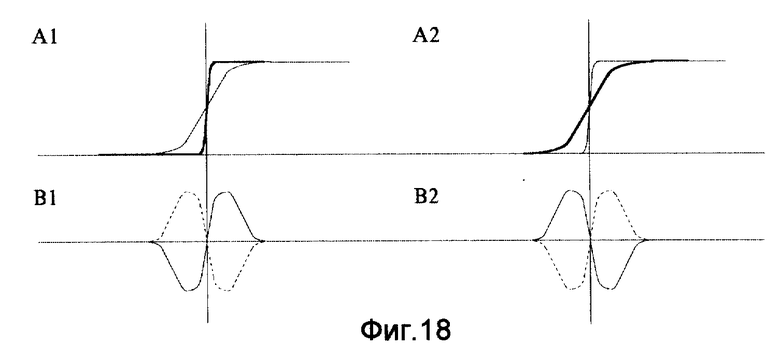

На фиг. 18 представлен пример вариантов сигналов на входах вычитателя в квазисовершенном корректоре (A1, A2), обусловленных перепадами в реальном входном и в синтезированном сигналах, и соответствующие разностные сигналы на выходе вычитателя (B1, B2), иллюстрирующие корректирование крутизны перепадов синтезированного сигнала.

На фиг. 16-18 сигналы, обусловленные перепадами реального входного сигнала, представлены жирными линиями. Пунктиром представлены разностные сигналы для отрицательных перепадов.

Первый вариант устройства содержит ФНЧ 1, дискретизатор 2, блок 3 редукции устройства к квазисовершенному.

Второй вариант устройства содержит ФНЧ 1, дискретизатор 2 и блок 3 редукции устройства к квазисовершенному, содержащий интерполирующий узел 4, синтезатор 5 сокращенного описания сигнала, квазисовершенный корректор 6.

Третий вариант устройства содержит ФНЧ 1, дискретизатор 2, блок 3 редукции устройства к квазисовершенному, содержащий интерполирующий узел 4, синтезатор 5 сокращенного описания сигнала, квазисовершенный корректор 6, а также в составе синтезатора 5 определитель 7 местоположения перепада и узел 8 памяти, в составе квазисовершенного корректора 6 коммутатор 9, формирователь 10 сигнала по сокращенному описанию, ФНЧ 11, вычитатель 12, корректор 13 сокращенного описания.

Дискретизатор 2 содержит, например, импульсный генератор 14, формирователь 15 сетки частот, аналого-цифровой преобразователь (АЦП) 16.

Определитель 7 местоположения перепада содержит, например, счетчик 17, вычислитель 18 производной, определитель 19 положения экстремумов.

Вычислитель 18 производной содержит, например, регистр 20, вычитатель 21.

Определитель 19 положения экстремумов содержит, например, регистр 22, элемент 23 сравнения, триггеры 24, 25, 28, элементы 26, 27 И, элементы 29, 30, 34, 35 задержки, элементы 31,32 ЗАПРЕТА (конъюнкции с одним запретом), элемент 33, 36 ИЛИ.

Формирователь 10 сигнала по сокращенному описанию содержит, например, триггер 37, счетчик 38, элемент 39 И, регистры 40, 41, 42, 43, интерполятор 44, цифровую линию задержки (ЦЛЗ) 45.

Интерполятор 44 содержит, например, вычитатели 46, 47, 49, сумматоры 48, 52, делитель 50, элемент 51 сравнения, коммутаторы 53,56, элемент 54 ЗАПРЕТА, регистр 55.

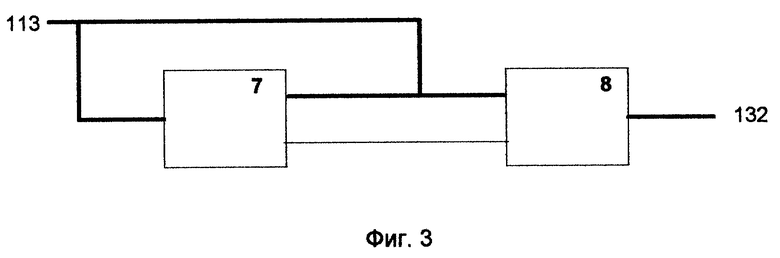

Корректор 13 сокращенного описания содержит, например, триггеры 57, 80, 81, элементы 58, 71 -73,74, 85-89 И, счетчик 59, сумматоры 60, 62, 76 - 78, вычитатель 61, регистры 63- 65, 82-84, 90, элементы 66-69, 96 сравнения, элементы 70, 75 ИЛИ, схему 79 выделения следующего импульса, накапливающие сумматоры 91-94, ЦЛЗ 95, дешифратор 97.

Каждый из накапливающих сумматоров 91-94 содержит, например, сумматор 98, регистр 99.

Схема выделения 79 следующего импульса содержит, например, элемент 100 ИЛИ, триггер 101, элемент 102 И.

Интерполирующий узел 4 содержит, например, ФНЧ 103, триггер 104, коммутаторы 105, 108, ЦЛЗ 106, 107.

Общей особенностью составных частей блока 3 редукции устройства к квазисовершенному, (а именно, интерполирующего узла 4, синтезатора 5 сокращенного описания сигнала, формирователя 10 сигнала по сокращенному описанию, ФНЧ 11, вычитателя 12, корректора 13 сокращенного описания) является наличие в каждой из них, кроме коммутатора 9, выходной памяти в виде ЦЛЗ, что позволяет по синхроимпульсам извне однократно считывать сформированные данные, необходимые для работы другой составной части. На фиг. 15 эти ситуации отражены пунктирными прямоугольниками, от которых стрелки направлены в сторону тактовых импульсов, являющимися внешними синхроимпульсами считывания данных из ЦЛЗ. Поскольку тактовые импульсы специализированны в обеспечении функционирования определенных составных частей блока 3 (ТИ1,G -интерполирующий узел 4; ТИ2 - синтезатор 5 сокращенного описания; ТИ 3 -формирователь 10 сокращенного описания сигнала; ТИ4 - ФНЧ 11; ТИ5 -вычитатель 12; ТИ 6 - корректор 13 сокращенного описания при коррекции уровня, ТИ7 - корректор 13 сокращенного описания при коррекции координат перепада; ТИ8 - корректор 13 сокращенного описания при коррекции ширины перепада), то эта мнемоника иллюстрирует, какие данные в работе какой составной части используются.

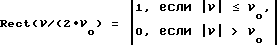

ФНЧ1 может быть выполнен, например, на основе индуктивностей и конденсаторов или резисторов и конденсаторов. Частотная характеристика ФНЧ 1 описывается, например, весовым окном Гаусса [6]

G(ν) = exp[-0,5•(A•ν/νo)2]•Rect(ν/(2•νo)),

где νo - - граничная частота ФНЧ 1,

A - параметр,

Узел 8 памяти может быть выполнен, например, в виде ЦЛЗ.

ФНЧ 11, 103 могут быть выполнены, например, на основе сумматоров, умножителей, регистров, логических элементов [7].

АЦП 16 может быть выполнен, например, в виде микросхемы AD570 [8].

Элементы 29, 30, 34, 35 задержки могут быть выполнены, например, в виде последовательно соединенных элементов 564 ЛН2 [7].

ФНЧ 1 (совместно с интерполирующим узлом 4) и ФНЧ 11 имеют одинаковые частотные характеристики и частоты дискретизации выходного сигнала.

Входы устройства:

109 - информационный вход.

Выходы устройства:

110 - информационный выход.

Входы и выходы составных частей, являющиеся входами и выходами составной части более высокого уровня, имеют номера входов и выходов составной части более высокого уровня.

Остальные входы блока 3, синтезатора 5, квазисовершенного корректора 6, дискретизатора 2, определителя 7 местоположения перепада, вычислителя 18 производной, определителя 19 положения экстремумов, формирователя 10 сигнала по сокращенному описанию, интерполятора 44, корректора 13 сокращенного описания, накапливающих сумматоров 91-94, схемы 79 выделения следующего импульса:

112 - вход блока 3,

113 - вход синтезатора 6,

114 - второй вход квазисовершенного корректора 6,

115 - первый вход квазисовершенного корректора 6,

116 - сигнальный вход дискретизатора 2,

117 - вход определителя 7 местоположения перепада,

118 - вход определителя положения экстремумов,

119 - вход формирователя сигнала по сокращенному описанию,

120 - вход (кода) текущего уровня перепада интерполятора 44,

121 - вход (кода) предыдущего уровня перепада интерполятора 44.

122 - вход (кода) ширины текущего перепада интерполятора 44,

123 - вход (кода) координаты текущего перепада интерполятора 44,

124 - вход (кода) текущей координаты интерполятора 44,

125 - вход (кода) сокращенного описания сигнала корректора 14 сокращенного описания,

126 - вход разностного сигнала корректора 14 сокращенного описания.

127 - информационный вход накапливающих сумматоров 91-94,

128 - синхровход накапливающих сумматоров 91-94,

144 - вход установки в нулевое состояние накапливающих сумматоров 91-94,

129 - вход серии импульсов схемы 79 выделения следующего импульса,

130 - информационный вход схемы 79 выделения следующего импульса (вход готовности коррективы),

131 - вход установки в исходное состояние схемы 79 выделения следующего импульса.

Остальные выходы синтезатора 5, дискретизатора 2, определителя 7 местоположения перепада, вычислителя 18 производной, определителя 19 положения экстремумов, формирователя 10 сигнала по сокращенному описанию, интерполятора 44:

132 - выход синтезатора 6,

133 - выход дискретизатора 2,

134 - информационный выход определителя 7 местоположения перепада,

135 - выход синхроимпульса определителя 7 местоположения перепада,

136 - выход вычислителя 18 произведений,

137 - выход знака перепада определителя 19 положения экстремумов,

138 - выход признака перепада определителя 19 положения экстремумов,

139 - выход формирователя 10 сигнала по сокращенному описанию,

140 - выход интерполятора 44,

141 - выход накапливающего сумматора 91-94,

142 - выход схемы 79 выделения следующего импульса,

143 - выход интерполирующего узла 4.

Внутренние входные шины - источники констант, задаваемых подключением отдельных линий к уровням логических "0" или "1":

145 - код задержки текущей координаты в интерполяторе 44,

146 - код задержки для коррекции уровня перепада в корректоре 13 сокращенного описания,

147 - код продолжительности анализа координаты и ширины перепада в корректоре 13 сокращенного описания.

148 - код коррективы координаты перепада в корректоре 13 сокращенного описания,

149 - код коррективы ширины перепада в корректоре 13 сокращенного описания.

На фиг. 1 - 14 тонкими линиями представлены одиночные связи для передачи одиночных сигналов, толстыми линиями - групповые связи для передачи групп сигналов.

Для упрощения описания далее рассматривается случай обработки одномерного сигнала при значении вышеуказанного параметра А, равном 3.5, что соответствует импульсной характеристике ФНЧ 1 без выбросов ("хвостов").

Последовательность действий составных частей устройства определяется тактовыми импульсами ТИ1-ТИ11, вырабатываемыми формирователем 15 сетки частот в составе дискретизатора 2. На фиг. 16, помимо тактовых импульсов, представлены также данные DD на выходе дискретизатора 2 и данные DI на выходе интерполирующего узла 4.

В исходном состоянии всех вариантов устройства на их информационном входе 109 сигнал отсутствует (действует сигнал, равный нулю), устройство обрабатывает нулевой сигнал, формируя нулевой сигнал во всех информационных сечениях и на своем выходе 110, то есть устройство находится в состоянии динамической готовности к обработке сигнала.

Первый вариант устройства для дискретной обработки сигналов работает следующим образом.

С поступлением сигнала на вход 109 устройства ФНЧ 1 преобразовывает его, ограничивая спектр соответственно своей граничной частоте νo. С выхода ФНЧ 1 сигнал с ограниченным спектром поступает на вход дискретизатора 2, который подвергает его дискретизации, например, с частотой νo и квантованию, например, равномерным двоичным 8-разрядным кодом.

С выхода дискретизатора двоичные коды отсчетов сигнала поступают на вход 112 блока 3 редукции устройства к квазисовершенному. Блок 3 производит интерполяцию полученных отсчетов сигнала, анализирует его с целью выявления перепадов и на этой основе формирует сокращенное описание сигнала как последовательность перепадов с характеристиками, приближенными к характеристикам перепадов во входном сигнале, то есть формирует на своем выходе 110, являющемся выходом устройства, квазисовершенный сигнал.

Второй вариант устройства характеризуется детализацией состава блока 3 редукции устройства к квазисовершенному, который работает следующим образом.

Двоичные коды отсчетов сигнала с выхода дискретизатора 2 поступают на вход 112 блока 3, являющийся входом интерполирующего узла 4, который производит вычисление отсчетов с меньшим шагом дискретизации, что необходимо для последующего выявления перепадов сигнала на его элементах предельно малой протяженности. Интерполированные отсчеты сигнала с выхода узла 4 в виде данных DI (фиг. 15) поступают на вход 113 синтезатора 5 сокращенного описания и на вход 114 квазисовершенного корректора 6. Синтезатор 5 выявляет в полученном сигнале, представленном его отсчетами, перепады и на этой основе формирует сокращенное описание сигнала, выдавая его через свой выход 132 на вход 115 квазисовершенного корректора 6. Квазисовершенный корректор 6 производит (поточечное) восстановление сигнала по полученному со своего входа 115 сокращенному описанию, фильтрацию восстановленного сигнала и (на основе сравнения этого фильтрованного сигнала с сигналом, полученным со своего входа 114) корректирование сокращенного описания. После коррекции сокращенное описание сигнала, ставшее сокращенным описанием квазисовершенного сигнала, выдается на выход квазисовершенного корректора 6, являющийся выходом блока 3 редукции устройства к квазисовершенному.

Третий вариант устройства характеризуется детализацией состава синтезатора 5 сокращенного описания сигнала и квазисовершенного корректора 6, которые работают следующим образом.

Со входа 113 синтезатора 5 интерполированные отсчеты поступают на вход 117 определителя 7 местоположения перепада и на второй вход узла 8 памяти. Определитель 7 местоположения перепада находит в сигнале перепады, определяет их координаты и знаки и в сопровождении признаков перепада выдает их через свой второй выход на второй вход узла 8 памяти. Синхронно с этими данными определитель 7 формирует синхроимпульс и выдает его через свой первый выход на первый вход узла 8 памяти. В узел 8 памяти (ЦЛЗ) данные записываются по заднему фронту синхроимпульса, приходящего на его первый вход из определителя 7 местоположения перепада. Во время заднего фронта этого синхроимпульса на втором входе узла 8 памяти присутствуют признак, знак и код координаты перепада, приходящие из определителя 7 местоположения перепада, а также код уровня сигнала после перепада, приходящий со входа 113 синтезатора 5 сокращенного описания сигнала. Поскольку сокращенное описание, формируемое синтезатором 5, является начальным и далее подвергается корректированию, то ширина перепада считается здесь постоянной, равной шагу дискретизации интерполированного сигнала, и поэтому в узел 8 памяти не записывается. Признак и знак перепада принципиально не являются необходимыми (так как информация о них содержится в уровнях перепадов), но записываются в узел 8 памяти для упрощения квазисовершенного корректора 6 (упрощение проявляется при детализации составных частей корректора по фиг. 4, формула изобретения инвариантна к наличию или отсутствию этих признаков и знака).

Со входа 115 квазисовершенного корректора 6 коды сокращенного описания сигнала поступают на первый вход коммутатора 9, который в это время находится в состоянии передачи на свой выход с первого входа. С выхода коммутатора 9 сокращенное описание поступает на вход формирователя 10 сигнала по сокращенному описанию и на второй вход корректора 13 сокращенного описания. Формирователь 10 преобразует сокращенное описание сигнала в последовательность кодов его отсчетов и выдает их через свой выход на вход ФНЧ 11. ФНЧ 11 производит частотную фильтрацию сигнала, поступившего на его вход в виде кодов отсчетов и выдает результат фильтрации (коды отсчетов фильтрованного сигнала) на первый вход вычитателя 12, на второй вход которого со второго входа 114 квазисовершенного корректора 6 поступают интерполированные отсчеты входного сигнала. Так как частотные характеристики и выходные частоты дискретизации ФНЧ 11 и интерполирующего узла 4 совместно с ФНЧ 1 одинаковы, то разностный сигнал, поступающий с выхода вычитателя 12 на первый вход корректора 13 сокращенного описания несет в себе информацию о различии реального входного и синтезированного сигналов. Используя этот разностный сигнал, корректор 13 сокращенного описания корректирует координаты, уровни и ширину перепадов. Скорректированное сокращенное описание с выхода корректора 13 поступает на выход 110 квазисовершенного корректора 6 и на второй вход коммутатора 9, который в это время находится в состоянии передачи данных со второго входа на его выход. Таким образом обеспечивается многократная коррекция сокращенного описания с итеративным приближением синтезированного сигнала к реальному входному. По окончании коррекции на входе 110 квазисовершенного корректора 6 действует достаточно приближенный к реальному входному и существенно более широкополосный, нежели на выходе интерполирующего узла 4, то есть квазисовершенный синтезированный сигнал.

Дискретизатор 2 работает следующим образом.

Генератор 14 вырабатывает импульсы G постоянной частоты, поступающие с его выхода в выходную шину 133 дискретизатора 2 и на вход формирователя 15 сетки частот. Формирователь 15 формирует из импульсов G тактовые импульсы ТИ1 - ТИ11. Импульсы ТИ1 с выхода формирователя 15 поступают на синхровход АЦП 16 и в выходную шину 133 дискретизатора 2. Импульсы ТИ2-ТИП с выхода формирователя 15 поступают в выходную шину 133 дискретизатора 2. АЦП 16 по переднему фронту каждого импульса ТИ1, поступающего на его синхровход, производит выборку (отсчет) значения сигнала, поступающего со входа 116 дискретизатора 2 на его сигнальный вход и преобразовывает это значение в линейный двоичный, например, 8- разрядный код, поступающий в виде данных DD с выхода АЦП 16 в выходную шину 133 дискретизатора 2. По шине 133 тактовые импульсы G, ТИ1-ТИП поступают на вход блока 3 редукции. Необходимые тактовые импульсы транслируются блоком 3 редукции и всеми его составными частями и, благодаря этому, присутствуют во всех информационных шинах устройства на всех уровнях (чтобы не перегружать рисунки, на фиг.1 - 14 трансляция тактовых импульсов не отражена).

Интерполирующий узел 4 работает следующим образом.

Со входа 112 отсчеты сигнала, произведенные дискретизатором 2, поступают на вход интерполирующего ФНЧ 103, с выхода которого интерполированные отсчеты с более высокой соответственно коэффициенту интерполяции частотой (например, вдвое более высокой частотой) поступают на информационные входы ЦЛЗ 106 и 107, на синхровход одной из которых через коммутатор 105 из входной шины 112 приходят тактовые импульсы ТИ4, по задним фронтам которых происходит запись интерполированных данных в соответствующую ЦЛЗ 106 или 107. На синхровход другой из этих ЦЛЗ 106 или 107 через коммутатор 105 из входной шины 112 поступают тактовые импульсы ТИ5, по задним фронтам которых происходит считывание данных из этой ЦЛЗ 106 или 107 через коммутатор 108 на выход 143. Коммутаторы 105 и 108 управляются по своим управляющим входам сигналом с выхода триггера 104, который меняет свое состояние на противоположное по заднему фронту каждого импульса ТИ10, приходящего из входной шины 112. При сигнале логической "1" на выходе триггера 104 коммутатор 105 пропускает на синхровходы ЦЛЗ 106 и 107 импульсы соответственно ТИ4 и ТИ5, а коммутатор 108 передает на выход 143 данные с выхода ЦЛЗ 107. При сигнале логического "0" на выходе триггера 104 картина обратная: коммутатор 105 пропускает на синхровходы ЦЛЗ 106 и 107 импульсы соответственно ТИ5 и ТИ4, а коммутатор 108 передает на выход 143 данные с выхода ЦЛЗ 106. Это обеспечивает работу синтезатора 5 и квазисовершенного корректора 6 в условиях непрерывного потока данных на выходе дискретизатора 2.

Определитель 7 местоположения перепада работает следующим образом.

Интерполированные отсчеты со входа 117 определителя 7 местоположения перепада поступают на вход вычислителя 18 производной, с выхода которого коды отсчетов производной поступают на вход определителя 19 положения экстремумов. Определитель 19 положения экстремумов определяет моменты экстремумов и формирует в эти моменты синхроимпульсы, означающие наличие в сигнале перепада. При этом локальным максимумам производной соответствуют положительные перепады, а локальным минимумам - отрицательные перепады, соответственно чему в определителе 19 положения экстремумов формируется знак перепада (положительному перепаду соответствует значение "0" знака перепада, отрицательному - значение "1" знака перепада). Одновременно в определителе 19 формируется признак перепада. Синхроимпульс с первого выхода определителя 19 положения экстремумов поступает на выход 135 определителя 7 местоположения перепада, признак и знак перепада со второго выхода определителя 19 поступает на выходную шину 134 определителя 7 местоположения перепада, в которой они совмещаются с кодом текущего значения координаты (то есть с кодом координаты перепада), приходящим с выхода счетчика 17, который увеличивает свое состояние на "1" по заданному фронту каждого тактового импульса ТИ2, приходящего на его синхровход, а предварительно устанавливается в "нулевое" состояние импульсом ТИ 9, приходящим на другой его вход (вход установки в "нулевое" состояние).

Вычислитель 18 производной работает следующим образом.

Интерполированные отсчеты со входа 117 вычислителя 18 производной поступают на информационный вход регистра 20 и заносятся в него задними фронтами импульсов ТИ2, приходящих из входной шины 117 на синхровход этого регистра 20. С выхода регистра 20 коды отсчетов поступают на вход вычитаемого вычитателя 21, на выход уменьшаемого которого поступают в это время следующие отсчеты. Таким образом, на выходе вычитателя 21 образуется последовательность кодов разности между текущими и предыдущими (опережающими на один такт импульсов ТИ2) отсчетами. Эти разности с точностью до постоянного множителя являются отсчетами производной сигнала, представленного интерполированными отсчетами, и с выхода вычитателя 21 поступают на выход 136 вычислителя 18 производной.

Определитель 19 положения экстремумов работает следующим образом.

С выхода 136 вычислителя 18 производной отсчеты производной через вход 118 определителя 19 положения экстремумов поступают на первый вход, а после задержки в регистре 22 на один такт импульсов ТИ2 - на второй вход элемента 23 сравнения (в регистр 22 отсчеты производной заносятся по задним фронтам импульсов ТИ2, приходящих на его синхровход из входной шины 118). Если отсчеты, приходящие на первый вход, обозначить через аi, а отсчеты, приходящие на второй вход схемы 24 сравнения, - через аi-1, то сигнал логической "1" на первом, втором, третьем, четвертом выходах элемента 23 сравнения будет вырабатываться, если соответственно аi≥ai-1, аi<аi-1, аi> аi-1, аi≤ai-1. Сигналы с первого и четвертого выходов элемента 23 сравнения поступают на первые входы элементов 26, 27 И, на вторые входы которых поступают сигналы со второго и третьего выходов элемента 23 сравнения после задержки на триггерах соответственно 24 и 25, в которые эти сигналы заносятся по задним фронтам импульсов ТИ2, приходящих на их синхровходы из выходной шины 118. Таким образом на выходе элемента 26 И сигнал логической "1" формируется, если на входах элемента 23 сравнения сложилось условие ai≥ai-1 после выполнения на предыдущем такте условия аi-1<ai-2. На выходе элемента 27 И сигнал логической "1" формируется, если на входах элемента 23 сравнения сложилось условие ai≤ai-1 после выполнения на предыдущем такте условия ai-1>аi-2. Иначе говоря, сигналы логической "1" на выходах элементов 26, 27 И формируются, если производная сигнала на входе 118 определителя 19 положения экстремумов имеет значение соответственно локального минимума и локального максимума. Эти сигналы, стробированные по третьим входам элементов 26, 27И импульсами ТИ2, поступают соответственно на вход установки в состояние "1" и на вход установки в состояние "0" триггера 28, то есть триггер 28 состояние "1" имеет после каждого отрицательного перепада во входном для устройства сигнале и состояние "0" после каждого положительного перепада. Сигнал с выхода триггера 28 поступает на выход 137 определителя 19 положения экстремумов в качестве знака перепада и на вход двух пар из элемента задержки и элемента И (29, 31 и 30, 32), являющихся формирователями импульсных сигналов логической "1" соответственно по переднему и заднему фронтам. Эти импульсные сигналы поступают на первый и второй входы элемента 33 ИЛИ и дают на его выходе импульс, соответствующий каждому перепаду входного сигнала независимо от его знака. С выхода элемента 33 ИЛИ импульс, задержавшись на элементе 34 задержки (для обеспечения правильного момента записи в узел 8 памяти), поступает на выход 135 в качестве синхроимпульса и на вход расширителя на элементах 35 задержки и 36 ИЛИ, с выхода которого расширенный импульс поступает на выход 138 определителя 19 положения экстремумов в качестве признака перепада. Выходы 137 знака и 138 признака перепада объединяются в шину, являющуюся вышеописанным вторым выходом определителя 19 положения экстремумов. На третий вход элемента 33 ИЛИ из входной шины 118 поступают импульсы ТИ3, обеспечивая считывание данных из узла 8 памяти, необходимых для работы формирователя 10 сигнала по сокращенному описанию.

Формирователь 10 сокращенного описания работает следующим образом.

Коды элементов сокращенного описания сигнала со входа 119 формирователя 10 поступают: признак перепадов - на информационный вход триггера 37, код ширины перепада - на информационный вход регистра 41, код уровня - на информационный вход регистра 40. Импульс ТИ9, приходящий на вход установки в "ноль" счетчика 38, приводит этот счетчик в начальное состояние, после чего по заднему фронту каждого импульса ТИ3 счетчик 38 увеличивает код своего состояния на "единицу" выдает этот код в качестве текущей координаты со своего выхода на информационный вход регистра 42 и на вход 124 интерполятора 44. При наличии признака перепада импульс ТИ 3, приходящий на синхровход триггера 37, устанавливает этот триггер в "единичное" состояние, благодаря чему импульс ТИ3 проходит через элемент 39 И на синхровходы регистров 40-43 и заносит в них коды соответственно уровня, ширины перепада, координаты перепада и (с выхода регистра 40) уровня после предыдущего перепада, которые с выходов этих регистров поступают на входы соответственно 120, 122, 123 и 121 интерполятора 44. Интерполированные в соответствии с шириной перепада, отсчеты сигнала с выхода 140 интерполятора 44, поступают на информационный вход ЦЛЗ 45 и записываются в нее по задним фронтам импульсов ТИ3, приходящих на первый синхровход ЦЛЗ 45 из входной шины 119. Приходящие из входной шины 119 на второй синхровход ЦЛЗ 45 импульсы ТИ4 обеспечивают считывание данных, необходимое для работы ФНЧ 11. Считываемые из ЦЛЗ 45 данные с ее выхода поступают в выходную шину 139 формирователя 10 сокращенного описания.

Интерполятор 44 работает следующим образом.

Уровень сигнала после текущего перепада со входа 120 интерполятора 44 поступает на вход уменьшаемого вычитателя 46. Уровень после предшествующего перепада со входа 121 поступает на вход вычитаемого вычитателя 46, на первый информационный вход коммутатора 53 и на первый информационный вход коммутатора 56. Код Ш ширины перепада со входа 122 поступает на первый вход делителя 50, на вход вычитаемого вычитателя 47 и на первый вход сумматора 48. Код К координаты текущего перепада со входа 123 поступает на вход уменьшаемого вычитателя 47 и на второй вход сумматора 48. Код М текущей координаты со входа 124 поступает на вход уменьшаемого вычитателя 49, на вход вычитаемого которого поступает формируемый в интерполяторе 44 код константы, соответствующей задержке τ (в числе тактов импульсов ТИ3) в интерполяторе 44, которая необходима для вычисления интерполируемых значений в точках, предшествующих середине перепада, и равна половине максимально возможной ширины перепада. С выхода вычитателя 46 код разности между уровнями текущего и предшествующего перепадов поступает на второй вход делителя 50, с выхода которого эта разность, поделенная на ширину перепада (то есть квант изменения синтезированного сигнала в пределах перепада при линейной его интерполяции), поступает на первый вход сумматора 52. С выходов вычитателя 47, сумматора 48 и вычитателя 49 коды соответственно G1=К-Ш/2 нижней границы перепада, G2= К+Ш/2 верхней границы перепада и n=m- τ задержанной текущей координаты поступают соответственно на первый, второй и третий входы элемента 51 сравнения. На первом выходе элемента 51 сравнения сигнал логической "1" формируется при выполнении условия n≥G1, на втором - при выполнении условия n≥G2. Сигнал с первого выхода элемента 51 сравнения поступает на первый управляющий вход коммутатора 53 и на управляющий вход коммутатора 56, со второго выхода элемента 51 сравнения - на второй управляющий вход коммутатора 53 и на первый вход (вход запрета) элемента 54 ЗАПРЕТА. Коммутатор 53 передает на свой выход код с первого информационного входа, если на первом управляющем входе действует сигнал логического "0" (то есть при выполнении условия n<G1) и со второго информационного входа, если на первом управляющем входе действует сигнал логической "1", а на втором управляющем входе действует сигнал логического "0" (то есть при выполнении условия G1≤n≤G2). Через элемент 54 ЗАПРЕТА со второго его входа на синхровход регистра 55 импульсы ТИ3 из входной шины 120 проходят, если на первом его входе действует сигнал логического "0" (то есть при выполнении условия n<G2). Коммутатор 56 передает на свой выход, являющийся выходом 140 интерполятора 44, коды со своих первого и второго информационных входов, если на его управляющем входе действует сигнал соответственно логического "0" и логической "1" (то есть при выполнении условий соответственно n<G1 и n≥G1). Поэтому сначала (при n<G1) на выход 140 интерполятора со входа 121 через коммутатор 56 проходит код уровня предшествующего перепада. Одновременно с этим через коммутатор 53 этот уровень проходит на информационный вход регистра 55 и заносится в него задним фронтом импульса ТИ3 с выхода элемента 54 ЗАПРЕТА. С выхода регистра 55 код уровня предшествующего перепада поступает на второй вход сумматора 52 и на каждом следующем такте импульсов ТИ3 (то есть при G1≤n≤G2) изменяется на очередной квант линейной интерполяции, так как в это время коммутатор 53 через свои выход и второй вход соединяет выход сумматора 52 с информационным входом регистра 55. Линейно изменяющиеся коды перепада через второй вход коммутатора 56 проходят в выходную шину 140. С наступлением условия n>G2 коммутатор 53 и элемент 54 ЗАПРЕТА закрываются и на выход 140 через коммутатор 56 проходит постоянный код с выхода регистра 55, равный уровню текущего перепада. С приходом следующего перепада этот уровень становится уровнем предыдущего перепада и продолжает проходить на выход 140 через коммутатор 56, но уже с его первого информационного входа. Далее работа интерполятора 44 повторяется вышеописанным образом.

Корректор 13 сокращенного описания работает следующим образом.

Коды элементов сокращенного описания со входа 125 корректора 13 сокращенного описания поступают: код уровня - на информационный вход регистра 63, код координаты перепада - на информационный вход регистра 64, код ширины перепада - на информационный вход регистра 65, признак перепада - на информационный вход триггера 57, знак перепада - на первый вход дешифратора 97. Разностный сигнал со входа 126 поступает на информационные входы регистра 90 и накопительных сумматоров 91-94. На элементе 75 ИЛИ объединяются поступающие на его входы из входной шины 126 тактовые импульсы ТИ7 и ТИ8. С выхода элемента 75 ИЛИ эти импульсы поступают на первые входы элементов 70 ИЛИ и 72 -74 И. Тактовые импульсы ТИ6 из входной шины 126 поступают на второй вход элемента 70 ИЛИ и первый вход элемента 85 И. Тактовые импульсы ТИ7 из входной шины 126 поступают также на первые входы элементов 86, 87 И, тактовые импульсы ТИ8 - на первые входы элементов 88, 89 И, а тактовые импульсы ТИ9 - на вход 131 установки в исходное состояние схемы 79 выделения следующего импульса и на входы установки в "нулевое" состояние сумматоров 91 - 94. С выхода элемента 70 ИЛИ импульсы ТИ678 (объединенные ТИ6, ТИ7, ТИ8) поступают на синхровходы триггера 57 и счетчика 59, на первый вход элемента 58 И и на вход 129 схемы 79 выделения следующего импульса. С выхода триггера 57 признак перепада, заносимый в него по переднему фронту импульса ТИ678, поступает на второй вход элемента 58 И, благодаря чему импульсы ТИ678 проходят на синхровходы регистров 63, 64, 65 и своими задними фронтами заносят в них коды соответственно уровня, координаты и ширины перепада, далее поступающие на первые входы сумматоров 76-78. С выхода регистра 64 код координаты (середины) перепада поступает также на входы сумматоров 60, 62, на вход уменьшаемого вычитателя 61 и на первый вход элемента 68 сравнения. На второй вход сумматора 60 подается код константы, соответствующей задержке для получения благоприятного момента съема кода коррективы уровня (в разностном сигнале). На вход вычитаемого вычитателя 61 и на второй вход сумматора 62 подается код константы, соответствующей продолжительности анализа разностного сигнала на предмет коррекции положения и ширины перепада. Таким образом, на выходе сумматора 60, вычитателя 61 и сумматора 62 формируются коды соответственно координаты съема коррективы уровня, координаты начала и координаты окончания анализа разностного сигнала (с целью выработки коррективы положения и ширины перепада), поступающие на первые входы элементов соответственно 66, 67 и 69 сравнения. После установки счетчика 59 (импульсом ТИ9, поступающем на его вход из входной шины 125) в "нулевое" состояние по задним фронтам импульсов ТИ678 в нем формируется последовательно нарастающий код М текущего значения координаты. С выхода счетчика 59 код текущей координаты поступает на вторые входы элементов 66-69 сравнения. В момент совпадения кодов текущей координаты с кодами, действующими на первых входах элементов 66-69 сравнения, на выходах этих элементов формируются сигналы логической "1", которые поступают на вторые входы элементов соответственно 85, 72-74 И, стробируются на этих элементах импульсами ТИ6, ТИ78 (объединенными импульсами ТИ7 иТИ8) и проходят на синхровход регистра 90 и на установочные входы триггеров 80, 81: с выхода элемента 72 И - на вход установки триггера 80 в состояние "1", с выхода элемента 73 И - на вход установки триггера 80 в состояние "0" и триггера 81 в состояние "1", с выхода элемента 74 И - на вход установки триггера 81 в состояние "0" (в состояние "1" триггеры устанавливаются по переднему фронту, в состояние "0" - по заднему). В результате, по переднему фронту импульса на синхровходе регистра 90 корректива уровня заносится в регистр 90 и с его выхода поступает на второй вход сумматора 76, а на выходе триггеров 80 и 81 формируются сигналы логической "1", продолжительность которых определяет интервалы анализа разностного сигнала соответственно слева и справа от координаты середины перепада. Эти сигналы логической "1" поступают на вторые выходы элементов соответственно 86, 88 и 87, 89 И, обеспечивая прохождение через них в течение интервалов анализа на синхровыводы накапливающих сумматоров 91, 92 и 93, 94 тактовых импульсов соответственно ТИ7 и ТИ8. По передним фронтам этих импульсов в сумматорах 91, 92 производятся накопление модулей отсчетов разностного сигнала, в сумматорах 93, 94 - накопление отсчетов разностного сигнала с учетом их знаков. С выходов сумматоров 91 и 92 накопленные суммы (обозначим их соответственно L и R) поступают на входы элемента 96 сравнения, на первом выходе которого сигнал логической "1" формируется при условии L>R, на втором выходе - при условии L<R. Эти сигналы с выходов элемента 96 сравнения поступают соответственно на первый и второй управляющие выходы сумматора 77, задающие соответственно уменьшение или увеличение координат перепада на величину корректирующей константы, действующей на втором информационном входе сумматора 77, что соответствует иллюстрации, представленной на фиг. 17. С выходов сумматоров 93, 94 знаки накопленных сумм (обозначим их соответственно SL и SR) поступают на второй и третий входы дешифратора 97, логические сигналы на выходах которого формируется соответственно таблице.

Сигналы с первого и второго выходов дешифратора 97 поступают на первый и второй управляющие входы сумматора 78, задавая соответственно уменьшение или увеличение ширины перепада на величину корректирующей константы, действующей на втором информационном выходе сумматора 78, что соответствует иллюстрации, представленной на фиг. 18. По задним фронтам импульсов, поступающих с выходов элементов 85, 87, 89 И на синхровходы регистров 82, 83, 84, скорректированные уровень, координата и ширина перепада, поступающие с выходов сумматоров 76, 77, 78 на информационные входы регистров 82, 83, 84, записываются в эти регистры. С выходов этих регистров названные характеристики перепадов поступают во входную шину данных ЦЛЗ 95. В эту же шину с выхода регистра 63 поступают признак и знак перепада. С выхода элемента 74 И импульсы поступают также на выход элемента 71 И, который стробирован импульсами ТИ8 и поэтому выделяет на своем выходе только последний импульс интервала анализа ширины перепада. Этот импульс с выхода элемента 71 И поступает на вход 130 схемы 79 выделения следующего импульса из числа поступающих в это время на ее вход 129. Схема 79 выделяет следующий импульс, который с ее выхода поступает на синхровход ЦЛЗ 95 и по заднему фронту записывает в нее коды сокращенного описания, действующие на ее информационном входе. По каждому из следующих перепадов коды элементов которых поступают на вход 125, вышеописанные действия корректора 13 сокращенного описания повторяются. По задним фронтам импульсов ТИ3, приходящих на второй синхровход ЦЛЗ 95, считываемые из нее данные выдаются на выход 110, что необходимо для работы формирователя 10 сигнала по сокращенному описанию (при повторении коррекции сокращенного описания) и для выдачи данных из устройства.

Накапливающий сумматор 91-94 работает следующим образом.

По импульсу ТИ9, приходящему со входа 144 на установочный вход регистра 99, этот регистр устанавливается в "нулевое" состояние. Выходной код регистра 99 поступает на вход сумматора 98 и складывается в нем с кодом, поступающим на его второй вход со входа 127 накапливающего сумматора. Получившаяся сумма с выхода сумматора 98 поступает на выход 141 и на информационный вход регистра 99 и заносится в него задним фронтом импульса, приходящего на синхровход регистра 99. Повторение действий занесения в регистр 99 сумм с выхода сумматора 98 дает в регистре 99 накопляемую сумму кодов, поступающих на вход 127 в сопровождении синхроимпульсов на входе 128. Соединение выхода 141 с выходом сумматора 98 позволяет по заднему фронту последнего накапливающего синхроимпульса заносить реакцию на последнюю накопленную сумму в регистры 83, 84 корректора 44 сокращенного описания.

Схема 79 выделения следующего импульса работает следующим образом.

По заднему фронту импульса ТИ9 через элемент 100 ИЛИ триггер 101 устанавливается в "нулевое" состояние. Приходящий после этого в произвольное время со входа 130 импульс готовности коррективы, привязанный к серии ТИ6, своим задним фронтом устанавливает триггер 101 в "единичное" состояние. Следующий за импульсом готовности по входу 129 импульс серии ТИ78 проходит через элемент 102 И на выход 142, а также через элемент 100 ИЛИ на установочный вход триггера 101, переводя этот триггер в "нулевое" состояние и тем самым закрывая элемент 102 И.

Работоспособность каждого варианта устройства обеспечивается при (Топ. 1<Т3)& (Топ.2<Т678), где Т3 - длительность периода импульсов ТИ3; Т678 -длительность периода импульсов ТИ6, ТИ7, ТИ8; Топ.1 - суммарная задержка (время выполнения операций) на триггере 37, элементе 39 И, регистре 40, регистре 43, вычитателе 46, делителе 50, сумматоре 52, коммутаторе 53; Топ.2 - суммарная задержка на триггере 57, элементе 58 И, регистре 64, вычитателе 61, элементе 67 сравнения, элементе 72 И, триггере 80, элементе 86 И, накопительном сумматоре 91, элементе 96 сравнения, сумматоре 97.

Сущность предлагаемого изобретения не меняется при перераспределении функций между составными частями устройства, при включении в его состав выходного средства восстановления сигнала по его сокращенному описанию и/или средства для дополнительного сжатия данных, представляющих обработанный сигнал, при нелинейной интерполяции перепадов сигнала.

Сокращенное описание обработанного сигнала, в силу его компактности, является предпочтительной формой хранения обработанных данных.

Для анализа данных, обработанных предлагаемым устройством, требуется поточечное восстановление сигнала по алгоритму вышеописанного формирователя 10 сигнала по сокращенному описанию.

Наибольший эффект предлагаемое устройство для дискретной обработки сигналов дает при его применении в системах для дискретной обработки сигналов с необходимостью хранения и/или передачи данных, где, помимо повышения разрешения, важно и уменьшение объема данных, представляющих обрабатываемые сигналы.

Коэффициент повышения разрешения, при котором анализ обработанных сигналов не затруднен осцилляциями и пониженным контрастом малопротяженных элементов сигнала, составляет не менее 2 по сравнению с устройствами-аналогами. При этом коэффициент уменьшения объема данных (при одинаковом разрешении предлагаемого устройства и устройств-аналогов) достигает в случае одномерных сигналов значений 2,0-3,0 и возрастает по степенному закону соответственно размерности обрабатываемых сигналов.

Использованная литература

1. Обработка изображений и цифровая фильтрация. Под редакцией Т. Хуанга. - М.: Мир, 1979, стр. 261.

2. Василенко Г.И. Теория восстановления сигналов. О редукции к идеальному прибору в физике и технике. - М.: Сов. радио, 1979, стр. 109-121.

3. Михайлов Б.А. К выбору частоты дискретизации, достаточной для восстановления формы непрерывного сигнала. - Электронная техника. Сер. 10. Микроэлектронные устройства, вып. 4 (46), 1984.

4. Michael L. Hilton, Bjom D. Jawerth, Ayan Sengupta. Compressing Still and Moving Images with Wavelets. - Multimedia Systems, Vol. 2, No. 3, April 18, 1994, p. 7-11.

5. А. Папулис. Теория систем и преобразований в оптике. - М.: Мир, 1971, стр. 28.

6. Ф. Дж. Хэррис. Использование окон при гармоничном анализе методом дискретного преобразования Фурье. - ТИИЭР, т. 66, N1, 1978, стр. 82.

7. Триполитов С. В. , Ермилов А. В. Микросхемы, диоды, транзисторы. Справочник. - М.: Машиностроение, 1994, стр. 205-207, 218-232, 310-313.

8. DESIGN - IN Reference Manual. - Analog Devices, Inc., 1994, стр. 2.18.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛОВ | 2000 |

|

RU2195014C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛОВ | 2008 |

|

RU2385489C1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛА ЦВЕТНОГО ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2030843C1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| Устройство передачи и приема сигналов | 1983 |

|

SU1312746A1 |

| Устройство для вывода графической информации | 1978 |

|

SU752403A1 |

| Устройство для регистрации информации | 1978 |

|

SU769576A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2344541C1 |

| Цифровой синтезатор речи | 1980 |

|

SU930365A1 |

| Устройство для формирования графических изображений | 1978 |

|

SU752404A1 |

Изобретение относится к области дискретной обработки сигналов. Техническим результатом является повышение разрешения элементов сигнала, при котором паразитные осцилляции не затрудняют анализ сигнала, и уменьшение объема представляющих его данных. Для этого оно содержит фильтр низких частот, дискретизатор и блок редукции устройства к квазисовершенному, при этом блок редукции устройства к квазисовершенному содержит интерполирующий узел, синтезатор сокращенного описания сигнала и квазисовершенный корректор, синтезатор сокращенного описания сигнала содержит определитель местоположения перепада и узел памяти, квазисовершенный корректор содержит коммутатор, формирователь сигнала по сокращенному описанию, фильтр низких частот, вычитатель, корректор сокращенного описания. 3 с. п. ф-лы, 18 ил., 1 табл.

| MICHAEL L | |||

| HILTON et al | |||

| Compressing still and Moving Images with Warelet, Multimedia Systems | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Василенко Г.И | |||

| Теория восстановления сигналов | |||

| О редукции к идеальному прибору в физике и технике.-М.: Советское радио, 1979, с | |||

| Шкив для канатной передачи | 1920 |

|

SU109A1 |

| Хуанга Т | |||

| Обработка изображений и цифровая фильтрация.-М.: Мир, 1979, с | |||

| Одновальный, снабженный дробителем, торфяной пресс | 1919 |

|

SU261A1 |

| US 4218704 A, 19.08.80 | |||

| Устройство квантования видеосигнала | 1973 |

|

SU467499A1 |

| Триполитов С.В | |||

| и др | |||

| Микросхемы, диоды, транзисторы./Справочник.-М.: Машиностроение, 1994, с | |||

| Автоматическая акустическая блокировка | 1921 |

|

SU205A1 |

Авторы

Даты

1999-11-20—Публикация

1998-09-11—Подача